《嵌入式系统基础教程》第07讲_第4章ARM存储器组织和异常中断_习题.pptx

嵌入式系统开发第四章课后作业答案

第四章LPC2000系列ARM硬件结构1、基础知识(8)、FIQ、IRQ有什么不同?向量IRQ和非向量IRQ有什么不同?答:FIQ是快速中断,具有最高优先级,中断处理转入FIQ模式;IRQ是普通中断,优先级低于FIQ,中断处理转入IRQ模式。

向量IRQ支持16个向量IRQ中断,16个优先级,能为每个中断源设置服务程序地址;非向量IRQ支持一个非向量IRQ中断,所有中断都共用一个相同的服务程序入口地址。

(9)、在使能,禁止FIQ和IIRQ时,为什么操作SPSR寄存器而不操作CPSR寄存器?答:在用户模式下,无法修改CPSR,只有在特权模式下修改SPSR后,通过退出特权模式,然后恢复SPSR到CPSR,才能修改CPSR。

(11)、向量中断能嵌套吗?请结合ARM体系结构进行阐述。

答:ARM的中断管理体系和51系列微控制器的中断管理体系不太一样。

ARM的中断不会自动嵌套,实现ARM微控制器的中断嵌套比较烦琐,不提倡中断嵌套。

但不排除需要嵌套的应用,因而在启动代码中,有对中断嵌套的处理。

中断嵌套的原则:低优先级的中断嵌套高优先级的中断可嵌套中断服务程序编写方法:1、保存当前中断使能寄存器VICIntEnable的值;2、禁止当前中断和低优先级中断;3、清除中断逻辑,使VIC能够响应更高优先级的中断;4、中断处理服务程序;5、恢复保存的中断使能寄存器的值。

(19)LPC2000系列ARM7微控制器具有哪两种低耗模式?如何降低系统的功耗?答: 2 个低功耗模式:空闲和掉电;降低功耗方法:设定极低功耗定时器每一秒钟触发CPU一次->CPU进入掉电状态->一秒钟后定时器触发CPU进入工作模式,写液晶显示器显示字符(走秒)->CPU进入掉电模式->一秒钟后定时器再次出发CPU进入工作模式。

ARM嵌入式学习教程第07讲

编I函数

µC/OS-Ⅱ(其它内核也一样)要求用户提供定时中断 来实现延时与超时控制等功能。这个定时中断叫 做时钟节拍,时钟节拍由OS_TICKS_PER_SEC 宏定义设定。时钟节拍的实际频率是由用户的应 用程序决定的。时钟节拍的频率越高,系统的负 荷就越重。 注意在具体设定是要考虑到处理器的 实际情况,太低可能造成定时器溢出,太高系统 负荷太重。

嵌入式人才培养工程

ARM嵌入式系统设计与 项目开发

第七讲 uC/OS-II多任务调度和通信 主要内容

uC/OS-II多任务程序的编写 uC/OS-II任务之间通信手段的介绍 uC/OS-II多任务间通信程序的编写

uC/OS可以管理64个任务,但目前的版本系统占用了两个任 务,还保留了其他六个任务,故用户可以使用56个任务。每 个任务必须赋予一定的优先级,优先级数越高,优先级越 低,所以0级优先级的任务有最高的优先级。通过在 OS_CFG.H文件中定义宏OS_LOWEST_PRIO可以决定系统 的任务的个数。系统目前占用的两个任务为空闲任务IDLE TASK和统计任务STAT TASK。当没有其他任务进入就绪状 态时空闲任务投入运行,空闲任务什么也不做,只是简单的 将计数器加1,这个计数器可以用来统计CPU的利用率。

uC/OS下每个任务可以有如下五种状态:

休眠态(dormant):指任务驻留在程序空间中,还没有交给内 核管理。把任务交给内核是通过调用OSTaskCreate( )或 OSTaskCreatExt( )实现的。 就绪(Ready):当任务一旦建立,这个任务就处于就绪态准备 运行。任务可以动态的被另一个程序建立,也可以在系统运 行开始之前建立。通过调用OSTaskDel( )使任务返回到休眠 态。就绪态的任务都放在就绪列表中。在任务调度时,指针 OSTCBHighRdy指向优先级最高的就绪任务,也就是立刻 就要运行的任务。

ARM嵌入式系统基础教程试题及答案

《ARM嵌入式系统基础教程》试题及答案一、选择题1、以下说法不正确的是(B )。

A、任务可以有类型说明B、任务可以返回一个数值C、任务可以有形参变量D、任务是一个无限循环2下列描述不属于RISC计算机的特点的是(C)。

A.流水线每周期前进一步。

B.更多通用寄存器。

C.指令长度不固定,执行需要多个周期。

D.独立的Load和Store指令完成数据在寄存器和外部存储器之间的传输。

3 存储一个32位数0x2168465到2000H~2003H四个字节单元中,若以大端模式存储,则2000H存储单元的内容为(D)。

A、0x21B、0x68C、0x65D、0x024 μCOS-II中对关键代码段由于希望在执行的过程中不被中断干扰,通常采用关中断的方式,以下X86汇编代码正确而且不会改变关中断之前的中断开关状态的是(D)A.先CLI、执行关键代码、再STIB. 先STI、执行关键代码、再CLIC. 先POPF、CLI、执行关键代码、再PUSHFD. 先PUSHF、CLI、执行关键代码、再POPF。

5 RS232-C串口通信中,表示逻辑1的电平是(D )。

A、0vB、3.3vC、+5v~+15vD、-5v~-15v6 ARM汇编语句“ADD R0, R2, R3, LSL#1”的作用是(A)。

A.R0 = R2 + (R3 << 1)B. R0 =( R2<< 1) + R3C. R3= R0+ (R2 << 1)D. (R3 << 1)= R0+ R27 IRQ中断的入口地址是(C)。

FIQ的入口地址为0x0000001CA、0x00000000B、0x00000008C、0x00000018D、0x000000148 S3C2420X I/O口常用的控制器是(D)。

A.端口控制寄存器(GPACON-GPHCON)。

B.端口数据寄存器(GPADAT-GPHDA T)。

(完整word版)《ARM嵌入式系统基础教程》期末试题

《ARM嵌入式系统基础教程》期末试题一、填空题(请将答案填入题后括号中):共10小题,每小题2分,满分20分。

1、一般而言,嵌入式系统的构架可以分为4个部分:处理器、(存储器)、输入/输出和软件,一般软件亦分为(操作系统)和应用软件两个主要部分。

2、根据嵌入式系统使用的微处理器,可以将嵌入式系统分为(嵌入式微控制器),嵌入式DSP,(嵌入式微处理器)以及片上系统。

3、操作系统是联接硬件与应用程序的系统程序,其基本功能有进程管理、(进程间通信)、(内存管理)、I/O资源管理。

4、从嵌入式操作系统特点可以将嵌入式操作系统分为实时操作系统和(分时操作系统),其中实时系统亦可分为(硬实时操作系统)和软实时系统。

5、内核负责管理各个任务,或者为每个任务分配CPU时间,并且负责任务之间的(通信),内核的基本服务是(任务调度)。

6、嵌入式开发一般采用(宿主机/目标机方式)方式,其中宿主机一般是指(PC机或者台式机)。

7、哈佛体系结构数据空间和地址空间(分开),ARM920T采用(哈佛体系)的内核架构。

8. ARM7TDMI采用(3)级流水线结构,ARM920TDMI采用(5)级流水线。

9 .按操作系统的分类可知,Dos操作系统属于顺序执行操作系统,Unix操作系统属于(分时)操作系统,VxWorks属于(实时嵌入式)操作系统。

10、ARM7TDMI中,T表示支持16位Thumb指令集,D表示(在片可调试),M表示内嵌乘法器Multiplier,I表示(嵌入式ICE),支持在线断点和调试。

二、选择题(请将答案填入题后括号中):共10小题,每小题2分,满分20分。

1、下面哪种操作系统不属于商用操作系统。

(B)A. windows xpB. LinuxC. VxWorksD. WinCE2. 下面哪点不是嵌入式操作系统的特点。

(C)A. 内核精简B. 专用性强C. 功能强大D. 高实时性3. 下面哪种不属于嵌入式系统的调试方法。

《嵌入式系统基础教程》第07讲第4章ARM存储器组织和异常中断习题

区域属性

l 有关区域的属性如下:

l 区域可以相互重叠 l 每一个区域有一个优先级,该优先级与分配给区域

的权限无关 l 当区域重叠时,具有最高优先权的区域的属性可以

参看ARM1136的方框图

2008年6月21日

《嵌入式系统基础教程》第07讲第4 章ARM存储器组织和异常中断习题

ARM966E-S核的TCM地址映射

2008年6月21日

《嵌入式系统基础教程》第07讲第4 章ARM存储器组织和异常中断习题

ARM966E-S的TCM别名地址空间

l 物理存储块可以 通过TCM接口映 射在片内的TCM 存储区

l 对于不需要PU的嵌入式系统而言,PU简化了硬件和 软件,主要表现在不使用转换表,这样免去了硬件遍 历转换表和软件建立与维护转换表。

2008年6月21日

《嵌入式系统基础教程》第07讲第4 章ARM存储器组织和异常中断习题

保护单元的工作原理和作用

l ARM核的PU使用区域(region)来管理系统保护。 区域是一个存储空间相关联的一组属性,处理器 核将这些属性保存在协处理器CP15的一些寄存器 里,并用0-7的号码标识每一个区域(它也是一个 具有特定属性的逻辑存储空间)。

ARM966E-S的TCM特点接口(续2)

The ARM966E-S processor contains a TCM controller that:

◇ schedules requests to the TCM interface ◇ handshakes with the ARM966E-S memory system

l 区域的存储边界通过两个属性进行配置:起始地 址和大小。

l 区域的大小可以是4KB~4MB的任何2的乘幂。

ARM嵌入式系统基础教程-第二版-不完整答案

第一周作业1写出下列英文简称对应的中文含义答MMR 存取DSP的寄存器PDA 个人数字助理DSP 嵌入式数字信号处理器EMPU 嵌入式微处理器MCU 微控制器SoC 片上系统RTOS 实时操作系统ISR中断服务子程序2 什么是嵌入式系统,有什么特点?答嵌入式系统:嵌入到对象体系中的专用计算机应用系统特点:嵌入性,内含计算机,专用性4 IEEE的实时UNIX分委会认为实时操作系统应具备哪些特点?答1,异步的事件响应2,切换时间和中断延时时间确定3,优先级中断和调度4,抢占式调度5,内存锁定6连续文件7同步5 前后台系统的概念答对于基于芯片开发来说应用程序一般是一个无限的循环,可称为前后台系统6 非占先式内核和占先式内核工作时有何不同答1非占先式内核要求每个任务自我放弃CPU的所有权,非占先式调度法耶称作合作型多任务,每个任务彼此合作共享一个CPU,异步事件还是由中断服务来处理,中断服务也可以使一个高优先级的任务由挂起状态变为就绪状态.但中断服务以后,控制权还是回到原来被中断了的那个任务,直到该任务主动放弃CPU的使用权时,高优先级的任务才能获得CPU的使用权。

2对于占先式内核,最高优先级的任务一旦就绪,总能得到CPU的控制权。

当一个运行着的任务使一个比它优先级高的任务进入了就绪状态,当前任务的CPU使用权就被剥夺了,那个高优先级的任务立刻得到了CPU的控制权。

7名词解释资源:程序运行时可使用的软,硬件环境。

共享资源:可以被一个以上任务使用的资源代码临界区:指处理时不可分割的代码,运行这些代码不允许被打断任务:一个任务也称为一个线程,是一个简单的程序内核:多任务系统中,内核负责管理各个任务,或者说每个任务分配CPU时间,并且负责任务之间的通信调度:调度是内核的主要职责之一,调度就是决定该轮到哪个任务运行了。

第二章作业1 ARM内核采用什么体系结构?ARM体系结构有什么特性?答ARM内核采用精简指令集计算机(RISC)体系结构。

嵌入式系统原理及应用 第四章习题

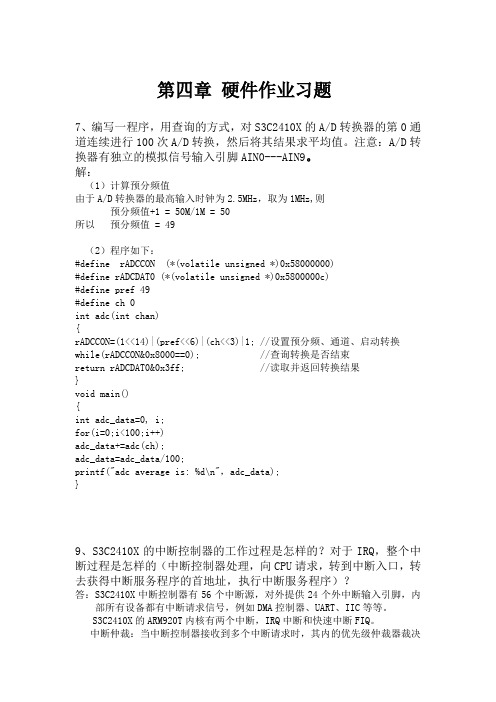

第四章硬件作业习题7、编写一程序,用查询的方式,对S3C2410X的A/D转换器的第0通道连续进行100次A/D转换,然后将其结果求平均值。

注意:A/D转换器有独立的模拟信号输入引脚AIN0---AIN9。

解:(1)计算预分频值由于A/D转换器的最高输入时钟为2.5MHz,取为1MHz,则预分频值+1 = 50M/1M = 50所以预分频值 = 49(2)程序如下:#define rADCCON (*(volatile unsigned *)0x58000000)#define rADCDAT0 (*(volatile unsigned *)0x5800000c)#define pref 49#define ch 0int adc(int chan){rADCCON=(1<<14)|(pref<<6)|(ch<<3)|1; //设置预分频、通道、启动转换while(rADCCON&0x8000==0); //查询转换是否结束return rADCDAT0&0x3ff; //读取并返回转换结果}void main(){int adc_data=0, i;for(i=0;i<100;i++)adc_data+=adc(ch);adc_data=adc_data/100;printf("adc average is: %d\n",adc_data);}9、S3C2410X的中断控制器的工作过程是怎样的?对于IRQ,整个中断过程是怎样的(中断控制器处理,向CPU请求,转到中断入口,转去获得中断服务程序的首地址,执行中断服务程序)?答:S3C2410X中断控制器有56个中断源,对外提供24个外中断输入引脚,内部所有设备都有中断请求信号,例如DMA控制器、UART、IIC等等。

S3C2410X的ARM920T内核有两个中断,IRQ中断和快速中断FIQ。

嵌入式系统的异常和中断

大多数嵌入式处理器体系结构提供异常和中断机制,允许处理器中断正常的执行路径。

这个中断可能有应用软件有意的触发,或者由一个错误的、不寻常的条件或某些非计划的外部事件触发。

许多实时操作系统提供处理异常和中断的封装器功能,以便保护嵌入式系统开发者避开低层的细节。

这种应用编程层允许程序员把精力集中在必须处理的高层异常处理上,而不是在处理那些冗长的序言和结束语的系统层次上。

然而,当程序员从一个嵌入式应用程序员过渡到一个嵌入式系统程序员的时候,这种隔离可能产生误会并且变成一种障碍。

一、什么是异常和中断一个异常是指任何打断处理器正常执行,并且迫使处理器进入一个由有特权的特殊指令执行的事件。

异常可以分为两类:同步异常和异步异常。

由内部事件(像处理器指令运行产生的事件)引起的异常称为同步异常。

同步异常的例子包括下列各项:1.在某些处理器体系结构中,对于确定的数据尺寸必须从内存的偶数地址进行读和写操作。

从一个奇数内存地址的读或写操作将引起存储器存取一个错误事件并引起一个异常(称为校准异常)。

2.造成被零除的算术运算引发一个异常。

由外部事件(与处理器指令执行不相关的事件)引发的异常,称为异步异常。

一般,这些外部事件与硬件信号相关。

这些硬件信号典型的来源于外部硬件装置。

异步异常的例子包括下列各项:1.按下嵌入式板上的复位按钮,触发一个异步的异常(称为系统复位异常)。

2.另外一个外部设备的例子是,通信处理器模块已经成为许多嵌入式设计的一个完整部分,当它接收数据包时引发异步异常。

一个中断,有时称为一个外部中断,是一个由外部硬件装置产生的事件引起的异步异常。

中断是异常的一类。

中断区别于其它类型的异常,或更精确地说,同步异常区别于异步异常的地方是事件的来源。

同步异常事件是由于执行某些指令而从处理器内部产生的。

而异步异常事件的来源是外部硬件装置。

异常和中断是大多数嵌入式系统中必须存在的精灵。

这个设施是处理器体系结构特定的;如果误用,将成为混乱的设计源。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2008年6月21日

南京大学计算机系

14

ARM966E-S的TCM接口特点(续1)

The features of the TCM interface include:

◇ independent ITCM and DTCM sizes of 0KB or 1KB64MB in power-of-two increments

参看下图,抽象成一个呈金字塔型的存储结构 注重研究第2层

寄存器 片内Cache,写缓存,TCM,片内SRAM

板卡级SRAM,DRAM和SDRAM NOR型和NAND型闪速存储器 硬盘驱动器、光盘驱动器

速

容

度

量

加

增

快

大

2008年6月21日

南京大学计算机系

5

4.6.3 片上存储器的用法

多数ARM处理器芯片内部集成了存储器

2008年6月21日

南京大学计算机系

6

片上存储器用作紧耦合存储器

紧耦合存储器的英文原文如下:

Tightly Coupled Memory,TCM

弥补Cache访问的不确定性而增加的片上存储器。

除了片上紧耦合存储器外,还有紧耦合存储器接 口,它能够提供低延时的外存储器访问。

有的处理器含有分立的指令TCM和数据TCM。 TCM包含在存储器地址映射空间中,可以作为快 速存储器来访问。除了不得包含读敏感地址之外, 对TCM接口上连接的存储器类型没有其他限制。 TCM使用物理地址,对TCM的写访问受到MMU 内部保护信息的控制。

2008年6月21日

南京大学计算机系

9

Cortex-R4F方框图—含TCM接口

注意图的右 侧含有一个 TCM仲裁 和接口模块

2008年6月21日

南京大学计算机系

10

ARM1136的TCM支持DMA传输

参看ARM1136的方框图

2008年6月21日

南京大学计算机系

11

ARM966E-S核的TCM地址映射

The ARM966E-S processor contains a TCM controller that:

◇ schedules requests to the TCM interface ◇ handshakes with the ARM966E-S memory system

2008年6月21日

南京大学计算机系

12

ARM966E-S的TCM别名地址空间

物理存储块可以 通过TCM接口映 射在片内的TCM 存储区

2008年6月21日

南京大学计算机系

13

ARM966E-S的TCM特点

The ARM966E-S processor supports both instruction and data TCMs. You can use the DTCM and ITCM to store real-time and performance-critical code. The TCMs are instantiated externally to the ARM966E-S macrocell providing for flexibility in the design of the memory subsystem. The system designer can select memory type and optimize the memory subsystem for power or s大学计算机系

2

4.6 ARM存储器组织

介绍以下内容:

数据类型和存储格式 ARM的存储体系 片上存储器的用法 协处理器CP15 存储器管理单元MMU 保护单元 快速上下文切换扩展 写缓存器(Write Buffer) ARM的异常中断向量表和异常中断处理与返回

2008年6月21日

南京大学计算机系

7

TCM在ARMv6处理器核的位置

ARMv6处理器包括:ARM1136J-S、ARM1156T2

2008年6月21日

南京大学计算机系

8

片内的TCM存储器

ARM926EJ-S核心内置32KB指令缓存、16KB 数字缓存和8KB数据-TCM(紧密耦合内存) 和8KB指令-TCM(紧密耦合内存);

◇ variable TCM wait state control for ITCM and DTCM

◇ ability to indicate sequential and nonsequential accesses.

2008年6月21日

南京大学计算机系

15

ARM966E-S的TCM特点接口(续2)

2008年6月21日

南京大学计算机系

3

4.6.1 数据类型和存储格式

ARM存储器中的数据类型有6种

有符号数

8位(字节)、16位(半字)、32位(字)

无符号数

8位(字节)、16位(半字)、32位(字)

缺省端序设置为小端序

2008年6月21日

南京大学计算机系

4

4.6.2 ARM的存储体系

它们统称为片上存储器

用途有:片上Cache、片上SRAM、紧耦合存储 器(TCM) 、写缓存

片上存储器的存储空间可以通过指令进行配置, 定义成片上Cache,或者片上SRAM,或者一部分 片上Cache加一部分片上SRAM。

紧耦合存储器和写缓存均需要编程使能或者硬件 接线使能

按照具体应用情况决定片上存储器配置方法

《嵌入式系统原理与开发》

2008年春季

第7讲

南京大学计算机系 俞建新主讲

2008年6月21日

南京大学计算机系

1

第4章ARM体系结构

本章主要介绍以下内容:

ARM体系结构版本 ARM处理器系列 ARM流水线 ARM工作模式和工作状态 ARM寄存器组织 ARM存储器组织 ARM的异常中断 AMBA和ARM7TDMI

◇ software visibility and programmability of TCM size and enable

◇ boot control for ITCM

◇ data access to the ITCM for literal pool accesses in code

◇ simple SRAM-style interface supporting both reads and writes