嵌入式系统数据共享存储器的实现

嵌入式系统课后答案

嵌⼊式系统课后答案嵌⼊式系统2011作业(⾮标准答案,仅供参考)第1章嵌⼊式系统概述 1、什么是嵌⼊式系统?答:嵌⼊式系统指的是以应⽤为中⼼和以计算机技术为基础的,并且软硬件是可裁剪的,能满⾜应⽤系统对功能、可靠性、成本、体积、功耗等指标严格要求的专⽤计算机系统。

3、根据嵌⼊式系统的复杂程度,嵌⼊式系统可分为哪4类?答:1:单个微处理器;2:嵌⼊式处理器可扩展的系统; 3:复杂的嵌⼊式系统; 4:在制造或过程控制中使⽤的计算机系统。

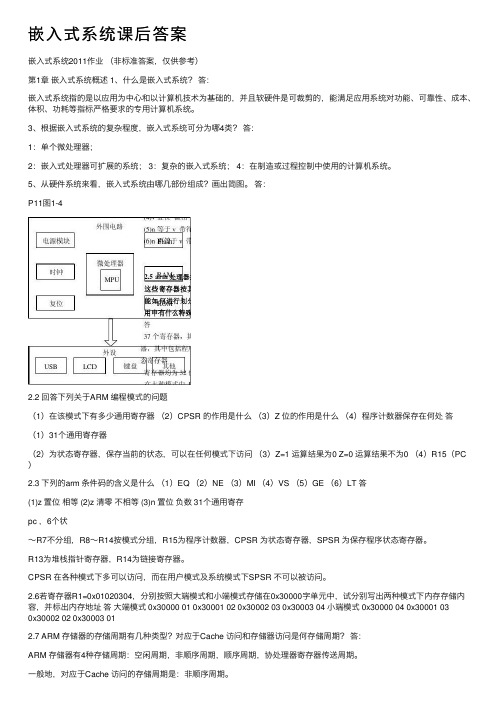

5、从硬件系统来看,嵌⼊式系统由哪⼏部份组成?画出简图。

答:P11图1-42.2 回答下列关于ARM 编程模式的问题(1)在该模式下有多少通⽤寄存器(2)CPSR 的作⽤是什么(3)Z 位的作⽤是什么(4)程序计数器保存在何处答(1)31个通⽤寄存器(2)为状态寄存器,保存当前的状态,可以在任何模式下访问(3)Z=1 运算结果为0 Z=0 运算结果不为0 (4)R15(PC)2.3 下列的arm 条件码的含义是什么(1)EQ (2)NE (3)MI (4)VS (5)GE (6)LT 答(1)z 置位相等 (2)z 清零不相等 (3)n 置位负数 31个通⽤寄存pc ,6个状~R7不分组,R8~R14按模式分组,R15为程序计数器,CPSR 为状态寄存器,SPSR 为保存程序状态寄存器。

R13为堆栈指针寄存器,R14为链接寄存器。

CPSR 在各种模式下多可以访问,⽽在⽤户模式及系统模式下SPSR 不可以被访问。

2.6若寄存器R1=0x01020304,分别按照⼤端模式和⼩端模式存储在0x30000字单元中,试分别写出两种模式下内存存储内容,并标出内存地址答⼤端模式 0x30000 01 0x30001 02 0x30002 03 0x30003 04 ⼩端模式 0x30000 04 0x30001 030x30002 02 0x30003 012.7 ARM 存储器的存储周期有⼏种类型?对应于Cache 访问和存储器访问是何存储周期?答:ARM 存储器有4种存储周期:空闲周期,⾮顺序周期,顺序周期,协处理器寄存器传送周期。

嵌入式系统的数据存储与管理方法

嵌入式系统的数据存储与管理方法随着技术的发展,嵌入式系统在各个领域中应用越来越广泛。

在嵌入式系统中,数据存储和管理是至关重要的一环。

嵌入式系统通常具有资源有限、功耗低、体积小等特点,因此,为实现高效的数据存储和管理,需要采用合适的方法和技术。

数据存储是嵌入式系统中必不可少的一部分。

在嵌入式系统中,数据可以分为两类:临时数据和持久数据。

临时数据通常存储在内存中,用于临时计算、传输和处理。

而持久数据通常存储在非易失性存储器(如闪存)中,以便断电后能够保持数据的一致性和完整性。

因此,在设计嵌入式系统时,需要结合存储器的种类和特性,选择合适的数据存储方案。

对于临时数据的存储和管理,嵌入式系统通常采用堆栈、队列、缓冲区等数据结构来存储和组织数据。

堆栈是一种后进先出(LIFO)的数据结构,适用于需要保持数据顺序的情况,如函数调用和中断处理。

队列是一种先进先出(FIFO)的数据结构,适用于需要按顺序处理数据的情况,如任务调度和消息传递。

缓冲区则是一种在内存中分配一定大小的空间,用于临时存储输入和输出数据。

通过合理地使用这些数据结构,可以高效地存储和管理临时数据。

对于持久数据的存储和管理,嵌入式系统通常使用闪存作为主要的存储介质。

闪存具有非易失性和高速度的特点,适用于嵌入式系统中需要长期存储和频繁访问的数据。

在进行数据存储和管理时,有几个关键的方面需要考虑。

首先,需要考虑数据的持久性和可靠性。

对于重要的数据,需要采用一定的容错机制来保证数据的完整性和可靠性。

常见的方法包括数据镜像、备份和恢复机制等。

其次,需要考虑数据的访问效率。

因为嵌入式系统的资源有限,对数据的读写需要尽可能地高效。

可以采用缓存技术、预取技术和索引技术等手段来提高数据的存取速度和效率。

此外,还需要考虑数据的安全性。

嵌入式系统中可能包含一些敏感数据,如密码、用户信息等,因此需要采取一定的安全措施,如数据加密、权限控制等,来保护数据的安全。

最后,对于嵌入式系统中大规模数据存储和管理的需求,可以考虑使用文件系统。

m2m技术原理

m2m技术原理M2M技术(Machine-to-Machine)指机器与机器之间自主通信的技术。

通过M2M技术,不同的设备和系统之间可以进行有效的数据交换和通信。

M2M技术也可以实现设备之间的协同工作,提高生产效率和产品质量。

M2M技术不仅应用于工业制造和物流领域,也在智能家居、健康监测、车联网等领域得到广泛应用。

下面将详细介绍M2M技术的原理和实现方法。

一、 M2M技术的原理M2M技术的基本原理是通过数据传输实现设备之间的自主通信。

实现M2M的关键是建立起设备之间的数据通信链路。

需要解决的问题包括数据的传输方式、通信协议、数据安全等问题。

1. 数据传输方式数据传输是实现M2M的关键技术之一。

常见的数据传输方式包括有线传输、无线传输和蓝牙传输等。

有线传输是指使用电缆或光纤等物理介质将数据传输到目的设备。

无线传输是指通过无线电波传输数据。

蓝牙传输是指通过蓝牙技术实现数据传输。

各种数据传输方式各有优劣,根据应用场景的需求进行选择。

2. 通信协议通信协议是实现M2M的另一个重要因素。

通信协议决定了数据传输的格式和通信方式。

不同的设备使用不同的通信协议会导致通信失败。

在实现M2M技术时,需要选择适用于不同设备的通信协议,同时修改协议以满足具体应用要求。

3. 数据安全由于M2M技术涉及大量敏感数据的传输,数据安全是其实现过程中的关键问题。

正确选择数据加密算法和合适的安全协议可以有效保护数据的传输和存储安全。

定期更新系统的安全策略和应急预案可以最大程度的提高数据安全性。

M2M技术的实现包括设备的接入、数据的传输和数据的处理等步骤。

下面将详细介绍这些步骤的实现方法。

1. 设备接入设备接入是指将各个设备接入到M2M环境中,实现设备的互联互通。

设备接入需要先确定设备的类型,然后选择适合该设备的接口和协议,通过配置运行参数等方式将设备连接到M2M系统中。

设备的接口和协议需要根据设备的功能和特性进行选择,同时要保证各个设备的接口和协议能够互相兼容,实现数据的共享和交换。

基于嵌入式软件控制器的多进程数据共享技术

w n a r :f a ii t ,f x bl ,s b l ,e tn ii t d f e dy u e ne f e tp vd l e s ig f t e e b l e us s i l iit y e i y t it a i y x e s l a r n l s r i tr b i n y i c a .I r i e a a y o s l w y frt e r e st n g AN e —s r g a t t a d c n b rc c l s d i c o l ,c l g d a s r o ma a e[ o h i wb u f c vy n a e pa t al u e n s h os ol e a n i i i i y es n

关键词:网络管理及监控系统 ; 嵌入式软件控制器 ; 内存映射文件 ; 共享节

on m ut l i—t r a e a a — s a i g t c n l g a e n h e d dd t h rn e h o o y b s d o e b d e o t r o tol r m e d d s fwa e c n r l e

i r a C + i id w p rt y tm .I r e o s le t e I I eo s d t n Vi u l t + n W n o s o e ai s se g n n o d r t ov h un ru aa— s a n rb e f l hr i g p o lms o mu d h e d d s s m ,N l t ra e y t e MMS s c e s l e eo e n e b d e f ae c nr l ru ig me r p  ̄ u c s f l d v lp d a m e d d s t r o t l sI mo y ma p u y o w oe l tc n lg d s c e s l t e e p c e e u rme t .B s d Ol o u h t e rq i m n n y i ,s s e h oo y a u c sf l me x e td rq i n u y h t e ns a e i t r g e ur e t a s o h h e a l s y—

嵌入式单片机三种应用程序架构

嵌入式单片机三种应用程序架构嵌入式单片机是一种集成了处理器、存储器、输入输出接口等功能的微型计算机系统,广泛应用于各种电子设备中。

针对不同的应用需求,嵌入式单片机可以采用不同的应用程序架构。

下面将介绍三种常见的嵌入式单片机应用程序架构,包括单任务、多任务和事件驱动架构。

一、单任务架构在单任务架构下,嵌入式单片机只能执行一项任务,也就是一次只能处理一个事件。

程序代码是按照顺序执行的,没有并行处理的能力。

在单任务架构下,主程序中通常包含一个主循环,通过循环不断地检测各种外部事件的发生并作出相应的处理。

例如,一个简单的嵌入式系统可能需要周期性地读取传感器数据并进行处理,然后将处理结果输出到显示屏上。

单任务架构的优点在于编程简单,逻辑清晰,适用于单一功能较简单的场景。

同时,由于不需要考虑并行处理的复杂性,系统资源的管理也相对简单。

然而,单任务架构的缺点在于不能同时进行多个任务处理,效率较低,且无法处理实时性要求较高的应用场景。

二、多任务架构多任务架构是一种支持多个任务并发执行的应用程序架构。

在多任务架构下,嵌入式单片机可以同时处理多个任务,提高系统的处理效率。

每个任务都有自己的代码段和数据段,并且任务之间可以实现相互通信和数据共享。

实现多任务的方法有多种,最常见的是利用操作系统的支持。

操作系统可以为每个任务分配独立的时间片,并负责任务的切换和调度。

常见的嵌入式操作系统有uc/OS、FreeRTOS等。

多任务架构的优点在于可以提高系统的并发处理能力,适用于多任务、复杂功能的应用场景。

同时,多任务架构可以实现任务间的相互独立,提高系统的可维护性和可重用性。

然而,多任务架构在设计和开发过程中需要考虑任务间的调度、通信、同步等问题,复杂度较高。

三、事件驱动架构事件驱动架构是一种基于事件触发的应用程序架构。

在事件驱动架构下,嵌入式单片机依据外部事件的发生而作出相应的响应,而非简单的按序执行代码。

事件可以是外部信号(如按键输入、传感器数据等)、定时器中断、通信中断等。

嵌入式系统实验一 存储器实验

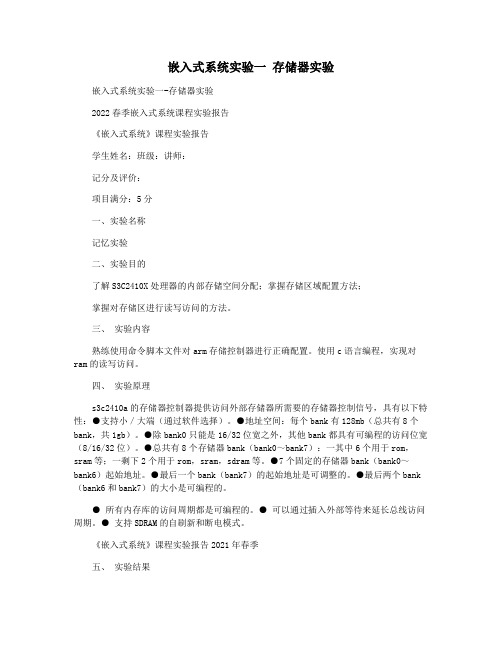

嵌入式系统实验一存储器实验嵌入式系统实验一-存储器实验2022春季嵌入式系统课程实验报告《嵌入式系统》课程实验报告学生姓名:班级:讲师:记分及评价:项目满分:5分一、实验名称记忆实验二、实验目的了解S3C2410X处理器的内部存储空间分配;掌握存储区域配置方法;掌握对存储区进行读写访问的方法。

三、实验内容熟练使用命令脚本文件对arm存储控制器进行正确配置。

使用c语言编程,实现对ram的读写访问。

四、实验原理s3c2410a的存储器控制器提供访问外部存储器所需要的存储器控制信号,具有以下特性:●支持小/大端(通过软件选择)。

●地址空间:每个bank有128mb(总共有8个bank,共1gb)。

●除bank0只能是16/32位宽之外,其他bank都具有可编程的访问位宽(8/16/32位)。

●总共有8个存储器bank(bank0~bank7):一其中6个用于rom,sram等;一剩下2个用于rom,sram,sdram等。

●7个固定的存储器bank(bank0~bank6)起始地址。

●最后一个bank(bank7)的起始地址是可调整的。

●最后两个bank (bank6和bank7)的大小是可编程的。

● 所有内存库的访问周期都是可编程的。

● 可以通过插入外部等待来延长总线访问周期。

● 支持SDRAM的自刷新和断电模式。

《嵌入式系统》课程实验报告2021年春季五、实验结果超级终端上显示一下信息:六、练习编写程序对sram进行字节的读写访问。

#包括\voidmemory_test(void){因蒂;uint16tdata;intmemerror=0;uint16t*pt;2022春季嵌入式系统课程实验报告uart_printf(\0x00e00000,_ram_startaddress+0x00f00000);pt=(uint16t*)(_ram_startaddress+0x00e0000);//记忆书写while((uint32t)pt<(_ram_startaddress+0x00f00000)){*pt=(uint16t)pt;pt++;}//memoryreaduart_uuuprintf(\memorytest(%xh-%xh):rd\\n\uuu内存_uuuu起始地址+0x00e00000,uuu内存_uuu起始地址+0x00f00000);pt=(uint16t*)(_ram_startaddress+0x00e00000);而((uint32t)pt<(_ram_startaddress+0x00f00000)){data=*pt;如果(数据!=(uint16t)pt){memerror=1;uart_uPrintf(\break;}pt++;}if(memerror==0)uart_printf(\}。

嵌入式系统双口存储器应用研究

Ap l ain r s a c fd a — o t a b s d o mb d e se p i t e e r ho u l r r m a e ne e d d s tm c o p y

F Qigh i Z ANG L i Y AN n —u , H e ANG F - n , umi

嵌入式系统双 口存储器应用研究

范庆辉 张 蕾 阳富 民 , ,

( 1 南科技 大学 电子信 息工程 学 院 ,河 南 洛 阳 4 10;2 河 703 .华 中科技 大学 计算机 学院 ,湖 北 武汉 4 07) 304

摘 要 : 含 多 C U 的嵌 入 式 系统 中, P 在 P C U之 间 的通讯和 数据 传输是 其重要 的组 成部 分。以数 字硬盘 录像机 ( R 为硬件 平 DV ) 台 , 简要 介 绍 D R系统 结构和硬 件设 计 的基 础上 , 过提 供双 口存储 器 的驱 动程序 对基 于双 口存储 器 的数 字信 号处理 器 在 V 通 ( P 与 C U之 间通讯 和数据 传输 进行 了研究 。通 过共 享双 口存 储 器的存储 单元 , DS ) P 有效地 实现 了DV R系统 中对 D P解码 过 S

程 的控 制 和 音 视 频 数 据 的 传 输 。

关 键 词 : 入 式 系 统 ; 数 字 视 频 录 像 机 ; 双 口 存 储 器 ; 驱 动 ; 数 字信 号 处 理 器 嵌

嵌入式系统的存储器管理技巧

嵌入式系统的存储器管理技巧嵌入式系统是一种专门设计用于特定应用领域的计算系统。

存储器管理在嵌入式系统设计中起着重要的作用,它对系统的性能和资源利用率有着直接影响。

本文将介绍几种常用的嵌入式系统存储器管理技巧,以帮助开发人员更好地设计和优化嵌入式系统。

一、存储器类型概述在嵌入式系统中,存储器通常分为内部存储器和外部存储器两类。

内部存储器通常指的是处理器内部的一级缓存和寄存器,速度较快但容量有限。

外部存储器则是指芯片外部连接的存储介质,如闪存、SDRAM等,容量较大但速度相对较慢。

二、存储器管理技巧1. 内存优化在嵌入式系统设计中,内存的使用非常关键。

为了最大限度地节省内存空间,可以采取以下几种优化技巧。

首先,合理使用数据结构和算法。

选择适合嵌入式系统的轻量级数据结构,如队列、链表等,可以减少内存的占用。

同时,合理选择算法,尽量减少临时变量的使用,减少内存的开销。

其次,进行代码优化。

嵌入式系统的代码大小对存储器的消耗是很大的,因此,合理使用编译器优化选项和去除不必要的代码可以有效减少存储器的使用量。

最后,灵活使用动态内存分配。

动态内存的分配和释放可以根据需要进行,避免不必要的内存占用。

但是需要注意内存泄漏和内存碎片的问题,以避免系统性能下降。

2. 外部存储器管理外部存储器在嵌入式系统中一般包括闪存、SDRAM等。

为了更好地管理外部存储器,可以采取以下技巧。

首先,合理规划存储器空间。

根据系统需求和资源限制,合理规划存储器的分布和使用,避免存储器空间的浪费。

可以采取分区、虚拟内存等技术进行管理。

其次,优化存储器读写操作。

外部存储器的读写速度相对较慢,在设计系统时要尽量减少存储器的读写次数,可采用缓存技术、预取技术等来优化存储器读写性能。

最后,采用压缩和加密技术。

为了提高存储器的利用率,可以采用数据压缩技术对存储的数据进行压缩,减少存储器的使用量。

另外,对敏感数据进行加密,确保数据的安全性。

3. 文件系统选择在嵌入式系统中,文件系统的选择也对存储器的管理起着重要作用。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

嵌入式系统数据共享存储器的实现Luo Hao (罗昊),Wang Zhihua (王志华)清华大学电子工程系北京 100084摘要:使用静态存储器(SRAM)和可编程逻辑器件(PLD)可以模拟共享存储器的行为,实现低成本、高速、大容量共享存储。

在实际应用中模拟共享存储器会遇到操作冲突的问题,这需要使用仲裁的办法加以解决。

正确选择SRAM和PLD能提高模拟共享存储器的速度。

关键字:共享存储器可编程逻辑嵌入式系统Implementation of Shared Memories in Embedded Systems Abstract: Use SRAM and PLD can simulate DPRAM to satisfy the need for high volume, high speed data switching. Collisions will arise when operate shared memory, some arbitration will be used to solve the problem. Select the right SRAM and PLD can improve the speed of the shared memory.Key word: DPRAM PLD EMBEDDED引言:有的嵌入式系统中需要使用共享存储器进行数据交换,常用的共享存储器有DPRAM (双口内存)、PRAM(多口内存)、FIFO等。

传统的DPRAM虽然简单易用,但是容量小,成本高。

使用SRAM和PLD可以方便地构成共享存储器。

1. 常见的双口内存在商用芯片中,常用的双口内存如IDT7133/4[1],容量为2K*16,异步操作,操作延迟时间20~90ns不等。

存储阵列通过左右两端的地址线独立寻址。

任意一端的接口方式与普通静态存储器完全一样。

每端有独立的片选、读出、写入信号,因为7133的数据宽度为16b,为了实现字节操作,还提供了字节读出使能,可以通过字节读出使能对其进行字节操作。

在实际的使用过程中,如果两侧同时对同一存储单元进行操作,任一侧为写入,都会使另一侧产生BUSY信号。

表示此时的操作无效,或是会出现不正常的结果。

在实际应用中这种情况是需要避免的。

2. 如何构造模拟双口内存如果在实际应用中遇到需要的双口内存容量远大于现有的双口内存的情形,可以使用多片双口内存并联的方案。

使用这种方案会使费用急剧增加,并且还需要增大存储控制器的扇出能力,增加的总线缓冲器或总线驱动器还会增加线路上的延时。

可以考虑使用一个替代的办法:使用一片或多片大容量静态存储器(SRAM)或动态存储器(DRAM)作为存储单元,使用一些外部逻辑生成两个端口,构成一个模拟双口内存。

使用类似操作双口内存的方法来操作这个模拟双口内存。

在文献[2]中有一个类似的方案,它使用SRAM实现共享存储。

图1中描绘了这种方案的实现方法。

存储阵列由SRAM构成,与SRAM操作相关的信号为数据总线,地址总线,读写控制和片选。

仲裁器由可编程逻辑实现,仲裁器的输入为两边端口送来的片选信号,读写控制信号,输出为控制存储阵列的片选及读写信号,送至处理器的等待信号和数据地址开关控制信号。

数据开关为双向三态开关,地址开关为单向三态开关。

理论上,数据和地址开关也可以集成到可编程器件中。

考虑到仲裁器的逻辑并不复杂,而数据和地址开关集成到仲裁器后,需要占用大量的可编程器件的I/O资源,从而需要选用容量较大的可编程器件。

这样会使得在实际应用中变得不太经济,所以数据地址开关采用外接的方案。

图1 模拟双口内存方案为叙述方便起见,现在两个端口分别命名为R端和L端。

理论上R端和L端是平等的,不存在任何优先的问题。

3. 基本原理当处理器需要对双口内存的一端进行读写时,将产生片选信号,仲裁器对这个片选信号进行仲裁,如果当前的状态可以允许对此端进行操作,仲裁器产生SRAM读写时序,并打开此端的数据地址开关。

从该端口写入或读出数据,如果条件不允许,仲裁器产生等待,通知处理器等待一段时间。

等待完毕后,再进行读写。

4. 如何处理冲突与双口内存不同的是,当在任一端对这个模拟双口内存进行操作,这个操作不论是读或是写,另一端都无法对这个模拟双口内存进行操作,如果正好在另一端需要对模拟双口内存进行操作,就会产生冲突,导致另一端无法立即写入或读出。

解决这个问题的有三个方法。

1、软件避免冲突保证任何时刻不会有两端同时操作模拟双口内存。

这可以再在这个模拟双口内存的基础上再附加一些处理器之间的握手。

当一端在进行操作时,另一端不操作。

这样做好好处是仲裁逻辑简单。

读写速度快。

缺点是,不能适用于某些需要实时交换数据的应用。

2、插入等待当R端需要操作模拟双口内存时,正好L端正在操作,这时可以在R端插入等待,让R 端等待一个或多个时钟周期,直到L端完成操作。

这在某些具有准同步总线的处理器上是可行的,如INTEL X86系列。

这种方式可优点是速度快,缺点是电路定时需要与处理器仔细匹配。

3、应答方式传输在任一端进行操作时,由仲裁器产生一个应答信号,告知处理器数据操作完毕。

如POWERPC处理器具有这样的传输方式。

比如当处理器需要在R端进行操作,而此时L端正在操作,仲裁器使R端的应答信号无效,一直等到L端操作完毕,并且完成R端的操作后,才送出R端操作完毕的应答信号,通知处理器操作完毕。

在这个应答的操作方式实际上隐含了等待。

能获得方式2的相同结果。

这种方法的优点是,可以以异步的方式传输数据。

实现的逻辑比较简单。

5. 仲裁机制如果模拟双口内存两端同时有操作请求,这时候会产生一个先后问题,根据不同的应用要求,可以采用固定优先级的仲裁机制,也可以采用轮流优先的仲裁机制。

6. 实现方法在这里应答方式传输避免冲突,固定仲裁优先级的方法实现模拟双口内存。

模拟双口内存的仲裁器使用两个有限状态机,分别命名为状态机0与状态机1。

状态机的时钟分别为各端的总线时钟,也就是说,两个状态机是异步的。

状态机之间依靠读取对方的状态进行通信。

如图2所示,每个状态机都有三个状态,依次为空闲态,请求态与忙态。

当复位时,两个状态机都进入空闲状态,当0端需要数据操作时,0端的片选信号变为有效,状态机0进入请求态,如果此时状态机1不处于忙态,则状态机0的下一状态为忙,否则重新进入闲态等待。

状态机在忙状态时对存储阵列进行操作。

操作完毕后等待片选信号变为无效重新进入空闲状态。

状态机1也以类似的方式运作,只是当状态机1在请求态时,因0端的优先级高,只有在状态机0为闲态时,才能进入忙态。

状态机在忙时产生存储器读写时序,并打开相应的数据和地址开关。

状态机0状态机1图2 模拟双口内存仲裁器状态机7. 具体电路在实际的电路中,存储阵列由2片NEC公司的U PD444012A,128K*16b 静态存储器构成,数据宽度为32b,总容量为512KB。

仲裁器使用了ALTERA公司EPM7032,数据开关和地址开关都使用74LVT16245三态双向缓冲器。

数据开关的方向使用写信号控制。

8. 仿真结果在MAX PLUS II中,对仲裁器进行仿真,仿真的结果如图3,从图中可以看出,不论是何端需进行数据操作,该端的CSxb有效(x为1或2),在确定的时间内能保证完成,并产生TAxb信号,作为与处理器的应答。

当两个CSxb同时有效即产生冲突时,仲裁器将按一定的先后顺序确保数据可靠传送。

在图中Taxb信号在无效时为高阻状态,这是为了适应处理器的总线操作的要求。

图3 模拟双口内存仿真结果9. 性能分析当总线时钟为66Mhz时,不发生冲突的情况下从一端读写一个数据需要的时间为:1个仲裁时钟 + 数据地址开关时延 + 存储器读写时延≈15 + 5 + 55 = 75ns也就是说无冲突时延为75ns。

发生冲突时,最坏的情况下读写一个数据需要的时间为:1个仲裁时钟+ 2 * 无冲突时延≈ 15 + 2*75 = 165ns在有冲突时,最坏的情况下需要有165ns才能读出或写入一个数据。

如果能提高总线时钟,可以减小仲裁期所占用的时间,如果选用速度更快的静态存储器,减少读写时间,有希望将最坏情况下的延时减小。

在表1中对双口内存和模拟双口内存作了一个比较表1 双口内存和模拟双口内存比较双口内存IDT7133 模拟双口内存备注速度 20ns~90ns 75ns~165ns2片32位容量 8KB 512KB成本≈100RMB≈100RMB10. 硬件测试应用模拟双口内存测试使用两块鑫微[3]MPC855T[4]标准板,模拟双口内存接在本地总线扩展口上,总线频率为60Mhz。

使用GPCM[4]与模拟双口内存接口。

MPC855T的Bootloader 为U-BOOT-1.0.2。

处理器相应的定时信息由U-BOOT完成,在U-BOOT监视命令行对模拟双口内存进行操作。

在一端使用存储器测试命令,对该端口进行不间断写入和读出,结果无误。

同时在另一端读出相应位置的模拟双口内存的内容。

结果也很正常。

说明读写冲突问题已经解决。

该硬件已在某型网络安全设备上得到应用,经长时间运行证明性能稳定可靠,达到了设计要求。

11. 结论在需要大容量快速数据交换的嵌入式系统中,为了获得较高的性价比,可以使用大容量静态存储器,配合一些外围逻辑实现本文所介绍的模拟双口内存。

模拟双口内存与嵌入式系统的接口方式跟常规的双口内存类似。

主要区别是需要在嵌入式硬件中处理冲突。

相同的思路也可以用于大容量的FIFO或多口内存。

12. 参考文献[1] HIGH-SPEED 2K x 16 CMOS DUAL-PORT STATIC RAMS [J/OE]IDT, Inc.[2] Implementing Shared Memory Interface with a TMS320C54x DSP [J/OE] TI co.[3] [4] MPC855T User’s Manual Integrated Communications Microprocessor freescale co.附录:CPLD代码(Verilog HDL)//--------------------------------------------------------------------------------------------------//// Title : ps_dpram// Design : ps_dpram// Author : Robert Luo// Company : Sinovee Microsystem////-------------------------------------------------------------------------------------------------//// File : ps_dpram.v// Generated : Thu Jan 29 15:38:15 2004//-------------------------------------------------------------------------------------------------//// Description :2 FSM be used to control each data operation// the state of each FSM as the input of the other FSM//-------------------------------------------------------------------------------------------------`timescale 1ps / 1psmodule ps_dpram ( DATAEN1b ,TA1b ,DATAEN2b ,TA2b ,CS1b ,CS2b ,RST1b ,ADEN1b ,RST2b ,CLK1 ,ADEN2b ,CLK2,//COLb,//OP1b,OP2b,DP1EN0b,DP1EN1b,DP1EN2b,DP1EN3b,DP2EN0b,DP2EN1b,DP2EN2b,DP2EN3b);input CS1b,CS2b,RST1b,RST2b,CLK1,CLK2 ;wire CS1b,CS2b,RST1b,RST2b,CLK1,CLK2 ;output DATAEN1b,TA1b,DATAEN2b,TA2b,ADEN1b,ADEN2b;output DP1EN0b,DP1EN1b,DP1EN2b,DP1EN3b;output DP2EN0b,DP2EN1b,DP2EN2b,DP2EN3b;reg DATAEN1b,DATAEN2b,ADEN1b,ADEN2b;tri TA1b,TA2b;tri DP1EN0b,DP1EN1b,DP1EN2b,DP1EN3b;tri DP2EN0b,DP2EN1b,DP2EN2b,DP2EN3b;wire DP1EN,DP2EN; //tri-state control of DP1ENb and DP2ENb;//output COLb; //OP1b,OP2b,//wire COLb; //OP1b,OP2b,reg TA1EN,TA2EN;reg bDATAEN1b,bDATAEN2b;reg CurState1,CurState2;parameter idle = 1'b0;parameter busy = 1'b1;//parameter op = 2'b10;parameter EN = 1'b0;parameter DIS = 1'b1;//counter signalsreg LOAD1,EN1;reg [3:0] CNTQ1;reg LOAD2,EN2;reg [3:0] CNTQ2;// State machine 1 //always @ (posedge CLK1 or negedge RST1b)beginif (RST1b == 1'b0)DATAEN1b = 1'b1; ADEN1b = 1'b1;TA1EN = 1'b1; CurState1 = idle; //COUNT CONTROL LOAD1 = 1'b0; EN1 = 1'b0; endelseif (CS1b == 1'b0) beginif ((CurState1 == idle) && (CurState2 != busy))beginCurState1 = busy;LOAD1 = 1'b1; EN1 = 1'b1;//ADEN1b = 1'b0;endelseif (CurState1 == busy) begin ADEN1b = 1'b0; LOAD1 = 1'b0; DATAEN1b = 1'b0; if (CNTQ1 == 1)TA1EN = 1'b0;if (CNTQ1 == 0)begin DATAEN1b = 1'b1; ADEN1b = 1'b1; TA1EN = 1'b1;CurState1 = idle;LOAD1 = 1'b0;EN1 = 1'b0;end end end end //State machine 2 //always @ (posedge CLK2 or negedge RST2b) beginif (RST2b == 1'b0)DATAEN2b = 1'b1; ADEN2b = 1'b1;TA2EN = 1'b1; CurState2 = idle; LOAD2 = 1'b0; EN2 = 1'b0; endelse if (CS2b == 1'b0) beginif ((CurState2 == idle) && (CurState1 != busy))beginCurState2 = busy;LOAD2 = 1'b1; EN2 = 1'b1; //ADEN2b = 1'b0; endelse if (CurState2 == busy && (CurState1 != busy))beginADEN2b = 1'b0; LOAD2 = 1'b0; DATAEN2b = 1'b0; if (CNTQ2 == 1)TA2EN = 1'b0;if (CNTQ2 == 0)begin DATAEN2b = 1'b1; ADEN2b = 1'b1; TA2EN = 1'b1;CurState2 = idle;LOAD2 = 1'b0;EN2 = 1'b0;end end elseCurState2 = idle;end endparameter CNTNUM = 4'b0011;//CNTNUM CAN BE CHANGED ACCORDING TO THE SRAM'S SPEED//COUNTER1always @ (posedge CLK1 or posedge LOAD1) beginif (LOAD1 == 1'b1)CNTNUM;=CNTQ1else if (EN1 == 1'b1)CNTQ1 = CNTQ1 - 1;end//COUNTER2always @ (posedge CLK2 or posedge LOAD2) beginif (LOAD2 == 1'b1)CNTNUM;=CNTQ2else if (EN2 == 1'b1)CNTQ2 = CNTQ2 - 1;endassign DP1EN = RST1b & ~DATAEN1b; assign DP2EN = RST2b & ~DATAEN2b;//assign OP1b = 1'b0;//assign OP2b = 1'b0;//assign COLb = CS1b | CS2b;assign TA1b = (TA1EN == 1'b0)? 1'b0 : 1'bZ; assign TA2b = (TA2EN == 1'b0)? 1'b0 : 1'bZ; assign DP1EN0b = (DP1EN == 1'b1)?1'b0 : 1'bZ; assign DP1EN1b = (DP1EN == 1'b1)?1'b0 : 1'bZ; assign DP1EN2b = (DP1EN == 1'b1)?1'b0 : 1'bZ; assign DP1EN3b = (DP1EN == 1'b1)?1'b0 : 1'bZ; assign DP2EN0b = (DP2EN == 1'b1)?1'b0 : 1'bZ; assign DP2EN1b = (DP2EN == 1'b1)?1'b0 : 1'bZ; assign DP2EN2b = (DP2EN == 1'b1)?1'b0 : 1'bZ; assign DP2EN3b = (DP2EN == 1'b1)?1'b0 : 1'bZ; endmodule。