VHDL语言设计4选1多路选择器讲解学习

实验五--4选1多路复用器和4位比较器设计与仿真

实验五 4选1多路复用器和4位比较器设计与仿真班级信息安全一班姓名邓一蕾学号2指导老师袁文澹一、实验目的1.熟悉QuartusⅡ仿真软件的基本操作,并用VHDL语言和逻辑图设计四选一多路选择器,4位比较器。

二、实验内容1.参照芯片74LS153的电路结构,用逻辑图和VHDL语言设计四选一多路复用器;2.从QuartusⅡ中取7485器件(比较器)进行仿真与分析;用VHDL语言设计4位比较器,接着进行仿真与分析,电路逻辑结构参照芯片74x85三.实验原理1.(1)四选一多路选择器逻辑电路的原理4选1多路选择器,GN为使能端,AB为选择通道控制端,c0,c1,c2,c3为数据输入端.Y为输出端。

当GN为1时,y=0;当GN为0,AB=00时,Y为c0的值;当GN为0,AB=01时,Y为c1的值;当GN为0,AB=10时,Y为c2的值;当GN为0,AB=11时,Y为c3的值;(2)通过实验实现逻辑的原理2.(1)4位比较器的逻辑电路图A0,B0,A1,B1,A2,B2,A3,B3为相比较数输入端,ALBI,AEBI,AGBI为级联输入端ALBO,AEBO,AGBO为比较输出端。

2)通过实验实现逻辑的逻辑功能表为四、实验方法与步骤实验方法:采用基于FPGA进行数字逻辑电路设计的方法。

采用的软件工具是QuartusII软件仿真平台,采用的硬件平台是Altera EPF10K20TI144_4的FPGA试验箱。

1.4选1多路选择器实验步骤:编写源代码。

打开QuartusⅡ软件平台,点击File中得New建立一个文件。

编写的文件名与实体名一致,点击 as以“.vhd”为扩展名存盘文件。

2、按照实验箱上FPGA的芯片名更改编程芯片的设置。

操作是点击Assign/Device,选取芯片的类型。

建议选“Altera的EPF10K20TI144_4”3、编译与调试。

确定源代码文件为当前工程文件,点击Complier进行文件编译。

四选一多路选择器

四选一选择器的VHDL程序实现及仿真一、四选一选择器的基本功能描述选择器常用于信号的切换,四选一选择器常用于信号的切换,四选一选择器可以用于4路信号的切换。

四选一选择器有四个输入端input(0)~ input(3),两个信号选择端a和b及一个信号输出端y。

当a、b输入不同的选择信号时,就可以使input(0)~ input(3)中某一个相应的输入信号与输出y端接通。

例如,当a=b=“0”时,input (0)就与y接通。

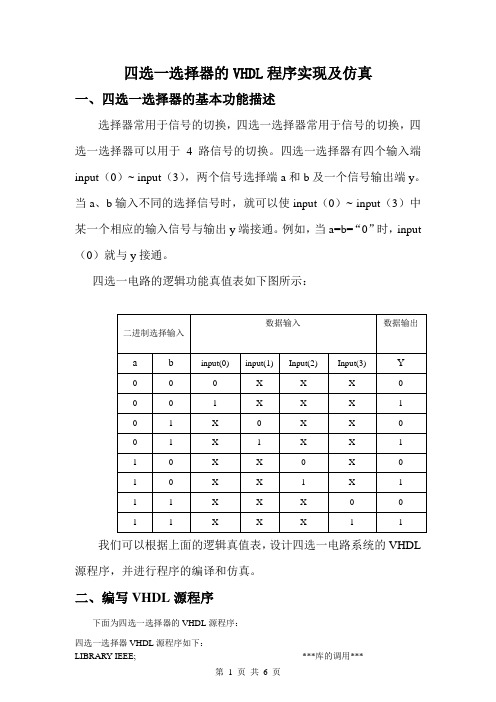

四选一电路的逻辑功能真值表如下图所示:我们可以根据上面的逻辑真值表,设计四选一电路系统的VHDL 源程序,并进行程序的编译和仿真。

二、编写VHDL源程序下面为四选一选择器的VHDL源程序:四选一选择器VHDL源程序如下:LIBRARY IEEE; ***库的调用***USE IEEE.STD_LOGIC_1164.ALL; ***库的调用***ENTITY mux4 IS ***实体定义*** PORT (input:IN STD_LOGIC_VECTOR(3 DOWNTO 0); ***输入管脚的定义***a,b:IN STD_LOGIC; ***输入管脚的定义***y:OUT STD_LOGIC ); ***输出管脚的定义***END mux4;ARCHITECTURE rtl OF mux4 IS ***结构的定义***SIGNAL sel:STD_LOGIC_VECTOR (1 DOWNTO 0); ***信号定义***BEGINsel<=b&a;PROCESS (input,sel) ***进程的定义***BEGINIF(sel="00") THENy<=input(0);ELSIF(sel<="01") THENy<=input(1);ELSIF(sel<="10") THENy<=input(2);ELSEy<=input(3);END IF;END PROCESS;END rtl;三、文本文件的编译及仿真全过程在编辑器中输入并保存了以上四选一选择器的VHDL源程序后就可以对它进行编译了,编译的最终目的是为了生成可以进行仿真、定时分析及下载到可编程器件的相关文件,如*.cnf,*.rpt,*.snf,*.pof 等。

4选1多路选择器VHDL语言设计

4选1多路选择器VHDL语言设计在VHDL语言中设计一个4选1多路选择器主要涉及到以下几个方面:实体声明、端口声明、内部信号声明、内部结构设计、行为建模以及仿真测试。

下面是一个VHDL语言设计的参考模板,详细解释了每个步骤的实现方法。

1. 实体声明(Entity Declaration)```vhdlentity mux_4to1 isportA, B, C, D : in std_logic;S : in std_logic_vector(1 downto 0);CLK : in std_logic;Y : out std_logicend mux_4to1;```2. 端口声明(Port Declaration)端口声明定义了输入和输出端口的类型。

在这个例子中,输入和输出端口的类型都是标准逻辑类型。

```vhdlarchitecture behavioral of mux_4to1 issignal input_mux : std_logic_vector(3 downto 0);beginA <= input_mux(0);B <= input_mux(1);C <= input_mux(2);D <= input_mux(3);end behavioral;```3. 内部信号声明(Internal Signal Declaration)内部信号声明是为了辅助模块内的信号传输和处理。

在这个例子中,我们需要声明一个内部信号来保存选择信号S对应的多路选择器输入信号。

```vhdlarchitecture behavioral of mux_4to1 issignal input_mux : std_logic_vector(3 downto 0);signal mux_out : std_logic;beginA <= input_mux(0);B <= input_mux(1);C <= input_mux(2);D <= input_mux(3);end behavioral;```4. 内部结构设计(Internal Structure Design)内部结构设计定义了多路选择器的逻辑结构。

实验二 四选一多路选择器的设计

实验二四选一多路选择器的设计姓名:庞啟明学号:1112120110 专业:自动化一、实验目的进一步熟悉QuartusⅡ的Verilog HDL文本设计流程,学习组合电路的设计、仿真和硬件测试。

二、实验原理if_else条件语句描述方式,以过程语句引导的顺序语句,适合描述复杂逻辑系统的行为描述语句。

(1)以模块定义语句关键词module_endmodule引导完整的电路模块。

(2)以input和output语句引导模块的外部端口。

(3)以reg等关键词定义模块内将出现的相关信息的特征和数据类型。

(4)以always @ 等关键词引导对模块逻辑功能描述的语句。

负责描述电路器件的内部逻辑功能和电路结构。

三、实验设备与软件平台实验设备:计算机、FPGA硬件平台是Cyclone系列FPGA软件平台:Quartus II 9.1 (32-Bit)、5E+系统四、实验内容编写Verilog程序描述一个电路,实现以下功能:具有6个输入端口 A、B、C、D、S1、SO,A、B、C、D均为输入端口,位宽为1;Sl、S0为通道选择控制信号端,位宽为1;Y为输出端口,位宽为1。

当S1S0为“00”时,A的数据从Y输出,S1S0为“01”时,B的数据从Y输出,S1S0为“10”时,C的数据从Y输出,S1S0为“11”时,D的数据从Y输出。

五、实验步骤设计流程:1、编辑和输入设计文件(1)、新建一个文件夹如D:\MUX41 ,本工程所有文件将存放在此目录中。

1)输入VHDL源程序打开QuartusII,选择菜单File->New。

选择Verilog HDL File,输入源程序。

2)文件存盘选择File->Save As命令,找到已设立的文件夹D:\MUX41,存盘文件名应与实体名一致,存盘为MUX41.v。

当出现语句“do you want to create…..”的对话框,选择“是”自动创建工程。

这里先选择“否”,即暂时不创建工程流程。

练习3_VHDL实现四选一的程序(选择信号)

课本P28-49

第五讲重点:

重点:1. 掌握VHDL语言的实体和结构体的描述。

(P30_P32)PORT端口说明。

(P31)

2. 熟悉库和程序包的说明语句。

(P33_P34)

例如:LIBRARY IEEE;

USE IEEE.std_logic_1164.all;

USE IEEE. STD_LOGIC_UNSIGNED.ALL;

USE IEEE. STD_LOGIC_SIGNED.ALL;

USE IEEE. STD_LOGIC_ARITH.ALL

3. 熟悉数据类型(P42-46)

BIT、BIT_VECTOR、STD_LOGIC、STD_LOGIC_VECTOR。

2. 熟悉信号赋值语句的用法(P57_P58)

(包括:并行信号赋值语句、条件信号赋值语句和选择信号赋值语句。

)

1、写出一位全加器电路(如下图)的实体和结构体描述。

(用并行信号赋值语句)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY IS

PORT ( );

END ;

ARCHITECTURE OF IS

BEGIN

S<=

Co<=

END ;

2、试写出8选1多路选择器的VHDL描述。

选择控制信号为s2,s1和s0,输入信号为i0~i7输出信号为y。

(要求分别用条件信号赋值和选择信号赋值语句)参考下面4选1多路选择器的VHDL描述

(1)用条件信号赋值语句

(2)用选择信号赋值语句

现。

2选1和4选1选择器VHDL设计

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY MUX41A IS PORT(a,b,c,d,s0,s1:IN STD_LOGIC;

y:OUT STD_LOGIC); END ENTITY MUX41A ; ARCHITECTURE BHV OF MUX41A IS SIGNAL S:STD_LOGIC_VECTOR(1 DOWNTO 0); BEGIN S <=S1 & S0; PROCESS(S1,S0) --敏感信号表中可以放s1、s0,也可直接放s,如(s) BEGIN CASE S IS WHEN "00" => y<=a; WHEN "01" => y<=b; WHEN "10" => y<=c; WHEN "11" => y<=d; WHEN OTHERS =>NULL; END CASE; END PROCESS; END BHV;

3.3 4选1多路选择器及其VHDL描述

3.1 多路选择器的VHDL描述

相关语法 1.IEEE库和1164程序包

在VHDL中也像很多高级语言一样,把常用的一些数据 类型,数据对象等事先定义好放在库和程序包中,供设计者 直接调用而不用定义。 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; 注意:一个典型的VHDL程序是由库和程序包,实体和结构 体三部分构成。

mux21a2

a

y

b

ቤተ መጻሕፍቲ ባይዱ

s

3.1 多路选择器的VHDL描述

相关语法

1.信号signal

VHDL语言设计四选一选择器

课程: 数字逻辑与数字系统VHDL语言设计四选一选择器实验报告系:电子信息与计算机科学系专业:自动化班级:文自112—2班姓名:桑*超学号: 2011905192**指导教师:徐红霞学年学期:2012-2013学年(第一学期)2012年12月15日姓名: 桑*超班级: 文自112-2班学号: 2011905192** 试验: VHDL语言设计日期:2012.12.15 指导老师: 徐洪霞一、实验报告的名称: VHDL语言设计二、本次实验的目的:1.掌握VHDL 语言的设计技巧2.用VHDL语言设计四选一选择器三、设计过程:1.工程编译源:用VHDL语言编程。

2.功能仿真:将功能编译后的结果进行仿真。

3.引脚锁定:将个信号按要求分配到相应引脚.4.物理实现:将结果下载到所悬着的器件中四、写出源程序,画出防真波形图.library ieee;use ieee.std_logic_1164.all;entity mux4_1 isport( a,b,c,d : in std_logic;s : in std_logic_vector(1 downto 0);z : out std_logic );end mux4_1;architecture one of mux4_1 isbeginprocess(s,a,b,c,d)begincase s iswhen "00"=>z<=a;when "01"=>z<=b;when "10"=>z<=c;when "11"=>z<=d;when others =>z<=null;end case;end process;end one ;波形仿真图:五、实验总结,主要包括实验中所犯错误,怎样改正等1.在文件名必须与VHDL文件中的设计实体名保持一致。

实验一 四选一多路选择器的设计与仿真

实验内容:

1.根据课本

2.2.3节的内容在QuratusⅡ软件上完成与或非门电路的VHDL程序

设计与程序仿真(原理图输入及其仿真暂不作为本次实验的要求),首先请完全按照课本内容走通一遍,熟悉源程序输入与仿真的过程,然后分别尝试修改工程名、VHDL文件名、波形文件名,看看对编译、仿真会造成什么样的影响?

2.以顺序描述语句和并行描述语句两种方式分别实现一个4选1多路选择器(请

利用上节课讲到的多选择控制IF语句、WHEN_ELSE并行赋值语句独立编程实现),实体名必须以各人学号作为后缀,例如:学号为123456的同学,可命名实体名为my_mux41_456,学号_456不可缺少,前面部分my_mux41可依据个人习惯任意命名。

在波形仿真时请任意设置输入端的时钟周期、偏移量与占空比,以区别于其他同学的仿真结果。

实验报告中至少应包含源程序、工程名、VHDL文件名、波形图文件名,以及仿真波形的截图。

实验报告:

除上面提到的实验报告要点外,标准实验报告的其它构成要素是必须的,请各位同学自己组织语言完善报告内容。

实验报告的重点应体现各人独立完成实验的过程、对实验的归纳总结等,这也将是评分的重点。

本门课程作为专业选修课,实验成绩是总成绩的重要组成部分,最后将统一上交归档,因此请同学们认真对待,杜绝抄袭。

每次实验一周后,请各班班长派代表收齐实验报告在上课前一并交给我。

缓交、不交、抄袭等问题都将对评分构成影响。

参考资料:

实体表达

结构体表达

WHEN_ELSE条件信号赋值语句

进程语句

多选择控制IF语句

逻辑操作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

V H D L语言设计4选1多路选择器

4选1多路选择器的VHDL描述

要求:THEN语句和CASE语句实现4选1多路选择器,其中选择控制信号s1和s0的数据类型为STD_LOGIC_VECTOR;当s1=‟0‟,s0=‟0‟;s1=‟0‟,s0=‟1‟;s1=‟1‟,s0=‟0‟和s1=‟1‟,s0=‟1‟时,分别执行y<=a、y<=b、y<=c、y<=d。

一、解法1:用IF_THEN语句实现4选1多路选择器

(1)程序:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY mux41 IS

PORT (a,b,c,d: IN STD_LOGIC;

s0: IN STD_LOGIC;

s1: IN STD_LOGIC;

y: OUT STD_LOGIC);

END ENTITY mux41;

ARCHITECTURE if_mux41 OF mux41 IS

SIGNAL s0s1 : STD_LOGIC_VECTOR(1 DOWNTO 0);--定义标准逻辑位矢量数据BEGIN

s0s1<=s1&s0; --s1相并s0,即s1与s0并置操作

PROCESS(s0s1,a,b,c,d)

BEGIN

IF s0s1 = "00" THEN y <= a;

ELSIF s0s1 = "01" THEN y <= b;

ELSIF s0s1 = "10" THEN y <= c;

ELSE y <= d;

END IF;

END PROCESS;

END ARCHITECTURE if_mux41;

(2)编译的结果如下:

编译报告:

二、解法2:用CASE语句实现4选1多路选择器(1)程序:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY mux41 IS

PORT (a,b,c,d: IN STD_LOGIC;

s0: IN STD_LOGIC;

s1: IN STD_LOGIC;

y: OUT STD_LOGIC);

END ENTITY mux41;

ARCHITECTURE case_mux41 OF mux41 IS

SIGNAL s0s1 : STD_LOGIC_VECTOR(1 DOWNTO 0);--定义标准逻辑位矢量数据类型

BEGIN

s0s1<=s1&s0; --s1相并s0,即s1与s0并置操作

PROCESS(s0s1,a,b,c,d)

BEGIN

CASE s0s1 IS --类似于真值表的case语句

WHEN "00" => y <= a;

WHEN "01" => y <= b;

WHEN "10" => y <= c;

WHEN "11" => y <= d;

WHEN OTHERS =>NULL ;

END CASE;

END PROCESS;

END case_mux41;

(2)编译结果:

编译报告:。