四选一数据选择器源程序

四选一多路选择器

四选一选择器的VHDL程序实现及仿真一、四选一选择器的基本功能描述选择器常用于信号的切换,四选一选择器常用于信号的切换,四选一选择器可以用于4路信号的切换。

四选一选择器有四个输入端input(0)~ input(3),两个信号选择端a和b及一个信号输出端y。

当a、b输入不同的选择信号时,就可以使input(0)~ input(3)中某一个相应的输入信号与输出y端接通。

例如,当a=b=“0”时,input (0)就与y接通。

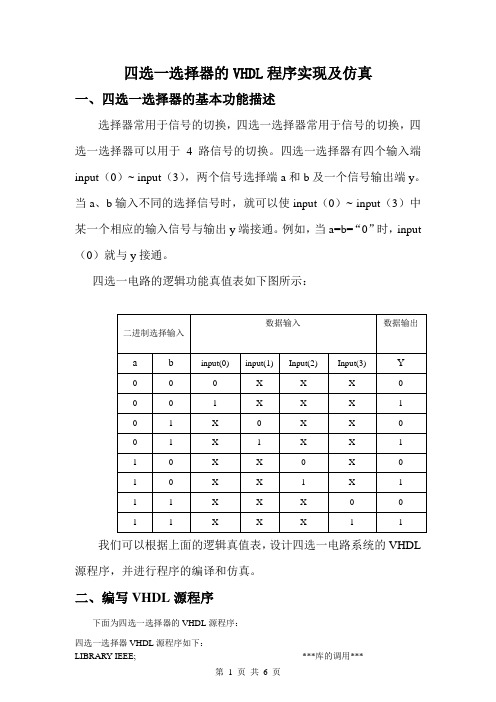

四选一电路的逻辑功能真值表如下图所示:我们可以根据上面的逻辑真值表,设计四选一电路系统的VHDL 源程序,并进行程序的编译和仿真。

二、编写VHDL源程序下面为四选一选择器的VHDL源程序:四选一选择器VHDL源程序如下:LIBRARY IEEE; ***库的调用***USE IEEE.STD_LOGIC_1164.ALL; ***库的调用***ENTITY mux4 IS ***实体定义*** PORT (input:IN STD_LOGIC_VECTOR(3 DOWNTO 0); ***输入管脚的定义***a,b:IN STD_LOGIC; ***输入管脚的定义***y:OUT STD_LOGIC ); ***输出管脚的定义***END mux4;ARCHITECTURE rtl OF mux4 IS ***结构的定义***SIGNAL sel:STD_LOGIC_VECTOR (1 DOWNTO 0); ***信号定义***BEGINsel<=b&a;PROCESS (input,sel) ***进程的定义***BEGINIF(sel="00") THENy<=input(0);ELSIF(sel<="01") THENy<=input(1);ELSIF(sel<="10") THENy<=input(2);ELSEy<=input(3);END IF;END PROCESS;END rtl;三、文本文件的编译及仿真全过程在编辑器中输入并保存了以上四选一选择器的VHDL源程序后就可以对它进行编译了,编译的最终目的是为了生成可以进行仿真、定时分析及下载到可编程器件的相关文件,如*.cnf,*.rpt,*.snf,*.pof 等。

实验一 FPGA VHDL四选一数据选择器的设计

实验设备:FPGA实验箱

拟用芯片:Altera EP3C55F484C8

3.实验设计

1)系统原理

根据4选1数据选择器的工作原理,有公式:

Y= + B+ C+ D

可见,要实现功能,需要6个输入,一个输出。其中 是数据选择端,A,B,C,D是数据输入端。由 输出高低电平(开关信号)பைடு நூலகம்定数据的输出和传送。

实验二四选一数据选择器的设计

1实验目的

(1)进一步熟悉和掌握QartusII的使用方法;

(2)掌握FPGA实验箱使用方法;

(3)学习和掌握电路原理图的设计流程

1.实验内容

使用QartusII的元件库,通过元件图的方式设计具有4选1功能的数据选择器,并使用FPGA实验箱对程序进行硬件下载,验证。

2.实验条件

L7=1,L8=开

L7=开,L8=开

发声频率

很慢

慢

较快

快

表2-1 开关不同位置时蜂鸣器发声状态

实验箱结果如图2-5所示

图2-5实验箱进行试验

5.心得体会

通过这次实验,让我学习到了如何在QartusII中使用原理图的方式做出所需要的功能器件。也学会了如何使用FPGA实验箱。

使用实验箱旁边的频率信号低的4个信号做输入信号,通过FPGA实验箱上的蜂鸣器发出的声音频率快慢来测试实验是否成功。

A输入接入1HZ信号B输入接入4HZ信号

C输入接入8HZ信号D输入接入16HZ

SO输入接入L8开关S1输入接入L7开关

Y输出接入蜂鸣器

可得实验结果如下表 表2-1所示

L7=关,L8=关

L7=关,L8=开

2)电路原理图

四选一数据选择器

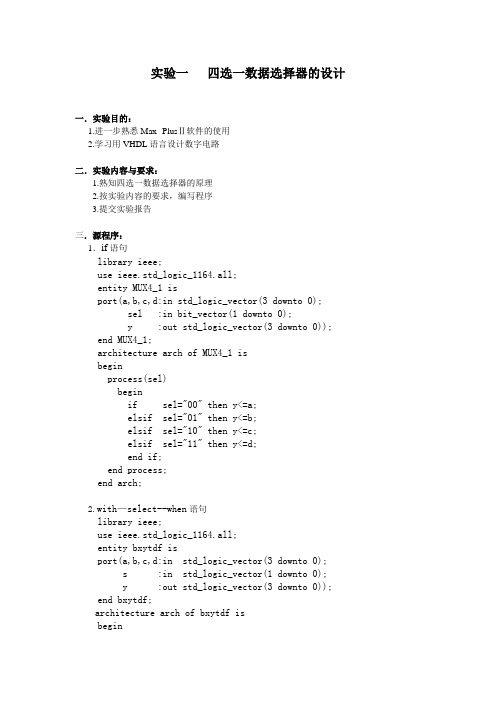

实验一四选一数据选择器的设计一.实验目的:1.进一步熟悉Max--PlusⅡ软件的使用2.学习用VHDL语言设计数字电路二.实验内容与要求:1.熟知四选一数据选择器的原理2.按实验内容的要求,编写程序3.提交实验报告三.源程序:1.if语句library ieee;use ieee.std_logic_1164.all;entity MUX4_1 isport(a,b,c,d:in std_logic_vector(3 downto 0);sel :in bit_vector(1 downto 0);y :out std_logic_vector(3 downto 0));end MUX4_1;architecture arch of MUX4_1 isbeginprocess(sel)beginif sel="00" then y<=a;elsif sel="01" then y<=b;elsif sel="10" then y<=c;elsif sel="11" then y<=d;end if;end process;end arch;2.with—select--when语句library ieee;use ieee.std_logic_1164.all;entity bxytdf isport(a,b,c,d:in std_logic_vector(3 downto 0);s :in std_logic_vector(1 downto 0);y :out std_logic_vector(3 downto 0));end bxytdf;architecture arch of bxytdf isbeginwith s selecty<=a when "00",b when "01",c when "10",d when "11",NULL when others;end arch;3. case语句LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY sy1 ISport(a,b,c,d:in std_logic_vector(3 downto 0);sel : in std_logic_vector(1 downto 0);y : out std_logic_vector(3 downto 0));END sy1;ARCHITECTURE arch OF sy1 ISBEGINPROCESS(sel)BEGINCASE sel ISWHEN "00"=>y<=a;WHEN "01"=>y<=b;WHEN "10"=>y<=c;WHEN "11"=>y<=d;WHEN OTHERS=>NULL;END CASE;END PROCESS;END arch;4.when--else语句library ieee;use ieee.std_logic_1164.all;entity Q4_1 isport(a,b,c,d:in std_logic_vector(3 downto 0);sel :in std_logic_vector(1 downto 0);y :out std_logic_vector(3 downto 0));end Q4_1;architecture arch of Q4_1 isbeginy<=a when sel="00" elseb when sel="01" elsec when sel="10" elsed;end arch;四.仿真波形图:1. if语句2.with—select--when语句3. case语句4.when--else语句。

EDA技术-VHDL-四选一数据选择器程序设计与仿真实验

EDA技术-VHDL-四选⼀数据选择器程序设计与仿真实验四选⼀数据选择器程序设计与仿真实验1 实验⽬的(1) 熟悉在QuartusⅡ软件平台上建⽴⼯作库⽂件和编辑设计⽂件的⽅法。

(2) 熟悉创建⼯程⽂件⽅法。

(3) 熟悉编译前设置和启动全程编译设置的⽅法。

(4) 熟悉波形编辑器的使⽤⽅法(5) 熟悉在QuartusⅡ软件平台上对设计进⾏仿真的操作全过程(6) 会⽤VHDL语⾔设计⼀个四选⼀数据选择器。

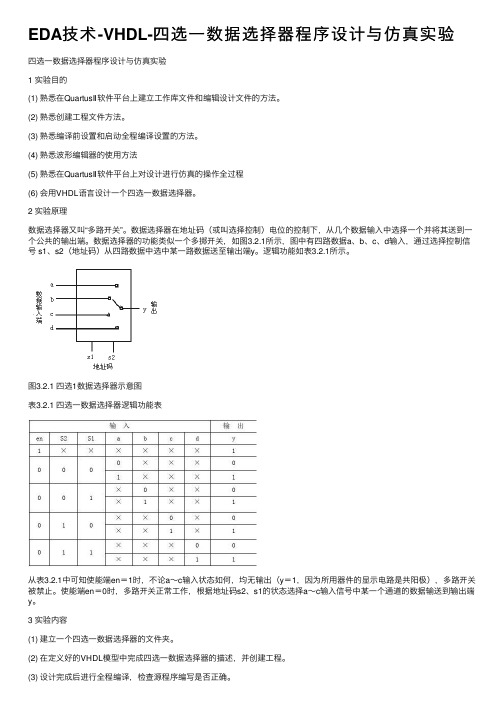

2 实验原理数据选择器⼜叫“多路开关”。

数据选择器在地址码(或叫选择控制)电位的控制下,从⼏个数据输⼊中选择⼀个并将其送到⼀个公共的输出端。

数据选择器的功能类似⼀个多掷开关,如图3.2.1所⽰,图中有四路数据a、b、c、d输⼊,通过选择控制信号 s1、s2(地址码)从四路数据中选中某⼀路数据送⾄输出端y。

逻辑功能如表3.2.1所⽰。

图3.2.1 四选1数据选择器⽰意图表3.2.1 四选⼀数据选择器逻辑功能表从表3.2.1中可知使能端en=1时,不论a~c输⼊状态如何,均⽆输出(y=1,因为所⽤器件的显⽰电路是共阳极),多路开关被禁⽌。

使能端en=0时,多路开关正常⼯作,根据地址码s2、s1的状态选择a~c输⼊信号中某⼀个通道的数据输送到输出端y。

3 实验内容(1) 建⽴⼀个四选⼀数据选择器的⽂件夹。

(2) 在定义好的VHDL模型中完成四选⼀数据选择器的描述,并创建⼯程。

(3) 设计完成后进⾏全程编译,检查源程序编写是否正确。

(4) 建⽴波形编辑⽂件并对输⼊波形进⾏编辑。

(5) 启动仿真器进⾏仿真,并分析仿真结果。

4 实验预习与思考(1) 进⼀步学习在QuartusⅡ软件平台上建⽴⼯作库⽂件和编辑设计⽂件的⽅法。

(2) 进⼀步学习建⽴波形编辑器⽂件编辑输⼊波形的⽅法。

(3) VHDL语⾔的结构体在整个程序中起什么作⽤。

5 VHDL仿真实验(1)新建⼀个⽂件夹。

本例中⽂件夹名为mux。

(2)输⼊源程序,打开计算机桌⾯上图标。

EDA实验报告(四选一、四位比较器、加法器、计数器、巴克码发生器)

EDA实验报告(四选一、四位比较器、加法器、计数器、巴克码发生器)EDA实验报告实验14选1数据选择器的设计一、实验目的1.学习EDA软件的基本操作。

2.学习使用原理图进行设计输入。

3.初步掌握器件设计输入、编译、仿真和编程的过程。

4.学习实验开发系统的使用方法。

二、实验仪器与器材1.EDA开发软件一套2.微机一台3.实验开发系统一台4.打印机一台三、实验说明本实验通过使用基本门电路完成4选1数据选择器的设计,初步掌握EDA设计方法中的设计输入、编译、综合、仿真和编程的过程。

实验结果可通过实验开发系统验证,在实验开发系统上选择高、低电平开关作为输入,选择发光二极管显示输出电平值。

本实验使用Quartus II 软件作为设计工具,要求熟悉Quartus II 软件的使用环境和基本操作,如设计输入、编译和适配的过程等。

实验中的设计文件要求用原理图方法输入,实验时,注意原理图编辑器的使用方法。

例如,元件、连线、网络名的放置方法和放大、缩小、存盘、退出等命令的使用。

学会管脚锁定以及编程下载的方法等。

四、实验要求1.完成4选1数据选择器的原理图输入并进行编译;2.对设计的电路进行仿真验证;3.编程下载并在实验开发系统上验证设计结果。

五、实验结果4选1数据选择器的原理图:仿真波形图:管脚分配:实验2 四位比较器一、实验目的1.设计四位二进制码比较器,并在实验开发系统上验证。

2.学习层次化设计方法。

二、实验仪器与器材1.EDA 开发软件 一套 2.微机 一台 3.实验开发系统 一台 4.打印机 一台 5.其它器件与材料 若干 三、实验说明本实验实现两个4位二进制码的比较器,输入为两个4位二进制码0123A A A A 和0123B B B B ,输出为M(A=B ),G (A>B )和L (A<B )(如图所示)。

用高低电平开关作为输入,发光二极管作为输出,具体管脚安排可根据试验系统的实际情况自行定义。

verilog4选一数据选择器原理(一)

verilog4选一数据选择器原理(一)Verilog中的4选1数据选择器简介在数字电路中,数据选择器是一种常见的电路组件,用于从多个数据输入中选择一个输出。

Verilog是一种硬件描述语言,广泛用于数字电路的设计和仿真。

本文将介绍Verilog中的4选1数据选择器的原理和实现方法。

原理4选1数据选择器有4个输入和1个输出。

根据选择信号,从4个输入中选择一个输入作为输出。

选择信号是2位的二进制数,共有4种可能的状态,每种状态对应一个输入。

当选择信号为00时,输出为第一个输入;当选择信号为01时,输出为第二个输入;当选择信号为10时,输出为第三个输入;当选择信号为11时,输出为第四个输入。

逻辑电路图以下是4选1数据选择器的逻辑电路图:______S0 ----| || |S1 ----| |----- Y|______|Verilog实现下面是实现4选1数据选择器的Verilog代码示例:module mux4to1 (input [3:0] D, input [1:0] S, outpu t Y);assign Y = (S[1] & S[0] & D[3]) | (S[1] & ~S[0] & D [2])| (~S[1] & S[0] & D[1]) | (~S[1] & ~S[0] & D[0]);endmodule在上面的代码中,D是4个输入的信号线,S是选择信号线,Y是输出信号线。

根据选择信号的不同状态,使用逻辑运算符进行输入的选取,然后将结果输出到输出信号线Y上。

仿真测试为了验证4选1数据选择器的正确性,可以进行仿真测试。

以下是一个简单的测试示例:module test_mux4to1;// Declare signalsreg [3:0] D;reg [1:0] S;wire Y;// Instantiate the modulemux4to1 mux (D, S, Y);// Stimulusinitial begin// Test case 1D = 4'b0001; S = 2'b00; // Expect Y to be 0 #10;// Test case 2D = 4'b0001; S = 2'b01; // Expect Y to be 0 #10;// Test case 3D = 4'b0001; S = 2'b10; // Expect Y to be 0 #10;// Test case 4D = 4'b0001; S = 2'b11; // Expect Y to be 1 #10;$finish;endendmodule上述代码中,D和S是输入信号,Y是输出信号。

四选一数据选择器实验报告

四选一数据选择器11微电子黄跃1117426021【实验目的】1.四选一数据选择器,2.学习V erilog HDL文本文件进行逻辑设计输入;3.学习设计仿真工具modelsim的使用方法;【实验内容】1. 实现四选一数据选择器的“V erilog ”语言设计。

2. 设计仿真文件,进行验证。

【实验原理】数据选择器又称为多路转换器或多路开关,它是数字系统中常用的一种典型电路。

其主要功能是从多路数据中选择其中一路信号发送出去。

所以它是一个多输入、单输出的组合逻辑电路。

4选1数据选择器的元件符号如图一所示,其中D0、D1、D2、D3是4位数据输入端,A0和A0是控制输入端,Y是数据输出端。

当A1A0=00时,输出Y=D1;A1A0=01时,Y=D1;A1A0=10时,Y=D2;A1A0=11,Y=D3。

由真值表写出输出逻辑表达式301201101001)()()()(D A A D A A D A A D A A F +++=由逻辑表达式做出逻辑电路图。

【程序源代码】module mux4_1(sel,in,out);input [1:0] sel;input [3:0] in;output out;reg out;always@(sel or in) begincase ({sel[1],sel[0]})2'b00: out=in[0];2'b01: out=in[1];2'b10: out=in[2];2'b11: out=in[3];default: out=1'bx;endcaseendEndmodule测试程序代码如下:module test_mux4_1;reg [1:0] S;reg [3:0] IN;wire Y;mux4_1 M1(.sel(S),.in(IN),.out(Y));always #10 IN[0]=~IN[0];always #20 IN[1]=~IN[1];always #40 IN[2]=~IN[2];always #80 IN[3]=~IN[3];initialbegin S=1'b0;IN=4'h0;#100 $stop;endalways #10 S=S+1;endmodule【仿真和测试结果】【实验心得和体会】这次实验与上次相比有明显的进步,通过这次实验我对modelsim的应用更加得心应手,深切的体会到了verilog是一种描述性语言,这次实验总的来说是比较顺利的,但在实验过程中还是遇到了一些问题,比如端口的匹配问题,在写程序的时候误将位宽写在了变量名的后面,虽然程序能够运行但有警告,仿真波形是错误的,可见在写程序时警告有时也是致命的,这要求我们在学习的过程中思想一定要严谨!其次在做实验时一定要多想,例如在学习这门课时,书上说在模块外部输入可以是wire型或reg型,但在写程序时激励模块往往要初始化数据,所以编程时其类型往往声明为reg型,通过这个例子我明白了书上所说的有时往往是一个比较笼统的,而更多的需要我们自己去实践、探索、勤思考,只有这样我们才能把书本上的知识转化为属于我们自己的知识,才能在学习的道路上走的更远!原文已完。

EDA实验报告(四选一、四位比较器、加法器、计数器、巴克码发生器)

EDA实验报告(四选⼀、四位⽐较器、加法器、计数器、巴克码发⽣器)实验1 4选1数据选择器的设计⼀、实验⽬的1.学习EDA软件的基本操作。

2.学习使⽤原理图进⾏设计输⼊。

3.初步掌握器件设计输⼊、编译、仿真和编程的过程。

4.学习实验开发系统的使⽤⽅法。

⼆、实验仪器与器材1.EDA开发软件⼀套2. 微机⼀台3. 实验开发系统⼀台4. 打印机⼀台三、实验说明本实验通过使⽤基本门电路完成4选1数据选择器的设汁,初步掌握EDA设计⽅法中的设汁输⼊、编译、综合、仿真和编程的过程。

实验结果可通过实验开发系统验证,在实验开发系统上选择⾼、低电平开关作为输⼊,选择发光⼆极管显⽰输出电平值。

本实验使⽤Quartus II软件作为设计⼯具,要求熟悉Quartus II软件的使⽤环境和基本操作,如设计输⼊、编译和适配的过程等。

实验中的设计⽂件要求⽤原理图⽅法输⼊,实验时,注意原理图编辑器的使⽤⽅法。

例如,元件、连线、⽹络爼的放巻⽅法和放⼤、缩⼩、存盘、退岀等命令的使⽤。

学会管脚锁定以及编程下载的⽅法等。

四、实验要求1.完成4选1数据选择器的原理图输⼊并进⾏编译;2.对设计的电路进⾏仿真验证:3.编程下载并在实验开发系统上验证设计结果。

五、实验结果管脚分配:N;如kne DteOwn LccatMi Pwecgj G【c^p I/ODo-l 2 GC6P I ifo Xfl-c t nk A Igt PHJ V21Bl NO AS-VLUTrifd2?B Irpjt PIW.VI DJ_W ^>VLVTTl(d 3? co1r(xt P1M IPS5a^Lumid 庐Cl Irpul P1W.KC654a>vivin(d 5* C213P1KLP2S M」JO a>vLum(d 6* C3Inpjt叽⼼:■? ^3-VLVTn(d I* GK incut PJWJtfH7B7JJ1 a>VLUTn(d8o v O J U X A7B7 M J S3-VLVTn(d9<wvx4fr?实验2 四位⽐较器⼀、实验⽬的1. 设计四位⼆进制码⽐较器,并在实验开发系统上验证。

四选一数据选择器课程设计

EDA课程设计报告题目:四选一数据选择器院系班级:设计者:指导老师:设计时间:目录目录 ......................................................................................................................................... - 1 - 1、设计目的、要求.................................................................................................................... - 2 -1.1、设计目的..................................................................................................................... - 2 -1.2、系统设计要求............................................................................................................. - 2 -1.3、设计工具..................................................................................................................... - 2 -2、设计原理及相关硬件............................................................................................................ - 3 -2.1、系统设计方案及原理................................................................................................. - 3 -2.2、硬件原理..................................................................................................................... - 3 -3、主要模块设计........................................................................................................................ - 4 -3.1、模块xy4 ...................................................................................................................... - 4 -4、系统编译及仿真过程............................................................................................................ - 5 -4.1、工程建立..................................................................................................................... - 5 -4.2、系统编译..................................................................................................................... - 6 -4.3、仿真............................................................................................................................. - 7 -5、硬件验证过程和分析............................................................................................................ - 7 -5.1、引脚设置和保护......................................................................................................... - 7 -5.2、硬件下载..................................................................................................................... - 8 -6、实验参考程序...................................................................................................................... - 11 -6.1、模块xy4 .................................................................................................................... - 11 -7、总结...................................................................................................................................... - 11 -1、设计目的、要求1.1、设计目的了解并掌握一般设计方法,具备初步的独立设计能力;掌握用VerilogHDL语言程序的基本技能;提高综合运用所学的理论知识独立分析和解决问题的能力;进一步掌握EDA技术的开发流程,学习其独特的运用,进一步的提高自己的动手能力和知识领域。

EDA4选一数据选择器程序

4选一LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY MUX41A_ZXT ISPORT (A1,A0: IN STD_LOGIC;EN: IN STD_LOGIC;D3,D2,D1,D0: IN STD_LOGIC;Y: OUT STD_LOGIC);END ENTITY MUX41A_ZXT;ARCHITECTURE BHV OF MUX41A_ZXT ISSIGNAL A :STD_LOGIC_VECTOR(2 DOWNTO 0); BEGINA <= EN & A1 & A0;Y <= D0 WHEN A="000" ELSED1 WHEN A="001" ELSED2 WHEN A="010" ELSED3 WHEN A="011" ELSE'Z';END ARCHITECTURE BHV;3—8译码器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY DEC38A_ZXT ISPORT ( A2,A1,A0: IN STD_LOGIC;S1,S2,S3: IN STD_LOGIC;Y: OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); END ENTITY DEC38A_ZXT;ARCHITECTURE EX2 OF DEC38A_ZXT ISSIGNAL A: STD_LOGIC_VECTOR(5 DOWNTO 0); BEGINA <= S1 & S2 & S3 & A2 & A1 & A0;WITH A SELECTY <= "11111110" WHEN "100000","11111101" WHEN "100001","11111011" WHEN "100010","11110111" WHEN "100011","11101111" WHEN "100100","11011111" WHEN "100101","10111111" WHEN "100110","01111111" WHEN "100111","ZZZZZZZZ" WHEN OTHERS; END ARCHITECTURE EX2;8-3编码器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY ENC83A_ZXT ISPORT(I7,I6,I5,I4,I3,I2,I1,I0:IN STD_LOGIC;Y2,Y1,Y0: OUT STD_LOGIC);END ENTITY ENC83A_ZXT; ARCHITECTURE EX4 OF ENC83A_ZXT IS SIGNAL I: STD_LOGIC_VECTOR (7 DOWNTO 0); SIGNAL Y: STD_LOGIC_VECTOR (2 DOWNTO 0); BEGINI <= I7&I6&I5&I4&I3&I2&I1&I0; WITH I SELECTY <= "000" WHEN "11111110","001" WHEN "11111101","010" WHEN "11111011","011" WHEN "11110111","100" WHEN "11101111","101" WHEN "11011111","110" WHEN "10111111","111" WHEN "01111111","ZZZ" WHEN OTHERS;Y2 <= Y(2);Y1 <= Y(1);Y0 <= Y(0);END ARCHITECTURE EX4;共阴极数码管LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY DEC_DISPLAY_ZXT ISPORT(EN:IN STD_LOGIC;A: IN STD_LOGIC_VECTOR(3 DOWNTO 0);Ya,Yb,Yc,Yd,Ye,Yf,Yg: OUT STD_LOGIC); END ENTITY DEC_DISPLAY_ZXT; ARCHITECTURE EX3 OF DEC_DISPLAY_ZXT IS SIGNAL S: STD_LOGIC_VECTOR(4 DOWNTO 0); SIGNAL Y: STD_LOGIC_VECTOR(6 DOWNTO 0); BEGINS <= EN&A;WITH S SELECTY <= "1111110" WHEN "10000","0110000" WHEN "10001","1101101" WHEN "10010","1111001" WHEN "10011","0110011" WHEN "10100","1011011" WHEN "10101","1011111" WHEN "10110","1110000" WHEN "10111","1111111" WHEN "11000","1111011" WHEN "11001","0000000" WHEN OTHERS;Ya <= Y(6);Yb <= Y(5);Yc <= Y(4);Yd <= Y(3);Ye <= Y(2);Yf <= Y(1);Yg <= Y(0);END ARCHITECTURE EX3;#include <reg51.h>sbit s1=P3^5;void delay(){ unsigned char i,j;for (i=0;i<255;i++)for(j=0;j<255;j++);}void main(){unsigned char i;unsigned char temp;P0=0xff;while(s1==1){temp=0x01;for(i=0;i<8;i++){P0=~temp;delay();temp=temp<<1;}}while(s1==0){temp=0x80;for(i=0;i<8;i++) {{unsigned char i; unsigned char temp; P0=0xff;while(s1==1) {temp=0x01;for(i=0;i<8;i++){P0=~temp;delay();temp=temp<<1;}}while(s1==0) {temp=0x80;for(i=0;i<8;i++) {P0=~temp;delay();temp=temp>>1; }}。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

四选一数据选择器源程序

Library ieee;

Use ieee.std_logic_1164.all;

Entity mux4_2 is

Port (din: in std_logic_vector(3 downto 0); a,b : in std_logic;

S: out std_logic);

End;

Architecture with_when of mux4_2 is Signal sel : std_logic_vector(1 downto 0); Begin

Sel<=a&b;

S<=din(0) when sel=“00”else

din(1)when sel= “01” else

din(2)when sel= “10” else

din(3);---见程序说明。

Architecture with_select of mux4 is

Signal sel :std_logic_vector(1 downto 0); begin

sel<=a&b;

with sel select

s<=din(0) when “00”,

s<=din(1) when “01”,

s<=din(2) when “10”,

s<=din(3) when “11”,

…Z‟when others;

End;

程序说明:

1.本程序中含有两个结构体,with_when和with_select,max+plus软

件系统自动执行几何位置处于最后的机构体with_select.

2.结构体with_when是用并行条件信号赋值语句描述四选一数据选

择器。

注意,最后一个输出din(3)不含有when子句;在s表达式中只有一个分号(;)。

3.结构体with_select.是用并行选择信号赋值语句描述四选一数据选

择器。

注意,选择信号赋值语句中选择条件与case语句相似,不允许条件重叠和涵盖不全。

由于a,b的值除了‘1’‘0’外,还有其他7个值,所以要用when others代表其他值,以穷尽所有可能值。

4.同一个设计任务,可以用不同的语句进行描述,

5.本程序中din为输入4位矢量信号。

实例2 3线----8线译码器

一、设计任务

描述一个3线-8线译码器,使能端为g1、g2a、g3b,地址选择端为a、

b、c,输出端为总线y。

二、算法设计

用case语句描述电路,利用真值表辅助,很容易编写出程序。

三、源程序

1.文件名decoder3_8.vhd

2.端口图

3线-8线译码器端口

3.源程序

Library ieee;

Use ieee.std_logic_1164.all;

Entity decoder3_8 is

Port (a、b、c g1、g2a、g2b:in std_logic;

Y: out std_logic_vector(7 downto 0));

End;

Architecture rtl of decoder3_8 is

Signal dz:std_logic_vector(2 downto 0);

Begin

Dz<=c&b&a;

Process(dz,g1,g2a,g3b)

Begin

If (g1= …1‟ and g2a= …0‟and g2b= …0‟) then

Case dz is

When “000”=>y<= “11111110”;

When “001”=>y<= “11111101”;

When “010”=>y<= “11111011”;When “011”=>y<= “111101111”;When “100”=>y<= “11101111”;When “101”=>y<= “11011111”;When “110”=>y<= “10111111”;When “111”=>y<= “01111111”;When others =>y<= “XXXXXXXX”;End case;

Else

Y<= “11111111”;

End if ;

End process;

End;。