相位差测量电路设计

用于相位法激光测距的电路系统设计

用于相位法激光测距的电路系统设计激光测距是一种常用的非接触式测量技术,可以精确测量目标物体与测距仪的距离。

相位法激光测距是其中一种常见的方法,通过测量激光光波的相位差来计算距离。

下面将介绍一个基于相位法激光测距原理的电路系统设计。

1. 激光发射电路:设计一个激光二极管的驱动电路,可以通过电流控制二极管的发射光强。

使用一个恒流源以确保驱动电流的稳定性。

此外,还需要添加一个调节电路,可以根据需要调整激光发射的光功率。

2. 光电检测电路:将光电二极管作为光电检测元件接在测距仪上,用于接收激光反射光信号。

光电二极管产生的电流与光的强度成正比。

使用一个高增益的放大器将光电二极管产生的微弱电流信号放大。

3. 相位差测量电路:使用一个相位差测量电路来测量激光光波发射和接收之间的相位差。

该电路可以采用锁相放大器或频率调制技术。

在锁相放大器中,将激光发射的信号作为参考信号,将光电二极管接收到的信号作为待测信号输入。

锁相放大器可以精确测量相位差,并输出一个稳定的直流电压信号。

4. 距离计算电路:将锁相放大器输出的直流电压信号输入到距离计算电路中,根据相位差和激光波长的关系,计算出目标物体与测距仪之间的距离。

该电路可以通过编程芯片或者专门的测距芯片来实现距离计算。

以上是一个基于相位法激光测距原理的电路系统设计。

通过精心选择和设计各个电路模块,可以实现高精度和稳定的激光测距功能。

需要注意的是,在实际设计中还需考虑电路的抗干扰能力、功率稳定性和其他实际应用需要的因素。

在激光测距中,相位法是一种常用的方法,能够提供高精度和高稳定性的测距结果。

相位法激光测距的原理是通过测量激光发射和接收之间的光波相位差来计算目标物体与测距仪之间的距离。

在设计电路系统时,需要考虑到激光发射电路、光电检测电路、相位差测量电路和距离计算电路等各个环节。

首先,激光发射电路是相位法激光测距系统中的重要组成部分。

它负责驱动激光二极管发射具有稳定光强的激光光束。

电路实验报告

实验一 元件特性的示波测量法一、实验目的1、学习用示波器测量正弦信号的相位差。

2、学习用示波器测量电压、电流、磁链、电荷等电路的基本变量3、掌握元件特性的示波测量法,加深对元件特性的理解。

二、实验任务1、 用直接测量法和李萨如图形法测量RC 移相器的相移ϕ∆即uC u sϕϕ-实验原理图如图5-6示。

2、 图5-3接线,测量下列电阻元件的电流、电压波形及相应的伏安特性曲线(电源频率在100Hz~1000Hz 内): (1)线性电阻元件(阻值自选)(2)给定非线性电阻元件(测量电压范围由指导教师给定)电路如图5-7 3、按图5-4接线,测量电容元件的库伏特性曲线。

4、测量线性电感线圈的韦安特性曲线,电路如图5-55、测量非线性电感线圈的韦安特性曲线,电源通过电源变压器供给,电路如图5-8所示。

图 5-7 图 5-8这里,电源变压器的副边没有保护接地,示波器的公共点可以选图示接地点,以减少误差。

三、思考题1、元件的特性曲线在示波器荧光屏上是如何形成的,试以线性电阻为例加以说明。

答:利用示波器的X-Y方式,此时锯齿波信号被切断,X轴输入电阻的电流信号,经放大后加至水平偏转板。

Y轴输入电阻两端的电压信号经放大后加至垂直偏转板,荧屏上呈现的是u x,u Y的合成的图形。

即电流电压的伏安特性曲线。

3、为什么用示波器测量电路中电流要加取样电阻r,说明对r的阻值有何要求?答:因为示波器不识别电流信号,只识别电压信号。

所以要把电流信号转化为电压信号,而电阻上的电流、电压信号是同相的,只相差r倍。

r的阻值尽可能小,减少对电路的影响。

一般取1-9Ω。

四、实验结果1.电阻元件输入输出波形及伏安特性2.二极管元件输入输出波形及伏安特性实验二 基尔霍夫定律、叠加定理的验证 和线性有源一端口网络等效参数的测定一、实验目的1、加深对基尔霍夫定律、叠加定理和戴维南定理的内容和使用范围的理解。

2、学习线性有源一端口网络等效电路参数的测量方法3、学习自拟实验方案,合理设计电路和正确选用元件、设备、提高分析问题和解决问题的能力 二、实验原理 1、基尔霍夫定律:基尔霍夫定律是电路普遍适用的基本定律。

基于STM32的全相位FFT相位差测量系统

第33卷第3期2010年6月电子器件Chinese Journal of Electr on DevicesVol .33 No .3Jun .2010收稿日期:2010-01-07 修改日期:2010-01-20The All 2Ph ase FFT Ph ase D i fference Measure ment Syste m B ased on ST M32Q IU L iangfeng,L IU J ingbiao 3,YU Haibin(School of E lectronics &Infor m ation,Hangzhou D ianzi U niversity,Hangzhou 310018,China )Abstract:For the need of signal phase difference measure ment in m ilitary and civil engineering fields ,based on A ll 2phase measure ment theory (a kind of FFT ).and the AR M company ’s high 2perfor mance p r ocess or,32B itCortex M32core ST M32F103,we designed and built a l o w 2cost,si m p le structure,fast p r ocessing and effective phase difference measure ment syste m.After by sa mp ling 127point and treating of the m,we make 64point FFT and achieve the signal phase measure ment .The tests show that the syste m has an effective res oluti on accuracy of 1degree .Key words:phase difference measure ment;ST M32;A ll 2phase FFT;si m ulati on testing EEACC:7310H基于ST M32的全相位FFT 相位差测量系统邱良丰,刘敬彪3,于海滨(杭州电子科技大学电子信息学院,杭州310018)摘 要:针对军用和民用工程领域信号相位差测量的需要,基于全相位测量理论,使用AR M 公司的高性能32B it Cortex M32内核处理器ST M32F103,设计并制作了一个低成本,结构简单,处理速度快而有效的相位差测量系统,通过采样了127个点,处理后做64个点的FFT,实现了信号相位差的测量。

Multisim仿真软件的相位差测量方法

Multisim仿真软件的相位差测量方法Multisim是一款功能强大的仿真软件。

它拥有丰富的工具和模块,能够实现各种电路的设计、仿真和分析。

其中,相位差测量是电子工程中常用的一种测试方法,也是Multisim中的一项基础功能。

本文将介绍Multisim如何进行相位差测量。

一、相位差的概念和测量相位差是指两个信号之间的时间延迟。

在电子工程中,相位差常用于比较两个信号的相对时间位置,用来判断是否符合预期的设计要求。

如果相位差符合预期,那么电路就可以正常工作,如果相位差不正确,则可能会导致电路出现故障或者严重失效。

在Multisim中,相位差是指两个信号的相对相位差,通常用角度(degree)或者弧度(radian)表示。

相位差可以通过两个信号在时间轴上的差值来计算。

如果两个信号的周期相同,则相位差可以用信号的相位角(phase angle)来表示。

相位差的表示方法有很多种,下面是一些常用的表示方法:1. 角度表示:相位差可以用角度表示,通常用degree表示,一个周期为360度。

2. 弧度表示:相位差可以用弧度表示,通常用radian表示,一个周期为2π(约等于6.28)。

3. 周期表示:相位差可以用周期表示,用一个信号的周期表示另一个信号的相位延迟,通常用T表示。

4. 时差表示:相位差可以用时差表示,即两个信号之间的时间差,通常用t表示。

二、Multisim中的相位差测量方法Multisim中提供了多种方法来测量相位差,下面是一些常用的方法:1. 用示波器测量相位差示波器是电子工程中经常用来测量信号的一种仪器。

在Multisim中,示波器也可以用来测量相位差。

首先,需要将两个信号分别输出到示波器中。

然后,可以使用示波器中的相位差测量功能来计算相位差。

具体步骤如下:1. 将示波器拖入工作区,并将两个信号线分别连接到示波器上。

2. 点击示波器,进入示波器的设置界面。

3. 在设置界面中,可以选择要测量的信号,以及相位差计算的方式。

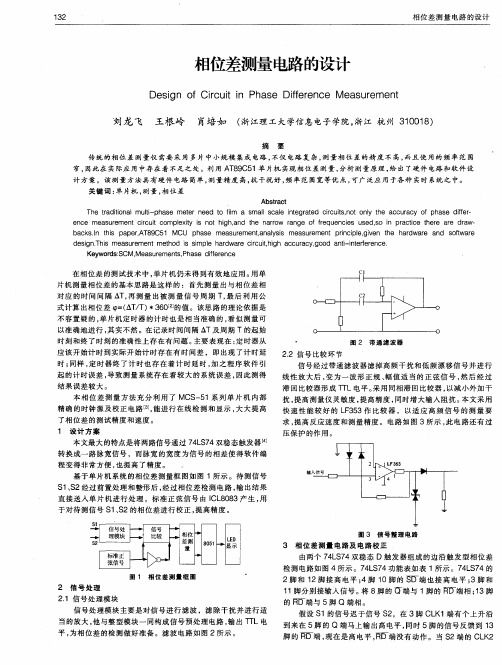

相位差测量电路的设计

Abs t r a c t

Th e t r adi t i on a l m u l t i -ph as e me t e r n ee d t o f i l m a s ma l l s c al e i n t egr a t e d ci r cu i t s , n o t on l y t he ac cu r a c y of ph a s e di fer — e n ce mea s ur emen t c i r cu i t co m pl e xi t y i s n ot h i gh , an d t h e n ar r o w r an ge of f r equ en ci e s u s ed, S O i n pr a c t i c e t h er e ar e dr a w—

时 刻 和终 了 时刻 的准 确 性 上 存 在 有 问 题 。 主 要表 现在 : 定 时 器 从 应 该 开始 计 时到 实 际开 始 计 时 存 在 有 时 间差 ,即 出 现 了计 时 延

图 2 带 通滤 波器

2 . 2 信 号 比较 环 节 信 号 经过 带通 滤 波 器 滤 掉 高 频 干 扰 和 低 频 漂 移 信 号 并 进 行

1 3 2 相 位 差源自测 量 电 路 的 设 计 相位差测量 电路的设计

De s i gn o f Ci r c u i t i n Ph a s e Di f f e r e n c e Me a s u r e me n t

刘龙 飞 王根 岭 肖培 如 ( 浙江理工大学信息电子学院, 浙江 杭州 3 1 0 0 1 8 )

摘 要

传 统 的相 位 差 测 量仪 需要 采 用 多片 中 小规 模 集成 电路 , 不 仅 电路 复 杂 , 测 量 相 位 差 的精 度 不 高 , 而且 使 用 的 频 率 范 围

基于差放的相位差测量电路的设计及仿真

性 不 高 (o H 1 k z时 , l 法 间 接 测量 计 算 结 果 为 图 方 _ 38 9 , 理 论 结果 比较 误差 为 1 4  ̄ 而文 中提 供 7 。  ̄与 7 . 8 7

. 很 近 的时候 。 量 的效果 很 不理 想 , 测 这是 增大 误 差 的一 11电路 组成 个重 要 原 因 :其 次是 测 得 的结果 还需 经 过相 关公 式 间 接 计 算而 得 . 过 程 显得 繁 琐 。 其 这显 然 不 符合 Mu i m hs i

一

尽 显 了仪 器 仪 表 众 多 、 方 便 快 捷 等 多 个 特 点 。但 是 被溺 电路 的输 入端 日接 入一 个 交 流信号 源 或者 函数 信 Nut i ls i m没 有 直接 测 量 电 压楣 位 差 的仪表 可 用 ( 件 号 发生器 .即波特 图示 仪是 在 既定 频 率下 以扫 描信 号 软 有 直接 显示 比较 两个 电位 的电位 差 的仪 器 .也 即波 特 源 ( 其初 相 位 为 o ) 设 o为参 考 , 量某 一信 号 与其 之 间 测

常用 的相 位差 处 理方 法圆 。

伊 一 9 一幻: —x3 。 竺 6 : 。 — 6 。 o o

T

() 1 ,

从 上 面的求 解 过 程 可知 . l中 的读数 指针 T 图 l和 1 2都 需要 依 靠 鼠标 的人 为 移 动得 以定 位 . 因此 其 精准

如 图 4和 图 5左 图所 示 .将 读 数 指 针 1定 位 到

10 H 0 k z时 ,经相 位 差 测量 电路后 出现 约 为 00 3 . .7  ̄ 小

于 01 ; 定 位 到 1 k z时 . 现 的 误 差 约 为 00 7  ̄ .。 当 0H 出 . 3 0 电路 中 R 和 R 为 电位器 , 作用 是 对输 入 信号 进 ( 处 图中未 显示 , 实 际 已测 量 ) 小于 00  ̄ , 2 其 此 但 , .1。当把 读 行 一 定 比例 的线 性 缩 小 ( 其 缩 小 比例 为 M) 因为 需 书 指 针 2定 位 到 1误 差 时 .可 测量 的最 大频 率 为 1 设 . o . 要 考虑 到 后续 运放 对最 大输 入 信 号大 小 的 限制 .必 须 3 MHz 7 。也 即呈 现频 率越 大 . 误差 就越 大 的规律 左 图 将 大 的输 入 信号 经 过一 定 的处 理才 方便 使 用 . 以 Rl 是 将 单 个 运 放 的 U i G i a d it 设 置 为 所 nt an B n w dh y— 和 R 2保 证 了后 续 电路 的正 常运 行 在 实 际使 用 时必 2 0 0 MHz 时所 得 结果 ,但 设 置 为软件 默认 IO z . O MH 时

电路基础原理分析与计算交流电路中的相位差

电路基础原理分析与计算交流电路中的相位差在电路中,相位差是一个重要的概念,它指示了两个交流电信号之间的时间差或相对位置差。

对于交流电路的设计和分析来说,了解和计算相位差是非常重要的。

在交流电路中,相位差是指两个电压或电流波形之间的时间差。

我们知道,交流电是通过周期性的正弦波形表示的,每个周期的长度称为周期T。

相位差的计算方法是通过比较两个波形中的相同点(比如峰值、波峰、波谷等)之间的时间差来进行的。

在交流电路中,我们经常会用到相位差的概念来描述不同电路元件之间的关系。

例如,在串联电感电阻电路中,电感元件的电压与电阻元件的电压之间存在相位差。

而且,相位差不仅可以是正数,还可以是负数,取决于两个波形之间的相对位置。

当两个交流电信号的相位差为0时,两者的波形完全一致,表示它们在相同的时间点上达到最大或最小值。

当相位差为90度时,两个波形之间存在四分之一个周期的时间差。

当相位差为180度时,波形完全相反,一个达到最大值时另一个达到最小值。

当相位差为270度时,两个波形之间存在三分之二个周期的时间差。

在交流电路设计和分析中,我们经常需要计算电路中不同元件之间的相位差。

为了计算相位差,我们可以使用示波器或频谱分析仪等仪器来测量电路中不同信号的相对位置。

此外,我们还可以利用波形的峰值和波形的周期来计算相位差。

对于正弦波形,我们可以使用以下公式来计算相位差:相位差(度)= 时间差 / 周期 × 360其中,时间差是两个信号之间的时间差,周期是信号的一个完整周期的长度。

通过计算相位差,我们可以更好地理解电路中不同信号之间的关系。

在电路设计中,准确计算相位差可以帮助我们选择合适的元件和确定合适的参数,从而实现所需的功能和性能。

总的来说,相位差是交流电路中的一个重要概念,它指示了电路中不同信号之间的时间差或相对位置差。

在电路设计和分析中,准确计算相位差对于实现所需的功能和性能非常重要。

基于FPGA的相位差测量模块的设计

基于FPGA的相位差测量模块的设计相位差测量设计思路相位差测量设计要求基于FPGA设计一个测量两路同频率信号相位差的模块,具体要求如下:测量信号频率范围: 20Hz~20kHz ,精度:2度,测量波形:方波。

自行设计相位差可控双路输出脉冲源作为被测对象。

发挥部分:(1)相位差和频率交替显示或同时显示(2)提高测量精度(3)拓宽频率范围到20Hz~200kHz(4)设计出一套相位计前置整形电路方案(采用模拟电路或者模数混合,仅设计和仿真,不制作),要求能自适应峰峰值在0.2V至5伏的非方波输入信号,尽量减少两路输入信号幅度不一致引入的误差,带宽不小于20Hz~20kHz,输出信号能接入本课题设计的相位差测量模块。

相位差测量设计方案根据题目要求,我们组把这个模块的设计分为四个子模块,分别为:信号源的发生、频率计的设计、相位差的测量和四位LED相位差显示。

信号源的发生产生两路同频、相位差可控的信号;频率计的设计是借用信号源产生的信号,然后根据内部晶振产生闸门宽度为1秒的闸门信号,在高电平时开始计数,记得的周期个数,即信号源产生信号的频率;相位差的测量是先通过测量两路信号的上升沿之间内部晶振的周期数,然后由此周期数换算出相位差,再通过VHDL语言内部函数转换成十进制数输出到显示模块。

RTL图如下:模块程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY kzys ISPORT ( CLK : IN STD_LOGIC;KG : IN STD_LOGIC;ZS : IN NATURAL;KG_OUT: OUT STD_LOGIC );END entity kzys;ARCHITECTURE one OF kzys ISSIGNAL CNT: NATURAL;BEGINPROCESS(KG,CLK)BEGINIF KG='0' THEN CNT<=0;KG_OUT<='0';ELSIF CLK'EVENT AND CLK='1' THEN IF CNT<ZS THENCNT<=CNT+1;ELSEKG_OUT<='1';END IF;END IF;END PROCESS;END;library ieee;use ieee.std_logic_1164.all;entity xhk isport(sw_1:in std_logic_vector(4 downto 0); f_out1:out natural;y_out2:out natural );end xhk;architecture one of xhk isbeginprocess(sw_1)begincase sw_1 iswhen "00001"=>f_out1<=499999;y_out2<=277778;when "00010"=>f_out1<=499999;y_out2<=625000;when "00011"=>f_out1<=499999;y_out2<=1666667;when "00100"=>f_out1<=6666;y_out2<=5556;when "00101"=>f_out1<=6666; y_out2<=11111;when "00110"=>f_out1<=6666; y_out2<=16667;when "00111"=>f_out1<=499; y_out2<=1806;when "01000"=>f_out1<=499; y_out2<=1667;when "01001"=>f_out1<=499; y_out2<=625;when "01010"=>f_out1<=82; y_out2<=174;when "01011"=>f_out1<=82; y_out2<=81;when "01100"=>f_out1<=82; y_out2<=220;when "01101"=>f_out1<=49;y_out2<=32;when "01110"=>f_out1<=49;y_out2<=65;when "01111"=>f_out1<=49;y_out2<=122;when "10000"=>f_out1<=0;y_out2<=0;when others=>f_out1<=0;y_out2<=0;end case;end process;end;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY plfsq ISPORT ( clk: IN STD_LOGIC; ZS: IN NATURAL;KG: IN STD_LOGIC;F_OUT : OUT STD_LOGIC );END ;ARCHITECTURE one OF plfsq IS SIGNAL FULL: STD_LOGIC ;BEGINPROCESS(clk)VARIABLE CNT8 : NATURAL;BEGINIF KG='0' THENFULL <='0';CNT8 :=ZS;ELSIF clk'EVENT AND clk='1' THEN IF CNT8 >0 THENCNT8:=CNT8-1;ELSECNT8 :=ZS;FULL <= NOT FULL;END IF;END IF;END PROCESS ;PROCESS(clk,FULL)BEGINIF KG='1' THENIF clk 'EVENT AND clk = '1' THEN IF FULL = '1' THEN F_OUT <='1'; ELSE F_OUT <='0';END IF;END IF;END IF;END PROCESS;END one;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY plfsqy ISPORT ( clk: IN STD_LOGIC; ZS: IN NATURAL;KG: IN STD_LOGIC;F_OUTY : OUT STD_LOGIC );END ;ARCHITECTURE one OF plfsqy IS SIGNAL FULL: STD_LOGIC ;BEGINPROCESS(clk)VARIABLE CNT8 : NATURAL;BEGINIF KG='0' THENFULL <='0';CNT8 :=ZS;ELSIF clk'EVENT AND clk='1' THEN IF CNT8 >0 THENCNT8:=CNT8-1;ELSECNT8 :=ZS;FULL <= NOT FULL;END IF;END IF;END PROCESS ;PROCESS(clk,FULL)BEGINIF KG='1' THENIF clk 'EVENT AND clk = '1' THEN IF FULL = '1' THEN F_OUTY <='1'; ELSE F_OUTY <='0';END IF;END IF;END IF;END PROCESS;END one;信号源的发生:library ieee;use ieee.std_logic_1164.all;entity xhy isport(sw_1:in std_logic_vector(4 downto 0); clk:in std_logic;kg:in std_logic;f_outy:out std_logic;f_out:out std_logic);end xhy;architecture qq of xhy iscomponent xhkport(sw_1:in std_logic_vector(4 downto 0);f_out1:out natural;y_out2:out natural ); end component ;component kzysPORT ( CLK : IN STD_LOGIC; KG : IN STD_LOGIC;ZS : IN NATURAL;KG_OUT: OUT STD_LOGIC ); end component;component plfsqyPORT ( clk: IN STD_LOGIC; ZS: IN NATURAL;KG: IN STD_LOGIC;F_OUTY : OUT STD_LOGIC ); end component; component plfsqPORT ( clk: IN STD_LOGIC;ZS: IN NATURAL;KG: IN STD_LOGIC;F_OUT : OUT STD_LOGIC );end component;signal a,b:NATURAL;signal c:STD_LOGIC;beginu1:xhk port map( sw_1=>sw_1,f_out1=>a,y_out2=>b);u2:kzys port map(zs=>b,clk=>clk,kg=>kg,kg_out=>c);u3: plfsqy port map(clk=>clk,ZS=>a, KG=>C,F_OUTY=>F_OUTY); u4: plfsq port map(clk=>clk,ZS=>a,KG=>KG,F_OUT=>F_OUT); END ARCHITECTURE qq;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt10 isport(clk,en,clr:in std_logic;count10:buffer integer range 0 to 400000000); end cnt10;architecture art of cnt10 isbeginprocess(clk,clr,en)beginif clr='1'thencount10<=0;elsif rising_edge(clk)thenif(en='1')thencount10<=count10+1;end if;end if;end process;end art;频率计的设计:use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity freq_measure isPort( clk0 : instd_logic;wave1 : in std_logic;q : out integer range 0 to 400000000);end freq_measure;architecture art of freq_measure iscomponent cnt10port(clk,en,clr:in std_logic;count10:buffer integer range 0 to 400000000);end component;signal en1,clr1 : std_logic;signal date:integer range 0 to 400000000;beginprocess(clk0)variable cnt:integer range 0 to 6;beginif rising_edge(clk0) thenif cnt = 0 then clr1 <= '1';cnt:=1;elsif cnt > 5 then cnt := 0;q<=date;else cnt := cnt+1;clr1 <= '0';en1 <= '1';end if;end if;end process;u1 : cnt10 port map(clk=>wave1,en=>en1,clr=>clr1,count10=>date);end art;library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity measure_n isPort( clk,clk0,clk1:instd_logic;n_out:out std_logic_vector(15 downto 0));end measure_n;architecture art of measure_n issignal count0,count01,count02,count1,count2 : std_logic_vector(15 downto 0);signal x,y,a,clk10,clk11,clk20,clk21: std_logic;beginprocess(clk,clk0,clk1,x,y,count1,count2)beginif clk'event and clk='1'thencase a iswhen '0'=>clk10<=clk0;clk11<=clk1;if clk10='0' and clk11='0'thencount1<=(others=>'0');end if;if clk10='0'thenx<='1';end if;if x='1' thenif clk10='1' thenif clk11='0' then y<='1'; end if;if y='1' thenif clk11='1' thencount01<=count1;count1<=count1;elsecount1<=count1+1;end if;end if;end if;end if;if count01=0 thena<='1';else a<='0';end if;when '1'=>clk20<=clk1;clk21<=clk0;if clk20='0' and clk21='0'then count2<=(others=>'0');end if;if clk20='0'thenx<='1';end if;if x='1' thenif clk20='1' thenif clk21='0' then y<='1';end if;if y='1' thenif clk21='1' thencount02<=count2;count2<=count2;elsecount2<=count2+1;end if;end if;end if;end if;if count02=0 thena<='0';else a<='1';end if;when others=>a<='1';end case;count0<=count01 or count02;end if;n_out<=count0;end process;end art;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity consider1 isport ( clk :in std_logic;n1:in std_logic_vector(15 downto 0);freq:in integer range 0 to 400000000;cout:out std_logic_vector(15 downto 0));end consider1;architecture arch of consider1 issignal c0,c1,e,e0,d0,d1:integer range 0 to 400000000;signal count:std_logic_vector(15 downto 0); signal m:std_logic_vector(15 downto 0); beginprocess(n1,clk)beginif rising_edge(clk) thenm<=n1;c0<=conv_integer(m);d0<=c0*151;d1<=d0/1024;end if;end process;process(clk,freq)beginif rising_edge(clk) thenc1<=freq;e<=c1*d1;e0<=e/2048;count<=conv_std_logic_vector(e0,16);end if;end process;cout<=count;end arch;library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity count isport( clk:in std_logic;c_in:in std_logic_vector(15 downto 0);qa1,qb1,qc1,qd1:out INTEGER RANGE 0 TO 9); End count;architecture art of count isSignal a:integer range 0 to 400000000;signal m: std_logic_vector(15 downto 0); BeginProcess(clk,c_in)variable ai,bi,ci,di:integer range 0 to 9; beginif clk'event and clk='1' thenm<=c_in;a<=conv_integer(m);di:=(a-ai-10*bi-100*ci) /1000;ci:= (a-ai-10*bi)/100;bi:= ((a-ai) rem 100)/10;ai:=a rem 10;end if;qd1<=di;qc1<=ci;qb1<=bi;qa1<=ai;end process;end art;相位差的测量:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity phase_measure1 isport( clkin,clk0in,clk1in:in std_logic;qa1out,qb1out,qc1out,qd1out:out integer range 0 to 9 );end;architecture art of phase_measure1 iscomponent measure_nPort( clk,clk0,clk1:instd_logic;n_out:out std_logic_vector(15 downto 0));end component;COMPONENT freq_measurePort( clk0 : instd_logic;wave1 : in std_logic;q : out integer range 0 to 400000000 );end COMPONENT;component consider1port ( clk :in std_logic;n1:in std_logic_vector(15 downto 0);freq:in integer range 0 to 400000000;cout:out std_logic_vector(15 downto 0));end component ;component countport( clk:in std_logic;c_in:in std_logic_vector(15 downto 0);qa1,qb1,qc1,qd1:out integer range 0 to 9);end component;signal d,f: std_logic_vector(15 downto 0);signal e: integer range 0 to 400000000;beginu1: measure_n portmap(clk=>clkin,clk0=>clk0in,clk1=>clk1in,n_out=>d);u2: freq_measure port map(clk0=>clkin,wave1=>clk0in,q=>e);u3: consider1 port map(clk=>clkin,n1=>d,freq=>8192,cout=>f);u4: count portmap(clk=>clkin,c_in=>f,qa1=>qa1out,qb1=>qb1out,qc1=>qc1out,qd1=>qd1out);end art;四位LED相位差显示:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY BCD7 ISPORT(BCD:IN INTEGER RANGE 0 TO 9;LED:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END;ARCHITECTURE ART OF BCD7 ISBEGINLED<= "0111111"WHEN BCD= 0 ELSE "0000110"WHEN BCD= 1 ELSE "1011011"WHEN BCD= 2 ELSE "1001111"WHEN BCD= 3 ELSE "1100110"WHEN BCD= 4 ELSE "1101101"WHEN BCD= 5 ELSE "1111101"WHEN BCD= 6 ELSE "0000111"WHEN BCD= 7 ELSE "1111111"WHEN BCD= 8 ELSE "1101111"WHEN BCD= 9 ELSE "0000000";END ART;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; ENTITY Vhdl1 ISPORT(LOCK:IN STD_LOGIC;QA,QB,QC,QD:IN INTEGER RANGE 0 TO 9;LEDA,LEDB,LEDC,LEDD:OUT STD_LOGIC_VECTOR(6 DOWNTO 0)); END;ARCHITECTURE ART OF Vhdl1 ISSIGNAL QAL,QBL,QCL,QDL:INTEGER RANGE 0 TO 9; COMPONENT BCD7PORT(BCD:IN INTEGER RANGE 0 TO 9;LED:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END COMPONENT;BEGINPROCESS(LOCK)BEGINIF(LOCK'EVENT AND LOCK='1')THENQAL<=QA;QBL<=QB;QCL<=QC;QDL<=QD;END IF;END PROCESS;U1:BCD7 PORT MAP(QAL,LEDA); U2:BCD7 PORT MAP(QBL,LEDB); U3:BCD7 PORT MAP(QCL,LEDC); U4:BCD7 PORT MAP(QDL,LEDD); END ART;。

Multisim仿真软件的相位差测量方法

Multisim仿真软件的相位差测量方法作者:潘蓉来源:《数字技术与应用》2016年第07期摘要:Multisim为电路的仿真及测量提供了很多便捷的功能,但其在正弦稳态等电路分析中测量电压相位差存在误差,为了解决这一问题,提出了Multisim软件中“单一频率交流分析法”。

本文通过实例电路的仿真测量,说明了测量方法,由此证明了Multisim软件中“单一频率交流分析法”对相位差测量的精确性。

关键词:Multisim 相位差测量单一频率交流分析法中图分类号:TP212 文献标识码:A 文章编号:1007-9416(2016)07-0240-02Multisim是一款功能强大的模拟与数字电路混合仿真软件,被广泛应用于模拟电子技术、数字电子技术和电路分析的仿真分析与设计。

相位差是正弦稳态电路分析中一个非常重要的参数,是比较两个同频率正弦信号之间的关系唯一指标。

在Multisim中,相位差的测量有三种方法:一是用双踪示波器和电流探针测量出两个正弦信号的波形,然后拖动示波器面板上的测量指针,测量两个正弦信号初相位对应的时间差,再根据正弦信号一个周期对应的相位角为360°,人工计算上述时间差相当的角度。

二是瞬态分析法测量出两个正弦信号的波形,测量两个正弦信号初相位对应的时间差。

相位差的计算方法和方法一完全相同。

三是用“单一频率交流分析”法。

前两种方法优点是直观,缺点是测量误差大,但是“单一频率交流分析”法可以准确地测量出电路中任意一点电压和电流的相位差。

1 Multisim软件中单一频率交流分析法介绍单一频率交流分析(Single Frequency AC Analysis)用来测试电路对某个特定频率进行交流频率响应分析的结果,该功能创建了某个特定频率下电压、电流和电源相量的文本输出。

分析结果以输出信号的实部/虚部或者幅度/相位的形式给出。

首先创建需分析的电路图,执行Simulate →Analysis →Single Frequency AC Analysis命令,弹出Single Frequency AC Analysis对话框。

用示波器测量相位差的方法

用示波器测量相位差的方法一、前言在电子技术领域中,相位差是非常重要的一个参数。

它可以用来描述两个信号之间的时间差,是许多电路和系统设计中必须考虑的因素。

而测量相位差的方法也是非常关键的,因为只有准确地测量了相位差,才能保证电路或系统的正常运行。

本文将介绍用示波器测量相位差的方法,包括仪器准备、接线方法、操作步骤等方面。

二、仪器准备1. 示波器:必须具有双通道功能,并且能够显示两个信号波形。

2. 信号源:提供两个相位不同但频率相同的信号。

信号源可以是任何可以输出正弦波或方波的设备,如函数发生器、信号发生器等。

3. 接线:需要一些连接线和探头来连接示波器和信号源。

三、接线方法1. 将示波器通道1和通道2分别与信号源输出端口连接。

通常情况下,通道1连接到主要信号源输出端口,而通道2连接到参考信号源输出端口。

2. 如果使用探头,则将探头插入示波器输入端口,并将另一端连接到信号源输出端口。

3. 确保连接正确无误,并且所有设备都已打开和调整好参数。

四、操作步骤1. 打开示波器,并将它设置为双通道模式。

确保通道1和通道2均已启用,并且它们的垂直灵敏度和时间基准已经调整好。

2. 设置示波器触发模式为“内部触发”,并选择一个适当的触发电平。

3. 调整信号源,使其产生两个相位不同但频率相同的信号。

可以使用正弦波或方波信号,但必须确保两个信号具有相同的频率。

4. 将通道1和通道2分别与两个信号源连接。

如果使用探头,则将其插入示波器输入端口,并将另一端连接到信号源输出端口。

5. 调整示波器水平扫描控制,使得两个信号在屏幕上能够清晰地显示出来,并且它们之间的时间差可以直观地看出来。

6. 测量相位差:在示波器屏幕上选择一个参考位置,如正弦波或方波的峰值位置。

然后测量第二个信号与参考位置之间的时间差。

这个时间差就是两个信号之间的相位差。

7. 重复以上步骤,直到得到准确的相位差测量结果。

五、注意事项1. 在进行测量时,必须确保两个信号具有相同的频率。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

本科毕业设计( 2015届)题目:相位差测量电路的设计学院:机电工程学院专业:自动化学生姓名:学号:指导教师:职称(学位):讲师合作导师:职称(学位):完成时间:2015 年 5 月 28日成绩:黄山学院教务处制原创性声明兹呈交的设计作品,是本人在指导老师指导下独立完成的成果。

本人在设计中参考的其他个人或集体的成果,均在设计作品文字说明中以明确方式标明。

本人依法享有和承担由此设计作品而产生的权利和责任。

声明人(签名):年月日目录摘要.................................................................................................错误!未定义书签。

英文摘要.ﻩ错误!未定义书签。

1 绪论ﻩ11.1研究背景及意义ﻩ错误!未定义书签。

1.2 发展现状和发展趋势ﻩ错误!未定义书签。

1.2.1国外发展状况........................................................错误!未定义书签。

1.2.2 国内发展状况ﻩ错误!未定义书签。

1.2.3 发展趋势........................................................................错误!未定义书签。

2 相位差测量的基本原理.............................................................错误!未定义书签。

2.1 相位的基本概念.............................................................错误!未定义书签。

2.2相位差测量原理ﻩ错误!未定义书签。

2.3 电路设计原理...................................................................错误!未定义书签。

3设计与分析.. (6)3.1 移相电路...........................................................................错误!未定义书签。

3.1.1 方案分析ﻩ错误!未定义书签。

3.1.2 移相电路设计................................................................错误!未定义书签。

3.2 检测电路ﻩ错误!未定义书签。

3.2.1 方案分析ﻩ错误!未定义书签。

3.2.2 检测电路设计ﻩ错误!未定义书签。

3.2.3 LM339特性分析ﻩ错误!未定义书签。

3.2.4 双稳态触发器ﻩ错误!未定义书签。

3.3 计数显示电路................................................................错误!未定义书签。

3.3.1 方案分析ﻩ错误!未定义书签。

3.3.2 计数显示电路设计......................................................错误!未定义书签。

3.3.3 数码管工作原理ﻩ错误!未定义书签。

4 仿真与调试ﻩ错误!未定义书签。

5实验分析...................................................................................错误!未定义书签。

总结ﻩ错误!未定义书签。

参考文献ﻩ错误!未定义书签。

致谢ﻩ错误!未定义书签。

附录ﻩ错误!未定义书签。

相位差测量电路设计机电工程学院自动化专业指导老师:(讲师)摘要: 随着计算机以及电子技术的发展,相位差测量技术作为常用的信号测量技术,得到了快速发展,已经成为现代科学研究不可或缺的一部分。

相位检测在信号变换、信息采集、控制等方面有着重要的意义,特别是在电气、工业自动化、智能控制及通讯电子等许多领域都有广泛的应用。

因此,相位差测量技术在信号的处理、检测方面有着极其重要的作用。

为了满足本课题的要求,从相位差的测量方法入手,设计了一个相位差检测电路,该电路可测试一个经过移相电路的信号(正弦波)移相后与原信号间存在的相位差,可由测试电路检测并显示。

该设计主要包括三个方面的即移相电路设计、相位差测量电路设计、计数显示电路设计等。

其主要过程是将源信号为一个正弦波经过由两级RC移相器和电压跟随器组成的移相电路后,得到一个移相后的正弦波,两个信号输入相位差检测电路进行整形电路和获得源信号和移相后信号的相位差信号,最后输出相位差波形的宽度,即源信号的过零点与被测量信号的过零点之间的时间差。

然后再通过显示电路,最终由共阴极数码管显示出来。

关键词:相位差;移相电路;检测电路;计数显示电路;整形电路,Design of CircuitinPhaseDifferenceMeasurement (College of mechanical and electrical engineering,Huangshan University,245021) Abstract:With the development ofcomputer andelectronic technology,the phase difference measurement technology,as a common signal measurement technology,has been rapid development andhas bec omean indispensable part of modern scientific research.Phase detection is of great significancein terms of signal transformation, data collection,control,especiallyit is widely usedinmany fields ,such as electrical,industrial automation,intelligent controland communications, electronics and soon. Therefore, phase difference measurement technology plays averyimportant roleinsignal processinganddetection .In orderto meet the requirements of this subject,I designed a phase difference detectioncircuit starting from thephase difference measurement method.The circuit can test a after aphase shift circuitsignal (a sine wavephase shifter between the original signal and thephase difference canbe detected and display by the testcircui t.The design mainly includes three aspects:the phase shift circuit design, the phase difference measurement circuitdesign, the counting anddisplay circuitdesign, etc..Source after a sinewave by two stage RC phase shifter and voltagefollowerof phase-shift circuit,aphase shifting sinewave isthe main process,thetwo input signal phasedifference detection circuit shaping circuit and sourcesignal and phase signalphasedisparitysignal,finallyoutputphase differencewaveformwidth, namelysignal source ofzeroand measured signal zero crossi ng point between the timedifference. And thenthrough thedisplaycirc uit,andultimately by thecommoncathode digital tubedisplay.Key words: Phasedifference ; Detection circuit;Counting display circuit; Display circuit ; Plastic circuitﻬ1绪论1.1研究背景及意义随着微机和电子技术的快速发展,信号相位测量技术已成为现代科技社会不可缺少的一部分。

相位差测量在多方面有着重要意义,包括信息的采集、信号的检测和控制等等方面,特别是在电力行业、工业自动化、智能化和其他的通讯电子等方面有着广泛应用。

例如:(1)确定电路谐振特性。

当电路发生谐振时,该电路的L、C两端的电压相等但相位相反,所以两信号相互抵消,即可确定两个信号的相位为零。

因此,根据相位差来确定该电路是否发生谐振。

(2)测量信号的传输特性。

我们可以通过测量某个信号的幅频和相频的特性,然后根据以此来分析信号的传输特性。

(3)测量信号的延时特性。

通过测量信号的相位差,可以分析该信号的延时特性。

(4)测量和校正伺服系统。

伺服系统是自动控制的重要组成部分,因其电动机、解调器等都设计成响应于同相信号,故它需要经常测量信号的相位。

(5)测量功率因数。

如在交流电路中,功率因数是电压与电流之间相位差的余弦,用θcos是函数关系,因此可以通过使用相位差测量的方法, cos表示。

因为θ与θ先测得θ值后再计算θcos的值。

(6)测量距离和方向。

该功能应用非常的广泛,如相位式激光测距,其原理是通过发出连续的调制光波来回往返产生的相位延迟进行测量,间接的测量出光经过被测物体距离的时间,从而求出被测距离[1]。

由此可见,相位差测量技术广泛应用于医疗、勘探、电力、航空航天、石油冶金等多种领域。