开关电源PCB layout与电容电感设计

【最牛笔记】开关电源设计全过程!

【最⽜笔记】开关电源设计全过程!反激变换器设计笔记1、概述开关电源的设计是⼀份⾮常耗时费⼒的苦差事,需要不断地修正多个设计变量,直到性能达到设计⽬标为⽌。

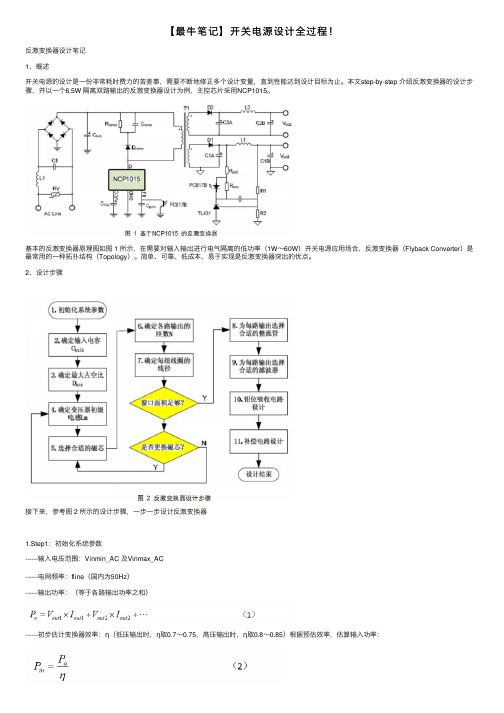

本⽂step-by-step 介绍反激变换器的设计步骤,并以⼀个6.5W 隔离双路输出的反激变换器设计为例,主控芯⽚采⽤NCP1015。

基本的反激变换器原理图如图 1 所⽰,在需要对输⼊输出进⾏电⽓隔离的低功率(1W~60W)开关电源应⽤场合,反激变换器(Flyback Converter)是最常⽤的⼀种拓扑结构(Topology)。

简单、可靠、低成本、易于实现是反激变换器突出的优点。

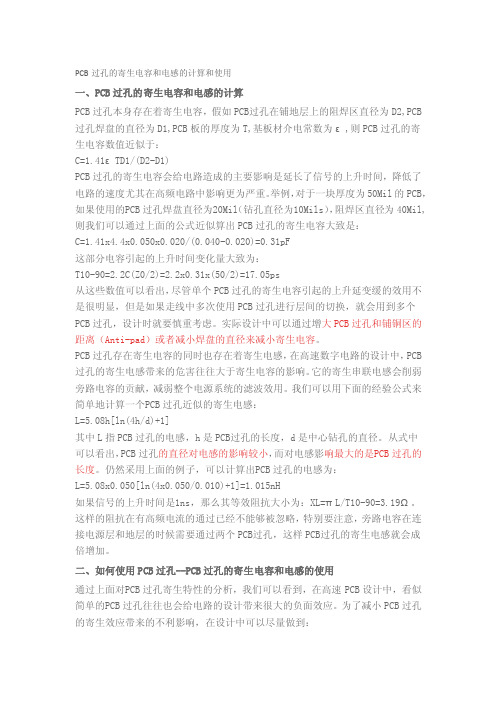

2、设计步骤接下来,参考图 2 所⽰的设计步骤,⼀步⼀步设计反激变换器1.Step1:初始化系统参数------输⼊电压范围:Vinmin_AC 及Vinmax_AC------电⽹频率:fline(国内为50Hz)------输出功率:(等于各路输出功率之和)------初步估计变换器效率:η(低压输出时,η取0.7~0.75,⾼压输出时,η取0.8~0.85)根据预估效率,估算输⼊功率:对多路输出,定义KL(n)为第n 路输出功率与输出总功率的⽐值:单路输出时,KL(n)=1.2. Step2:确定输⼊电容CbulkCbulk 的取值与输⼊功率有关,通常,对于宽输⼊电压(85~265VAC),取2~3µF/W;对窄范围输⼊电压(176~265VAC),取1µF/W 即可,电容充电占空⽐Dch ⼀般取0.2 即可。

⼀般在整流后的最⼩电压Vinmin_DC 处设计反激变换器,可由Cbulk 计算Vinmin_DC:3. Step3:确定最⼤占空⽐Dmax反激变换器有两种运⾏模式:电感电流连续模式(CCM)和电感电流断续模式(DCM)。

两种模式各有优缺点,相对⽽⾔,DCM 模式具有更好的开关特性,次级整流⼆极管零电流关断,因此不存在CCM 模式的⼆极管反向恢复的问题。

PCB过孔的寄生电容和电感

PCB过孔的寄生电容和电感的计算和使用一、PCB过孔的寄生电容和电感的计算PCB过孔本身存在着寄生电容,假如PCB过孔在铺地层上的阻焊区直径为D2,PCB 过孔焊盘的直径为D1,PCB板的厚度为T,基板材介电常数为ε,则PCB过孔的寄生电容数值近似于:C=1.41εTD1/(D2-D1)PCB过孔的寄生电容会给电路造成的主要影响是延长了信号的上升时间,降低了电路的速度尤其在高频电路中影响更为严重。

举例,对于一块厚度为50Mi l的PCB,如果使用的P CB过孔焊盘直径为20Mil(钻孔直径为10Mils),阻焊区直径为40Mil,则我们可以通过上面的公式近似算出PCB过孔的寄生电容大致是:C=1.41x4.4x0.050x0.020/(0.040-0.020)=0.31pF这部分电容引起的上升时间变化量大致为:T10-90=2.2C(Z0/2)=2.2x0.31x(50/2)=17.05ps从这些数值可以看出,尽管单个PC B过孔的寄生电容引起的上升延变缓的效用不是很明显,但是如果走线中多次使用PCB过孔进行层间的切换,就会用到多个PCB过孔,设计时就要慎重考虑。

实际设计中可以通过增大PCB过孔和铺铜区的距离(Anti-pad)或者减小焊盘的直径来减小寄生电容。

PCB过孔存在寄生电容的同时也存在着寄生电感,在高速数字电路的设计中,PCB 过孔的寄生电感带来的危害往往大于寄生电容的影响。

它的寄生串联电感会削弱旁路电容的贡献,减弱整个电源系统的滤波效用。

我们可以用下面的经验公式来简单地计算一个P CB过孔近似的寄生电感:L=5.08h[ln(4h/d)+1]其中L指PC B过孔的电感,h是PCB过孔的长度,d是中心钻孔的直径。

浅谈开关电源输出电感的设计

浅谈开关电源输出电感的设计――DC/DC 电路中电感的选择原文:Fairchild Semiconductor AB-12:Insight into Inductor Current 下载翻译:frm(注:只有充分理解电感在DC/DC电路中发挥的作用,才能更优的设计DC/DC电路。

本文还包括对同步DC/DC及异步DC/DC概念的解释。

)本文PDF文档下载简介在开关电源的设计中电感的设计为工程师带来的许多的挑战。

工程师不仅要选择电感值,还要考虑电感可承受的电流,绕线电阻,机械尺寸等等。

本文专注于解释:电感上的DC电流效应。

这也会为选择合适的电感提供必要的信息。

理解电感的功能电感常常被理解为开关电源输出端中的LC滤波电路中的L(C是其中的输出电容)。

虽然这样理解是正确的,但是为了理解电感的设计就必须更深入的了解电感的行为。

在降压转换中(Fairchild典型的开关控制器),电感的一端是连接到DC输出电压。

另一端通过开关频率切换连接到输入电压或GND。

在状态1过程中,电感会通过(高边“high-side”)MOSFET连接到输入电压。

在状态2过程中,电感连接到GND。

由于使用了这类的控制器,可以采用两种方式实现电感接地:通过二极管接地或通过(低边“low-side”)MOSFET接地。

如果是后一种方式,转换器就称为“同步(synchronus)”方式。

现在再考虑一下在这两个状态下流过电感的电流是如果变化的。

在状态1过程中,电感的一端连接到输入电压,另一端连接到输出电压。

对于一个降压转换器,输入电压必须比输出电压高,因此会在电感上形成正向压降。

相反,在状态2过程中,原来连接到输入电压的电感一端被连接到地。

对于一个降压转换器,输出电压必然为正端,因此会在电感上形成负向的压降。

我们利用电感上电压计算公式:V=L(dI/dt)因此,当电感上的电压为正时(状态1),电感上的电流就会增加;当电感上的电压为负时(状态2),电感上的电流就会减小。

如何一步一步设计开关电源?开关电源设计调试步骤全过程

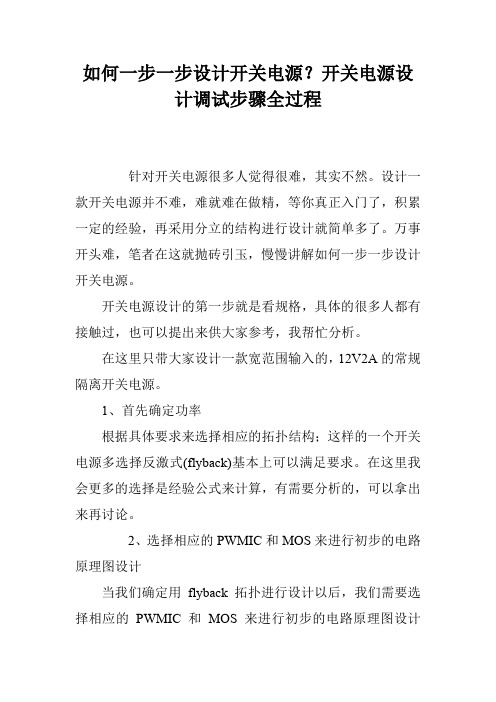

如何一步一步设计开关电源?开关电源设计调试步骤全过程针对开关电源很多人觉得很难,其实不然。

设计一款开关电源并不难,难就难在做精,等你真正入门了,积累一定的经验,再采用分立的结构进行设计就简单多了。

万事开头难,笔者在这就抛砖引玉,慢慢讲解如何一步一步设计开关电源。

开关电源设计的第一步就是看规格,具体的很多人都有接触过,也可以提出来供大家参考,我帮忙分析。

在这里只带大家设计一款宽范围输入的,12V2A的常规隔离开关电源。

1、首先确定功率根据具体要求来选择相应的拓扑结构;这样的一个开关电源多选择反激式(flyback)基本上可以满足要求。

在这里我会更多的选择是经验公式来计算,有需要分析的,可以拿出来再讨论。

2、选择相应的PWMIC和MOS来进行初步的电路原理图设计当我们确定用flyback拓扑进行设计以后,我们需要选择相应的PWMIC和MOS来进行初步的电路原理图设计(sch)。

无论是选择采用分立式的还是集成的都可以自己考虑。

对里面的计算我还会进行分解。

分立式:PWMIC与MOS是分开的,这种优点是功率可以自由搭配,缺点是设计和调试的周期会变长(仅从设计角度来说);集成式:就是将PWMIC与MOS集成在一个封装里,省去设计者很多的计算和调试分步,适合于刚入门或快速开发的环境。

3、做原理图确定所选择的芯片以后,开始做原理图(sch),在这里我选用STVIPer53DIP(集成了MOS)进行设计。

设计前最好都先看一下相应的datasheet,确认一下简单的参数。

无论是选用PI的集成,或384x或OBLD等分立的都需要参考一下datasheet。

一般datasheet里都会附有简单的电路原理图,这些原理图是我们的设计依据。

4、确定相应的参数当我们将原理图完成以后,需要确定相应的参数才能进入下一步PCBLayout。

当然不同的公司不同的流程,我们需要遵守相应的流程,养成一个良好的设计习惯,这一步可能会有初步评估,原理图确认,等等,签核完毕后就可以进行计算了。

开关电源的电磁干扰防制技术——传导篇

1 前言电源产品在做验证时,经常会遭遇到电磁干扰(EMI)的问题,有时处理起来需花费非常多的时间,许多工程师在对策电磁干扰时也是经验重于理论,知道哪个频段要对策那些组件,但对于理论上的分析却很欠缺。

笔者从事开关电源设计多年,希望能藉由之前对策的经验与相关理论基础做个整理,让目前正从事或未来想从事开关电源设计的人员对电磁干扰防制技术能有初步的认识。

开关电源的电磁干扰测试可分为传导测试与辐射测试,一般开关电源的传导测试频段是指150K~30MHz之间,而辐射干扰的频段是指30M~300MHz,300MHz之后的频段一般皆不是电源所产生,因此大都可以给予忽略。

下面内容章节包括开关电源的传导测试法规,测试与量测方式,基本概念,抑制传导干扰的滤波器设计,布线与变压器设计等章节。

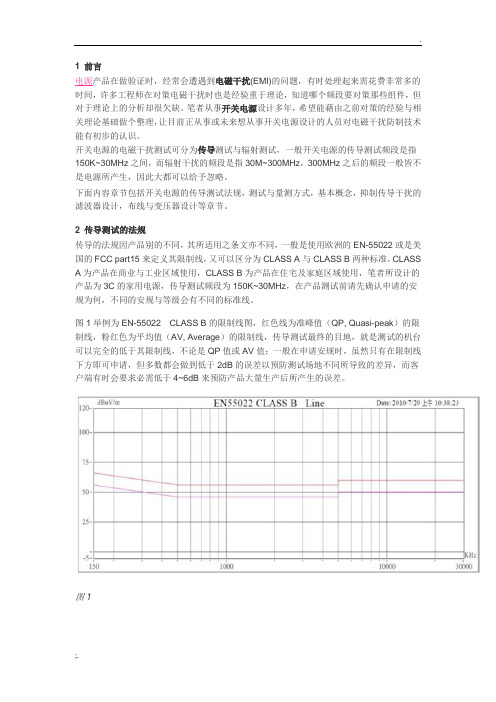

2 传导测试的法规传导的法规因产品别的不同,其所适用之条文亦不同,一般是使用欧洲的EN-55022或是美国的FCC part15来定义其限制线,又可以区分为CLASS A与CLASS B两种标准,CLASS A为产品在商业与工业区域使用,CLASS B为产品在住宅及家庭区域使用,笔者所设计的产品为3C的家用电源,传导测试频段为150K~30MHz,在产品测试前请先确认申请的安规为何,不同的安规与等级会有不同的标准线。

图1举例为EN-55022CLASS B的限制线图,红色线为准峰值(QP, Quasi-peak)的限制线,粉红色为平均值(AV, Average)的限制线,传导测试最终的目地,就是测试的机台可以完全的低于其限制线,不论是QP值或AV值;一般在申请安规时,虽然只有在限制线下方即可申请,但多数都会做到低于2dB的误差以预防测试场地不同所导致的差异,而客户端有时会要求必需低于4~6dB来预防产品大量生产后所产生的误差。

图1图2图2为一量测后的例子,一般量测时都会先用峰值量测,因峰值量测是最简单且快速的方法,量测仪器以9KHz为一单位,在150K~30MHz之间用保持最大值(maximum hold)的方式来得到传导的峰值读值,用此来确认电源的最大峰值然后再依此去抓最高峰值的实际QP,AV值来减少扫描时间,图2的蓝色曲线为准峰值的峰值量测结果,一般在峰值量测完后会再对较高的6个频率点做准峰值(QP)与平均值(AV)的量测,就如同图2所标示。

电容式触摸感应面板PCB Layout指南

电容式触摸面板PCB Layout 指南本文旨在为S-Touch T M 电容触摸感应设计所采用的各种PcB(印刷电路板)的结构和布局提供设计布局指导,包括触摸键,滑动条和旋转条。

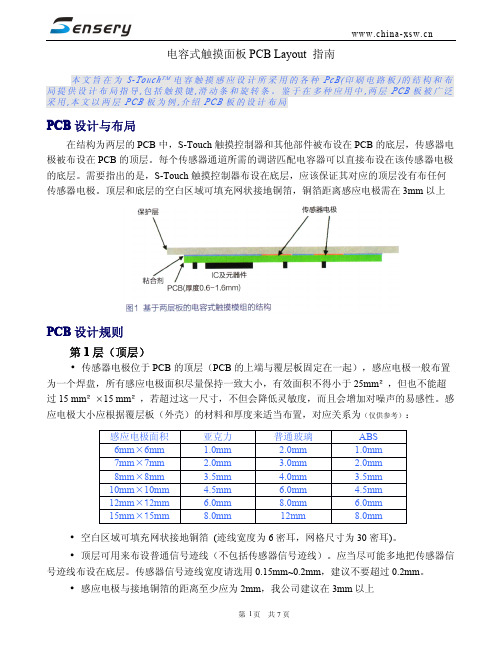

鉴于在多种应用中,两层PCB 板被广泛采用,本文以两层PCB 板为例,介绍PCB 板的设计布局PCB 设计与布局在结构为两层的PCB 中,S-Touch 触摸控制器和其他部件被布设在PCB 的底层,传感器电极被布设在PCB 的顶层。

每个传感器通道所需的调谐匹配电容器可以直接布设在该传感器电极的底层。

需要指出的是,S-Touch 触摸控制器布设在底层,应该保证其对应的顶层没有布任何传感器电极。

顶层和底层的空白区域可填充网状接地铜箔,铜箔距离感应电极需在3mm 以上PCB 设计规则第1层(顶层)•传感器电极位于PCB 的顶层(PCB 的上端与覆层板固定在一起),感应电极一般布置为一个焊盘,所有感应电极面积尽量保持一致大小,有效面积不得小于25mm ²,但也不能超过15mm ²×15mm ²,若超过这一尺寸,不但会降低灵敏度,而且会增加对噪声的易感性。

感应电极大小应根据覆层板(外壳)的材料和厚度来适当布置,对应关系为(仅供参考):空白区域可填充网状接地铜箔(迹线宽度为6密耳,网格尺寸为30密耳)。

•顶层可用来布设普通信号迹线(不包括传感器信号迹线)。

应当尽可能多地把传感器信号迹线布设在底层。

传感器信号迹线宽度请选用0.15mm~0.2mm ,建议不要超过0.2mm 。

•感应电极与接地铜箔的距离至少应为2mm ,我公司建议在3mm 以上感应电极面积亚克力普通玻璃ABS 6mm ×6mm 1.0mm 2.0mm 1.0mm 7mm ×7mm 2.0mm 3.0mm 2.0mm 8mm ×8mm 3.5mm 4.0mm 3.5mm 10mm ×10mm 4.5mm 6.0mm 4.5mm 12mm ×12mm 6.0mm 8.0mm 6.0mm 15mm ×15mm8.0mm12mm8.0mm第2层(底层)•传S-Touch控制器和其他无源部件应该设计布局在底层。

(完整版)反激式开关电源的设计方法

1 设计步骤:1.1 产品规格书制作1.2 设计线路图、零件选用.1.3 PCB Layout.1.4 变压器、电感等计算.1.5 设计验证.2 设计流程介绍:2.1 产品规格书制作依据客户的要求,制作产品规格书。

做为设计开发、品质检验、生产测试等的依据。

2.2 设计线路图、零件选用。

2.3 PCB Layout.外形尺寸、接口定义,散热方式等。

2.4 变压器、电感等计算.变压器是整个电源供应器的重要核心,所以变压器的计算及验证是很重要的,2.4.1 决定变压器的材质及尺寸:依据变压器计算公式Gauss x NpxAeLpxIp B 100(max ) ➢ B(max) = 铁心饱合的磁通密度(Gauss)➢ Lp = 一次侧电感值(uH)➢ Ip = 一次侧峰值电流(A)➢ Np = 一次侧(主线圈)圈数➢ Ae = 铁心截面积(cm 2)➢B(max) 依铁心的材质及本身的温度来决定,以TDK FerriteCore PC40为例,100℃时的B(max)为3900 Gauss ,设计时应考虑零件误差,所以一般取3000~3500 Gauss 之间,若所设计的power 为Adapter(有外壳)则应取3000 Gauss 左右,以避免铁心因高温而饱合,一般而言铁心的尺寸越大,Ae 越高,所以可以做较大瓦数的Power 。

2.4.2 决定一次侧滤波电容:滤波电容的决定,可以决定电容器上的Vin(min),滤波电容越大,Vin(win)越高,可以做较大瓦数的Power ,但相对价格亦较高。

2.4.3 决定变压器线径及线数:变压器的选择实际中一般根据经验,依据电源的体积、工作频率,散热条件,工作环境温度等选择。

当变压器决定后,变压器的Bobbin 即可决定,依据Bobbin 的槽宽,可决定变压器的线径及线数,亦可计算出线径的电流密度,电流密度一般以6A/mm 2为参考,电流密度对变压器的设计而言,只能当做参考值,最终应以温升记录为准。

开关电源制作设计(电路原理图+PCB)

一、工作原理我们先熟悉一款开关电源的工作原理,该电源可输出5V电压,如图1所示。

1. 抗干扰电路在电网输入端首先设置一个NTC5D-9负温度系数热敏电阻,作用是保护后面的整流桥,刚开机时热敏电阻处于冷态,阻值比较大,可以限制输入电流,正常工作时,电阻比较小。

这样对开机时的浪涌电流起到有效的缓冲作用。

电容CY1、CY2、CY3、CY4用以滤除从工频电网上进入开关稳压电源和从开关稳压电源进入工频电网的不对称杂散信号,电容CX1、CX2用以滤除从工频电网上进入开关稳压电源和从开关稳压电源进入工频电网的对称杂散信号,用电感L1抑制从工频电网上进入开关稳压电源和从开关稳压电源进入工频电网的频率相同、相位相反的杂散干扰电流信号。

采用高频特性好的瓷片电容和铁芯电感,实现开关稳压电源电路中的高频辐射不污染工频电网和工频电网上的杂散电磁波不会窜入开关稳压电源电路中而干扰和影响其工作,对高频分量或工频的谐波分量具有急剧阻止通过功能,而对于几百赫兹以下的低频分量近似一条短路线。

图1 开关电源的工作原理图2. 整流滤波电路在电路中D1、D2、D3、D4组成全桥整流电路,把输入的交流电压进行全波整流,然后用C1进行滤波,最后变成直流输出供电电压,为后级的功率变换器供电,整流滤波后的电压约为300V。

3. UC3842供电与振荡300V的脉动直流电压,此电压经R12降压后给C4充电,供电UC3842的7脚,当C4的电压达到UC3842的启动电压门槛值时,UC3842开始工作并提供驱动脉冲,由6脚输出推动开关管工作。

一旦开关管工作,反馈绕组的能量经过D6整流,C4滤波,又供电到UC3842的7脚,这时可以不需要R12的启动了。

C9、R11接UC3842的定时端,和内部电路构成振荡电路,振荡的工作频率计算为:f=1.8/(Rt*Ct)代入数据可计算工作频率:f=68.18K4. 稳压电路该电路主要由精密稳压源T L 4 3 1 和线性光耦P C 8 1 7 组成,假设输出电压↑→经过R 1 6 、R 1 9 、R20、RES3的取样电压↑→TL431的1脚电压↑,当该脚电压大于TL431的基准电压2.5V时,TL431的2、3脚导通,→通过光电耦合到UC3842的2脚,于是UC3842的6脚驱动脉冲的占空比↓→开关变压器T1绕组上的能量↓→输出电压↓,达到稳压作用;反之,假设输出电压下降,则稳压过程与上相反。

开关电源PCB设计实例

开关电源PCB设计实例标签:开关电源PCB印制电路板的制作所有开关电源设计的最后一步就是印制电路板(PCB)的线路设计。

如果这部分设计不当,PCB也会使电源工作不稳定,发射出过量的电磁干扰(EMI)。

设计者的作用就是在理解电路工作过程的基础上,保证PCB设计合理。

开关电源中,有些信号包含丰富的高频分量,因而任何一条PCB引线都可能成为天线。

引线的长和宽影响它的电阻和电感量,进而关系到它们的频率响应。

即使是传送直流信号的引线,也会从邻近的引线上引入RF(射频)信号,使电路发生故障,或者把这干扰信号再次辐射出去。

所有传送交流信号的引线要尽可能短且宽。

这意味着任何与多条功率线相连的功率器件要尽可能紧挨在一起,以减短连线长度。

引线的长度直接与它的电感量和电阻量成比例,它的宽度则与电感量和电阻量成反比。

引线长度就决定了其响应信号的波长,引线越长,它能接收和传送的干扰信号频率就越低,它所接收到的RF(射频)能量也越大。

主要电流环路每一个开关电源内部都有四个电流环路,每个环路要与其他环路分开。

由于它们对PCB布局的重要性,下面把它们列出来:1.功率开关管交流电流环路。

2.输出整流器交流电流环路。

3.输入电源电流环路。

4.输出负载电流环路。

图59a、b、c画出了三种主要开关电源拓扑的环路。

通常输入电源和负载电流环路并没有什么问题。

这两个环路上主要是在直流电流上叠加了一些小的交流电流分量。

它们一般有专门的滤波器来阻止交流噪声进入周围的电路。

输入和输出电流环路连接的位置只能是相应的输入输出电容的接线端。

输入环路通过近似直流的电流对输入电容充电,但它无法提供开关电源所需的脉冲电流。

输入电容主要是起到高频能量存储器的作用。

类似地,输出滤波电容存储来自输出整流器的高频能量,使输出负载环能以直流方式汲取能量。

因此,输入和输出滤波电容接线端的放置很重要。

如果输入或输出环与功率开关或整流环的连接没有直接接到电容的两端,交流能量就会从输入或输出滤波电容上流进流出,并通过输入和输出电流环“逃逸”到外面环境中。

开关电源PCB设计要点及实例分析

开关电源PCB设计要点及实例分析开关电源PCB设计要点及实例分析开关电源PCB设计要点及实例分析为了适应电子产品飞快的更新换代节奏,产品设计工程师更倾向于选择在市场上很容易采购到的AC/DC适配器,并把多组直流电源直接安装在系统的线路板上。

由于开关电源产生的电磁干扰会影响到其电子产品的正常工作,正确的电源PCB设计就变得非常重要。

开关电源PCB设计与数字电路PCB设计完全不一样。

在数字电路排版中,许多数字芯片可以通过PCB软件来自动排列,且芯片之间的连接线可以通过PCB软件来自动连接。

用自动排版方式排出的开关电源肯定无法正常工作。

所以,设计人员需要对开关电源PCB设计基本规则和开关电源工作原理有一定的了解。

1 开关电源PCB设计基本要点1.1 电容高频滤波特性图1是电容器基本结构和高频等效模型。

图1 电容器结构和寄生等效串联电阻和电感电容的基本公式是C=Εrε0 (1)式(1)显示,减小电容器极板之间的距离(D)和增加极板的截面积(A)将增加电容器的电容量。

电容通常存在等效串联电阻(ESR)和等效串联电感(ESL)二个寄生参数。

图2是电容器在不同工作频率下的阻抗(ZC)。

图2 电容阻抗(ZC)曲线一个电容器的谐振频率(F0)可以从它自身电容量(C)和等效串联电感量(LESL)得到,即F0= (2)当一个电容器工作频率在F0以下时,其阻抗随频率的上升而减小,即ZC= (3)当电容器工作频率在F0以上时,其阻抗会随频率的上升而增加,即ZC=J2πfLESL(4)当电容器工作频率接近F0时,电容阻抗就等于它的等效串联电阻(RESR)。

电解电容器一般都有很大的电容量和很大的等效串联电感。

由于它的谐振频率很低,所以只能使用在低频滤波上。

钽电容器一般都有较大电容量和较小等效串联电感,因而它的谐振频率会高于电解电容器,并能使用在中高频滤波上。

瓷片电容器电容量和等效串联电感一般都很小,因而它的谐振频率远高于电解电容器和钽电容器,所以能使用在高频滤波和旁路电路上。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电容 10uF/10V 瓷片 100uF/10V 钽

ESR 4m 46 m

ESL 1.25nH 3nH 15nH

470uF/10V 电解 100 m

电容并联高频特性

电源步板基本要点之一:旁路瓷片 电源步板基本要点之一 电容的电容量不易太大, 而它的寄 生串联电感量应该尽量减小。多个 电容并联能改善单个电容的阻抗特 性。最小容量的瓷片电容应最靠近 负载。

输出滤波电容电路分析

PSPICE AC模拟 (图A) 瞬态模拟 (图 B) 运用直流电路分析方式:

∆I 1 = ∆I 2 =

R2 10 ∆I L = ⋅ 4.2 = 1.4 A R1 + R 2 20 + 10 R1 20 ∆I L = ⋅ 4.2 = 2.8 A R1 + R 2 20 + 10

电感寄生电容影响

在理想状态下电感( 〕和电容( 在理想状态下电感(L〕和电容(COUT〕将 VD 谐波全滤掉 VOUT 只剩下直流和极小的一次谐波

电感寄生电容影响

L

V1 V2

10uH

C1

100uF

V1 = 0 V2 = 12 TD = 100us TR = 10ns TF = 10ns PW = 0.45us PER = 1.67us

∆VOUT = ∆I C 1 Z C 1 = 4.05 A ⋅ 20 mΩ = 81mV

输出滤波电容电路分析

计算和模拟结果 fS @ 300KHz ZC1 ZC2 ∆ IC1 ∆ IC2 ∆ VOUT ∆ VOUT (PSPICE 模拟) 1颗 1µF 1颗 10µF 2颗 10µF 20 m 530 m 4.05 A 0.15 A 81 mV 83 mV 20 m 53 m 3.05 A 1.15 A 61 mV 63 mV 20 m 27 m 2.41 A 1.79 A 48 mV 50 mV 3颗 10µF 20 m 18 m 2.00 A 2.20 A 40 mV 42 mV

电感寄生电容影响

C3 470pF 100pF C6

L

V1 V3 0A

L3 V2 1uH C4

10uH

C1

100uF

V1 = 0 V2 = 12 TD = 100us TR = 10ns TF = 10ns PW = 0.45us PER = 1.67us L1 10nH 0A

C2

10uF

10uF

Resr1

4π 3 ⋅ 10

2

(

1

5 2

) (6 ⋅ 10 )

−3 2

≈ 20 mΩ

ZC2 =

(0.01)2 +

4π 3 ⋅ 10

2

(

1

5 2

) (1 ⋅ 10 )

−6 2

≈ 530 mΩ

∆I C 1 =

ZC2 530 ∆I L = ⋅ 4.2 A = 4.05 A Z C1 + Z C 2 20 + 530

焊盘(PAD)和旁路电容的放置 焊盘(PAD)和旁路电容的放置 (PAD)

焊盘

旁路电容

降压式电源排版的例子

电源排版基本要点之九: 电源排版基本要点之九:

功率器件所组成的电流环路面积要小。

降压式电源排版的例子

电源排版基本要点之十: 电源排版基本要点之十:

功率器件接功率地 信号器件接信号地 功率地与信号地单点连接 (一根很短导线或一个或多个过孔)

C EQ = 2C 1 = 2C 2

REQ = R1 R 2 = 2 2

如有 n 颗同一电容并联, 并联后的 CEQ 和 REQ 为:

CEQ = nC

REQ =

RESR n

重新分析由四颗 1500µF 电解电容 (C1) 和一颗 1µF瓷片电容 (C2) 所组 成的输出滤波电路:

Z C1 =

(0.02 )2 +

Part II. Output Capacitor Design Ripple Voltage Analysis

高频输出瓷片电容 高频输出瓷片电容特性 输出瓷片电

-Y5V 电容值随工作电压而变化大 -Y5V ESR值随工作电压而变化大 -Y5V 电容值随温度而变化大

高频输出瓷片电容 高频输出瓷片电容特性 输出瓷片电

当输出瓷片电容由一颗增加到三颗,输出纹波电压值 (∆VOUT) 被稳定地 控制在 50 mV 以下。通过公式计算出来的∆VOUT 为 40 mV,而通过 PSPICE 模拟计算出来的∆VOUT 是 42 mV。

输出滤波电容电路分析

PSPICE 模拟电路图 (A) 四颗 1500 µF 电解和一颗 10µF 瓷片并联

10uF/10V Y5V 与 1uF/10V X7R 性能相差不大

输出滤波电容电路分析

∆VESR = RESRδI OUT

(1) (2) (3) (4) 四颗1500µF,80m 电解电容 并联后电容值是6000 µF,ESR 是 20 m 电感纹波电流 (∆IL) 为 4.2A,输出纹波电压 84 mV (80 x 4.2 / 4) 能不能并联一个或多个瓷片电容来减小输出电压纹波值?

C2

10uF

Resr1

20m

Resr2

4m

RL

3.3

Vphase

L1 10nH

0A

L2 1nH

0A

0

在理想状态下电感( 〕和电容( 在理想状态下电感(L〕和电容(COUT〕将 VD 谐波全滤掉 VOUT 只剩下直流和极小的一次谐波 (fs = 600KHz)

电感寄生电容影响

C3 470pF

L

V1 V2

(B) 四颗 1500 µF 电解和二颗 10µF 瓷片并联

(C) 四颗1500 µF 电解和三颗10µF 瓷片并联

Part III. Inductor Capacitance Effect on VDSL

xDSL 传播速度图

ADSL/ADSL2 可选用开关频率大于 1.1MHz 的电源稳压器 ADSL2+可选用开关频率大于 2.2MHz 的电源稳压器 + VDSL 必须减小 20MHz 以下输出电压噪音

电感模型

Ac: 电流环路截面结 Lm: 电流环路周长

L: 电感值 EPR: 等效并联电阻 Cp: 等效并联电感

电感特性

电感特性

电源步板基本要点之二:电感的 电源步板基本要点之二 寄生串联电容量应该尽量减小。 电感引脚之间的距离越远越好。

镜象面概念

电源步板基本要点之三: 电源步板基本要点之三 避免在地层上放置任何功 率或信号走线。

f0 =

ZC =

1 2π C ⋅ LESL

−1 j 2πfC

Z C = j 2πf ⋅ LESL

Z C = RESR

电容参数

封装 瓷片电容 0603 0805 1206 1210 钽电容 0805 1206 1411 2412 电解电容 表面贴 引脚 6.8 >10 1.6 2.2 2.3 2.8 0.8 1.0 1.2 1.0 典型电感值 (nH)

20m

Resr2

4m

0A

Resl3 4m

RL

3.3

Vphase

L2 1nH 0A

L4 1nH 0A

0

总结:

VDSL 需要二次滤波器来消除由电感寄生电容在 20MHz 内所产生的噪音

Thank You

2

并联后的 CEQ 和 REQ 为:

Z EQ = Z C1Z C 2 = REQ Z C1 + Z C 2 1 + 2πfC EQ

2

(R1 + R 2 )2 (2πf )2 C12 C 2 2 + (C1 + C 2 )2 C EQ = (R12 C1 + R2 2 C 2)(2πf )2 C1C 2 + (C1 + C 2)

REQ R1R 2(R1 + R 2 )(2πf ) C12 C 2 2 + R1C12 + R2C 2 2 = (R1 + R2 )2 (2πf )2 C12 C 2 2 + (C1 + C 2)2

2

(

)

输出滤波电容电路分析

当 C1 = C2 和 R1 = R2,CEQ 和 REQ 才与频率无关。此时:

10uH

C1

100uF

V1 = 0 V2 = 12 TD = 100us TR = 10ns TF = 10ns PW = 0.45us PER = 1.67us L1 10nH 0A

C2

10uF

Resr1

20m

Resr2

4m

RL

3.3

Vphase

L2 1nH A

0

具有寄生电容的电感( 〕和电容( 具有寄生电容的电感(L〕和电容(COUT〕无法将 VD 谐波全滤掉

降压式 电源: 降压式(BUCK)电源:功率部分电流和电压波形 电源

降压式电源排版差的例子

电路等效图

Minimize These Inductances

PCB Trace - Via 电感估算

PCB Trace 长 1 inch (2.54cm), PCB 层厚 0.1mm PCB Trace 约为20nH/inch

高频交流电流环路

电源步版基本要点之四: 电源步版基本要点之四 高频交流环路的面积应该尽量减小。

过孔 (VIA) 的例子

电源步版基本要点之五: 电源步版基本要点之五: 过孔放置不应破坏高频交流电流在地层上路径。

PCB板层分割 板层分割

电源步版基本要点之六: 电源步版基本要点之六: 摸拟电源层与数字地层不应有重叠。 信号层应有相应的地层。

Power Supply PCB Layout/Output Capacitor Design