EDA技术和VHDL设计第5章 VHDL基本语句.ppt

2023年大学_EDA技术与VHDL第二版(潘松著)课后习题答案下载

2023年EDA技术与VHDL第二版(潘松著)课后习题答案下载EDA技术与VHDL第二版(潘松著)课后答案下载第1章 EDA技术概述1.1 EDA技术及其发展1.1.1 EDA技术的发展1.1.2 EDA技术的涵义1.1.3 EDA技术的基本特征1.2 EDA技术的主要内容及主要的EDA厂商1.2.1 EDA技术的主要内容1.2.2 主要EDA厂商概述1.3 EDA技术实现目标1.3.1 超大规模可编程逻辑器件1.3.2 半定制或全定制ASIC1.3.3 混合ASIC1.4 EDA技术应用1.4.1 EDA技术应用形式1.4.2 EDA技术应用场合1.5 EDA技术的发展趋势1.5.1 可编程器件的发展趋势1.5.2 软件开发工具的发展趋势1.5.3 输入方式的发展趋势__小结思考题和习题第2章大规模可编程逻辑器件2.1 可编程逻辑器件概述2.1.1 PLD的'发展进程2.1.2 PLD的种类及分类方法2.2 简单可编程逻辑器件2.2.1 PLD电路的表示方法及有关符号 2.2.2 PROM基本结构2.2.3 PLA基本结构2.2.4 PAL基本结构2.2.5 GAL基本结构2.3 复杂可编程逻辑器件2.3.1 CPLD基本结构2.3.2 Altera公司器件2.4 现场可编程逻辑器件2.4.1 FPGA整体结构2.4.2 Xilinx公司FPGA器件2.5 在系统可编程逻辑器件2.5.1 ispLSl/pLSl的结构2.5.2 Lattice公司ispLSI系列器件 2.6 FPGA和CPLD的开发应用2.6.1 CPLD和FPGA的编程与配置2.6.2 FPGA和CPLD的性能比较2.6.3 FPGA和CPLD的应用选择__小结思考题和习题第3章 EDA设计流程与开发3.1 EDA设计流程3.1.1 设计输入3.1.2 综合3.1.3 适配3.1.4 时序仿真与功能仿真3.1.5 编程下载3.1.6 硬件测试3.2 ASIC及其设计流程3.2.1 ASIC设计方法3.2.2 一般的ASIC设计流程3.3 可编程逻辑器件的开发环境 3.4 硬件描述语言3.5 IP核__小结思考题和习题第4章硬件描述语言VHDL4.1 VHDL概述4.1.1 VHDL的发展历程4.1.2 VHDL的特点4.2 VHDL程序基本结构4.2.1 实体4.2.2 结构体4.2.3 库4.2.4 程序包4.2.5 配置4.3 VHDL基本要素4.3.1 文字规则4.3.2 数据对象4.3.3 数据类型4.3.4 运算操作符4.3.5 VHDL结构体描述方式 4.4 VHDL顺序语句4.4.1 赋值语句4.4.2 IF语句4.4.3 等待和断言语句4.4.4 cASE语句4.4.5 LOOP语句4.4.6 RETIARN语句4.4.7 过程调用语句4.4.8 REPORT语句4.5 VHDL并行语句4.5.1 进程语句4.5.2 块语句4.5.3 并行信号代人语句4.5.4 并行过程调用语句4.5.5 并行断言语句4.5.6 参数传递语句4.5.7 元件例化语句__小结思考题和习题第5章 QuartusⅡ软件及其应用5.1 基本设计流程5.1.1 建立工作库文件夹和编辑设计文件 5.1.2 创建工程5.1.3 编译前设计5.1.4 全程编译5.1.5 时序仿真5.1.6 应用RTL电路图观察器5.2 引脚设置和下载5.2.1 引脚锁定5.2.2 配置文件下载5.2.3 AS模式编程配置器件5.2.4 JTAG间接模式编程配置器件5.2.5 USBBlaster编程配置器件使用方法 __小结思考题和习题第6章 VHDL应用实例6.1 组合逻辑电路设计6.1.1 基本门电路设计6.1.2 译码器设计6.1.3 数据选择器设计6.1.4 三态门设计6.1.5 编码器设计6.1.6 数值比较器设计6.2 时序逻辑电路设计6.2.1 时钟信号和复位信号6.2.2 触发器设计6.2.3 寄存器和移位寄存器设计6.2.4 计数器设计6.2.5 存储器设计6.3 综合实例——数字秒表的设计__小结思考题和习题第7章状态机设计7.1 一般有限状态机7.1.1 数据类型定义语句7.1.2 为什么要使用状态机 7.1.3 一般有限状态机的设计 7.2 Moore型有限状态机设计 7.2.1 多进程有限状态机7.2.2 单进程有限状态机7.3 Mealy型有限状态机7.4 状态编码7.4.1 状态位直接输出型编码 7.4.2 顺序编码7.4.3 一位热码编码7.5 状态机处理__小结思考题和习题第8章 EDlA实验开发系统8.1 GW48型实验开发系统原理与应用8.1.1 系统性能及使用注意事项8.1.2 GW48系统主板结构与使用方法8.2 实验电路结构图8.2.1 实验电路信号资源符号图说明8.2.2 各实验电路结构图特点与适用范围简述8.3 GW48CK/GK/EK/PK2系统信号名与芯片引脚对照表 __小结思考题和习题第9章 EnA技术实验实验一:全加器的设计实验二:4位加减法器的设计实验三:基本D触发器的设计实验四:同步清零计数器的设计实验五:基本移位寄存器的设计串人/串出移位寄存器实验六:同步预置数串行输出移位寄存器的设计实验七:半整数分频器的设计实验八:音乐发生器的设计实验九:交通灯控制器的设计实验十:数字时钟的设计EDA技术与VHDL第二版(潘松著):内容简介《EDA技术与VHDL》主要内容有Altera公司可编程器件及器件的选用、QuartusⅡ开发工具的使用;VHDL硬件描述语言及丰富的数字电路和电子数字系统EDA设计实例。

集成电路设计的EDA系统.pptx

第12页/共75页

逻辑模拟

• 逻辑模拟的基本概念:将逻辑设计输入到计算机,用软件方法形成硬件的模型, 给定输入波形,利用模型算出各节点和输出端的波形,判断正确否

• 主要作用:验证逻辑功能和时序的正确性

• 分类:根据所模拟逻辑单元规模的大小

• 整个设计过程就是把高层次的抽象描述逐级向下进行综合、验证、实现,直到物理级的低层次描述,即掩 膜版图。

• 各设计阶段相互联系,例如,寄存器传输级描述是逻辑综合的输入,逻辑综合的输出又可以是逻辑模拟和 自动版图设计的输入,版图设计的结果则是版图验证的输入。

• ICEDA系统介入了包括系统功能设计、逻辑和电路设计以及版图设计等在内的集成电路设计的各个环节

• 分配:给定性能、面积/功耗条件下,确定相应的RTL级单元来实现各种操 作,产生相应的数据通道,即将行为(如数据处理、存储、传输等)与元件 对应起来

• 调度:确定这些操作单元的次序 • 结果:与工艺无关的通用RTL级单元组成的结构描述

第8页/共75页

逻辑综合

• 概念:通过逻辑综合器结合单元库,将RTL级描述转换成逻辑级描述 • 核心:由给定的功能和性能要求,在一个包含许多结构、功能、性能已知的逻辑

• VHDL • Verilog HDL

第6页/共75页

综合

• 概念:通过附加一定的约束条件,结合相应的单元库,从设计的高层次向低层 次转换的过程,是一种自动设计的过程

• 分类: • 高级综合:从算法级到寄存器传输(RTL)级 • 逻辑综合:从寄存器传输级到逻辑级

第7页/共75页

高级综合

• 概念:结合RTL级单元库,将算法级描述转换成RTL级描述 • 核心:分配(ALLOCATION)和调度(SCHEDULING)

EDA技术与VHDL实用教程(第2版)电子课件 第1章EDA技术概述

2.计算机辅助工程设计CAE阶段

各种设计工具,如原理图输入、编译与 连接、逻辑模拟、测试码生成、版图自动布 局以及各种单元库均已齐全。由于采用了统 一数据管理技术,因而能够将各个工具集成 为一个CAE系统。

EDA技术与VHDL实用教程

作者: 苏莉萍 陈东 廖超平

3.电子系统设计自动化ESDA阶段

EDA技术与VHDL实用教程

作者: 苏莉萍 陈东 廖超平

三、 面向FPGA/CPLD的常用EDA工具

可编程逻辑器件PLD(Programmable Logic Device)是一种可根据用户需要而自行构造逻辑功 能的逻辑器件。目前主要有两大类型:CPLD( Complex PLD)和FPGA(Field Programmable Gate Array)。借助于EDA工具软件,用原理图、硬件描 述语言等设计输入法,可设计生成相应的目标文件 ,最后用编程器下载到目标器件实现用户需要的逻 辑功能。生产PLD的厂家很多,但最有代表性的PLD 厂家为Altera、Xilinx和Lattice公司。

EDA技术与VHDL实用教程

作者: 苏莉萍 陈东 廖超平

1. ALTERA 其原先的开发工具MAX+PLUS II是较成功的PLD 开发平台,现在使用Quartus II开发软件。

2. XILINX 开发软件为Foundation和ISE。

3. Lattice-Vantis 开发工具ispLEVER比Altera和Xilinx略逊一筹。

EDA技术与VHDL实用教程

作者: 苏莉萍 陈东 廖超平

1. ALTERA 其原先的开发工具MAX+PLUS II是较成功的PLD 开发平台,现在使用Quartus II开发软件。

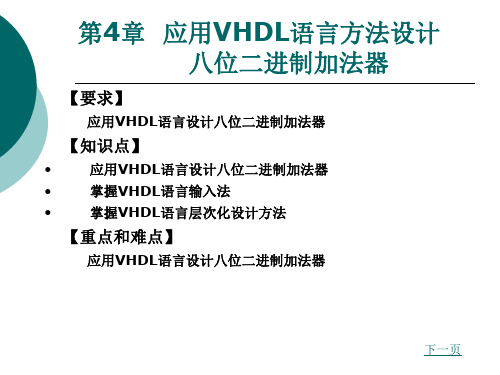

第4章 应用VHDL语言方法设计八位二进制加法器 《EDA技术》PPT 教学课件

对所设计的八位二进制加法器的各个底层模块和顶层模块进行编译 仿真,以验证所设计电路否符合设计的要求。

上一页 下一页

§2 完成工作任务的引导

六、评估

应用第一种方案设计八位二进制加法器在编译后,可以看到它的 延时情况,如图4-1所示。

第一种设计方案占用资源的情况如图4-2所示。 应用第一种方案设计八位二进制加法器在编译后,可以看到它的 延时情况,如图4-3所示。 第一种设计方案占用资源的情况如图4-4所示。 所以,无论从输出信号对输入信号的延迟时间或占用资源的情况 来看,第一种方案性能都好一些。

返回

§4.2 完成工作任务的引导

第三种方案在设计上不是很简单,但性能好,在加法器的位数比 较大时应采用此法。可在学习第5章时再做练习。

四、实施

在应用第一种方案设计时,请参考下一节例4.1或例4.2。先设计 底层模块全加器,再在顶层文件中调用全加器元件,构成八位二进制 加法器。在应用第一种方案设计时,请参考下一节例4.3。

上一页 下一页

§4.3 相关技术基础知识与基本技能

对于弹出的选择其他EDA工具的对话框,由于我们使用 Quartus且的集成环境进行开发,因此不需做任何改动。单击Next 按钮进入如图4-11所示工程的信息总概对话框。

在图4-11中单击Finish按钮就建立了一个空的工程项目。 2.建立VHDL文件

如图4-12所示,执行File=>New命令,弹出如图4-13所示的 新建文件对话框。

在新建文件对话框中选择“VHDL File”,单击OK按钮即建立一 个空的文件。执行File=>SaVe as命令,把它另存为文件名是 fulladd 的 VHDL文件,文件后缀为.vhd。

上一页 下一页

配套课件 EDA技术与VHDL程序设计基础教程

它支持原理图、VHDL和Verilog 语言文本输入方式和波形或EDIF 格式的文件作为输入,且支持这 些文件的混合设计。

Quartus II的GUI界面

EDA技术与VHDL程序开发基础教程

五、EDA集成开发工具

ISE+ModelSim

ispLEVER

EDA技术与VHDL程序开发基础教程

。(b)中三条竖线A、B、C也为输入线,输入到或门的横线为和线。和线与

输入线的交叉点为编程点。

当输入线与和线相连通时,

在编程点处以“×”表示。

Y=AB

可以看出,图中电路表示

Y=A+B+C

的逻辑表达式分别为Y=AB

和Y=A+B+C。

ABC

ABC

(a)

(b)

EDA技术与VHDL程序开发基础教程

三、 CPLD的基本结构和工作原理

EDA技术与VHDL程序开发基础教程

第1章 EDA概述

重点内容:

EDA技术发展和应用 EDA工程设计流程 EDA集成开发工具

EDA技术与VHDL程序开发基础教程

一、EDA工程简介

EDA(Electronic Design Automation)工程是现代电子信息工程领 域中一门发展迅速的新技术。

流程

需求分析

算法设计 (Algorithm Optimization)

构架设计 (Architecture Exploration)

RTL 设计 (RTL Design)

RTL 验证 (RTL Verification)

综合 (Synthesis)

门级验证 (Gate-level Verification)

《EDA技术与VHDL》 选择题

一、VHDL基本结构1. 一个项目的输入输出端口是定义在A. 实体中B. 结构体中C. 任何位置D. 进程中2. 描述项目逻辑功能的是A. 实体B. 结构体C. 配置D. 进程3. 关键字ARCHITECTURE定义的是A. 结构体B. 进程C. 实体D. 配置4.VHDL语言共支持四种常用库,其中哪种库是用户的VHDL设计现行工作库:A.IEEE库B.VITAL库C.STD库D.WORK工作库5. VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述是A.器件外部特性;B.器件的内部功能;C.器件的综合约束;D.器件外部特性与内部功能。

6. 在VHDL中,库可以包含一个或多个A. 程序包B. 结构体C. 输入D. 输出7. 一个能为VHDL综合器接受,并能作为一个独立的设计单元的完整的VHDL程序成为A.设计输入 B. 设计输出 C. 设计实体 D. 设计结构8. Q为输出信号,但内部设计会用到其反馈信号,其正确的端口说明是:A. Q:IN BIT;B. Q:OUT BIT;C. Q:INOUT BIT;D. Q:BUFFER BIT;9.VHDL语言程序结构的特点是把一个设计实体分成A.外部和内部B.实体和实体说明C.结构体和结构体说明D.图形部分和文本部分10. VHDL设计文件的实体说明部分描述的是A.电路系统的内部结构B.电路系统的逻辑功能C.电路系统的主要参数D.电路系统的外部端口11.VHDL语言程序结构中必不可少的部分是:A.库B.程序包C.配置D.实体和结构体12. 下列选项中,哪些项在VHDL程序设计文件中属于可选部分A.库和实体B.实体和结构体C.结构体和配置D. 库、程序包和配置13. 关于VHDL中实体说明的格式,以下叙述不正确的是A.实体说明以“ENTITY 实体名 IS”开头,以“END 实体名”结束B.实体说明中包含类属表和端口说明两部分C.端口说明中只需要规定端口的模式即可D.实体名一定要与设计文件同名14. 在VHDL的实体说明中,端口名表的作用是A.列出所有输入端口的名称B.列出所有输出端口的名称C.说明实体输入、输出端口的信号类型及端口模式D.只定义输入、输出端口的数目15. 在VHDL中,为了使已声明的数据类型、子程序、元件能被其他设计实体调用或共享,可以把它们汇集在中。

2_EDA技术

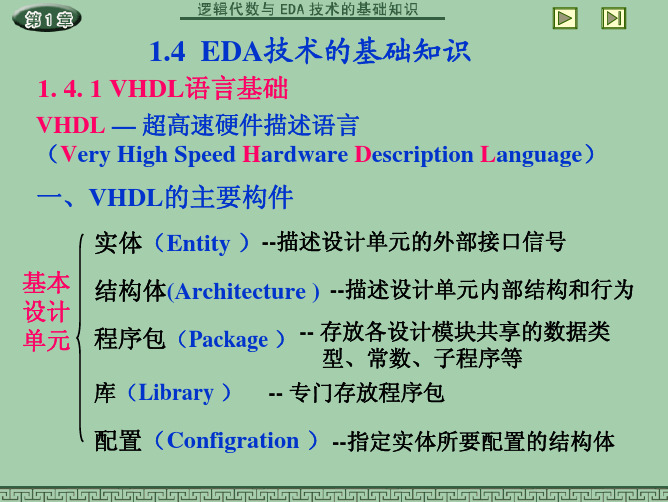

硬件描述语言VHDL

eqcomp4.vhd

库 包 实体

--eqcomp4 is a four bit equality comparator

文件名和实体 名一致

Library IEEE; use IEEE.std_logic_1164.all;

entity eqcomp4 is port(a, b:in std_logic_vector(3 downto 0); equal :out std_logic); end eqcomp4; architecture dataflow of eqcomp4 is begin equal <= ‘1’ when a=b else ‘0’; End dataflow;

硬件描述语言VHDL

VHDL的优点

• 用于设计复杂的、多层次的设计。支持设计库和 设计的重复使用 • 与硬件独立,一个设计可用于不同的硬件结构, 而且设计时不必了解过多的硬件细节。 • 有丰富的软件支持VHDL的综合和仿真,从而能 在设计阶段就能发现设计中的Bug,缩短设计时 间,降低成本。 • 更方便地向ASIC过渡 • VHDL有良好的可读性,容易理解。

每行;结尾 关键字end后跟 实体名

构造体

关键字begin

关键字end后跟 构造体名

VHDL 大小写不敏感

硬件描述语言VHDL

• 2.1 库(Library)

– 库是专门存放预编译程序包(Package)的地 方。库的使用方法是:在每个设计的开头声明 选用的库名,用USE语句声明所选中的逻辑单 元 。 – 库的一般格式为

硬件描述语言VHDL

结构体--数据流描述 描述输入信号经过怎样的变换得到输出信号

• architecture dataflow1 of eqcomp4 is • begin • equal <= ‘1’ when a=b else ‘0’; • end dataflow1; • • • • • • •

EDA基础VHDL

其书写顺序无关,在实际 电路中所有并行语句功能 同时实现。

3. 库、程序包和配置 (1) 库

功能: 存储和放置设计单元(元件、程序包等)。

[例1.4.14] WHILE…LOOP应用举例

abcd: WHILE (i<10) LOOP sun:=i+sum; i=i+1; END LOOP abcd;

(6)NEXT语句 满足条件时中止 格式: NEXT [WHEN 条件]; 当前循环,开始 下一次循环。 [例1.4.15] NEXT语句举例

函数名(实际参数表);

函数的参数只能是方式为IN的输入信号,函数 只能有一个返回值。 [例1.4.17] 比较器函数形式的程序设计实例

用并行语句形式描述设计 单元功能

并行语句类型

进程语句(PROCESS) 块描述语句(BLOCK) 信号赋值语句 子程序调用语句 元件例化语句

ARCHITECTURE 结构体名 OF 实体名 IS [结构体说明语句] BEGIN [功能描述语句] END 结构体名;

[例1.4.2] 2 输入与门的结构体描述。

常用资源库 含IEEE认可和某些公司提供的如: VHDL标准库 STD库 STD_LOGIC_1164 程序包 存放:STANDARD的程序集合 STD_LOGIC_ARITH算术运算包 VHDL库 ASIC库 资源库 集合定义了多种常用的数据类型 存放:和各种逻辑门一一对应的 实体 WORK库 当前作业库 存放:当前设计项目生成的全部文 用户自定义库 资源库 件目录 存放:用户自己创建定义的非 库说明语句格式: 标准程序包集合和实体。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

L5 ENTITY example2 IS

L6

PORT(a, b, c : IN STD_LOGIC;

L7

x, y, z : BUFFER STD_LOGIC);

L8 END;

L9 -------------------------------------------------------------------------------------------------------------------------

L5 ENTITY example1 IS

L6

PORT(a, b, c : IN

STD_LOGIC;

L7

x, y, z : BUFFER STD_LOGIC);

L8 END;

L9 -------------------------------------------------------------------------------------------------------------------------

7

第5章 VHDL基本语句

正如图5-2的硬件电路图所表明的,只有当信号a或者b的 值改变后才能执行赋值语句“x <= a AND b;”,即信号a或b的 值改变之前信号x的值不会发生变化。同样,信号x的值改变之 前,y的值也不会发生变化;信号c或y的值改变之前,z的值也 不会发生变化。由此可以看出,VHDL代码的执行是由事件控 制的,这就意味着并行VHDL语句可以按任意顺序书写,其设 计的功能不变。

4

第5章 VHDL基本语句

图5-2 例5-1和例5-2综合后电路结构

5

第5章 VHDL基本语句

【例5-1】

L1 -------------------------------------------------------------------------------------------------------------------------

L2 LIBRARY ieee;

L3 USE ieee.std_logic_1164.all;

L4 -------------------------------------------------------------------------------------------------------------------------

2

第5章 VHDL基本语句

图5-1 结构体中的语句使用示例

3

第5章 VHDL基本语句 5.1.1 并行语句的特点 并行语句是硬件描述语言的一大特点,它与C语言等计 算机高级程序设计语言最大的不同是:并行语句在结构体中 的执行是并行的,不会因为书写顺序的前后而产生执行顺序 的先后。例5-1和例5-2结构体内都含有3条相同的并行语句, 它们体现了在不同的描述顺序下,仍然能够综合出一致的电 路结构,如图5-2所示。

L10 ARCHITECTURE construct OF example1 IS

L11 BEGIN

L12

x <= a AND b;

L13

y <= NOT x;

L14

z <= c OR y;

L15 END;

L16 -------------------------------------------------------------------------------------------------------------------------

L10 ARCHITECTURE construct OF example2 IS

L11 BEGIN

L12

z <= c OR y;

L13

y <= NOT x;

L14

x <= a AN -------------------------------------------------------------------------------------------------------------------------

6

第5章 VHDL基本语句

【例5-2】

L1 -------------------------------------------------------------------------------------------------------------------------

L2 LIBRARY ieee;

第5章 VHDL基本语句

第5章 VHDL基本语句

5.1 并行语句 5.2 顺序语句 5.3 常用语句的比较 5.4 组合逻辑电路的设计 5.5 时序逻辑电路的设计

1

第5章 VHDL基本语句

5.1 并 行 语 句

VHDL中既具有并行语句(如元件例化语句),也具有顺 序语句(如IF语句)。不同的语句使用在不同的地方。对于 VHDL设计者来说,重要的是要知道哪些语句结构中需要使 用并行语句,哪些语句结构中需要使用顺序语句。可以简单 地概括为:结构体中除进程(PROCESS)、函数(FUNCTION) 和过程(PROCEDURE)结构内部以外的其他VHDL代码都是 并行语句,如图5-1所示。需要注意的是,信号赋值语句既 可以出现在进程中,也可以出现在结构体的并行语句部分, 只是运行的含义不同(参考4.2.3节)。

例5-3再次显示了并行语句的特点,L13~L15这3条语句对 应生成了3个加法器(见图5-3),即3个加法器同时在进行加法操 作,没有顺序关系,而不是一个加法器顺序执行3条加法操作 指令。VHDL代码最终实现的是具体的硬件电路,而不是在 CPU中的逐条指令执行,这是VHDL语言相对于传统软件语言 的不同。

8

第5章 VHDL基本语句

【例5-3】

L1 -------------------------------------------------------------------------------------------------------------------------

L3 USE ieee.std_logic_1164.all;

L4 -------------------------------------------------------------------------------------------------------------------------