全国大学生电子设计大赛题一等奖数字频率计

历届电子设计大赛题目(一至六)1994-2003

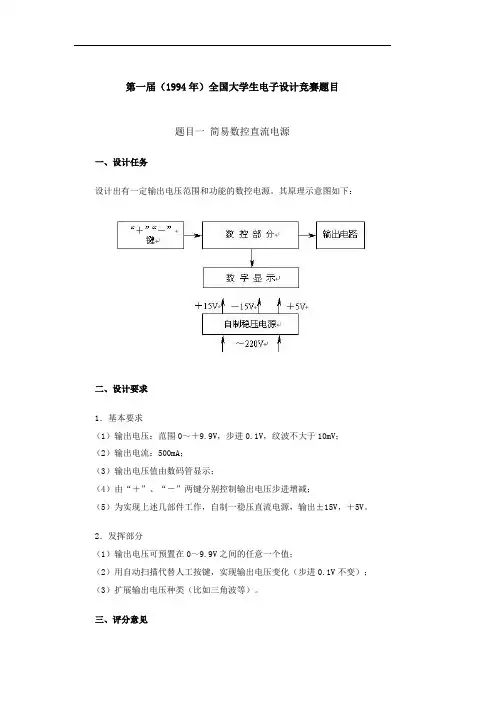

第一届(1994年)全国大学生电子设计竞赛题目题目一简易数控直流电源一、设计任务设计出有一定输出电压范围和功能的数控电源。

其原理示意图如下:二、设计要求1.基本要求(1)输出电压:范围0~+9.9V,步进0.1V,纹波不大于10mV;(2)输出电流:500mA;(3)输出电压值由数码管显示;(4)由“+”、“-”两键分别控制输出电压步进增减;(5)为实现上述几部件工作,自制一稳压直流电源,输出±15V,+5V。

2.发挥部分(1)输出电压可预置在0~9.9V之间的任意一个值;(2)用自动扫描代替人工按键,实现输出电压变化(步进0.1V不变);(3)扩展输出电压种类(比如三角波等)。

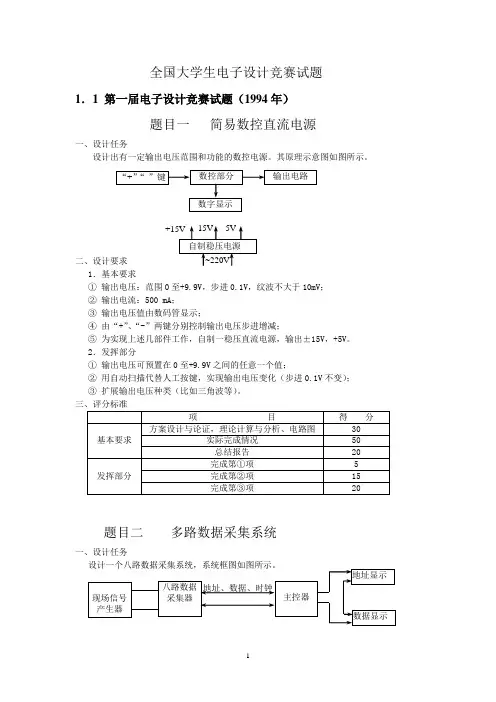

三、评分意见项目得分基本要求方案设计与论证、理论计算与分析、电路图30实际完成情况50总结报告20 发挥部分完成第一项 5完成第二项15完成第三项20题目二多路数据采集系统一、设计任务设计一个八路数据采集系统,系统原理框图如下:主控器能对50米以外的各路数据,通过串行传输线(实验中用1米线代替)进行采集的显示和显示。

具体设计任务是:(1)现场模拟信号产生器。

(2)八路数据采集器。

(3)主控器。

二、设计要求1.基本要求(1)现场模拟信号产生器:自制一正弦波信号发生器,利用可变电阻改变振荡频率,使频率在200Hz~2kHz范围变化,再经频率电压变换后输出相应1~5V直流电压(200Hz对应1V,2kHz对应5V)。

(2)八路数据采集器:数据采集器第1路输入自制1~5V直流电压,第2~7路分别输入来自直流源的5,4,3,2,1,0V直流电压(各路输入可由分压器产生,不要求精度),第8路备用。

将各路模拟信号分别转换成8位二进制数字信号,再经并/串变换电路,用串行码送入传输线路。

(3)主控器:主控器通过串行传输线路对各路数据进行采集和显示。

采集方式包括循环采集(即1路、2路……8路、……1路)和选择采集(任选一路)二种方式。

第一至五届全国大学生电子设计竞赛试题

全国大学生电子设计竞赛试题1.1 第一届电子设计竞赛试题(1994年)题目一 简易数控直流电源一、设计任务设计出有一定输出电压范围和功能的数控电源。

其原理示意图如图所示。

二、设计要求1.基本要求① 输出电压:范围0至+9.9V ,步进0.1V ,纹波不大于10mV ; ② 输出电流:500 mA ;③ 输出电压值由数码管显示; ④ 由“+”、“-”两键分别控制输出电压步进增减;⑤ 为实现上述几部件工作,自制一稳压直流电源,输出±15V ,+5V 。

2.发挥部分① 输出电压可预置在0至+9.9V 之间的任意一个值;② 用自动扫描代替人工按键,实现输出电压变化(步进0.1V 不变); ③ 扩展输出电压种类(比如三角波等)。

题目二 多路数据采集系统一、设计任务主控器能对50米以外的各路数据,通过串行传输线(实验中用1米线代替)进行采集和显示。

具体设计任务是:①现场模拟信号产生器。

②八路数据采集器。

③主控器。

二、设计要求1.基本要求①现场模拟信号产生器自制一正弦波信号发生器,利用可变电阻改变振荡频率,使频率在200Hz至2kHz范围变化,再经频率电压娈换电路后输出相应1V至5V直流电压(200Hz对应1V,2kHz对应5V)②八路数据采集器数据采集器第一路输入自制1V至5V直流电压,第2至7路分别输入来自直流源的5,4,3,2,1,0V直流电压(各路输入可由分压器产生,不要求精度),第八路备用。

将各路模拟信号分别转换成八位二进制数字信号,再经并/串变换电路,用串行码送入传输线路。

③主控器主控器通过串行传输线路对各路数据进行采集和显示。

采集方式包括循环采集(即1路、2路、…、8路、1路…)和选择采集(任选一路)二种方式。

显示部分能同时显示地址和相应的数据。

2.发挥部分①利用电路补偿或其它方法提高可变电阻值变化与输出直流电压变化的线性关系;②尽可能减少传输线数目;③其它功能的改进(例如:增加传输距离,改善显示功能等)1.2 第二届电子设计竞赛试题(1995年)题目一实用低频功率放大器一、任务设计并制作具有弱信号放大能力的低频功率放大器。

设计并制作闸门时间为1s的数字频率计

摘要频率计用一个频率稳定度高的频率源作为基准时钟,对比测量其他信号的频率。

通常情况下计算每秒内待测信号的脉冲个数,此时我们称闸门时间为1s。

本设计以ARM核心处理器,设计并制作了闸门时间为1s的数字频率计,能够测量频率。

该频率计硬件部分高速比较器74HC14整形电路组成。

利用32定时器的ETR功能可准确测出低高频信号,实现了对正弦波的频率测量。

经测试该频率计性能良好,正弦信号频率测量范围可从1Hz到25MHz。

关键词:STM32;高速比较;;测频一、系统方案论述1.整形电路的比较与选择方案一:由施密特触发器对74HC14信号进行调理,可以直接输出TTL电平,。

方案二:由比较器整形后的信号再由施密特整形,输出TTL电平。

从性能上讲此方案较好,但是由于时间问题,找不到合适的高速比较器和施密特触发器组合。

综上选择方案一。

2.微处理器的比较与选择方案一:采用STM32对调理后的信号测频。

输入信号的测量能达到频率达到100MHz,测频精度高,速度快。

方案二:采用430测频,但是最多测量到16M而且引脚速度不够导致无法完成指标内的频率测量为了更好地实现题目要求,我们选择方案一。

3.测频方法的选择与比较方案一:输入捕获测频法是累积单位时间里的周波数,在频率较低时采用。

频率较高时精度低,但不适合高频的测量。

方案二:周期法是测一个周期的时间,通过周期转换成频率,在频率较低时采用。

频率较低时精度高但不适合高频。

方案三:利用ETR外部信号触发将外部的信号(测量信号)作为计数信号,不用经历中断产生时间延时,ETR可以直接作为时钟输入也可以通过触发输入(TRGI)来作为时钟输入即在时钟模式1中触发源选择为ETR,两个效果上是一样的。

可准确测出低高频,在低频段使用不分频ETR触发,高频时使用4分频测量提高测量范围。

由于输入信号的要求为1Hz~25MHz,所以选择方案三。

4.系统总体方案通过高速比较器74HC14对信号源的波形进行整形,输出标准的方波。

2015全国大学生电子设计竞赛重庆赛区(编号190)

2015年全国大学生电子设计竞赛数字频率计(F题)【本科组】时间:2015年8月15日摘要本作品以FPGA和STM32F103ZET6设计了一台闸门时间为1s的数字频率计,作品主要由主控模块、放大器模块、FPGA模块、电源模块及TFT显示模块构成。

为了满足测频对小信号的要求,系统采用电压反馈放大器OPA847搭建二级放大电路对小信号进行放大处理;通过FPGA模块对高频信号进行计数,达到了测频率、测周期等功能。

由STM32F103ZET6接受FPGA传来的信号,再进行数据处理,控制TFT模块显示相关测量数据。

最后,通过对作品进行实测,得到的实验数据表明,本设计达到了预期在功能和精度方面的要求。

关键字:FPGA,STM32,小信号放大,频率计。

AbstractIn this work, a digital frequency meter is designed by FPGA and STM32F103ZET6, which is composed of main control module, amplifier module, FPGA module, power module and TFT display module. And gate time is 1s. In order to meet the requirements of small signal frequency measurement, the system uses the voltage feedback amplifier OPA847 to set up the two stage amplifier circuit to amplify the small signal. Through the FPGA module, the high frequency signal is counted, and the function of the frequency and cycle is reached. The signal that is received by FPGA is processed by STM32F103ZET6, and the data processing is controlled by TFT module. Finally, the experimental results show that the design can meet the requirements of the function and precision.Keywords: FPGA, STM32, small signal amplification, frequency meter.一、方案选择与论证1、主控模块方案选择方案一:利用STM32单片机作为主控芯片直接进行数据采集和处理,其优点是硬件电路比较简单。

2015全国大学生电子设计大赛F题一等奖--数字频率计

2.

2.1.

本设计的宽带通道放大器如图2所示,是一个自动增益控制模块。 压控放大器VCA810依靠反馈得到的控制电压控制放大倍数;高速比较器

AD8561比较的是VCA810输出信号和预设电压,使用二极管和RC对比较器的 输出信号进行检波;TL082将检波得到的电压转换至VCA810的控制电压范围内,使得VCA810能够正常工作;OPA690起着二级放大与级联缓冲的作用。具 体电路连接如图3所示。

0.03

726

29.97

34

0.088

667

49.98

902

0.02

196

70.00

331

0.004

731

89.9

987

0.001

444

5MH

z

10.00

41

0.04

1

30.02

6

0.086

667

50.08

29

0.16

58

70.23

478

0.335

404

90.0

235

0.026

111

4.3.

1、频率测量时,在1Hz-100MHz时,最低测量有效值Vrms可降低为5mV;

(2)测量结果

表4占空比测量数据表

设

定 占 空 比

10%

30%

50%

70%

90%

频 率

测量 值

/%

误差

/%

测量 值

/%

误差

/%

测量 值

/%

误差

/%

测量 值

/%

误差

/%

测量 值

/%

误差

电赛论文-数字频率计

“瑞萨杯”全国大学生电子设计大赛题目:数字频率计(F题)参赛学校:参赛队员:摘要本设计是基于FPGA的数字频率计,利用Verilog硬件描述语言设计实现了频率计内部功能模块,采用了等精度测量的方法,相比直接测频法和测周法有精度更高的特点。

被测信号由DDS产生,经衰减器后得到。

被测信号输入调理采用高速运放OPA657和OPA820对其进行放大,由FPGA进行采样测量,算得频率值后传给单片机,由单片机显示数值及单位。

对于时间间隔的测量,被测信号同样分两路通过OPA657放大电路进行放大,再分别输入FPGA,由FPGA进行时间间隔测量,单片机显示。

发挥部分脉冲信号占空比测量设计同前。

关键词:等精度测量FPGA 单片机高速运放1.系统方案1.1整体系统的论证和选择本系统主要由信源模块、前级运算放大电路模块、控制计数模块、显示模块组成,难点在于高速运算放大器的选择,及控制技术模块的选择。

下面分别论证这两个个模块的选择。

1.2前级电路的论证与选择方案一:采用高速运算放大电路与比较电路,由于比较电路电压翻转较慢,容易产生抖动,导致测量精度不够,实现起来较难。

方案二:采用两级级联高速运算放大电路。

本方案通过使用集成运算放大芯片OPA657搭建两级运算放大电路,使增益达到100倍,当增益达到一定程度后,波形失真,成为正弦波,省去了整形过程,且满足了增益带宽100M 的需求。

综合以上两种方案,选择方案二。

1.3控制计数模块的论证和选择方案一:用硬件电路实现。

使用芯片搭建计数、控制电路模块,实现起来较困难,且效率跟不上,精度不够,不适宜。

方案二:用单片机实现。

用单片机完成整个测量电路的测试控制、数据处理和显示输出]。

该方案实现起来比较简单,但是由于单片机的处理频率一般不是很高,易受外部条件的干扰,功耗也高,不适宜。

方案三:利用FPGA实现。

在EDA工具软件平台上以硬件描述语言VHDL 为系统逻辑描述手段完成的设计文件,自动地完成逻辑编译、逻辑化简、逻辑分割、逻辑综合、结构综合经及逻辑优化与仿真,直到实现既定的电子线路系统功能。

2015年全国大学生电子设计竞数字频率计(F题)张佳鹏 宋岩 谭贻凯

2015年全国大学生电子设计竞赛数字频率计(F题)2015年8月15日数字频率计(F题)大连东软信息学院参赛队员:张佳鹏宋岩谭贻凯摘要:本频率计由OPA656和LM319运放芯片搭建放大和比较器电路,使50mV-1V的正弦波信号放大整形成单片机能够识别的TTL电平信号,并由STM32F407MCU为主控芯片,通过捕获信号的上升沿来对信号进行频率统计,并通过中断计数的方式对两路经放大后的方波的时间间隔进行测量,统计结果通过OLED液晶屏进行显示,并能通过I/O口电平的输入选择频率测量和时间间隔的测量。

关键词:频率时间间隔信号放大宽频运算放大器高速比较器。

目录数字频率计(F题) (I)大连东软信息学院参赛队员:张佳鹏宋岩谭贻凯 (I)摘要: (I)关键词: (I)1系统方案 (3)1.1 运算放大器的论证与选择 (3)1.2 正弦波测量方法的论证与选择 (3)1.3 提高仪器灵敏度的论证与选择 (4)2 系统原理分析 (4)2.1 OPA656 运算放大器原理 (4)2.2 LM319 比较器原理 (5)3电路与程序设计 (5)3.1 电路设计 (5)3.1.1 系统设计 (6)3.2 程序设计 (6)4 测试方案和测试结果 (7)4.1测试方法 (7)4.2 测试结果 (8)4.3 结果分析 (9)参考文献 (9)附录 (9)数字频率计(F题)【本科组】1系统方案本系统主要由电源模块、运算放大模块、比较器模块、控制显示模块组成,下面分别论证这几个模块的选择。

1.1 运算放大器的论证与选择方案一:LM358LM358是双运算放大器。

内部包括有两个独立的、高增益、内部频率补偿的双运算放大器,适合于电源电压范围很宽的单电源使用,也适用于双电源工作模式,在推荐的工作条件下,电源电流与电源电压无关。

它的使用范围包括传感放大器、直流增益模块和其他所有可用单电源供电的使用运算放大器的场合。

LM358最小识别电压变化为2mV,运放宽度为1Hz~1.1MHz,与本题的50mV~1V 的1Hz~10MHz的信号不符,故不可用。

2015年全国大学生电子设计竞赛-F题(数字频率计)-全国一等奖-电子科技大学

| N s | 。题目中极限情况下要 Ns

-3-

求在 5MHz 、10%占空比时 达到 0.01。因此,由

| N s | 0.01 ,可求得 Ns

Ns 100 。为在 20ns 时间内计数值大于 100,时基脉冲频率需大于 5GHz。可通

图 1 系统框图

单片 机

人机 界面

二、理论分析与计算

2.1 宽带通道放大器设计 按题目的要求, 被测正弦波信号有效值范围需要为 10mVrms 至 1Vrms,频率范 围为 1Hz 到 100MHz。一般考虑用放大器进行放大,再使用门电路整形。假设门 电路输入电压超过 2V 就被识别逻辑 1 电平,则对于小信号,要使放大后能够触 发逻辑门或者缓冲器进行缓冲整形,所需放大器增益为:

dt 100% 。

| D0 D | 100% 。 D0

4.2.4 数据刷新时间测量 在本系统中单片机提供预设的闸门时间为 1.2s,实际的闸门时间约为 1.4s, 数据在单片机中处理并送去显示所需要的时间约为几 ms,总刷新时间不会超过

-6-

1.5s。 理论上 1Hz 的信号所需要的刷新时间是最多的,故在 1Hz 频率的情况下,通 过秒表测量信号的刷新时间。 4.3 测试结果及分析 4.3.1 频率和周期测量 测量数据如下表 2 所示:

图 6 系统流程图

图 7 FPGA 和单片机连接框图

-5-

四、测试方案与测试结果

4.1 测试仪器 根据题目要求,所需要的测试仪器如下表 1:

表 1 测量仪器表

序号 1 4.2 测试方案

仪器名称 双通道函数信号发生器

型号 DG4162

指标 0~160MHz

2015年全国大学生电子设计大赛F题-数字频率设计报告

2015年全国大学生电子设计大赛F题-数字频率设计报告2015年全国大学生电子设计竞赛数字频率计(F 题)【本科组】2015年8月15日摘要频率计是数字电路中的一个典型应用,是计算机、通讯设备、音频视频等科研生产领域不可缺少的测量仪器,频率测量在科技研究和实际应用中的作用日益重要。

该系统由信号输入电路、数据处理电路和显示电路构成,可实现数字频率计的测频率、周期、占空比、脉宽等各项功能。

以FPGA为核心处理数据最更大程度地提高了精度。

经过综合测评,发现该系统具有高分辨率、输入频率量程宽、测量精度高和输出稳定等特点。

关键词:FPGA 频率计高精度等精度高带宽AbstractFrequency meter is a typical application of digital circuit, computer, communications equipment, audio, video, and other areas of the scientific research production indispensable measuring instrument, the role of frequency measurement in science and technology research and practical application is increasingly important.The system consists of signal input circuit, data processing circuit and display circuit, which can realize the digital frequency meter measuring frequency, cycle, pulse rate, pulse width and so on various functions.The FPGA as the core processing improves the accuracy of data is the greater.Through the comprehensive evaluation, found that the system has high resolution, wide input frequency range, high measurement accuracy and stable output.Keywords: FPGA、Frequency meter、High precision、equal precision、High bandwidth目录目录 (2)第一章设计任务与要求 (4)1.1 设计任务 (4)1.2 设计要求 (4)1.2.1 基本要求 (4)1.2.2 发挥部分 (4)第二章方案讨论与选择 (5)2.1方案设计 (5)2.1.1方案一 (5)2.1.2方案二 (5)2.2方案选择 (6)第三章理论分析与计算 (6)3.1 总体分析 (6)3.2各项被测参数 (7)3.2.1 等精度测量的原理: (7)3.2.2 等精度测量的实现 (7)3.2.3 等精度数字频率计误差分析 (8)3.3 宽带通道放大器分析 (8)3.4 提高仪器灵敏度的措施 (8)第四章硬件电路与程序设计 (9)4.1 硬件电路 (9)4.1.1前置信号输入电路 (9)4.1.2 主控FPGA (10)4.1.3显示模块 (10)4.1.4电源模块 (10)4.2 程序设计 (11)4.2.1 FPGA处理数据程序框图 (11)第五章测试方案与结果 (11)5.1 测试方案与测试结果 (11)5.1.1 测试方案 (11)5.1.2 测试结果 (11)5.2测试结果分析 (17)参考文献 (17)附录 (18)1、核心器件 (18)2、输入电路图 (18)3、FPGA顶层设计图 (19)4、实物图展示 (22)第一章设计任务与要求1.1 设计任务设计并制作一台闸门时间为1s的数字频率计。

频率计 相位——【全国大学生电子设计大赛】

集成电路应用技术设计——数字频率计08004102 鲍婧项目综述:要求设计一个频率计,达到以下要求:功能:测量信号的频率测量信号间的相位差具有灵敏度调节指标:频率测量范围0.1~1MHz频率测量精度0.01%信号幅度0.1~10V系统总体技术方案:系统采用测频与测周方式相结合的办法,在对输入信号进行放大整形后,根据被测信号频率选择合适的测量频率的方法,并把测量结果交单片机处理,通过数码管显示出来。

按照自顶向下的设计方法,分别画出频率计的系统级框图如下:12项目分析:1、输入级放大整形从输入端进来的可能是0.1V~10V 的正弦波或者方波。

不能直接测量计数,须经过放大整形后变成标准的TTL 方波。

该部分电路全部采用模拟集成电路来实现。

然后再用数字微分电路把方波信号变成正的窄脉冲,方便测量相位差。

考虑到1MHz 的频率信号所用的运放、比较器带宽需足够大,采用了高速模拟器件MAX4016、MAX902,把幅度0.1V~10V 信号分成三档,小于2.5V 、2.5~5V 、大于5V ,分别称为低中高档。

放大增益分别为10、1、1/2。

在低档时,电压幅度乘以增益后会大于供电电压因而使波形发生形变。

但此形变不会影响到频率测量。

电压比较器设计时,可以把触发电平调节电路直接设置在电压比较器的输入端,这样实现方便设计简单。

输 入 级A 通道B 通道频率 测量 模块键盘 开关 按钮单片机LED显示fc一组三个拨动开关作为脉冲幅值档的选择,从上到下依次是2.5~5V、小于2.5V、大于5V档。

右下角的可变电阻作为比较器的触发电平,可调节。

此外,因为模拟通道部分所用器件都是宽带高速器件,为防止寄生振荡,在每个器件的电源引脚附近到地之间均需加上去耦电容,每组去耦电容由小容量(0.1uF)的陶瓷电容和容量大(6.8uF)的钽电容并联而成。

小容量陶瓷电容对高频分量有良好的去耦作用,大容量的钽电容对低频分量有良好的去耦作用。

(这里只画出一个作为示例)数字微分器的工作原理是:输入脉冲及其两级反相门延时后的信号同时加到异或门的输入端,由于时延,在其输出端就得到了与输入信号的前后沿对应的窄脉冲,即达到了微分效果。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2015 年全国大学生电子设计竞赛

全国一等奖作品

设计报告部分错误未修正,软

件部分未添加

竞赛选题:数字频率计(F 题)

摘要

本设计选用FPGA 作为数据处理与系统控制的核心,制作了一款超高精度的数字频率计,其优点在于采用了自动增益控制电路(AGC)和等精度测量法,全部电路使用PCB 制版,进一步减小误差。

AGC 电路可将不同频率、不同幅度的待测信号,放大至基本相同的幅度,且高于后级滞回比较器的窗口电压,有效解决了待测信号输入电压变化大、频率范围广的问题。

频率等参数的测量采用闸门时间为1s 的等精度测量法。

闸门时间与待测信号同步,避免了对被测信号计数所产生±1 个字的误差,有效提高了系统精度。

经过实测,本设计达到了赛题基本部分和发挥部分的全部指标,并在部分指标上远超赛题发挥部分要求。

关键词:FPGA 自动增益控制等精度测量法

目录

1. 系统方案

1.1. 方案比较与选择

宽带通道放大器

方案一:OPA690 固定增益直接放大。

由于待测信号频率范围广,电压范围大,所以选用宽带运算放大器OPA690,5V 双电源供电,对所有待测信号进行较大倍数的固定增益。

对于输入的正弦波信号,经过OPA690 的固定增益,小信号得到放大,大信号削顶失真,所以均可达到后级滞回比较器电路的窗口电压。

方案二:基于VCA810 的自动增益控制(AGC)。

AGC 电路实时调整高带宽压控运算放大器VCA810 的增益控制电压,通过负反馈使得放大后的信号幅度基本保持恒定。

尽管方案一中的OPA690 是高速放大器,但是单级增益仅能满足本题基本部分的要求,而在放大高频段的小信号时,增益带宽积的限制使得该方案无法达到发挥部分在频率和幅度上的要求。

方案二中采用VCA810 与OPA690 级联放大,并通过外围负反馈电路实现自动增益控制。

该方案不仅能够实现稳定可调的输出电压,而且可以解决高频小信号单级放大时的带宽问题。

因此,采用基于VCA810 的自动增益控制方案。

正弦波整形电路

方案一:采用分立器件搭建整形电路。

由于分立器件电路存在着结构复杂、设计难度大等诸多缺点,因此不采用该方案。

方案二:采用集成比较器运放。

常用的电压比较器运放LM339 的响应时间为1300ns,远远无法达到发挥部分100MHz 的频率要求。

因此,采用响应时间为4.5ns 的高速比较器运放TLV3501。

主控电路

方案一:采用诸如MSP430、STM32 等传统单片机作为主控芯片。

单片机在现实中与FPGA 连接,建立并口通信,完成命令与数据的传输。

方案二:在FPGA 内部利用逻辑单元搭建片内单片机Avalon,在片内将单片机和测量参数的数字电路系统连接,不连接外部接线。

在硬件电路上,用FPGA 片内单片机,除了输入和输出显示等少数电路外,其它大部分电路都可以集成在一片FPGA 芯片中,大大降低了电路的复杂程度、减小了体积、电路工作也更加可靠和稳定,速度也大为提高。

且在数据传输上方便、简单,因此主控电路的选择采用方案二。

参数测量方案

频率等参数的测量采用闸门时间为 1s 的等精度测量法。

闸门时间与待测信 号同步,相比于传统方案,避免了对被测信号计数所产生±1 个字的误差,有效 提高了系统精度。

测量频率时,在闸门时间内同时对待测信号和标准信号(时钟 信号)计数,标准信号计数值除以待测信号计数值乘上时钟周期即为待测周期; 对脉冲信号等精度测量得到间隔时间。

测量频率时计算闸门时间内的上升沿脉冲 除以闸门时间;测量两个信号的相位差时,则计算第一个信号

1.2. 方案描述

系统总体框图如图 1 所示,待测信号首先进入自动增益电路,其输出电压增 益到一个大于后级滞回比较器窗口电压的固定值,经过比较器电路后,输出给 FPGA 进行相关参数的测量,并最终显示在屏幕上。

在 FPGA 内部,数字电路系 统与片内单片机通信,基于闸门时间为 1s 的等精度测量算法,测算相关参数。

放大信号 信号整形 参数测量 结果输出

图 1 系统总体框图

2. 电路设计

2.1. 宽带通道放大器分析

本设计的宽带通道放大器如图 2 所示,是一个自动增益控制模块。

压控放大器 VCA810 依靠反馈得到的控制电压控制放大倍数;高速比较器 AD8561 比较的是 VCA810 输出信号和预设电压,使用二极管和 RC 对比较器的 输出信号进行检波;TL082 将检波得到的电压转换至 VCA810 的控制电压范围 内,使得 VCA810 能够正常工作;OPA690 起着二级放大与级联缓冲的作用。

具 体电路连接如图 3 所示。

FPGA

比较器电路

AGC 电路 宽带放大 输入信号

NIOS

II

TFT 显示

蓝牙模块

图 2 自动增益模块流程图 图 3 自动增益模块原理图

2.2. 正弦波整形电路

AGC 电路后,进入如图 4 所示的滞回比较器,整成方波。

96mV

图 4 滞回比较器3. 软件设计

图 5 软件流程图4. 测试方案与测试结果

4.1. 测试仪器

表 1 测试仪器

4.2. 测试方案及数据

频率测试

(1)测试方法:选取1Hz、100Hz、1KHz、1MHz、10MHz5 个频率点,测量分别测量输入信号在3mVrms、10mVrms、50mVrms、100mVrms、1Vrms 的结果,并计算误差

(2)测量结果

表 2 频率测量数据表

时间间隔测量

(1)测试方法:选取0.1us、1ms、100ms 个频率点,测量分别测量输入信号在100Hz、200Hz、500Hz、1000Hz 四种时间间隔以及20mV、50mV、以及1V 时的结果,并计算误差

(2)测量结果

表 3 方波Vpp=20mV 时间间隔测量数据表

表 4 方波Vpp=50mV 时间间隔测量数据表

表5 方波Vpp=1V 时间间隔测量数据表

占空比测量

(1)测试方法:选取10%、30%、50%、70%、90%四个相位测,分别测量输入信号是1Hz、100Hz、10KHz、1MHz、5MHz 的结果,并计算误差(2)测量结果

4.3. 其他发挥部分(亮点)

1、频率测量时,在1Hz-100MHz 时,最低测量有效值Vrms 可降低为5mV;

2、方波测量占空比和时间间隔时,最低测量的Vpp 可达到10mV;

3、频率、时间间隔测量时分辨率超过发挥部分要求;

4、除使用键盘进行人机交互外,增加了蓝牙通讯功能,可实现无线控制功能,

切换仪器测量模式。

4.4. 测试结论

实测表明,本设计在频率测量、相位测量、占空比测量等多个参数上全都可以达到赛题基本部分和发挥部分的要求,并在部分指标上远超发挥部分要求。

参考文献

[1]张永瑞. 电子测量技术基础[M]. 西安:西安电子科技大学出版社, 2009. [2]夏宇

闻. Verilog 数字系统设计教程[M]. 北京:北京航空航天大学出版社, 2013. [3]刘凯,

顾新.VHDL 硬件描述语言与数字逻辑电路设[M] 西安:西安电子科技大

学出版社,2009.

[4]冈村迪夫. OP 放大电路设计:从重视再现性设计的基础到实际应用[M]. 北京:科学出版社, 2004.

[5]Sergio, Franco. 基于运算放大器和模拟集成电路的电路设计[M]. 西安:西安交通大学出版社, 2004.。