第12章 IC工艺几种IC工艺流程

第12章 光刻:掩膜,光刻胶和光刻机

浸没式

CASSETTE HANDLER

批量或单片浸入显影液槽中。 是最初的显影方式。

Bath

Develop

Developer

in-let

Developer

WAFER

WAFER CHUCK

DRAIN

WAFER CASSETTE shake up and down to improve develop uniformity and its speed. Usually develop material company use this one. It’s easy to control Develop temperature.

工艺线直击——光刻过程

11.2 掩模版(Photomask)

一种透明的平板,上面有要转印到硅片上光刻胶层的图形。 按照图形的完整度分为两类:

投影掩模版和掩模版

掩膜版的材料

衬底材料:最主要的用于亚微米光刻的投影掩膜 版衬底材料是熔融石英(fused silica)。它在深紫外 光谱部分(248nm和193nm)有着很高的光学透射。 熔融石英相对昂贵,但性能优越。它具有很低的热 膨胀系数。 图形材料:用于掩膜版上不透明的图形材料通常 是薄层的铬(Chrome,Cr)。厚度通常小于1000A, 通过溅射淀积。有时候会在铬上形成一层氧化铬 (200A)的抗反射涂层。

Use for IN-LINE SYSTEM.Developer is spraying on therotating wafer( hundreds rpm.) Merit : High contrast,Low scum Demerit : Large usage,Bad CD uniformity

前烘设备

IC的生产工序流程以及其结构

IC的生产工序流程以及其结构IC(集成电路)是一种通过技术手段将多个电子器件集成到一个芯片上的电子器件。

IC的生产工序流程包含了多个环节,每个环节都需要严格的控制和测试,以确保最终产品的质量和性能。

IC的生产工序流程可以大致分为晶圆制备、晶圆加工、封装和测试四个阶段。

第一阶段:晶圆制备晶圆制备是IC生产的第一步,即将选择好的硅片制备成适用于IC加工的基片。

该阶段主要包括以下步骤:1.基片选择:选择具有较高晶片质量的硅片作为基片。

2.磨平:使用化学机械研磨等技术将硅片的表面进行磨平,以提高晶片的表面质量。

3.清洗:通过化学清洗等方法清除硅片表面的杂质,以增加晶片的纯度。

4.涂覆:将具有特殊光敏性的光刻胶均匀涂覆在硅片表面,用于后续的芯片图案制作。

第二阶段:晶圆加工晶圆加工是IC生产的核心阶段,主要是通过光刻、蚀刻、沉积等工艺,将芯片的电路图案逐层刻制在硅片上。

该阶段主要包括以下步骤:1.光刻:使用光刻胶模具和紫外光照射,将芯片电路的设计图案转移到硅片上。

2.蚀刻:使用化学或物理蚀刻方法,将光刻胶以外的硅片材料去除,形成芯片电路的各个层次。

3.沉积:使用化学气相沉积、物理气相沉积等方法,将金属、氧化物等材料沉积在芯片表面,形成电路的导线、阻抗等元件。

4.清洗和检查:对加工后的芯片进行清洗和检查,确保电路图案和元件的质量和完整性。

第三阶段:封装封装是将完成加工的芯片封装成IC产品的过程,主要是为了保护芯片、便于使用和连接外部元件。

该阶段主要包括以下步骤:1.切割和研磨:将加工好的硅片切割成单个的芯片,并通过研磨等方法将芯片的厚度调整到设计要求。

2.封装设计:根据芯片的功能和尺寸要求,设计适用的封装结构和材料,并设计电路连接引脚和封装外壳。

3.芯片安装:将芯片粘贴或焊接到封装结构的基座上,并通过线键和焊球等方法与引脚进行连接。

4.密封:将芯片和引脚密封在封装外壳中,以保护芯片免受环境影响。

5.清洗和测试:对封装好的芯片进行清洗和测试,确保封装的质量和性能。

IC基础知识及制造工艺流程

IC基础知识及制造工艺流程IC(集成电路)是由多个电子元件和电子器件组成的电路,采用一种特定的制造技术将它们整合在一起,形成一个封装紧密的芯片。

IC基础知识涉及到IC的分类、原理、封装等方面,而IC的制造工艺流程则包括晶圆制备、光刻、扩散、制备、封装等多个步骤。

一、IC的基础知识1. IC的分类:IC按用途可分为模拟集成电路和数字集成电路;按制造工艺可分为Bipolar IC和MOS IC;按封装方式可分为单片封装和双片封装等。

2.IC的原理:IC基本元件包括电阻、电容、电感、二极管、晶体管等,通过它们的组合和连接形成各种电路,实现不同的功能。

3.IC的封装:IC芯片制造完成后,需要进行封装,即将芯片连接到载体上,并保护和封闭,以便与外界连接。

常见的封装方式有DIP、QFP、BGA等。

1.晶圆制备:IC的制造过程始于晶圆制备,即将硅单晶材料通过切割和抛光等工艺,制成规定尺寸和厚度的圆片。

晶圆表面还需要进行特殊的处理,如清洗和去除杂质。

2.光刻:光刻是通过光源和掩膜对晶圆表面进行曝光,形成所需图形模式的一种工艺。

光刻是将光照射到光刻胶上,使其发生化学反应,然后通过相应的蚀刻工艺将光刻胶及下方的膜层去除。

3.扩散:扩散是将所需的杂质原子(如硼、磷等)掺入晶圆内部,形成p区和n区,以便实现PN结的形成。

扩散过程需要在高温条件下进行,使杂质原子能够在晶格中扩散。

4.制备:制备过程是将晶圆表面的绝缘层开孔,形成连接电路,然后通过金属线或导线连接各个元件。

制备步骤包括物理蚀刻、金属蒸镀、光刻等。

5.封装:IC芯片制造完成后,需要进行封装,将芯片连接到载体上,并保护和封闭。

封装工艺包括焊接引脚、防尘、封胶等步骤。

6.测试:IC制造完成后,需要进行各种电性能和可靠性测试,以确保芯片的质量和功能。

测试内容包括电流、电压、频率等方面的测试。

在IC制造的过程中,上述步骤是不断重复的,每一次重复都会在前一步骤的基础上进行,逐渐形成多层结构,最终形成完整的IC芯片。

清华大学 集成电路制造工艺 王水弟 课件第12章纳米时代的挑战-2

电容C与介电常数 k 的关系

对于某种给定的电解质材料,一个充满了这 种电解质的电容器的电容C与同一尺寸的真空电 容器的电容C0 之比叫做该材料的介电常量。

C k C0

C C0

(12 - 1)

kA 0 C kC0 t

其中

(12 - 2)

A: 面积(单位:平方米) k :两板之间电介质的介 电常数 0 :真空电容率 t :两板之间距离

第12章 纳米时代的挑战

本章内容 12.1 摩尔定律的极限 12.2 纳米时代的设备 12.3 纳米时代的材料

12.4 纳米时代的工艺 12.5 结束语

e

12.1 摩尔定律的极限

IC发展的两个驱动力 硅圆片的尺寸从 100mm → 125mm → 150mm → 200mm → 硅片尺寸 300mm → 450mm , 不断扩大 以提高芯片产量和降 低芯片成本,最终获 取更大的利润。

(摘自:苏州大学宁兆元,《世界科技研究与发展》2004年12月)

低 k 值电介材料

根据2004年的报导,比较有前途的低k值电介质 材料是:

● 英特尔公司的碳掺杂氧化物(CDO)

● DOW Chemical公司的旋转涂布聚合物

● Thomas West公司的多孔硅绝缘材料(k = 2.2)

● 应用材料公司的黑金钢石(一种有机和无机的混

PMOS 金属 PMOS 高k (鉿基)

nFET

STI

pFET

英特尔45nmHKMG(高k金属栅极)技术解析

据报道:氧化铪(HfO2 )栅极介电材料(1.0nmEOT);双 带边功函数金属栅极(TiN用于PMOS,TiAlN用于NMOS) 。 硅基板和HfO2层之间形成一个氧化硅(也可能是氧氮化硅)底部 接口层(BIL),避免了铪带来的不利之处(阈值电压牵制和载流 子迁移率降低)。

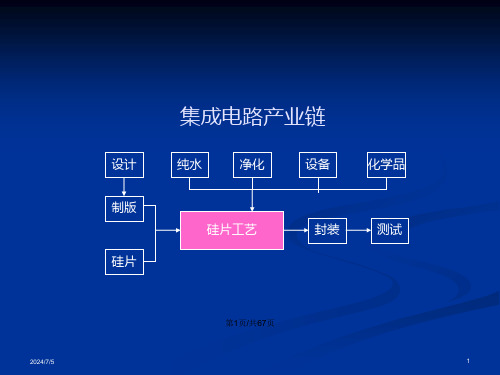

ic工艺流程及对应半导体设备

ic工艺流程及对应半导体设备?

答:IC(集成电路)工艺流程主要包括制造单晶硅片、设计IC、制作光罩、制造IC、测试IC和封装IC。

具体步骤如下:

1.制造单晶硅片:这是制造IC的第一步,单晶硅片的制造流程主要有拉晶、切割、研磨、抛光和清洗等五个步骤。

2. 设计IC:即设计ic电路,把设计好的电路转化为版图,ic设计决定了ic产品的性能和稳定性。

3.制作光罩:把设计好的ic电路版图等比例缩小转化到一块玻璃板上。

4.制造ic:在单晶硅片上制作集成电路芯片,整个过程主要有蚀刻、氧化、扩散和化学气相沉积薄膜以及金属溅镀等。

5.测试ic:为了确保ic的质量,还需要进行测试,包括功能测试和质量测试。

6.封装ic:封装ic是ic制造的最后一步流程,是指晶圆点测后对IC进行封装,主要的流程有晶圆切割,固晶、打线、塑封、切筋成形等。

而在这个工艺流程中,需要使用到的半导体设备包括但不限于光刻机、刻蚀机、薄膜沉积设备、离子注入机、化学机械抛光机、热处理设备以及测试与封装设备等。

这些设备在IC制造过程中扮演着重要的角色,它们的功能和性能直接影响到IC产品的质量和生产效率。

IC制作流程范文

IC制作流程范文IC(Integrated Circuit,集成电路)制作流程是指将电子元器件中的电晶体、电阻、电容等元件及其连接线等,通过特定的工艺步骤在半导体材料上制造出集成电路的过程。

下面将详细介绍IC制作的主要流程。

IC制作的主要流程包括芯片设计、掩膜制作、晶圆加工、电极制作、封装测试等几个主要步骤,具体如下:1.芯片设计:首先是根据需要设计出芯片电路。

设计师根据电路功能和性能要求,使用仿真软件进行电路设计,并通过仿真验证电路的准确性和可行性。

2.掩膜制作:设计好的电路通过计算机辅助设计软件(CAD)生成芯片的图形信息,然后将图形信息转化为半导体晶圆的光刻掩膜。

掩膜制作一般使用光刻技术,将电路设计的图形信息通过激光束刻写到光刻胶上,并通过光刻机将图形转移到硅片上。

3.晶圆加工:在晶圆加工过程中,需要将芯片的电路图案通过蚀刻、离子注入、扩散等工艺步骤加工到硅片上。

首先是将掩膜映射到硅片上,然后通过蚀刻工艺去除掉不需要的材料,留下芯片电路所需要的结构。

再通过离子注入或扩散工艺改变硅片的导电性能,形成导电区和绝缘区。

4.电极制作:在硅片表面形成电极是制作IC的重要步骤之一、首先是将金属薄膜或者金属线路沉积在硅片表面,通过各种光刻和蚀刻技术形成电极引线。

然后通过热处理来实现电极与半导体器件之间的连接,并形成稳定的电路结构。

5.封装测试:在IC制作完成后,需要将元器件和电路在硅片上面封装成IC。

同时还需要进行电性能测试、可靠性测试等。

封装是将芯片放置到适当的封装载体中,并通过焊接或粘接进行可靠地连接。

6.封装完成后,对IC进行电性能测试和可靠性测试。

测试包括功能测试、性能测试、温度测试、电压测试、电流测试等。

这些测试主要是为了验证芯片的各项电性能指标的准确性和稳定性。

以上是IC制作的主要流程,其中每个步骤都包括了一系列的操作和工艺方法。

整个IC制作流程需要高度的技术和严格的控制,以确保制造出优质的集成电路产品。

IC芯片生产工艺

IC芯片生产工艺IC芯片生产工艺是指将芯片设计完成后,通过一系列的制造过程将芯片加工成最终产品的技术和工艺。

IC芯片生产工艺一般包括前端工艺和后端工艺两个阶段。

前端工艺是指从半导体硅晶圆开始,通过一系列工艺步骤将晶圆上的电子器件逐步形成的过程。

具体包括晶圆切割、清洗、去胶、扩散、氧化、沉积、光刻、蚀刻、离子注入、退火等工艺步骤。

其中,扩散工艺用于形成掺杂区,氧化工艺用于制作氧化层,光刻工艺用于将电路图案转移到晶圆上,蚀刻工艺用于去除不需要的材料,离子注入工艺用于控制材料的电性质,退火工艺用于改善材料性质等。

前端工艺的主要目标是形成复杂的电路结构和控制电子器件的性能。

后端工艺是指将前端制造好的芯片进行封装和测试,形成最终的产品的过程。

具体包括封装、焊接、刻蚀、涂覆、热压、绑线、测试等工艺步骤。

封装工艺将芯片封装成塑料或陶瓷封装的封装体,焊接工艺用于将芯片与引脚焊接在一起,刻蚀工艺用于去除不需要的材料,涂覆工艺用于保护芯片表面,热压工艺用于固定芯片与封装体,绑线工艺用于连接芯片与外部引脚,测试工艺用于验证芯片的功能和性能。

后端工艺的主要目标是保证芯片的稳定性和可靠性。

IC芯片生产工艺的发展主要体现在以下几个方面:1. 工艺精度:随着技术的进步,工艺的精度不断提高,将电子器件的尺寸缩小到微纳米级别,提高了集成度和性能。

2. 制造工艺:引入了新的制造工艺,如激光技术、电子束曝光等,使得芯片制造更加精细和高效。

3. 材料创新:研发了新的材料,如高介电常数介质、高温超导材料等,用于提高芯片的速度和功能。

4. 封装技术:发展了新的封装技术,如3D封装、无线封装等,提高了芯片的集成度和可靠性。

IC芯片生产工艺的发展对于电子信息产业的发展起到了十分重要的推动作用。

随着技术的不断进步,IC芯片的生产工艺将会继续提高,为未来的科技发展提供更强大的支持。

IC基础知识及制造工艺流程

0.0008-cm(发射区)

第9页/共67页

2024/7/5

9

硅片主要技术指标

-晶向 (111)/(100) -掺杂类型/掺杂剂 P/N -电阻率 -直径/厚度 -平整度/弯曲度/翘曲度 -含氧量/含碳量 -缺陷(位错密度/层错密度) -表面颗粒

第10页/共67页

2024/7/5

10

目录

-最重要的半导体材料-硅 -构建集成电路的主要半导体器件 -关键的集成电路工艺制造技术 -集成电路技术发展趋势

第63页/共67页

2024/7/5

63

IC制造环境(3)

超纯化学药品

DRAM 64k 线宽(um) 3.0 试剂纯度 10pp

m 杂质颗粒 0.5u

颗粒含量 1000 (个/ ml) 金属杂质

256K 4M 2.0 1.0 5ppm 100pp

b

0.2u 0.1u

64M

0.5

80pp b 0.05u

等离子体 F*

扩散 吸附 反应

解吸附

第21页/共67页

2024/7/5

21

RIE刻蚀装置(Parallel Plate)

Gas

RF

2024/7/5

Pumping System

第22页/共67页

22

RIE刻蚀机 (AME8330)

第23页/共67页

2024/7/5

23

IC基础工艺(2)-刻蚀

被刻膜 SiO2 Si Al

第4页/共67页

2024/7/5

4

绝缘体/半导体/导体

-绝缘体 -半导体 -导体

电阻率=108-1018-cm 石英、玻璃、 塑料

电阻率=10-3-108-cm 锗、硅 、砷化镓 、磷化铟

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

4.

Discuss the key process and equipment used in each CMOS manufacturing step.

能讨论每一步流程的关键工艺和设备

Major Fabrication Steps in MOS Process Flow

Extraction assembly Analyzing magnet

Ion beam

Lighter ions

Process chamber

Heavy ions

Scanning disk

Graphite

Thin Film Metallization Bay

Simplified Schematics of CVD Processing System

top nitride

G D S G D S G D

Ion Implantation

Active Regions

Nitride Deposition

Contact Etch

Metal Deposition and Etch

CMOS Process Flow

• Overview of Areas in a Wafer Fab

– – – – – – Diffusion Photolithography Etch Ion Implant Thin Films Polish

Model of Typical Wafer Flow in a Sub-Micron CMOS IC Fab

Wafer Fabrication (front-end)

Gate Structure 多晶硅栅结构 Lightly Doped Drain Implants 轻掺杂漏注入 Sidewall Spacer 侧墙形成 Source/Drain Implants 源/漏注入 Contact Formation 接触孔形成

8

n+ LI metal M-3

13

ILD-4

Quartz tube

Temperaturesetting voltages

Heater 1

Heater 2

Heater 3 Three-zone Heating Elements

Pressure controller

Exhaust

Photolithography Bay in a Sub-micron Wafer Fab

12

M-2

ILD-3

11

M-1

ILD-2

10

ILD-1

Via

9

Poly gate

3

p+

5

p+

LI oxide STI n+ n+ p+

2 7

4

n-well

6

p-well

1

pEpitaxial layer

p+ Silicon substrate

CMOS Manufacturing Steps

8. 9. Local Interconnect 局部互连 Interlayer Dielectric to Via-1 通孔1和金属塞1的形成 10. First Metal Layer 金属1互连 11. Second ILD to Via-2 通孔2和金属塞2的形成 12. Second Metal Layer to Via-3

9、清洗 10、 1000 C干氧,~150Ǻ;保护外延层 11、Si3N4膜淀积:~750C LPCVD NH3+SiH2Cl2 ;保护有源区; CMP的阻挡材料 12、第三层掩膜:检测;由于特征尺寸减小,光刻难度增加。 13、STI槽刻蚀:F基或Cl基等离子体刻蚀;检测台阶高度、特征尺 寸、和腐蚀缺陷

e -

e

-

Glow discharge (plasma) Vacuum gauge

Ion sheath

e

Wafer Cathode electrode +

R

Flow of byproducts and process gases

Chamber wall Positive ion Radical chemical Vacuum line

Wafer Cassettes

Wafer Transfer System

Soft Bake

Cool Plate

Cool Plate

Hard Bake

Simplified Schematic of Dry Plasma Etcher

Gas distribution baffle Anode electrode Etchant gas entering gas inlet High-frequency energy RF coax cable Photon Electromagnetic field Free electron

Selective etching opens isolation regions in the epi layer.

+Ions

3

Photoresist

4

2

1

Nitride

Oxide n-well

4

h

p-well p- Epitaxial layer

STI trench

p+ Silicon substrate

Simplified Schematic of a Photolithography Processing Module

Load Station Vapor Prime Resist Coat Develop- Edge-Bead Rinse Removal Transfer Station Wafer Stepper (Alignment/Exposure System)

画出典型的流程图

2.

Give an overview of the six major process areas and the sort/test area in the wafer fab.

对6种主要工艺的应用和测试有大概的认识

3.

For each of the 14 CMOS manufacturing steps, describe its primary purpose.

Scanning ion beam

Photoresist Strip

Oxidation (Gate oxide)

Polysilicon Deposition

Polysilicon Mask and Etch

silicon nitride G ox S D S

Contact holes

Metal contacts G drain D S

CMOS Manufacturing Steps

1. 2. 3. 4. 5. 6. 7. Twin-well Implants 双阱注入 Shallow Trench Isolation 浅槽隔离

M-4 Passivation layer ILD-6

14

Bonding pad metal

ILD-5

n-well

Liner oxide

p-well p- Epitaxial layer

p+ Silicon substrate

Poly Gate Structure Process

18、去除氧化层:栅氧化前进行。

19、栅氧化层生长:完成后立即进行多晶硅淀积(~5000Ǻ) 20、第四层掩膜:光刻多晶硅栅;深紫外光刻;加抗反射涂层ARC;检测。 21、多晶硅栅刻蚀:先进的各向异性的等离子刻蚀机。

Gas inlet Process chamber Capacitivecoupled RF input

Chemical vapor deposition

Wafer Susceptor

Exhaust

Heat lamps

CVD cluster tool

Polish Bay in a Sub-micron Wafer Fab

p-well p- Epitaxial layer

p+ Silicon substrate

STI Formation

16、沟槽氧化抛光(CMP): 17、氮化物去除:热磷酸

Planarization by chemical-mechanical polishing

1

STI oxide after polish 2 Nitride strip

STI Oxide Fill

14、沟槽衬垫氧化: 1000 C干氧,~150Ǻ; 15|、沟槽CVD氧化物填充:可用高速淀积。

Trench fill by chemical vapor deposition Oxide

2

Trench CVD oxide Nitride

1

n-well

Liner oxide

Via M-3 ILD-5 M-4 Passivation layer ILD-6

14

Bonding pad metal

13

ILD-4

12

M-2

ILD-3

11

M-1

ILD-2

10

ILD-1

金属2互连 13. Metal-3 to Pad Etch 金属3 压点形成 14. Parametric Testing 测试

Wafer Start

Unpatterned Wafer Thin Films Polish

Completed Wafer

Diffusion

Photo

Etch

Test/Sort