第四章逻辑门电路作业题(参考答案)

数电第四章习题答案

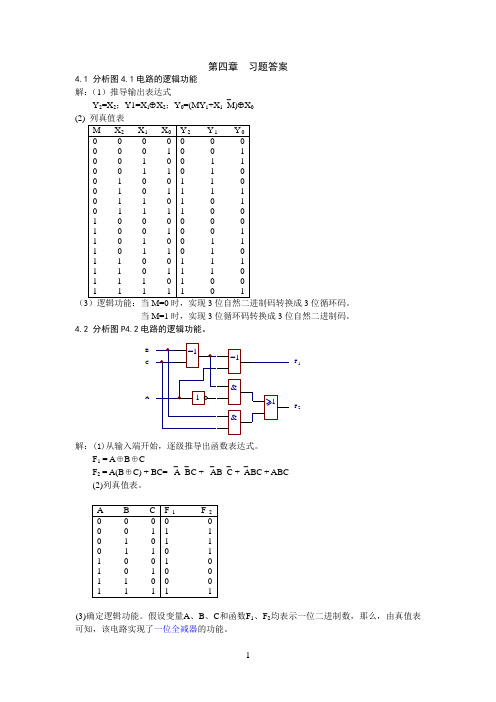

第四章习题答案4.1 分析图4.1电路的逻辑功能解:(1)推导输出表达式Y2=X2;Y1=X1⊕X2;Y0=(MY1+X1⎺M)⊕X0A 、B 、C 、F 1、F 2分别表示被减数、减数、来自低位的借位、本位差、本位向高位的借位。

A BCF 1F 2-被减数减 数借 位差4.3分析图4.3电路的逻辑功能 解:(1)F 1=A ⊕B ⊕C ;F 2=(A ⊕B)C+AB (2)(3)4.4 设ABCD 是一个8421BCD 码,试用最少与非门设计一个能判断该8421BCD 码是否大于等于5的电路,该数大于等于5,F= 1;否则为0。

解:(1)列真值表10 1 1 010 1 0 100 1 0 000 0 1 110 1 1 100 0 1 000 0 0 100 0 0 0F A B C D Ø1 1 1 0Ø1 1 0 1Ø1 1 0 0Ø1 0 1 1Ø1 1 1 1Ø1 0 1 011 0 0 111 0 0 0F A B C D(2)写最简表达式F = A + BD + BC=⎺A · BD · BC&&&DBC AF&4.6 试设计一个将8421BCD码转换成余3码的电路。

(F2=⎺C⎺D+CD F1=⎺D 电路图略。

4.7 在双轨输入条件下用最少与非门设计下列组合电路:(1)F(ABC)=∑m(1,3,4,6,7)(2) F(ABCD)=∑m(0,2,6,7,8,10,12,14,15)解:F=⎺B⎺D+A⎺D+BC∑+∑m)3(φ(DCFAB,,,7,4,0(10=) ,)12),9,8,6,5,2(解:函数的卡诺图如下所示:4.10 电话室对3种电话编码控制,按紧急次序排列优先权高低是:火警电话、急救电话、普通电话,分别编码为11,10,01。

试设计该编码电路。

F 1=A+BF 2=BA +4.11 试将2/4译码器扩展成4/16译码器 解:A 3A 2A 1 A 0⎺Y 0⎺Y 1⎺Y 2⎺Y 3 ⎺Y 4 ⎺Y 5⎺Y 6⎺Y 7 ⎺Y 8⎺Y 9⎺Y 10⎺Y 11 ⎺ Y 12⎺Y 13⎺Y 14⎺Y 154.12 试用74138设计一个多输出组合网络,它的输入是4位二进制码ABCD ,输出为: F 1 :ABCD 是4的倍数。

逻辑门电路习题

逻辑门电路习题一、选择题1.门电路的平均传输时间是()。

A.t pd=t PHL B.t pd=t PLH C.t pd=(t PHL+t PLH)/2 D. t pd=(t PHL-t PLH)/22.对TTL与非门多余输入端的处理,不能将它们()。

A.与有用输入端并联 B.接地 C.接高电平 D.悬空3.输出端可直接连在一起实现“线与”逻辑功能的门电路是()。

A.与非门 B.或非门 C.三态门 D.OC门4.为实现数据传输的总线结构,要选用()门电路。

A.或非 B.OC C.三态 D.与或非5.标准TTL电路的开门电阻R ON=2.1KΩ,一个3输入与门的A端接一个电阻R到地,要实现Y=BC,则R的取值应()。

A.小于700Ω B.大于2.1KΩ C.小于2.1KΩ D.可取任意值二、填空题6.用作线与逻辑的门只能是门。

7.三态门的输出可以出现、、三种状态。

8.可用作多路数据分时传输的逻辑门是门。

9.对CMOS逻辑门,未使用的输入端应当按逻辑要求接或接,而不允许。

10.标准TTL门输出高电平典型值是伏,低电平典型值是伏。

11.在TTL门电路中,输入端悬空在逻辑上等效于输入电平。

12.把两个OC门的输出端直接连在一起实现“与”逻辑关系的接法叫。

13.正逻辑系统规定,高电平表示逻辑态;低电平表示逻辑态。

14.TTL、CMOS电路的抗干扰能力是强于。

三、判断题15.CMOS门电路的多余输入端悬空时,在逻辑上等效于输入高电平。

16.用作线与逻辑的TTL门只能是OC门。

17. TTL或非门的多余输入端可以与其他使用端连接在一起,或者悬空处理。

18. CMOS与非门的多余输入端可以悬空处理。

(完整word版)电子技术基础数字部分第五版康光华主编第4章习题答案

第四章习题答案4.1.4 试分析图题4.1.4所示逻辑电路的功能。

解:(1)根据逻辑电路写出逻辑表达式:()()L A B C D =⊕⊕⊕ (2)根据逻辑表达式列出真值表:由真值表可知,当输入变量ABCD 中有奇数个1时,输出L=1,当输入变量中有偶数个1时,输出L=0。

因此该电路为奇校验电路。

4.2.5 试设计一个组合逻辑电路,能够对输入的4位二进制数进行求反加1 的运算。

可以用任何门电路来实现。

解:(1)设输入变量为A 、B 、C 、D ,输出变量为L3、L2、L1、L0。

(2)根据题意列真值表:(3)由真值表画卡诺图(4)由卡诺图化简求得各输出逻辑表达式()()()3L AB A C AD ABCD A B C D A B C D A B C D =+++=+++++=⊕++ ()()()2L BC BD BCD B C D B C D B CD =++=+++=⊕+ 1L CD CD C D =+=⊕0L D =(5)根据上述逻辑表达式用或门和异或门实现电路,画出逻辑图如下:A B CDL 3L 2L 1L 04.3.1判断下列函数是否有可能产生竞争冒险,如果有应如何消除。

(2)(,,,)(,,,,,,,)2578910111315L A B C D m =∑ (4)(,,,)(,,,,,,,)4024612131415L A B C D m =∑解:根据逻辑表达式画出各卡诺图如下:(2)2L AB BD =+,在卡诺图上两个卡诺圈相切,有可能产生竞争冒险。

消除办法:在卡诺图上增加卡诺圈(虚线)包围相切部分最小项,使2L AB BD AD =++,可消除竞争冒险。

(4)4L AB AD =+,在卡诺图上两个卡诺圈相切,有可能产生竞争冒险。

消除办法:在卡诺图上增加卡诺圈(虚线)包围相切部分最小项,使4L AB AD BD =++,可消除竞争冒险。

4.3.4 画出下列逻辑函数的逻辑图,电路在什么情况下产生竞争冒险,怎样修改电路能消除竞争冒险。

数字电路与逻辑设计习题_4第四章组合逻辑电路剖析

数字电路与逻辑设计习题_4第四章组合逻辑电路剖析第四章组合逻辑电路一、选择题1.下列表达式中不存在竞争冒险的有。

A.Y=B +A BB.Y=A B+B CC.Y =A B C +ABD.Y =(A+B )A D 2.若在编码器中有50个编码对象,则要求输出二进制代码位数为位。

A.5B.6C.10D.503.一个16选一的数据选择器,其地址输入(选择控制输入)端有个。

A.1B.2C.4D.16 4.下列各函数等式中无冒险现象的函数式有。

A.B A AC C B F ++= B.B A BC C A F ++=C.B A B A BC C A F +++=D.C A B A BC B A AC C B F +++++=E.B A B A AC C B F +++= 5.函数C B AB C A F ++=,当变量的取值为时,将出现冒险现象。

A.B=C=1B.B =C=0C.A =1,C=0D.A =0,B=0 6.四选一数据选择器的数据输出Y 与数据输入X i 和地址码A i 之间的逻辑表达式为Y = 。

A.3X A A X A A X A A X A A 01201101001+++B.001X A AC.101X A AD.3X A A 017.一个8选一数据选择器的数据输入端有个。

A.1 B.2 C.3 D.4 E.8 8.在下列逻辑电路中,不是组合逻辑电路的有。

A.译码器B.编码器C.全加器 D.寄存器9.八路数据分配器,其地址输入端有个。

A.1B.2C.3D.4E.8 10.组合逻辑电路消除竞争冒险的方法有。

A. 修改逻辑设计B.在输出端接入滤波电容C.后级加缓冲电路D.屏蔽输入信号的尖峰干扰 11.101键盘的编码器输出位二进制代码。

A.2B.6C.7D.812.用三线-八线译码器74LS 138实现原码输出的8路数据分配器,应。

A.A ST =1,B ST =D ,C ST =0 B. A ST =1,B ST =D ,C ST =D C.A ST =1,BST =0,CST =D D.A ST =D ,BST =0,CST =013.以下电路中,加以适当辅助门电路,适于实现单输出组合逻辑电路。

逻辑门电路 作业题(参考答案)

第四章逻辑门电路(Logic Gates Circuits)1.知识要点CMOS逻辑电平和噪声容限;CMOS逻辑反相器、与非门、或非门、非反相门、与或非门电路的结构;CMOS逻辑电路的稳态电气特性:带电阻性负载的电路特性、非理想输入时的电路特性、负载效应、不用的输入端及等效的输入/输出电路模型;动态电气特性:转换时间、传输延迟、电流尖峰、扇出特性;特殊的输入/输出电路结构:CMOS传输门、三态输出结构、施密特触发器输入结构、漏极开路输出结构。

重点:1.CMOS逻辑门电路的结构特点及与逻辑表达式的对应关系;2.CMOS逻辑电平的定义和噪声容限的计算;3.逻辑门电路扇出的定义及计算;4.逻辑门电路转换时间、传输延迟的定义。

难点:1.CMOS互补网络结构的分析和设计;2.逻辑门电路对负载的驱动能力的计算。

(1)PMOS和NMOS场效应管的开关特性MOSFET管实际上由4部分组成:Gate,Source,Drain和Backgate,Source和Drain之间由Backgate连接,当Gate对Backgate的电压超过某个值时,Source和Drain之间的电介质就会形成一个通道,使得两者之间产生电流,从而导通管子,这个电压值称为阈值电压。

对PMOS管而言,阈值电压是负值,而对NMOS管而言,阈值电压是正值。

也就是说,在逻辑电路中,NMOS管和PMOS管均可看做受控开关,对于高电平1,NMOS导通,PMOS截断;对于低电平0,NMOS截断,PMOS导通。

(2)CMOS门电路的构成规律每个CMOS门电路都由NMOS电路和PMOS电路两部分组成,并且每个输入都同时加到一个NMOS管和一个PMOS管的栅极(Gate)上。

对正逻辑约定而言,NMOS管的串联(Series Connection)可实现与操作(Implement AND Operation),并联(Parallel Connection)可实现或操作(Implement OR Operation)。

数字电子技术第四章课后习题答案(江晓安等编)

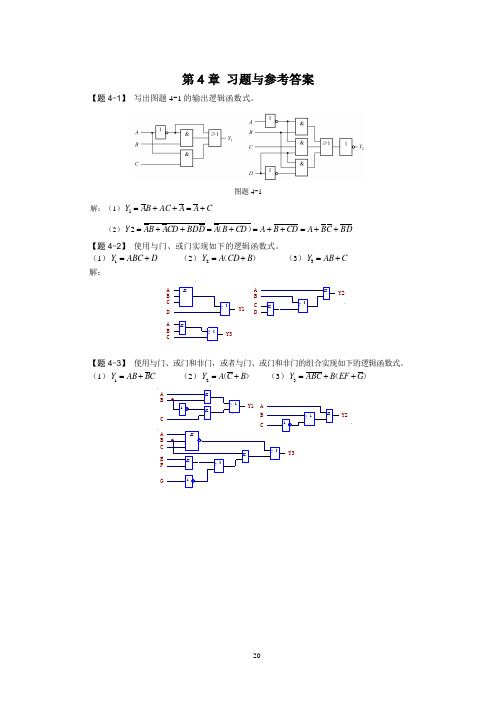

第四章组合逻辑电路1. 解: (a)(b)是相同的电路,均为同或电路。

2. 解:分析结果表明图(a)、(b)是相同的电路,均为同或电路。

同或电路的功能:输入相同输出为“1”;输入相异输出为“0”。

因此,输出为“0”(低电平)时,输入状态为AB=01或103. 由真值表可看出,该电路是一位二进制数的全加电路,A为被加数,B为加数,C为低位向本位的进位,F1为本位向高位的进位,F2为本位的和位。

4. 解:函数关系如下:SF++⊕=+ABSABS BABS将具体的S值代入,求得F 312值,填入表中。

A A FB A B A B A A F B A B A A F A A F AB AB F B B A AB F AB B A B A B A AB F B A A AB F B A B A B A F B A AB AB B A B A F B B A B A B A B A B A B A F AB BA A A B A A B A F F B A B A F B A B A F A A F S S S S =⊕==+==+⊕===+⊕===⊕===⊕===+⊕===+=+⊕===⊕==+==⊕==Θ=+=+⊕===+++=+⊕===+=⊕===⊕==+=+⊕==+=+⊕===⊕==01111111011010110001011101010011000001110110)(01010100101001110010100011000001235. (1)用异或门实现,电路图如图(a)所示。

(2) 用与或门实现,电路图如图(b)所示。

6. 解因为一天24小时,所以需要5个变量。

P变量表示上午或下午,P=0为上午,P=1为下午;ABCD表示时间数值。

真值表如表所示。

利用卡诺图化简如图(a)所示。

化简后的函数表达式为D C A P D B A P C B A P A P DC A PD B A P C B A P A P F =+++=用与非门实现的逻辑图如图(b )所示。

第4章 习题与参考答案20-35

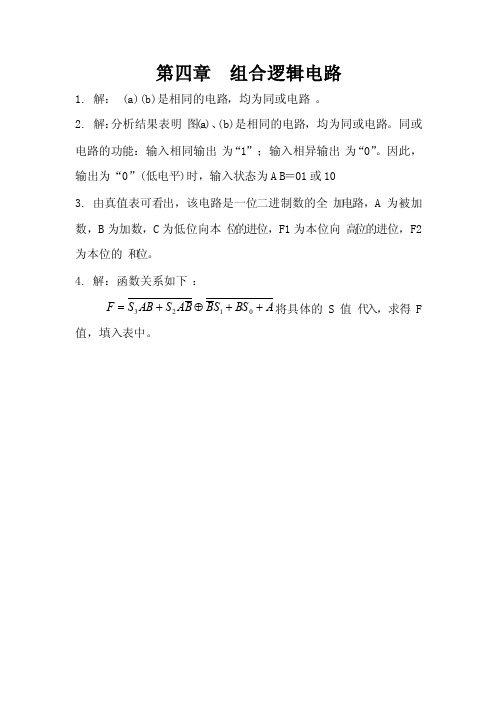

第4章 习题与参考答案【题4-1】 写出图题4-1的输出逻辑函数式。

图题4-1解:(1)C A A AC B A Y +=++=1(2)D B C B A CD B A CD B A D BD CD A B A Y ++=++=+=++=)(2 【题4-2】 使用与门、或门实现如下的逻辑函数式。

(1)1Y ABC D =+ (2)2Y A CD B =+() (3)3Y AB C =+ 解:&1≥AB C DY11≥&&A B C DY2&A B 1≥Y3C....【题4-3】 使用与门、或门和非门,或者与门、或门和非门的组合实现如下的逻辑函数式。

(1)1Y AB BC =+(2)2Y A C B =+() (3)3Y ABC B EF G =++()ABC.Y2A B C .E F G...【题4-4】试写出图题4-4所示电路的逻辑函数式,列出真值表,并分析该电路的逻辑功能。

图题4-4解:=1+ACBCABY+此电路是三人表决电路,只要有两个人输入1,输出就是1。

Y+CDABCDBA++⋅=⋅⋅=2BCDABCDCDDABCABBDCAABCDA该电路在4个输入中有3个为1时,输出Y2为1。

【题4-5】 逻辑电路与其输入端的波形如图题4-5所示,试画出逻辑电路输出端Y 的波形。

图题4-5解:B A Y +=BA.Y..【题4-6】 图题4-6所示的逻辑电路中,与非门为74LS00,或非门是74LS02,非门是74LS04。

试分析该电路的最大传输延迟时间。

图题4-6解:74LS00、74LS02和74LS04的最大t PHL 和t PLH 都是15ns ,因为A 信号经过4级门达到输出端X ,因此最大传输延迟时间为4×15ns=60ns 。

【题4-7】 图题4-7所示的是家用报警器装置,该装置具有6个开关,各开关动作如下:ALARM....图题4-7人工报警开关M ,该开关闭合时,报警信号ALARM=1,开始报警。

数电习题解答_杨志忠_第四章练习题_部分

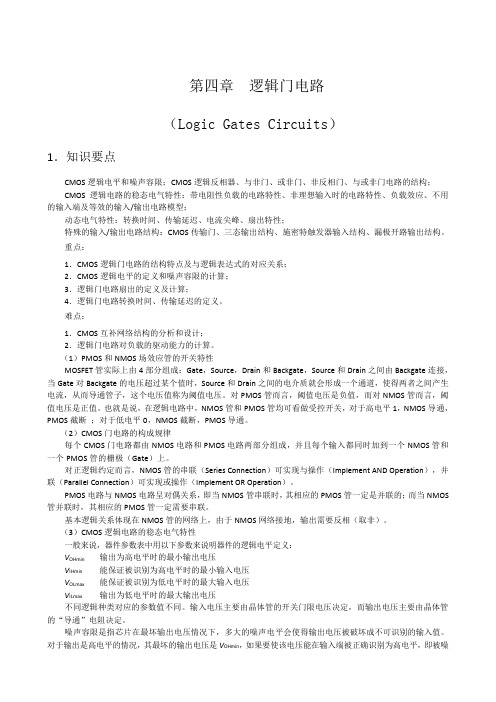

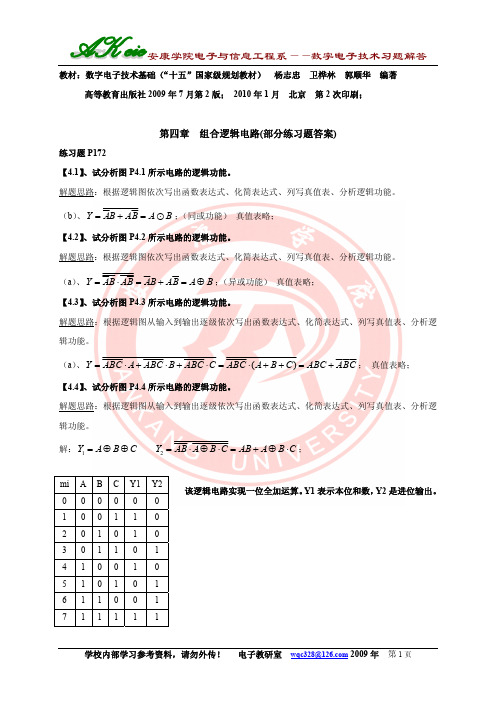

教材:数字电子技术基础(“十五”国家级规划教材) 杨志忠 卫桦林 郭顺华 编著高等教育出版社2009年7月第2版; 2010年1月 北京 第2次印刷;第四章 组合逻辑电路(部分练习题答案)练习题P172【4.1】、试分析图P4.1所示电路的逻辑功能。

解题思路:根据逻辑图依次写出函数表达式、化简表达式、列写真值表、分析逻辑功能。

(b )、Y AB AB A B =+=:;(同或功能) 真值表略; 【4.2】、试分析图P4.2所示电路的逻辑功能。

解题思路:根据逻辑图依次写出函数表达式、化简表达式、列写真值表、分析逻辑功能。

(a )、Y AB AB AB AB A B =⋅=+=⊕;(异或功能) 真值表略; 【4.3】、试分析图P4.3所示电路的逻辑功能。

解题思路:根据逻辑图从输入到输出逐级依次写出函数表达式、化简表达式、列写真值表、分析逻辑功能。

(a )、()Y ABC A ABC B ABC C ABC A B C ABC ABC =⋅+⋅+⋅=⋅++=+; 真值表略; 【4.4】、试分析图P4.4所示电路的逻辑功能。

解题思路:根据逻辑图从输入到输出逐级依次写出函数表达式、化简表达式、列写真值表、分析逻辑功能。

解:12 Y A B C Y AB A B C AB A B C =⊕⊕=⋅⊕⋅=+⊕⋅;该逻辑电路实现一位全加运算。

Y1表示本位和数,Y2是进位输出。

mi A B C Y1 Y2 0 0 0 0 0 0 1 0 0 1 1 02 0 1 0 1 03 0 1 1 0 14 1 0 0 1 05 1 0 1 0 16 1 1 0 0 17 1 1 1 1 1【4.6】、写出图P4.6所示电路的逻辑函数表达式,并且把它化成最简与或表达式。

解题思路:变量译码器实现逻辑函数是把逻辑变量输入译码器地址码,译码器输出i i m Y =,再用与非门(输出低电平有效)变换就可以得到所需的逻辑函数,输出函数具有下列的表达形式:(,,)0356m(0,3,5,6)A B C F Y Y Y Y ==∑。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第四章逻辑门电路(Logic Gates Circuits)1.知识要点CMOS逻辑电平和噪声容限;CMOS逻辑反相器、与非门、或非门、非反相门、与或非门电路的结构;CMOS逻辑电路的稳态电气特性:带电阻性负载的电路特性、非理想输入时的电路特性、负载效应、不用的输入端及等效的输入/输出电路模型;动态电气特性:转换时间、传输延迟、电流尖峰、扇出特性;特殊的输入/输出电路结构:CMOS传输门、三态输出结构、施密特触发器输入结构、漏极开路输出结构。

重点:1.CMOS逻辑门电路的结构特点及与逻辑表达式的对应关系;2.CMOS逻辑电平的定义和噪声容限的计算;3.逻辑门电路扇出的定义及计算;4.逻辑门电路转换时间、传输延迟的定义。

难点:1.CMOS互补网络结构的分析和设计;2.逻辑门电路对负载的驱动能力的计算。

(1)PMOS和NMOS场效应管的开关特性MOSFET管实际上由4部分组成:Gate,Source,Drain和Backgate,Source和Drain之间由Backgate连接,当Gate对Backgate的电压超过某个值时,Source和Drain之间的电介质就会形成一个通道,使得两者之间产生电流,从而导通管子,这个电压值称为阈值电压。

对PMOS管而言,阈值电压是负值,而对NMOS管而言,阈值电压是正值。

也就是说,在逻辑电路中,NMOS管和PMOS管均可看做受控开关,对于高电平1,NMOS导通,PMOS截断;对于低电平0,NMOS截断,PMOS导通。

(2)CMOS门电路的构成规律每个CMOS门电路都由NMOS电路和PMOS电路两部分组成,并且每个输入都同时加到一个NMOS管和一个PMOS管的栅极(Gate)上。

对正逻辑约定而言,NMOS管的串联(Series Connection)可实现与操作(Implement AND Operation),并联(Parallel Connection)可实现或操作(Implement OR Operation)。

PMOS电路与NMOS电路呈对偶关系,即当NMOS管串联时,其相应的PMOS管一定是并联的;而当NMOS管并联时,其相应的PMOS管一定需要串联。

基本逻辑关系体现在NMOS管的网络上,由于NMOS网络接地,输出需要反相(取非)。

(3)CMOS逻辑电路的稳态电气特性一般来说,器件参数表中用以下参数来说明器件的逻辑电平定义:V OHmin输出为高电平时的最小输出电压V IHmin能保证被识别为高电平时的最小输入电压V OLmax能保证被识别为低电平时的最大输入电压V ILmax输出为低电平时的最大输出电压不同逻辑种类对应的参数值不同。

输入电压主要由晶体管的开关门限电压决定,而输出电压主要由晶体管的“导通”电阻决定。

噪声容限是指芯片在最坏输出电压情况下,多大的噪声电平会使得输出电压被破坏成不可识别的输入值。

对于输出是高电平的情况,其最坏的输出电压是V OHmin,如果要使该电压能在输入端被正确识别为高电平,即被噪声污染后的电压值应该不小于V IHmin,则噪声容限为V OHmin?V IHmin。

对于输出是低电平的情况,噪声容限为V ILmax?V OLmax。

输出电流的定义如下。

I OLmax:输出低态且仍能维持输出电压不大于V OLmax时,输出端能吸收的最大电流;I OHmax:输出高态且仍能维持输出电压不小于V OHmin时,输出端可提供的最大电流。

(4)扇出逻辑门的扇出(fanout)是指该门电路在不超出其最坏情况负载规格的条件下能驱动的输入端的个数。

扇出不仅依赖于输出端的特性,还依赖于它驱动的输入端的特性。

扇出的计算必须考虑输出的两种可能状态:高电平状态和低电平状态。

直流扇出能力的计算方法为:最大输出电流/最大输入电流。

一个门电路的高电平扇出和低电平扇出不一定相等。

通常,门电路的总扇出应为高电平扇出和低电平扇出中的较小值。

(5)CMOS电路的动态特性转换时间可分为输出上升时间t r和输出下降时间t f,其值的大小和门的导通电阻与负载电容之积成正比。

传输延迟时间t p指的是从输入变化到输出变化所需的时间。

其值取决于器件内部的结构与信号传输的路径;同一个器件,不同输入/输出间的传输延迟可能不同,由多种因素决定。

(6)CMOS电路的功耗输出不变时的CMOS电路功耗称为静态功耗。

CMOS电路在状态转换时消耗的电能称为动态功耗,其来源是输出端上的电容性负载C L,输出从低到高转换时,电流流过P沟道晶体管给负载充电,类似地,输出从高到低转换时,电流流过N沟道晶体管给负载放电,这两种情况下晶体管导通的电阻都消耗功率。

充电开始时电压变化为V DD,结束时电压变化很小,故平均电压变化为V DD/2,则每次转换消耗的电能为2L DD /2C V,若每秒钟变化2f次,则由电容性负载引起的动态功耗为2L DDC V f。

2.ExercisesThe Stub Series Terminalted low Voltage(SSTV) logic family, used for SDRAM modules, defines a LOW signal to be in the range ~, and a HIGH signal to be in the range ~. Under a positive-logic convention, indicate the logic value associated with each of the following signal levels:(a) (b) (c) (d) ?(e) (f) ? (g) (h)(a) 0 (b) 0 (c) 1 (d) undefined(e) undefined (f) undefined (g) 1 (h) undefinedRepeat exercise using a negative-logic convention.(a) 1 (b) 1 (c) 0 (d) undefined(e) undefined (f) undefined (g) 0 (h) undefinedTrue or false: For a given set of input values, a NAND gate produces the opposite output as a NOR gate.When the two inputs are different, it will be ture.For a given silicon area, which is likely to be faster, a CMOS NAND gate or a CMOS NORCMOS NAND will be faster than CMOS NOR.Which has fewer transistors, a CMOS inverting gate or a noninverting gateCMOS inverting gate has fewer transistors.For each of the following resistive loads, determine whether the output drive specifications of the 74HC00 over the commercial operating range are exceeded (use V OLmax = ,V OHmin = and V CC = V). You may not exceed I OLmax (4mA) or I OHmax (4mA) in any state.(1) ??to V CC and 820 ??to GND (2) 470 ??to V CC and 470 ??to GND(1) V Thev = Vcc ×R2 / (R1+R2)= 5×820 / (1200+820)≈I Short = Vcc / R1 R Thev = V Thev / I Short= R1×R2 / (R1+R2)= 1200×820 / (1200+820)≈ ?∵V OHmin = ∴ I OH = (V OHmin -V Thev ) / R Thev ≈ mA < I OHmax = 4 mA ∵V OLmax = ∴ I OL = (V Thev - V OLmax ) / R Thev ≈ mA < I OLmax = 4 mA 因此,没有超出商用工作范围,可以正常驱动负载。

(2) V Thev = Vcc ×R2 / (R1+R2)= 5 / 2=I Short = Vcc / R1 R Thev = V Thev / I Short = R1×R2 / (R1+R2) = 470 / 2= 235 ?∵V OHmin = ∴ I OH = (V OHmin -V Thev ) / R Thev ≈OHmax ∵V OLmax = ∴ I OL = (V Thev - V OLmax ) / R Thev ≈ mA > I OLmax = 4 mA 因此,超出了商用工作范围,不能驱动负载。

4.7 A particular Schmitt-trigger inverter has ILmax V = V, IHmin V = V, T+V = V, and T V - = V. How much hysteresis does it haveHysteresis = T+V -T V -= =Discuss the pros and cons of larger versus smaller pull-up resistors for open-drain CMOS outputs.较小的上拉电阻:优点是输出电平在上升时较快,使得其工作运行的速度较快;缺点是在输出低电平时电源对地的电流较大,使得其功耗较大。

较大的上拉电阻:优点是在输出低电平时电源对地的电流较小,使得其功耗较小;缺点是输出电平在上升时较慢,使得其工作运行的速度较慢。

How many diodes are required for an n-input diode AND gaten diodes are required.Compute the maximum fanout for each of the following cases of a TTL output driving multiple TTL inputs. Also indicate how much “excess” driving capability is available in the LOW or HIGH state for each case. ( Refer to datasheets in Appendix )(1) 74LS driving 74AS (2) 74LS driving 74F(1) 根据数据表,74LS的I OLmax = 8 mA,74AS的I ILmax = mA∴ Low-state Fan-Out = 8 / = 1674LS的I OHmax = -400μA,74AS的I IHmax = 20μA∴ High-state Fan-Out = 400 / 20 = 20因此,总的最大扇出为16。