PLL锁相环电路

《应用于LVDS的锁相环电路研究》

《应用于LVDS的锁相环电路研究》一、引言随着现代电子技术的飞速发展,数据传输速率的要求日益提高,低电压差分信号传输(LVDS)技术因其低功耗、高速度和低噪声的特性,在高速数据传输领域得到了广泛应用。

锁相环(PLL)电路作为LVDS系统中的关键部分,其性能的优劣直接影响到整个系统的稳定性和传输质量。

因此,对应用于LVDS的锁相环电路进行研究具有重要的现实意义。

二、锁相环电路的基本原理锁相环电路是一种闭环相位控制系统,主要由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成。

其基本原理是通过鉴相器比较输入信号和压控振荡器输出的信号之间的相位差,将相位差转换为电压或电流信号,经过环路滤波器的滤波后,控制压控振荡器的频率和相位,使输出信号的相位与输入信号的相位保持一致。

三、LVDS中锁相环电路的应用在LVDS系统中,锁相环电路主要用于实现数据的同步传输。

由于LVDS采用差分信号传输方式,要求发送端和接收端之间的时钟信号必须保持严格的同步。

锁相环电路通过捕获输入信号的相位信息,将其与压控振荡器输出的信号进行比对和调整,从而保证数据的准确传输。

四、应用于LVDS的锁相环电路设计要点在应用于LVDS的锁相环电路设计中,需要注意以下几个要点:1. 输入范围和稳定性:设计时应考虑到输入信号的范围、频率波动和噪声干扰等因素,确保鉴相器能够准确捕获输入信号的相位信息。

2. 环路滤波器的设计:环路滤波器的作用是滤除鉴相器输出的高频噪声和杂散信号,为压控振荡器提供稳定的控制信号。

设计时需要考虑滤波器的带宽、阶数和稳定性等因素。

3. 压控振荡器的选择:压控振荡器的性能直接影响到锁相环电路的频率和相位调整范围。

选择时需要考虑其频率范围、相位噪声、功耗和稳定性等因素。

4. 电路布局与调试:在电路布局和调试过程中,需要考虑到电磁干扰(EMI)和电磁兼容性(EMC)等问题,确保锁相环电路的稳定性和可靠性。

五、实验结果与分析通过实验验证了应用于LVDS的锁相环电路的有效性和性能。

毕业设计论文:PLL锁相环电路

1摘 要随着通信及电子系统的飞速发展,促使集成锁相环和数字锁相环突飞猛进。

本次毕业设计的主要任务是,采用0.180.18μμm CMOS 工艺,设计实现一个基于改进的鉴频鉴相器,压控振荡器,环路滤波器的全集成的CMOS PLL 锁相环电路,设计重点为PLL 锁相环电路的版图设计,设计工具为Laker 。

本论文介绍了PLL 锁相环电路的基本原理以及其完整的版图设计结果。

本次设计表明,采用该方案实现的锁相环电路主要功能工作正常,初步达到设计要求。

求。

关键词:PLL 锁相环电路,鉴频鉴相器,压控振荡器,环路滤波器,版图设计,0.180.18μμm CMOS 工艺工艺AbstractWith the development of the communications and electronic systems, the technology of the integrated PLL and digital PLL develops rapidly.The main task of graduation is to design and realize a fully integrated CMOS PLL circuit which is based on an improved phase detector, VCO, loop filter using the 0.18μm CMOS technology 0.18μm CMOS technology. The design focus on the layout of the PLL circuit, and the . The design focus on the layout of the PLL circuit, and the design tools is the Laker.This paper introduces the basic principles of PLL phase locked loop circuit and its comprehensive layout results. This design shows that the program implemented by the main function of PLL circuit is working well, and it meets the design requirements.Key words:PLL phase locked loop circuits, popularly used phase detectors, discrimination, VCO loop filter, layout design, 0.18 μm CMOS process目 录 (11)摘 要.............................................................................................................................. (22)Abstract .......................................................................................................................... (44)第1章 绪论................................................................................................................ (44)1.1 锁相技术的发展.............................................................................................. (44)1.2 锁相环路的主要特性......................................................................................1.3 PLL锁相环的应用领域 (5)第2章 基于CMOS锁相环的电路设计 (7)2.1 锁相环的基本组成.......................................................................................... (77) (77)2.2 锁相环工作原理.............................................................................................. (88)2.3 鉴相器..............................................................................................................2.3.1 鉴频鉴相器(PFD) (9) (110)2.3.2 鉴频鉴相器设计.................................................................................. (110)2.4 环路滤波器....................................................................................................11 (11)2.5 压控振荡器....................................................................................................第3章 关于COMS锁相环的版图设计 (12) (112)3.1 电路设计........................................................................................................3.2 版图设计........................................................................................................ (112) (113)3.2.1 版图设计规则检查.............................................................................. (113)3.2.2 注意事项..............................................................................................3.3 锁相环的版图设计........................................................................................ (115) (117)第4章 结束语............................................................................................................ (118)参考文献...................................................................................................................... (119)致谢..............................................................................................................................第1章 绪论1.1锁相技术的发展 锁相技术起源于20世纪30年代,提出无线电调幅信号的锁相同步检波技术。

简述锁相环电路的关键指标

简述锁相环电路的关键指标锁相环(PLL)是一种电路系统,它以某个外部参考信号为基准,通过比较输出信号和输入信号的相位差,实现信号的同步和跟踪。

锁相环电路广泛应用于通信、计算机、控制系统等领域,其关键指标对于性能和稳定性具有重要意义。

锁相环电路的关键指标有以下几个方面:1. 频率稳定性:频率稳定性是指锁相环输出信号的频率与参考信号的频率之间的稳定性。

一般情况下,频率稳定性可以用频率偏差和频率漂移来描述。

频率偏差是指锁相环输出信号的实际频率与参考信号频率之间的偏离程度,频率漂移是指锁相环输出信号的频率随时间的变化趋势。

在实际应用中,频率稳定性通常是评价锁相环电路性能的重要指标,特别是在无线通信系统中,频率稳定性的好坏直接影响到系统的性能和覆盖范围。

2. 锁定时间:锁定时间是指锁相环从失锁状态到稳定锁定状态所需的时间。

在实际应用中,锁定时间也是锁相环性能的重要指标之一。

一般情况下,锁相环的锁定时间越短越好,因为锁定时间短意味着锁相环能够更快地跟踪和同步输入信号。

在快速变化的环境中,锁定时间短可以使锁相环更好地适应信号的变化,保持稳定的工作状态。

3. 相位噪声:相位噪声是指锁相环输出信号的相位随机扰动的程度。

通常情况下,相位噪声可以通过相位噪声密度来描述。

相位噪声对于一些高精度的应用来说是非常重要的,比如雷达、卫星导航等系统,因为相位噪声的存在会影响到系统的精度和测量精度。

4. 抑制比:抑制比是指锁相环输出信号与输入信号的比较结果的信噪比。

在实际应用中,抑制比是评价锁相环抑制噪声和干扰的重要指标之一。

抑制比越大,意味着锁相环对输入信号的跟踪能力和抗干扰能力越强。

除了以上几个关键指标之外,锁相环的带宽、稳定性、幅度恢复时间、输出电平等指标也是需要考虑的重要因素。

带宽是指锁相环对输入信号的跟踪范围,通常用于描述锁相环的跟踪速度和跟踪能力。

在很多应用中,锁相环的带宽需要根据具体的要求来调整,以满足不同的跟踪和同步要求。

pll锁相环原理

pll锁相环原理PLL锁相环原理PLL锁相环是一种常见的电路,它可以将输入信号的频率和相位与参考信号同步。

PLL锁相环的原理是通过反馈控制,使输出信号的频率和相位与参考信号保持一致。

PLL锁相环广泛应用于通信、计算机、音频、视频等领域。

PLL锁相环由相位检测器、低通滤波器、振荡器和分频器组成。

相位检测器用于比较输入信号和参考信号的相位差,输出一个误差信号。

低通滤波器用于滤除误差信号中的高频成分,得到一个平滑的误差信号。

振荡器用于产生输出信号,其频率和相位受到误差信号的控制。

分频器用于将输出信号分频,以便与参考信号进行比较。

PLL锁相环的工作原理如下:首先,输入信号和参考信号经过相位检测器比较,得到一个误差信号。

然后,误差信号经过低通滤波器滤除高频成分,得到一个平滑的误差信号。

接着,平滑的误差信号控制振荡器产生输出信号,其频率和相位受到误差信号的控制。

最后,输出信号经过分频器分频,与参考信号进行比较,得到一个新的误差信号,反馈给相位检测器,形成一个闭环控制系统。

PLL锁相环的优点是具有高精度、高稳定性、快速响应等特点。

它可以将输入信号的频率和相位与参考信号同步,实现信号的精确控制和处理。

PLL锁相环在通信系统中广泛应用,例如频率合成器、时钟恢复器、调制解调器等。

在计算机系统中,PLL锁相环用于时钟同步、数据传输等方面。

在音频、视频系统中,PLL锁相环用于数字信号处理、数字时钟恢复等方面。

PLL锁相环是一种重要的电路,它可以实现信号的精确控制和处理。

它的原理是通过反馈控制,使输出信号的频率和相位与参考信号保持一致。

PLL锁相环在通信、计算机、音频、视频等领域都有广泛的应用。

锁相环

i (t ),o (t )

瞬时相位

uo (t ) U 2m cos[ot o (t )] U 2m coso 式中, 0 是为压控振荡器在输入控制电压为零或为直流

电压时的振荡频率,称为电路的固有振荡频率。设乘法器 的增益系数为Am,则鉴相器输出的误差电压ud(t)

在控制电压的作用下,输出信号频率在固有频率的基础上 按一定规律变化的振荡电路。

作用——使振荡频率向输入信号的频率靠拢,直至两者的频 率相同,相位差恒定。

3 锁相环的基本组成分析

3、压控振荡器(VCO)

输入输出特性(线性):

o(t ) o Aouc(t )

Ao

压控灵敏度

3 锁相环的基本组成分析

pe(t ) AdAoAF(p )sin e(t ) pi(t )

瞬时频差 控制频差 固有频差

捕捉过程—环路由失锁进入锁定的过程

捕捉带(Δωp )—— 环路由失锁状态进入锁定状态所 允许信号频率偏离的最大值。

捕捉时间(τP )——环路由失锁状态进入锁定状态所 需的时间

跟踪过程—环路维持锁定的过程

1 锁相环路概述 一、基本概念(绪)

其中,当输出信号频率与输入信号频率相同时,输出信号与 输入信号之间的相位差同步(相位差为常数)。故称为锁相 环路,简称为锁相环。 其中,频率相同是目的,相位同步(锁定)是手段。 (具体):锁相环将输入信号与输出信号间的相位进行比较, 产生相位误差电压,来调整输出信号的频率,最终达到:相 位锁定,信号同频。

则上式可写为

3 锁相环的基本组成分析

3、压控振荡器(VCO)

压控振荡器传递给鉴相器的反馈信号起作用的不是瞬时角 频率而是它的瞬时相位。 所以,VCO在锁相环中起了一次 积分作用,因此也称为环路中的固有积分环节。 对 o( t ) o Aouc(t ) 积分,得

PLL锁相环详解-经典收藏

PLL的概念我们所说的PLL。

其实就是锁相环路,简称为锁相环。

许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。

锁相环路是一种反馈控制电路,简称锁相环(PLL)。

锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

目前锁相环主要有模拟锁相环,数字锁相环以及有记忆能力(微机控制的)锁相环。

PLL的组成锁相环通常由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成,锁相环组成的原理框图如图8-4-1所示。

锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成uD(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压uC(t),对振荡器输出信号的频率实施控制。

压控振荡器(VCO)的基本概念调节可变电阻或可变电容可以改变波形发生电路的振荡频率,一般是通过人的手来调节的。

而在自动控制等场合往往要求能自动地调节振荡频率。

常见的情况是给出一个控制电压(例如计算机通过接口电路输出的控制电压),要求波形发生电路的振荡频率与控制电压成正比。

这种电路称为压控振荡器,又称为VCO或u-f转换电路。

压控振荡器是锁相环中关键部件,在实际应用中有很多种结构。

压控振荡器(VCO)电路的举例和原理利用集成运放就可以构成精度高、线性好的压控振荡器。

我们知道积分电路输出电压变化的速率与输入电压的大小成正比,如果积分电容充电使输出电压达到一定程度后,设法使它迅速放电,然后输入电压再给它充电,如此周而复始,产生振荡,其振荡频率与输入电压成正比。

即压控振荡器。

模拟电子技术基础 7.3锁相环路(PLL)PPT课件

LF

VCO

输入调频信号

输出解调信号

uC(t)

捕捉带 > 输入调频信号的最大频偏

环路带宽>输入调频信号中调制信号的频谱பைடு நூலகம்度

为实现不失真解调,要求:

2. 调幅波的同步检波

乘积型同步检波框图

AMXY

LPF

uO(t)

ur(t)

us(t)

同步信号利用PLL提取

2. 调幅波的同步检波

PDⅡ的输入信号只在上升沿起作用,故该PD能处理非常窄的脉冲。

工作波形

VCO输入

VDD

PDⅡ输出

u14

u3

u13

锁定指示:锁定时高电平 失锁时低电平

u1

u9

PDⅡ称为鉴频鉴相器,因为:

o

uD(t)

PLL基本方程 的含义?

PLL基本方程 的含义?

7.3 锁相环路

可以锁定相位,可以消除频率误差,实现频率的无误差跟踪

主要要求:

掌握PLL的基本组成、工作原理和锁定的概念。

了解PLL的相位模型和基本方程。

了解PLL的捕捉与跟踪。

7.3 锁相环路

了解集成PLL和PLL的应用。

7.3.1 锁相环路基本原理

一、 锁相环路基本组成

鉴相器(PD):用以比较ui、 uo相位, 输出反映相位误差 的电压uD(t)

CMOS锁相环路CD4046简介

为数字PLL。内有两个PD、VCO、缓冲放大器、输入信号放大与整形电路、内部稳压器等。

具有电源电压范围宽(5~15V)、功耗低、输入阻抗高等优点。工作频率0~1MHz

内部VCO产生50%占空比的方波。输出电平可与TTL电平或CMOS电平兼容。

解调电压输出

锁相环PLL原理与应用

V V

2—9KHZ频率合成器

9V 100K 10K 47n

16 13 9

晶振

14

40 46

Uo 4

1K Hz

3

11

67 5 8

10 0K

1n

9V

3 16 RE SET

14

15

40 17

8

13

2 4 7 10 1 5 6 9 11

X2 X4 X6 X8 X1 X3 X5 X7 X9

3)拨盘开关式1—999KHZ

百位

A VD D

4X 100 K

8421

十位

A VD D

4X 100 K

8421

个位

A VD D

4)健盘置数式1—999KHZ频率合 成器 (P12)

• 就是用数字健盘以及某些数字IC替代拨盘 V开关构成1——999KHZ频率合成器。最终

应做到:当顺序按键盘旳任意三个健(如 5.9.2)时,则输出信号旳频率就为592KHz。 置数部分旳框图如图

捕获带旳测量

• 环路失锁后,缓慢变化信号源频率, 从高端或低端向4046A旳中心 频率接近,当信号源频率分别为fP H和fPL时,环路又锁定。则环路捕 获带ΔfP = fPH-fPL。

f H f P fL f o L P f H H f H

ωn、ξ旳测量 P(8)

9V

9V

10K

W1

10K

16 15 14 13 12 11 10

9

晶振

14

4

OU T

1K Hz

PD 2

40 46

VC O

3

8

5 11 6

7

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

R2 10 0K

-5 V R3

10 0K

VCO

Uo

PLL锁相环电路

三、环路开环增益(KH)的测量

• 当鉴相器比较两同相信号时,UF = 0,VC0 振荡于fmin; 当鉴相器比较两反相信号时, UF = VDD,VCO振荡于fmax

• 在理想情况下 • KH = 2(fmax - fmin)

U P L V i U

PLL锁相环电路

捕捉带的测量

• 环路失锁后,缓慢改变信号源频率,

从高端或低端向4046A的中心

频率靠近,当信号源频率分别为fP H和fPL时,环路又锁定。则环路捕 捉带ΔfP = fPH-fPL。

fHL fPL f o fPH fHH

f

PLL锁相环电路

ωn、ξ的测量 P(8)

9V

9V

10K

W1

1 0K

PLL锁相环电路

-

同步带ωH,捕捉带ωp 和VCO 中 心频率ωo的 关系

o P H

PLL锁相环电路

实验原理及步骤 P(4)

• CD4046原理图 Ui 14

4046

A1

P D1

16 V CC

2

3

4

6

11 7

V CO

12

5

8

P D2

+ A2

-

13 1

9

10

15

PLL锁相环电路

实验一、PLL参数测试(P5)

PLL锁相环电路

• 但当信号源频率远大于(高端)或远小于 (低端)4046A的中心频率时,Ui波 形还保持稳定清晰,但Uo不能保持稳定清 晰,这就是失锁。记下刚出现失锁时的Ui 频率即高端频率fHH和低端频率fHL,则同步 带ΔfH = fHH-fHL 。由于我们用的是 PD1,是异或门相鉴器,当Ui和Uo为分数 倍数关系时,也可能出现两个稳定的波形, 这种情况应认为是“失锁”。只有出现两 个同频的稳定波形时才认为是“锁定

dt

KOUF

• 二.鉴相器(PD) • Ud = Kd *θ • Kd 为鉴相灵敏度 • • 三.压控振荡器(VCO) (P2) • ωo(t)= ωom + K0 UF(t) • K0——VCO控制特性曲线的斜率,常

称为VCO的控制灵敏度,或称压控灵 敏度。

PLL锁相环电路

四、环路滤波器,这里仅讨论 无源比例积分滤波器

• 其传递函数为: R1

KF(s)U UO i((ss))s(1 s2 21 )1Ui

R2

Uo

C

• 式中:τ1 = R1 C

•

τ2 = R2 C

PLL锁相环电路

• 当锁相环处于锁定状态时,鉴相器

(PD)的两输入端一定是两个频率

完全一样但有一定相位差的信号。如

果它们的频率不同,则在压控振荡器

(VCO)的输入端一定会产生一个

种可能 Vo

L R

欠阻尼 临界阻尼

Vi

Vo

C

过阻尼

t

PLL锁相环电路

当锁相环的输入信号的相位有一个 阶跃跳变时,输出信号相位的变化 也有三种情况

Vi Vo

Qo

欠阻尼

临界阻尼

过阻尼

t

PLL锁相环电路

ωn、ξ就是指欠阻尼振荡时的 振荡频率和和阻尼系数

PLL锁相环电路

六、锁相环的同步和捕捉

• 同步状态:锁相环的输出频率(或 VCO的频率)ωo能跟踪输入频率 ωi的工作状态,称为同步状态(或 锁定状态),在同步状态下,始终 有ωo = ωi。这时如果用示波器观 察Vi与Vo,即使单路触发,两个波 形都是清晰稳定的。

PLL锁相环电路

第一部分:锁相环基本原理(P1)

• 一、锁相环基本组成

• 一个典型的锁相环(PLL)系统,是由鉴相 器(PD),压控荡器(VCO)和低通滤波 器(LPF)三个基本电路组成

Ud = Kd (θi–θo)

UF = Ud F(s)

Ui PD

L P FV C O U o

PLL锁相环电路

do

PLL锁相环电路

实验二、PLL应用实验

• 一、PLL频率合成器实验 • 二、PLL调频(FM)解调 • 三、锁相式双音多频信号

(DTMF)解码器 • 四、 PLL 数字调谐实验 • 五、设计5 / 6分频器

PLL锁相环电路

实验目的

• 通过上述实验,使大家对由 模拟电路、数字电路组成的 硬件系统的设计、电路的搭 接、故障的分析判断、故障 的排除得到一次锻炼。

• 一、压控灵敏度KO的测量

9V

9V

1K

1M

1 0K

1 0K

16 15 14 13 12 11 10 9 4 04 6

12345678

数字电压表

频率计

1n

PLL锁相环电路

二、鉴相灵敏度Kd的测量。

信号源Ui PD1

40 46B

40 46A

LPF +12V

R1 10 0K

32 4+1 2VRw -5 VPLL锁相环电路

Vi

Vo

• 同步带:在锁相环保持同步的

条件下,输入频率ωi的最大变 化范围,称为同步带宽,用 ωH 表示。超出此范围,环路 则失锁。

PLL锁相环电路

捕捉带

• 失锁时,ωoωi,如果从两个方向 设法改变ωi,使ωi向ωo靠拢,进 而使ωo =(ωi-ωo),当ωo 小到某一数值时,环路则从失锁进 入锁定状态。这个使PLL经过频率 牵引最终导致入锁的频率范围称为 捕捉带ωp。

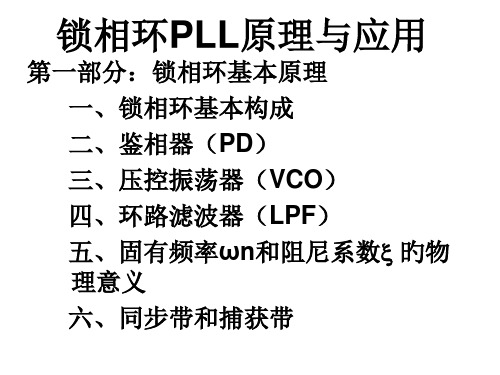

锁相环PLL原理与应用

第一部分:锁相环基本原理 一、锁相环基本组成 二、鉴相器(PD) 三、压控振荡器(VCO) 四、环路滤波器(LPF) 五、固有频率ωn和阻尼系数 的物 理意义 六、同步带和捕捉带

PLL锁相环电路

• 第二部分:锁相环实验

• 实验一、PLL参数测试 • 一、压控灵敏度KO的测量 • 二、鉴相灵敏度Kd的测量 • 三、环路开环增益(KH)的测量 • 四、同步带和捕捉带的测量 • 五、 ωn、ξ的测量

16 15 14 13 12 11 10

9 100u

Ui

4046B

控制信号使压控振荡器的振荡频率发

生变化,最终使鉴相器(PD)的两

输入信号(一个是锁相环的输入信号

Vi, 一个是压控振荡器的输出信号Vo)

的频率完全一样,则环路系统处于稳

定状态。

PLL锁相环电路

五、系统的固有频率ωn和阻尼系数

的物理意义

(P3)

• 一个RLC串联电路,当输入端加一

个阶跃电压时,输出端电压变化有三

U

i

PLL锁相环电路

同步带的测量

• 调信号源(图11)频率约为4046 A的中心频率。示波器分别测Ui和Uo, 并以Ui作为示波器的触发同步信号, 频率计测Ui,这时示波器可显示两个 稳定的波形,即Ui和Uo是锁定的。在 一定范围内缓慢改变信号源频率,可 看到两个波形的频率同时变化,且都 保持稳定清晰,这就是跟踪。