Verilog VHDL 曼彻斯特编码器

Manchester编码器的VHDL设计

Manchester编码器的VHDL设计

谭必思

【期刊名称】《中南民族大学学报(自然科学版)》

【年(卷),期】2002(021)003

【摘要】指出了Manchester波形具有无直流分量、宏观纠错力强、定时信号提取容易等优点,提出了采用Verilog HDL设计实现的Manchester编码器,这种设计是用软件设计技术来设计硬件系统,具有很好的灵活性、实用性和可操作性.

【总页数】3页(P52-54)

【作者】谭必思

【作者单位】中南民族大学外语系电教室

【正文语种】中文

【中图分类】TN911.21

【相关文献】

1.基于VHDL语言的多功能车辆总线编码器设计与分析 [J], 江文丹;董昱;薛红岩;陈小伟

2.基于FPGA的IRIG-B标准DC code编码器VHDL设计 [J], 王丽秋

3.基于VHDL的非系统前馈卷积码编码器设计 [J], 蔡烁;曹伟;王新

4.Manchester编码器的FPGA设计与实现 [J], 陈新坤;周东;余敬东

5.基于VHDL的HDB3编码器的设计与实现 [J], 弓云峰

因版权原因,仅展示原文概要,查看原文内容请购买。

Verilog_VHDL_曼彻斯特编码器

1.5.什么叫“综合”?一般“综合”包含哪些过程?答:在电子设计领域中“综合”的概念可以表示为:将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。

综合包含的过程:对VHDL或Verilog HDL进行处理分析,并将其转换成电路结构或模块,这时不考虑实际器件实现,即完全与硬件无关,这个过程是一个通用电路原理图形成的过程:第2步,对实际实现目标器件的结构进行优化,并使之满足各种约束条件,优化关键路径,等等。

2.10 使用Quartus II的 Mega Wizard Plug-In Manager宏功能模块中的PLL设计一个能实现图题2.10波形的电路元件(包括一个VHDL文件和一个*.bsf原理图图标)。

其中:inclk0为电路的主频输入端,频率为50MHz;areset为异步置位端,c2和主频inclk0同频率。

c1为主频inclk0的倍频输出信号。

C0为c2的反相信号。

Locked为相位控制信号,也是输出使能控制信号。

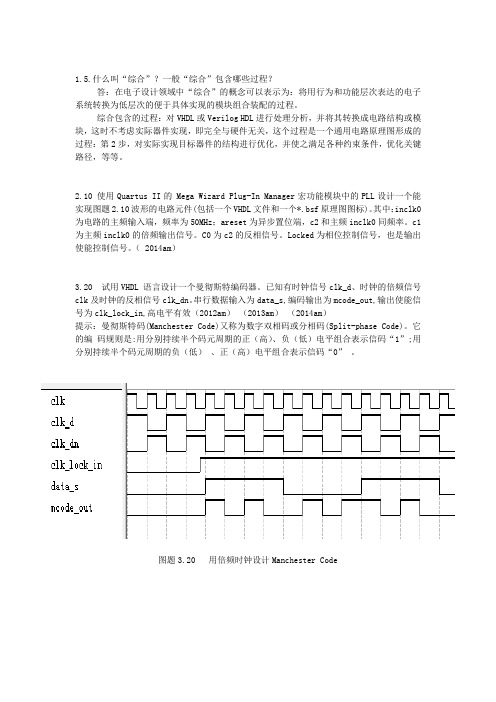

( 2014am)3.20 试用VHDL 语言设计一个曼彻斯特编码器。

已知有时钟信号clk_d、时钟的倍频信号clk及时钟的反相信号clk_dn。

串行数据输入为data_s,编码输出为mcode_out,输出使能信号为clk_lock_in,高电平有效(2012am)(2013am)(2014am)提示:曼彻斯特码(Manchester Code)又称为数字双相码或分相码(Split-phase Code)。

它的编码规则是:用分别持续半个码元周期的正(高)、负(低)电平组合表示信码“1”;用分别持续半个码元周期的负(低)、正(高)电平组合表示信码“0”。

图题3.20 用倍频时钟设计Manchester Code图题3.20 用双时钟设计Manchester Code 的仿真结果hsu_manchester_code_vmodule hsu_manchester_code_v ( clk,clk_d,clk_dn,data_s,clk_lock_in,mcode_out); input clk,clk_d,clk_dn,data_s,clk_lock_in;output mcode_out;reg mcode_out;reg temp_mcode_out;reg temp_mcode_out_ddn;always ( posedge clk or posedge clk_lock_in )beginif (clk_lock_in==1'b1)if (data_s==1'b1)temp_mcode_out<=clk_d;elsetemp_mcode_out<=1'b0;elsetemp_mcode_out=1'b0;endalways ( posedge clk or posedge clk_lock_in )beginif (clk_lock_in==1'b1)if (data_s==1'b0)temp_mcode_out_ddn<=clk_dn;elsetemp_mcode_out_ddn<=1'b0;elsetemp_mcode_out_ddn=1'b0;Endalways ( posedge clk or posedge clk_lock_in )beginif (clk_lock_in==1'b1)mcode_out<=temp_mcode_out;temp_mcode_out_ddn;elsemcode_out<=1'b0;endendmodule3.21 试用VHDL 语言设计一个求两个数中最大值的程序,要求用函数调用的方法设计。

一种基于FPGA的曼彻斯特编译码电路设计

图 2 1B2B 编码电路的顶层设计图

具体设计说明如下 : PS7 模块用于产生 7 阶 m 序列 ,以作为编码的信号源. 为了防止移位寄存器产 生死循环 ,设计采用基于 Load 信号的自启动设计 ,产 生伪随机序列“1111001000110010”.

通过 MaxPlusII 软件仿真 ,得到了编码电路中伪 随机序列 seq 和编码后串行数据 q 的输出 ,仿真结果 如图 3 所示.

参考文献 :

[ 1 ] 李履信. 光纤通信系统 [ M ] . 北京 : 机 械 工 业 出版 社 , 2007.

[ 2 ] 倪康婷. CPLD 在光纤传输系统数字编码中的应用 [J ] . 国外电子测量技术 ,2005 ,12 (24) :31232.

[ 3 ] 段吉海 ,黄志伟. 基于 CPLD/ FP GA 的数字通信系统建 模与设计[ M ] . 北京 :电子工业出版社 ,2004.

图 1 曼彻斯特码编码原理

1. 3 1 B2 B 编码电路的 FPGA 实现 在用 V HDL 语言设计 1B2B 编码电路时 ,采用

自顶向下的设计方法[324] ,其顶层设计图如图 2 所示.

2 曼彻斯特解码器设计

2. 1 1 B2 B 译码电路的工作原理 1B2B 译码部分主要包括 2 部分 :位同步提取部

第 30 卷 第 6 期 2008 年 12 月

三峡大学学报 (自然科学版) J of China Three Gorges U niv. (Nat ural Sciences)

Vol1 30 No . 6 Dec1 2008

一种基于 FPGA 的曼彻斯特编译码电路设计

程 希 罗志会 陈小刚

在光纤传输系统中 ,从电端机输出的数字信号是 适合于电缆传输的双极性码. 而光端机中 ,光源不能 发射负的光脉冲 ,只能采用‘0’和‘1’二电平码. 但简 单的二电平码的直流基线会随着信息流中 0 和 1 的 不同组合而随机起伏 ,劣化光接收机的性能 ,而进行 线路编码能稳定直流基线 ,方便时钟提取和进行在线 的误码检测[1] . 常 用的 编码 方式 有扰 码 、mBnB 码 、 mB1C/ 1 H/ 1 P 码等 ,其中最常用的就是曼彻斯特编 码 (即 1B2B 码) . 以曼彻斯特编码为例 ,介绍了一种 基于全数字锁相环的 mBnB 编解码 ,以及在 Max + Plus 系统上 ,用 V HDL 语言实现曼彻斯特编译码电 路的思想和方法.

设计报告--009---曼彻斯特编译码器的FPGA设计与实现

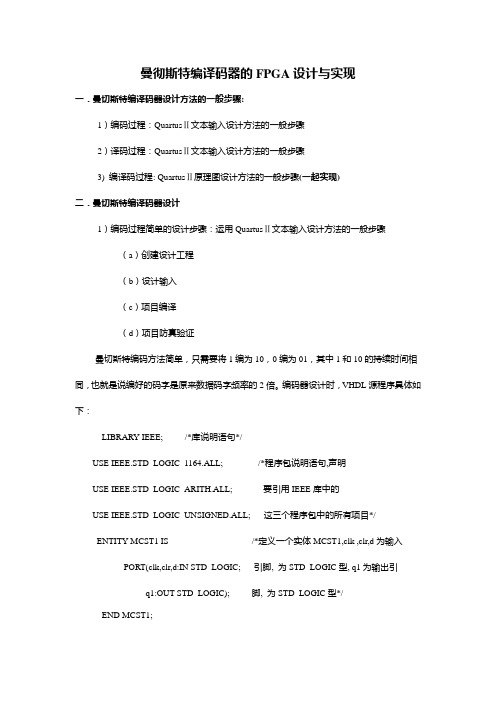

曼彻斯特编译码器的FPGA设计与实现一.曼切斯特编译码器设计方法的一般步骤:1)编码过程:QuartusⅡ文本输入设计方法的一般步骤2)译码过程:QuartusⅡ文本输入设计方法的一般步骤3) 编译码过程: QuartusⅡ原理图设计方法的一般步骤(一起实现)二.曼切斯特编译码器设计1)编码过程简单的设计步骤:运用QuartusⅡ文本输入设计方法的一般步骤(a)创建设计工程(b)设计输入(c)项目编译(d)项目防真验证曼切斯特编码方法简单,只需要将1编为10,0编为01,其中1和10的持续时间相同,也就是说编好的码字是原来数据码字频率的2倍。

编码器设计时,VHDL源程序具体如下:LIBRARY IEEE; /*库说明语句*/USE IEEE.STD_LOGIC_1164.ALL; /*程序包说明语句,声明USE IEEE.STD_LOGIC_ARITH.ALL; 要引用IEEE库中的USE IEEE.STD_LOGIC_UNSIGNED.ALL; 这三个程序包中的所有项目*/ENTITY MCST1 IS /*定义一个实体MCST1,clk ,clr,d为输入PORT(clk,clr,d:IN STD_LOGIC; 引脚, 为STD_LOGIC型, q1为输出引q1:OUT STD_LOGIC); 脚, 为STD_LOGIC型*/END MCST1;ARCHITECTURE divcnt OF MCST1 IS /*根据MCST1定义一个结构体名为divcnt*/ BEGINPROCESS(clk,clr) /*当clk, clr改变时,执行下面的进程*/BEGINIF(clr='1')THEN /*如果clr='1'*/q1<='0'; /* q1清0*/ELSEq1<=NOT(clk XOR d); /* clk与d的同或送q1*/END IF;END PROCESS;END divcnt;原理:当clr为1时,q1为0,则当clr为1时,把clk与d的同或送q1,若d在一个周期内为高电平时,所得的波形为clk波形。

verilog曼切斯特编码

//---------曼切斯特编码------------`timescale 1ns/1psmodule match( fifo_rd, //the enable single of superior fifo readfifo_out, //the out data of superior fifofifo_out_vaild, // the effective single of the out datafifo_empty, // the empty single of superior fifomach_out, //machester datai_clk_2, // double of hdlc clki_rst_n,clk);input i_rst_n;input fifo_out;input fifo_out_vaild;input fifo_empty;input i_clk_2;input clk;output fifo_rd;output mach_out;reg [5:0]out_count;reg [5:0]rd_count;reg fifo_rd;reg mach_out;reg [5:0]out_reg;reg [5:0]so_on;reg one;reg zero;reg temp;parameter rd_fifo_count=4'b1010;parameter mach_out_count=6'b010100;//20parameter rest=10;//-------控制fifo读---------------always @(posedge clk or negedge i_rst_n)beginif(!i_rst_n)fifo_rd<=0;else if(!fifo_empty && rd_count<rd_fifo_count && rd_count>0)fifo_rd<=1;else if(!fifo_empty && rd_count==0 && out_count==0)fifo_rd<=1;else if(rd_count==rd_fifo_count)fifo_rd<=0;elsefifo_rd<=0;end//----------fifo输出数据计?-----------always @(posedge clk or negedge i_rst_n)beginif(!i_rst_n)rd_count<=0;else if(fifo_rd && rd_count<rd_fifo_count)rd_count<=rd_count+1;elserd_count<=0;end//-----------manch数据输出-------------always @(posedge i_clk_2 or negedge i_rst_n )beginif(!i_rst_n)beginout_reg<=6'b111000;endelse if(fifo_out_vaild && out_count==0 )out_reg<=6'b111000;else if(out_count>0 && out_count<mach_out_count+8 ||out_count==mach_out_count+8)out_reg<={out_reg[4:0],temp};end//-------------控制输出mach------------always @(posedge i_clk_2 or negedge i_rst_n )beginif(!i_rst_n)begintemp<=0;zero<=0;one<=0;endelse if(fifo_out_vaild && fifo_out && zero==0)begintemp<=1;zero<=1;one<=0;endelse if(zero && fifo_out_vaild && fifo_out)begintemp<=0;zero<=0;one<=0;endelse if(fifo_out_vaild && !fifo_out && one==0)begintemp<=0;zero<=0;one<=1;endelse if(one && fifo_out_vaild && !fifo_out)begintemp<=1;one<=0;zero<=0;endelsebegintemp<=0;one<=0;zero<=0;endend//---------mach输出计数器--------------always @(posedge i_clk_2 or negedge i_rst_n)beginif(!i_rst_n)out_count<=0;else if(out_count==mach_out_count+8)out_count<=0;else if (fifo_out_vaild==1 && out_count==0)out_count<=out_count+1;else if(out_count>0 && out_count<mach_out_count+8)out_count<=out_count+1;endalways @(posedge i_clk_2 or negedge i_rst_n)beginif(!i_rst_n)mach_out<=1;elsemach_out<=out_reg[5];end endmodule。

一种基于FPGA的曼彻斯特编译码电路设计

中 图分 类 号 : TN9 9 1 2.1

文 献标识 码 : A

文 章编 号 :6 29 8 2 o ) 60 8 —3 1 7 —4 X(o 8 0 —0 50

M a c s e c d ng a c d ng Ci c i s d o n he t r En o i nd De o i r u tBa e n FPGA

的通 信 , 其帧 格式 为 : 位 同步 头 +1 奇 偶校 验 标 志 6 位

位+1 6数 据 +1位奇偶 校 验 , 中同步头 主 要用 于 标 其 识 帧 的开始 , 偶校 验标 志位 用来 通知 接 收方 采用 何 种

P u 系统 上 , VHD ls 用 L语 言 实 现曼 彻 斯 特 编译 码 电

编 码. 目前最 广泛 应用 的局 域 网一 以太 网 , 在数 据 传 输

时 就采 用这 种数 字编码 l . 2 ] 实 验 中的曼 彻斯 特 编 码 主 要 用 于 实 验 仪 器 之 间

码( 1 2 即 B B码 ) 以曼 彻 斯 特 编 码 为 例 , 绍 了一 种 . 介

基 于 全 数 字 锁 相 环 的 mB B 编 解 码 , 及 在 M a + n 以 x

第 3 0卷 第 6期 20 0 8)

J o i a Th e r e i. Na u a ce c s fCh n r e Go g s Un v ( t r lS in e )

V0 . O NO 6 13 .

在 曼彻 斯特 编码 中 , 个二 进制 位 ( 元 ) 中间 每 码 的

都 有 电 压 跳 变 . 电压 的 正 跳 变 表 示 “ ” 电 压 的 负 跳 用 0,

变 表示 “ ” 由于跳 变 都 发 生 在 每 一个 码 元 的 中间 位 1. 置( 半个 周期 ) 接 收端 就可 以方便 地 利用 它作 为 同步 , 时钟 , 因此这 种曼 彻斯 特编 码 又称 为 白同步 曼 彻斯 特

基于FPGA的曼彻斯特码功能实现技术

基于FPGA的曼彻斯特码功能实现技术茅飞;朱昊;朱兴华;朱志勇【摘要】随着曼彻斯特码的应用场合不断扩展,对曼彻斯特编解码的研究与应用也在不断深入和扩展,基于CYCLONE Ⅱ系列FPGA芯片,利用VHDL硬件描述语言和Quartus Ⅱ 9.0开发环境,完成了曼彻斯特编解码模块的设计.在编解码模块的复位单元中使用了异步复位、同步释放的双缓冲电路,降低了异步复位发生亚稳态的概率和减少了同步复位的资源消耗.经过数字仿真波形分析,验证了设计方法的可行性和正确性.【期刊名称】《机电产品开发与创新》【年(卷),期】2011(024)006【总页数】3页(P148-150)【关键词】曼彻斯特码;现场可编程门阵列;编解码模块【作者】茅飞;朱昊;朱兴华;朱志勇【作者单位】南京康尼电子科技有限公司,江苏南京210013;南京工程学院先进数控技术江苏省高校重点建设实验室,江苏南京211167;常州大学机械工程学院,江苏常州213016;南京康尼电子科技有限公司,江苏南京210013【正文语种】中文【中图分类】TN910 引言曼彻斯特 (Manchester)码又称裂相码、双向码,是信道编码的一种码型,已广泛应用在数控测井、安全系统、环境控制系统和车辆总线等领域。

对曼彻斯特码应用的研究也逐渐深入和扩展,如孙枫叶等人研究了曼彻斯特编码在RFID(Radio Frequency Identification,射频识别系统)电子标签中的应用[1],陈志颖研究了曼彻斯特解码在列车控制中心数据传输中的应用[2],张淑玲等人研究了曼彻斯特解码在测井数据传输中的应用[3]等。

目前常用的曼彻斯特编解码器是由美国英特锡尔(Intersil)公司生产的HD6408和HD6409集成芯片,但其最高传输速率只有1MB/s,且需要辅助电路实现串并转换和并串转换功能,无形中影响了工作效率和使用成本。

鉴于此,有学者研究了高速单片机实现曼彻斯特编解码功能的应用[4],然而一直被功能可维护性、可移植性和系统可升级等问题困扰,随着半导体技术的快速发展和生产工艺水平的不断提高,FPGA(Field Programmable Gate Array,现场可编程门阵列)[7]和 CPLD(Complex Programmable Logic Device,复杂可编程逻辑器件)[5,6]实现曼彻斯特编解码功能的应用芯片凭借其在性能和密度方面的提高和具有性能高、密度高、电压低、功耗低、可靠性高等优点脱颖而出,本文介绍了基于FPGA的曼彻斯特编解码功能的实现方法和技术。

基于FPGA的类曼彻斯特编码发送模块设计

基于FPGA的类曼彻斯特编码发送模块设计摘要本文基于类曼彻斯特码,采用VHDL编程,设计和仿真了串行数据传输过程中编码发送模块的功能。

类曼彻斯特码采用数据中嵌入时钟信号的设计思想,是一种利用自同步法保持位同步的线路码型,在高速串行通信过程中采用这种编码方式可以降低系统功耗,同时具有很强的抗干扰能力。

0 引言类曼彻斯特码是一种利用自同步法保持位同步的线路码型,它用上升沿来表示一个码元的开始,然后连续两个时钟信号的高电平表示“1”,对应编码数据“0100”,反之连续两个时钟的低电平表示“0”,对应编码数据”0111”。

经类曼彻斯特编码后,无论是数据“1”还是数据“0”,在开始的时候都有一个上升沿,包含了时钟信息,正是具有这一特点,类曼彻斯特编码发送功能的设计实现解决了串行数据传输的同步时钟问题。

1硬件设计在硬件设计时采用LVDS差分电路,LVDS是一种低摆幅的差分信号技术,它使得信号能够在差分平衡电缆上以几百Mbps的速率传输,其低压幅和低电流的驱动输出完全达到了低噪声和低功耗的要求。

本设计中,FPGA传出的串行数据通过差分电路的转换,形成差分形式的数据,向外传输,设计电路如图1所示。

图1 发送模块该电路临近输出端串接了10Ω的电阻,可以防止差分线对短路,缺点在于420mV的驱动电压已接近数据手册中给出的V od最大值454mV。

同时设计中还需要考虑信号反射问题,这种现象的产生会导致噪声类型的转变,使其从原来的共模信号转变为差模信号,从而降低数据传输的准确性。

为了避免这一问题,我们在设计中应做到在信号值不同时输出阻抗保持不变,同时,输出阻抗的下限只能稍小于传输线特性阻抗,而它的上限必须略大于传输线的特性阻抗。

2 软件设计类曼彻斯特编码可以分为三步进行。

第一步,检测编码周期是否开始并发送开始信号;第二步,对十五位数据进行类曼彻斯特编码;第三步,采用偶校验方式生成校验位,完成编码周期。

具体编程时可以分为数据定义、数据转换及校验和数据编码及发送三大模块。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1.5.什么叫“综合”?一般“综合”包含哪些过程?答:在电子设计领域中“综合”的概念可以表示为:将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。

综合包含的过程:对VHDL或Verilog HDL进行处理分析,并将其转换成电路结构或模块,这时不考虑实际器件实现,即完全与硬件无关,这个过程是一个通用电路原理图形成的过程:第2步,对实际实现目标器件的结构进行优化,并使之满足各种约束条件,优化关键路径,等等。

2.10 使用Quartus II的 Mega Wizard Plug-In Manager宏功能模块中的PLL设计一个能实现图题2.10波形的电路元件(包括一个VHDL文件和一个*.bsf原理图图标)。

其中:inclk0为电路的主频输入端,频率为50MHz;areset为异步置位端,c2和主频inclk0同频率。

c1为主频inclk0的倍频输出信号。

C0为c2的反相信号。

Locked为相位控制信号,也是输出使能控制信号。

( 2014am)3.20 试用VHDL 语言设计一个曼彻斯特编码器。

已知有时钟信号clk_d、时钟的倍频信号clk及时钟的反相信号clk_dn。

串行数据输入为data_s,编码输出为mcode_out,输出使能信号为clk_lock_in,高电平有效(2012am)(2013am)(2014am)提示:曼彻斯特码(Manchester Code)又称为数字双相码或分相码(Split-phase Code)。

它的编码规则是:用分别持续半个码元周期的正(高)、负(低)电平组合表示信码“1”;用分别持续半个码元周期的负(低)、正(高)电平组合表示信码“0”。

图题3.20 用倍频时钟设计Manchester Code图题3.20 用双时钟设计Manchester Code 的仿真结果hsu_manchester_code_vmodule hsu_manchester_code_v ( clk,clk_d,clk_dn,data_s,clk_lock_in,mcode_out); input clk,clk_d,clk_dn,data_s,clk_lock_in;output mcode_out;reg mcode_out;reg temp_mcode_out;reg temp_mcode_out_ddn;always @ ( posedge clk or posedge clk_lock_in )beginif (clk_lock_in==1'b1)if (data_s==1'b1)temp_mcode_out<=clk_d;elsetemp_mcode_out<=1'b0;elsetemp_mcode_out=1'b0;endalways @ ( posedge clk or posedge clk_lock_in )beginif (clk_lock_in==1'b1)if (data_s==1'b0)temp_mcode_out_ddn<=clk_dn;elsetemp_mcode_out_ddn<=1'b0;elsetemp_mcode_out_ddn=1'b0;Endalways @ ( posedge clk or posedge clk_lock_in )beginif (clk_lock_in==1'b1)mcode_out<=temp_mcode_out;temp_mcode_out_ddn;elsemcode_out<=1'b0;endendmodule3.21 试用VHDL 语言设计一个求两个数中最大值的程序,要求用函数调用的方法设计。

其中:data为输入信号,位宽8bit,dataout为最大值输出,位宽8bit。

Clk为时钟信号。

设计一位控制信号set,当set为低电平时,输出data和peak中的最大值。

(2013am) 2014am) 。

实体部分LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE WORK.ning_bpac.ALL;ENTITY ning_peakdetect ISPORT(data:IN STD_LOGIC_VECTOR(7 DOWNTO 0);clk,set: IN STD_LOGIC;dataout: OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END ning_peakdetect ;ARCHITECTURE peakdetect_behave OF ning_peakdetect ISSIGNAL peak: STD_LOGIC_VECTOR(7 DOWNTO 0);BEGINdataout<=peak;PROCESS(clk)BEGINIF(clk'EVENT AND clk='1') THENIF (set='1' ) THENpeak<=data;ELSEpeak<=max(data , peak);END IF;END IF;END PROCESS;END;函数部分LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;PACKAGE ning_bpac ISFUNCTION max(a: STD_LOGIC_VECTOR;b: STD_LOGIC_VECTOR)RETURN STD_LOGIC_VECTOR;END ning_bpac;PACKAGE BODY ning_bpac ISFUNCTION max(a: STD_LOGIC_VECTOR;b: STD_LOGIC_VECTOR)RETURN STD_LOGIC_VECTOR ISVARIABLE temp: STD_LOGIC_VECTOR(a'RANGE); BEGINIF (a>b) THENtemp:=a;ELSEtemp:=b;END IF;RETURN temp;END max;END ning_bpac;3.22 试用VHDL 语言设计一个8位二进制加计数器。

其中:qout 为8位二进制输出,cout 为进位输出,clr 为同步清零端,当clr为高电平时清零、低电平时工作。

Cipher为8位密码控制输入端,其控制功能如下表所示:(2014am)cipher 功能00001111 加计数11110000 减计数11001100 停止计数11111111 停止计数并且输出BCD码要求:1.设计一个计数分频器,输入频率 clk 为50Mhz ,输出频率 newclk 为1hz。

newclk 为计数器的计数频率。

2.编写一个把二进制转换为整数的函数。

3.当停止计数时,调用上述函数用整数除法把二进制数转换为BCD 码。

(2014am)LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY Updowncnt8 ISPORT (clk,clr:IN STD_LOGIC;cipher:IN STD_LOGIC_VECTOR(7 DOWNTO 0);cout:OUT STD_LOGIC;q:BUFFER INTEGER RANGE 0 TO 15);END Updowncnt8;ARCHITECTURE one OF Updowncnt8 ISBEGINPROCESS(clk,clr)BEGINIF clk'EVENT AND clk='1' THEN IF clr ='0' THENCASE cipher ISWHEN "00001111"=>IF q=15 THEN q<=0;cout<='0';ELSIF q=14 THEN q<=q+1;cout<='1';ELSE q<=q+1;END IF;WHEN "11110000"=>IF q=0 THEN q<=15;cout<='0';ELSIF q=1 THEN q<=q-1;cout<='1';ELSE q<=q-1;END IF;WHEN "11001100"=>NULL;WHEN "11111111"=>NULL;WHEN OTHERS =>NULL;END CASE;ELSIF clr ='1' THENq<=0;END IF;END IF;END PROCESS;END one;4.14 8线-3线优先编码器CD4532功能表如表4.1a所示,试用Verilog HDL语言实现该8线-3线优先编码器。

(2011am)(2011gam)(2012am) (2013am)(2014am)module coder_8(y,a);input[7:0] a;output[2:0]y;reg[2:0] y;always @(a)beginif(~a[7]) y='b111;else if(~a[6]) y='b110;else if(~a[5]) y='b101;else if(~a[4]) y='b100;else if(~a[3]) y='b011;else if(~a[2]) y='b010;else if(~a[1]) y='b001;else y='b000;endendmodule表4.1a 8线-3线优先编码器CD4532功能表(P109.例题4.6)4.15 把下列VHDL程序改写成Verilog HDL语言,并且用Quartus Ⅱ通过编译。

(2014am) LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY hsu_count6_updown ISPORT(CLK,RST,ENA:IN STD_LOGIC;OUTY:OUT STD_LOGIC_VECTOR(3DOWNTO 0);COUT:OUT STD_LOGIC;cipher: IN STD_LOGIC_VECTOR(7 DOWNTO 0));END hsu_count6_updown;ARCHITECTURE behave_cnt6 OF hsu_count6_updown ISSIGNAL CQI: STD_LOGIC_VECTOR(3 DOWNTO 0):="0000";SIGNAL flag1_2: STD_LOGIC_VECTOR(1 DOWNTO 0);SIGNAL cipher_temp: STD_LOGIC_VECTOR(7 DOWNTO 0);BEGINcipher_temp<=cipher;P_COUNT10_VT: PROCESS(CLK,RST,ENA)BEGINIF RST='1' THEN CQI<="0000";ELSIF CLK 'EVENT AND CLK='1' THENIF ENA='1' THENif (flag1_2="00") thenIF CQI<5 THENCQI<=CQI+ 1;ELSECQI<="0000";END IF;elsif (flag1_2="01") thenIF CQI>0 THENCQI<=CQI- 1;ELSECQI<="0101";END IF;end if;END IF;END IF;OUTY<=CQI;IF (flag1_2="00") THENCOUT<= NOT( CQI(2) AND CQI(0));ELSIF (flag1_2="01") THENCOUT<= CQI(3) OR CQI(2) OR CQI(1) OR CQI(0); END IF;END PROCESS P_COUNT10_VT;p1: Process(clk,cipher_temp)BEGINIF (clk 'EVENT AND clk='1') THENIF (cipher_temp="00001111") THENflag1_2<="00";ELSIF (cipher_temp="11110000") THENflag1_2<="01";ELSIF (cipher_temp="11001100") THENflag1_2<="10";END IF;END IF;END PROCESS p1;P2_stop: Process(clk,flag1_2,CQI)BEGINIF (clk 'EVENT AND clk='1') THENIF ( flag1_2="10") THENCQI<=CQI;END IF;END IF;END PROCESS p2_stop;END behave_cnt6;。