第4章 Verilog HDL设计初步习题 PPT

合集下载

EDA技术与Verilog_HDL(潘松)第四章课后习题答案

图4-27

1位全减器

习

题

x为被减数, y为减数, sub_in为 低位的借 位, diff r为差,su b_out为向 高位的借 位。

x 0 0 0 y 0 0 1 sub_in diffr sub_out 0 1 0 0 1 1 0 1 1

//一个二进制半减器设计进行了阐述

module h_suber(x,y,diff,s_out); input x,y; output diff, s_out; assign diff=x^y; assign s_out=(~x)&y; endmodule

reg [2:0]A ;

wire[7:0]Y ; reg G1 ,G2 ,G3;

decoder3_8 DUT ( G1 ,Y ,G2 ,A ,G3 );

initialቤተ መጻሕፍቲ ባይዱbegin $monitor($time,"A=%d,G1=%b,G2=%b, G3=%b,Y= %d\n",A, G1, G2, G3, Y); end

习

题

4-3 阻塞赋值和非阻塞赋值有何区别? 答:Verilog中,用普通等号“=”作为阻塞式赋值语句的赋值符号,如y=b。 Verilog中,用普通等号“<=”作为非阻塞式赋值语句的赋值符号,如y<=b。 阻塞式赋值的特点是,一旦执行完当前的赋值语句,赋值目标变量y即刻 获得来自等号右侧表达式的计算值。如果在一个块语句中含有多条阻塞式赋值 语句,则当执行到其中某条赋值语句时,其他语句将禁止执行,即如同被阻塞 了一样。 非阻塞式赋值的特点是必须在块语句执行结束时才整体完成赋值操作。非 阻塞的含义可以理解为在执行当前语句时,对于块中的其他语句的执行情况一 律不加限制,不加阻塞。这也可以理解为,在begin_end块中的所有赋值语句都 可以并行运行。

EDA技术与Verilog-HDL(潘松)第四章课后习题答案精品PPT课件

begin s <= G2 | G3 ; if (G1 == 0) Y <= 8'b1111_1111; else if (s) Y <= 8'b1111_1111; else case ( A ) 3'b000: Y = 8'b11111110; 3'b001: Y = 8'b11111101; 3'b010: Y = 8'b11111011; 3'b011: Y = 8'b11110111; 3'b100: Y = 8'b11101111; 3'b101: Y = 8'b11011111; 3'b110: Y = 8'b10111111; 3'b111: Y = 8'b01111111; default:Y = 8'bxxxxxxxx; endcase end

else if (A==3'b101)Y=8'b11011111;

else if (A==3'b110)Y=8'b10111111;

else if (A==3'b111)Y=8'b01111111;

else

Y=8'bxxxxxxxx;end

end

endmodule

//测试文件,??部分请根据被测试的文件修改 module stimulus;

//一个二进制全减器顶层设计进行了阐述

output diffr,sub_out;

input x,y,sub_in;

wire e,d,f;

h_suber u1(x,y,e,d);

//

h_suber u2(.x(e),.diff(diffr),.y(sub_in),.s_out(f));//

else if (A==3'b101)Y=8'b11011111;

else if (A==3'b110)Y=8'b10111111;

else if (A==3'b111)Y=8'b01111111;

else

Y=8'bxxxxxxxx;end

end

endmodule

//测试文件,??部分请根据被测试的文件修改 module stimulus;

//一个二进制全减器顶层设计进行了阐述

output diffr,sub_out;

input x,y,sub_in;

wire e,d,f;

h_suber u1(x,y,e,d);

//

h_suber u2(.x(e),.diff(diffr),.y(sub_in),.s_out(f));//

第四章VerilogHDL设计初步.

4.2.5 含异步清0的锁存器及其Verilog描述

4.2.6 Verilog的时钟过程描述注意点

4.2.6 Verilog的时钟过程描述注意点

4.2.7 异步时序电路

4.2.7 异步时序电路

4.3.1 4位二进制加法计数器及其Verilog描述

4.3.1 4位二进制加法计数器及其Verilog描述

4-8 给出一个4选1多路选择器的Verilog描述。此器件与图4-1类似,但选通控制 端有4个输入:S0、S1、S2、S3。当且仅当S0=0时:Y=A;S1=0时:Y=B; S2=0时:Y=C;S3=0时:Y=D。

习

题

4-9 把例4-21改成一异步清0,同步时钟使能和异步数据加载型8位二进 制加法计数器。图4-27 含2选1多路选择器的模块

1. 半加器描述

4.1.5 简单加法器及其Verilog HDL描述

1. 半加器描述

4.1.5 简单加法器及其Verilog HDL描述

1. 半加器描述

4.1.5 简单加法器及其Verilog HDL描述

1. 半加器描述

2. 全加器顶层文件设计

2. 全加器顶层文件设计

Verilog中元件例化语句的结构比较简单,一般格式如下:

2.过程赋值语句 (1)阻塞式赋值。 (2)非阻塞式赋值。 3.数据表示方式 “=”

4.1.4 4选1多路选择器及其Verilog HDL描述4

4.1.5 简单加法器及其Verilog HDL描述

1. 半加器描述

4.1.5 简单加法器及其Verilog HDL描述

1. 半加器描述

4.1.5 简单加法器及其Verilog HDL描述

4.2.3 含异步清0和时钟使能结构的D触发器及其Verilog描述

精品课件-Verilog HDL数字设计教程-第4章 Verilog HDL常用电路设计

begin if(enable==2'b10) out=input1; else out='bz;

end

4.2 常用时序逻辑电路设计

1 D触发器和锁存器 2 寄存器 3 移位寄存器 4计数器 5分频器 6程序存储器 ROM 7数据存储器 RAM

4.2 常用时序逻辑电路设计

D触发器和锁存器

【例4-12】 一位D触发器

input0:'bz; endmodule

input3[7..0] input2[7..0] input1[7..0] input0[7..0]

2' h1 --

A[1..0] B[1..0]

OUT

EQUAL

Equal2

2' h2 --

A[1..0] B[1..0]

OUT

EQUAL

Equal3

2' h3 --

Equal0

2' h0 --

A[1..0] B[1..0]

OUT

out~[15..8]

out=(enable==2'b01)?

EQUAL

Equal1

IO_BUF (TRI)

out~[23..16]

out[7..0]

input2:'bz, out=(enable==2'b10)?

input1:'bz, out=(enable==2'b11)?

if(enable==1) dataout=datain; else dataout='bz;

【例4-8】N位4通道的三态总线三驱态动总器线 module tri_bus(input3,input2,input1,input0,enable,out);

end

4.2 常用时序逻辑电路设计

1 D触发器和锁存器 2 寄存器 3 移位寄存器 4计数器 5分频器 6程序存储器 ROM 7数据存储器 RAM

4.2 常用时序逻辑电路设计

D触发器和锁存器

【例4-12】 一位D触发器

input0:'bz; endmodule

input3[7..0] input2[7..0] input1[7..0] input0[7..0]

2' h1 --

A[1..0] B[1..0]

OUT

EQUAL

Equal2

2' h2 --

A[1..0] B[1..0]

OUT

EQUAL

Equal3

2' h3 --

Equal0

2' h0 --

A[1..0] B[1..0]

OUT

out~[15..8]

out=(enable==2'b01)?

EQUAL

Equal1

IO_BUF (TRI)

out~[23..16]

out[7..0]

input2:'bz, out=(enable==2'b10)?

input1:'bz, out=(enable==2'b11)?

if(enable==1) dataout=datain; else dataout='bz;

【例4-8】N位4通道的三态总线三驱态动总器线 module tri_bus(input3,input2,input1,input0,enable,out);

第4章 Verilog HDL设计初步

等效于 assign drain[3]=source[1] assign drain[2]=source[0]

15

第4章 Ver型变量---默认值为X

寄存器(register)类型变量对应于具有状态保持作用的电路元件,如 触发器、锁存器等;即它能保持其值,直到它被赋于新的值。 在设计中,此类变量必须放在块语句(always语句)中,通过过程语 句赋值。 同一个register变量只能在一个块语句中重复赋值,而不能同时在多个块 语句中赋值使用。 register变量类型包括:

reg integer real time 无符号整数变量,可以选择不同的位宽。 有符号整数变量,32位宽,算术运算可产生2的补码。 有符号的浮点数,双精度。 无符号整数变量,64位宽(Verilog-XL仿真工具用64 位的正数来记录仿真时刻)

注意:寄存器(register)类型变量不一定会在Verilog中映射出时序电路。 16 如例4.1就是一个组合逻辑电路。

第4章 Verilog HDL设计初步

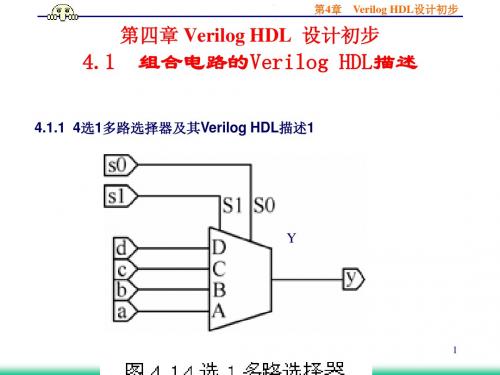

第四章 Verilog HDL 设计初步

4.1

组合电路的Verilog HDL描述

4.1.1 4选1多路选择器及其Verilog HDL描述1

Y

1

第4章 Verilog HDL设计初步

例4-1: 4选1数据选择器的Verilog HDL语言描述。 module mux41a(A,B,C,D,S1,S0,Y); input A,B,C,D; input S1,S0; output Y; reg Y; always@(A,B,C,D,S1,S0) begin:MUX41 case ({S1,S0}) 2’B00:Y<=A; 2’B01:Y<=B; 2’B10:Y<=C; 2’B11:Y<=D; Default:Y=A; endcase end endmodule

15

第4章 Ver型变量---默认值为X

寄存器(register)类型变量对应于具有状态保持作用的电路元件,如 触发器、锁存器等;即它能保持其值,直到它被赋于新的值。 在设计中,此类变量必须放在块语句(always语句)中,通过过程语 句赋值。 同一个register变量只能在一个块语句中重复赋值,而不能同时在多个块 语句中赋值使用。 register变量类型包括:

reg integer real time 无符号整数变量,可以选择不同的位宽。 有符号整数变量,32位宽,算术运算可产生2的补码。 有符号的浮点数,双精度。 无符号整数变量,64位宽(Verilog-XL仿真工具用64 位的正数来记录仿真时刻)

注意:寄存器(register)类型变量不一定会在Verilog中映射出时序电路。 16 如例4.1就是一个组合逻辑电路。

第4章 Verilog HDL设计初步

第四章 Verilog HDL 设计初步

4.1

组合电路的Verilog HDL描述

4.1.1 4选1多路选择器及其Verilog HDL描述1

Y

1

第4章 Verilog HDL设计初步

例4-1: 4选1数据选择器的Verilog HDL语言描述。 module mux41a(A,B,C,D,S1,S0,Y); input A,B,C,D; input S1,S0; output Y; reg Y; always@(A,B,C,D,S1,S0) begin:MUX41 case ({S1,S0}) 2’B00:Y<=A; 2’B01:Y<=B; 2’B10:Y<=C; 2’B11:Y<=D; Default:Y=A; endcase end endmodule

第4章VerilogHDL基本语法课件

•从字面上理解,always的意思是“总是,永远”。在 Verilog HDL中,只要指定的事件发生,由always指定的内 容将不断地重复运行,不论该事件已经发生了多少次。这 恰恰反映了实际电路的特征,即在通电的情况下电路将不 断运行。

•最常用的两种事件是电平触发和边沿触发。电平触发是指 当某个信号的电平发生变化时,执行always指定的内容; 边沿触发是指当某个信号的上升沿或下降沿到来时,执行 always指定的内容。 •电平触发的写法是在“@”后面直接写触发信号的名称; 边沿触发的写法是在“@”后面写“posedge 信号名”或者 “negedge 信号名”,posedge代表信号的上升沿, negedge则代表信号的下降沿。

数字电路系统的设计者通过这种语言

a可以从上层到下层,从抽象到具体,逐层次地描述自 己的设计思想, b用一系列分层次的模块来表示极其复杂的数字系统, C然后利用模块组合经由自动综合工具转换到门级电路 网表, d再用自动布局布线工具把网表转换为具体电路进行布 局布线后, e下载到专用集成电路(ASIC)或现场可编程逻辑器件。

准的制定使得Verilog语言在综合、仿真、验证及IP重用等方面有很 大幅度的提高。

• Verilog HDL 是System Verilog语言的基础。SystemVerilog结合了来自 Verilog、VHDL、C++的概念,它将硬件描述语言(HDL)与现代的高 层级验证语言结合了起来。System Verilog加入了一些C++的元素。

通常用来描述组合逻辑 。

assign声明语句很简单,只需要写一个“assign” (赋 值),后面再加一个方程式即可。

• 例如 :assign s=a & b & c; • 该语句描述了一个三输入的与门,这是一个组合逻

•最常用的两种事件是电平触发和边沿触发。电平触发是指 当某个信号的电平发生变化时,执行always指定的内容; 边沿触发是指当某个信号的上升沿或下降沿到来时,执行 always指定的内容。 •电平触发的写法是在“@”后面直接写触发信号的名称; 边沿触发的写法是在“@”后面写“posedge 信号名”或者 “negedge 信号名”,posedge代表信号的上升沿, negedge则代表信号的下降沿。

数字电路系统的设计者通过这种语言

a可以从上层到下层,从抽象到具体,逐层次地描述自 己的设计思想, b用一系列分层次的模块来表示极其复杂的数字系统, C然后利用模块组合经由自动综合工具转换到门级电路 网表, d再用自动布局布线工具把网表转换为具体电路进行布 局布线后, e下载到专用集成电路(ASIC)或现场可编程逻辑器件。

准的制定使得Verilog语言在综合、仿真、验证及IP重用等方面有很 大幅度的提高。

• Verilog HDL 是System Verilog语言的基础。SystemVerilog结合了来自 Verilog、VHDL、C++的概念,它将硬件描述语言(HDL)与现代的高 层级验证语言结合了起来。System Verilog加入了一些C++的元素。

通常用来描述组合逻辑 。

assign声明语句很简单,只需要写一个“assign” (赋 值),后面再加一个方程式即可。

• 例如 :assign s=a & b & c; • 该语句描述了一个三输入的与门,这是一个组合逻

Verilog_HDL设计初步PPT课件

19

4.1 组合电路的Verilog HDL描述

2. 全加器顶层文件设计

20

4.1 组合电路的Verilog HDL描述

2. 全加器顶层文件设计

Verilog中元件例化语句的结构比较简单,一般格式如下: <模块元件名>: <例化元件名> ( .例化元件端口(例化元件外接端口名),...);

21

4.1 组合电路的Verilog HDL描述

A=1’b0; B=1’b1; C[3:0]=4’b1100; D[3:0]=4’b1011; E[5:0]=6’b010110;

7

4.1 组合电路的Verilog HDL描述

4.1.2 4选1多路选择器及其Verilog HDL描述2 2.等式操作符

A=4’b1011; B=4’b0010; C=4’b0z10; D=4’b0z10;

3. 8位加法器描述

22

4.1 组合电路的Verilog HDL描述

3. 8位加法器描述

23

4.2 时序电路的Verilog HDL描述

4.2.1 边沿触发型D触发器及其Verilog描述

24

4.2 时序电路的Verilog HDL描述

4.2.1 边沿触发型D触发器及其Verilog描述

25

4.2 时序电路的Verilog HDL描述

wire tmp1,tmp2; assign Y = tmp1 ^ tmp2;

5.注释符号

10

4.1 组合电路的Verilog HDL描述

4.1.3 4选1多路选择器及其Verilog HDL描述3

11

4.1 组合电路的Verilog HDL描述

4.1.3 4选1多路选择器及其Verilog HDL描述3

4.1 组合电路的Verilog HDL描述

2. 全加器顶层文件设计

20

4.1 组合电路的Verilog HDL描述

2. 全加器顶层文件设计

Verilog中元件例化语句的结构比较简单,一般格式如下: <模块元件名>: <例化元件名> ( .例化元件端口(例化元件外接端口名),...);

21

4.1 组合电路的Verilog HDL描述

A=1’b0; B=1’b1; C[3:0]=4’b1100; D[3:0]=4’b1011; E[5:0]=6’b010110;

7

4.1 组合电路的Verilog HDL描述

4.1.2 4选1多路选择器及其Verilog HDL描述2 2.等式操作符

A=4’b1011; B=4’b0010; C=4’b0z10; D=4’b0z10;

3. 8位加法器描述

22

4.1 组合电路的Verilog HDL描述

3. 8位加法器描述

23

4.2 时序电路的Verilog HDL描述

4.2.1 边沿触发型D触发器及其Verilog描述

24

4.2 时序电路的Verilog HDL描述

4.2.1 边沿触发型D触发器及其Verilog描述

25

4.2 时序电路的Verilog HDL描述

wire tmp1,tmp2; assign Y = tmp1 ^ tmp2;

5.注释符号

10

4.1 组合电路的Verilog HDL描述

4.1.3 4选1多路选择器及其Verilog HDL描述3

11

4.1 组合电路的Verilog HDL描述

4.1.3 4选1多路选择器及其Verilog HDL描述3

第4章 Verilog设计初步 数字系统设计与Verilog HDL (第4版)教学课件

qout[0]<=~qout[WIDTH-1];

end

end

endmodule

Synplify Pro新建项目对话框

Synplify Pro新建文件对话框

Implementation Option对话框

约翰逊计数器综合后的RTL级原理图

约翰逊计数器综合后的门级原理图 (MAX7000器件)

begin

if(~reset) begin q<=1'b0;qn<=1'b1; end //异步清0,低电平有效

else if(~set) begin q<=1'b1;qn<=1'b0; end

//异步置1,低电平有效

else

begin q<=d;qn<=~d; end

end

endmodule

4.4 Verilog基本时序电路设计

begin if(~reset) begin q<=1'b0;qn<=1'b1;end

//同步清0,低电平有效 else if(~set) begin q<=1'b1;qn<=1'b0;end //同步置1,低电平有效 else begin q<=d; qn<=~d; end

end endmodule

【例4.11】 带异步清0/异步置1(低电平有效)的D触发器

module dff_asyn(q,qn,d,clk,set,reset);

input d,clk,set,reset; output reg q,qn;

always @(posedge clk or negedge set or negedge reset)

EDA技术与Verilog_HDL(潘松)第四章课后习题答案

x 0 0 y 0 1 diff 0 1 s_out 0 1

0

1 1

1

0 0

1

0 1

0

1 0

1

0 0

1

1

1

1

0

1

0

1

0

1

1

1

0110 Nhomakorabea0

0

module f_suber(x,y,sub_in,diffr,sub_out); //一个二进制全减器顶层设计进行了阐述 output diffr,sub_out; input x,y,sub_in; wire e,d,f; h_suber u1(x,y,e,d); // h_suber u2(.x(e),.diff(diffr),.y(sub_in),.s_out(f));// or2a u3(.a(d),.b(f),.c(sub_out)); endmodule

reg [2:0]A ;

wire[7:0]Y ; reg G1 ,G2 ,G3;

decoder3_8 DUT ( G1 ,Y ,G2 ,A ,G3 );

initial begin $monitor($time,"A=%d,G1=%b,G2=%b, G3=%b,Y= %d\n",A, G1, G2, G3, Y); end

习

module MUXK (a1, a2, a3, s0, s1, outy); input a1, a2, a3, s0, s1; output outy; wire outy; wire tmp;

题

4-6 图4-26所示的是双2选1多路选择器构成的电路MUXK。对于其中MUX21A,当s=0 和s=1时,分别有y=a和y=b。试在一个模块结构中用两个过程来表达此电路。 答:参考实验1

0

1 1

1

0 0

1

0 1

0

1 0

1

0 0

1

1

1

1

0

1

0

1

0

1

1

1

0110 Nhomakorabea0

0

module f_suber(x,y,sub_in,diffr,sub_out); //一个二进制全减器顶层设计进行了阐述 output diffr,sub_out; input x,y,sub_in; wire e,d,f; h_suber u1(x,y,e,d); // h_suber u2(.x(e),.diff(diffr),.y(sub_in),.s_out(f));// or2a u3(.a(d),.b(f),.c(sub_out)); endmodule

reg [2:0]A ;

wire[7:0]Y ; reg G1 ,G2 ,G3;

decoder3_8 DUT ( G1 ,Y ,G2 ,A ,G3 );

initial begin $monitor($time,"A=%d,G1=%b,G2=%b, G3=%b,Y= %d\n",A, G1, G2, G3, Y); end

习

module MUXK (a1, a2, a3, s0, s1, outy); input a1, a2, a3, s0, s1; output outy; wire outy; wire tmp;

题

4-6 图4-26所示的是双2选1多路选择器构成的电路MUXK。对于其中MUX21A,当s=0 和s=1时,分别有y=a和y=b。试在一个模块结构中用两个过程来表达此电路。 答:参考实验1

《EDA技术与Verilog HDL》PPT第3版 第4章 FPGA硬件实现

实验4-4 应用宏模块设计数字频率计

图4-59 测频时序控制电路

实验与设计

实验4-4 应用宏模块设计数字频率计

图4-60 测频时序控制电路工作波形

实验与设计

实验4-4 应用宏模块设计数字频率计

图4-61 频率计顶层电路原理图

实验与设计

实验4-4 应用宏模块设计数字频率计

图4-62 频率计工作时序波形

4.8 安装Quartus II 13.1说明

图4-45 安装QuartusII 13.1设计文件界面,点击右侧安装按钮

4.8 安装Quartus II 13.1说明

图4-46 设定QuartusII 13.1设计文件安装路径

4.8 安装Quartus II 13.1说明

图4-47 选择安装软件。注意不要漏了ModelSim-Altera Starter Edition

图4-3 利用New Project Wizard创建工程CNT10 ⑵ 将设计文件加入工程中。

4.1 代码编辑输入和系统编译

4.1.2 创建工程 ⑶ 选择目标芯片。

图4-4 选择目标器件EP4CE55F23C8

4.1 代码编辑输入和系统编译

4.1.2 创建工程 ⑷ 工具设置。

图4-5 设计与验证工具软件选择

(3)原理图文件存盘。

图4-30 完成设计并将半加器封装成一个元件,以便在更高层设计中调用

4.4 电路原理图设计流程

4.4.1 设计一个半加器

(4)创建原理图文件为顶层设计的工程。

(5)绘制半加器原理图。

(6)仿真测试半加器。

4.4 电路原理图设计流程

4.4.2 完成全加器顶层设计

图4-31 在f_adder工程下加入半加器原件

图4-59 测频时序控制电路

实验与设计

实验4-4 应用宏模块设计数字频率计

图4-60 测频时序控制电路工作波形

实验与设计

实验4-4 应用宏模块设计数字频率计

图4-61 频率计顶层电路原理图

实验与设计

实验4-4 应用宏模块设计数字频率计

图4-62 频率计工作时序波形

4.8 安装Quartus II 13.1说明

图4-45 安装QuartusII 13.1设计文件界面,点击右侧安装按钮

4.8 安装Quartus II 13.1说明

图4-46 设定QuartusII 13.1设计文件安装路径

4.8 安装Quartus II 13.1说明

图4-47 选择安装软件。注意不要漏了ModelSim-Altera Starter Edition

图4-3 利用New Project Wizard创建工程CNT10 ⑵ 将设计文件加入工程中。

4.1 代码编辑输入和系统编译

4.1.2 创建工程 ⑶ 选择目标芯片。

图4-4 选择目标器件EP4CE55F23C8

4.1 代码编辑输入和系统编译

4.1.2 创建工程 ⑷ 工具设置。

图4-5 设计与验证工具软件选择

(3)原理图文件存盘。

图4-30 完成设计并将半加器封装成一个元件,以便在更高层设计中调用

4.4 电路原理图设计流程

4.4.1 设计一个半加器

(4)创建原理图文件为顶层设计的工程。

(5)绘制半加器原理图。

(6)仿真测试半加器。

4.4 电路原理图设计流程

4.4.2 完成全加器顶层设计

图4-31 在f_adder工程下加入半加器原件

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

wire [2:0] A ;

output [7:0] Y ;

reg [7:0] Y ;

reg s;

always @ ( A ,G1, G2, G3)

begin

s <= G2 | G3 ;

if (G1 == 0)

Y <= 8'b1111_1111;

else if (s)

Y <= 8'b1111_1111;

第4章 Verilog HDL设计初步

习题

4-1 举例说明,Verilog HDL的操作符中,哪些操作符的运算结果总是一位的。 答: if_else条件语句

4-2 wire型变量与reg型变量有什么本质区别,它们可用于什么类型语句中? 答:书上P261~262《9.2 Verilog HDL数据类型》 reg主要是用于定义特定类型的变量,即寄存器型(Register)变量(或称寄存器型数据类的 变量)。如果没有在模块中显式地定义信号为网线型变量,Verilog综合器都会将其默认定 义为wire型。过程语句always@引导的顺序语句中规定必须是reg型变量。 wire型变量不允许有多个驱动源

释为,对于不满足条件,跳过赋值语句Q<=D不予执行,即意味着保持Q的原值

不变(保持前一次满足if条件时Q被更新的值)。对于数字电路来说,当输入改变后

试图保持一个值不变,就意味着使用具有存储功能的元件,就是必须引进时序元

件来保存Q中的原值,直到满足if语句的判断条件后才能更新Q中的值,于是便产

生了时序元件。

begin s <= G2 | G3 ; if (G1 == 0) Y <= 8'b1111_1111; else if (s) Y <= 8'b1111_1111; else case ( A ) 3'b000: Y = 8'b11111110; 3'b001: Y = 8'b11111101; 3'b010: Y = 8'b11111011; 3'b011: Y = 8'b11110111; 3'b100: Y = 8'b11101111; 3'b101: Y = 8'b11011111; 3'b110: Y = 8'b10111111; 3'b111: Y = 8'b01111111; default:Y = 8'bxxxxxxxx; endcase end

习题

4-3 阻塞赋值和非阻塞赋值有何区别? 答:Verilog中,用普通等号“=”作为阻塞式赋值语句的赋值符号,如y=b。

Verilog中,用普通等号“<=”作为非阻塞式赋值语句的赋值符号,如y<=b。 阻塞式赋值的特点是,一旦执行完当前的赋值语句,赋值目标变量y即刻

获得来自等号右侧表达式的计算值。如果在一个块语句中含有多条阻塞式赋值 语句,则当执行到其中某条赋值语句时,其他语句将禁止执行,即如同被阻塞 了一样。

非阻塞式赋值的特点是必须在块语句执行结束时才整体完成赋值操作。非 阻塞的含义可以理解为在执行当前语句时,对于块中的其他语句的执行情况一 律不加限制,不加阻塞。这也可以理解为,在begin_end块中的所有赋值语句都 可以并行运行。

4-4 举例说明,为什么使用条件叙述不完整的条件句能导致产生时序模块的综合结果?

时也能启动过程,但由于CLK=0,无法执行if语句,从而也就无法执行赋值语句

Q<=D,导致Q只能保持原值(这也意味着需要在设计模块中引入存储元件)。

在以上两种情况中,由于if语句不满足条件,于是将跳过赋值表达式Q<=D,

不执行此赋值表达式而结束if语句和过程.对于这种语言现象,Velilog综合器解

endmodule

4-5 用Verilog设计一个3-8译码器,要求分别用case语句和if_else语句。比较这两 种方式。

module decoder3_8 ( G1 ,Y ,G2 ,A ,G3 );

input G1, G2, G3;

wire G1, G2, G3;

input [2:0] A ;

答:● 当CLK发生了电平变化,但是从1变到0。这时无论D是否变化,都将启动

过程去执行if语句;但此时CLK=0,无法执行if语句,从而无法执行赋值语句

Q<=D,于是Q只能保持原值不变(这就意味着需要在设计模块中引入存储元件)。

● 当CLK没有发生任何变化,且CLK一直为0,而敏感信号D发生了变化。这

//测试文件,??部分请根据被测试的文件修改 module stimulus;

else begin if (A==3'b000)Y=8'b11111110;

else if (A==3'b001)Y=8'b11111101;

else if (A==3'b010)Y=8'b11111011;

else if (A==3'b011)Y=8'b11110111;

else if (A==3'b100)Y=8'b11101111;

else if (A==3'b101)Y=8'b11011111;

else if (A==3'b110)Y=8'b10111111;

else if (A==3'b111)Y=8'b01111111;

else

Y=8'bxxxxxxxx;end

end

endmodule

大家应该也有点累了,稍作休息

大家有疑问的,可以询问和交流

module LATCH1 (CLK, D, Q);

output Q;

input CLK, D;

reg Q;

always @(D or CLK)

if(CLK)Q<=D;

//当CLK=1时D被锁入Q

endmodule

4-5 用Verilog设计一个3-8译码器,要求分别用case语句和if_else语句。比 较这两种方式。

4-5 用Verilog设计一个3-8译码器,要求分别用case语句和if_else语句。比较这两 种方式。

module decoder3_8 ( G1 ,Y ,G2 ,A ,G3 ); input G1, G2, G3; wire G1, G2, G3; input [2:0] A ; wire [2:0] A ; output [7:0] Y ; reg [7:0] Y ; reg s; always @ ( A ,G1, G2, G3)