上电时序标准版

FIBOCOM Mini PCIe 硬件用户手册

H330 Mini PCIe硬件用户手册文档版本: V1.0.5更新日期: 2013-09-11版权声明版权所有©深圳市广和通实业发展有限公司2013。

保留一切权利。

非经本公司书面许可,任何单位和个人不得擅自摘抄、复制本文档内容的部分或全部,并不得以任何形式传播。

注意由于产品版本升级或其他原因,本文档内容会不定期进行更新。

除非另有约定,本文档仅作为使用指导,本文档中的所有陈述、信息和建议不构成任何明示或暗示的担保。

商标申明为深圳市广和通实业发展有限公司的注册商标,由所有人拥有。

目录1前言 (6)1.1说明 (6)1.2引用标准 (6)2产品概述 (7)2.1产品说明 (7)2.2产品规格 (7)3接口说明 (8)3.1Mini PCIe接口 (8)3.2天线接口 (10)4接口电气特性 (11)4.1极限条件 (11)4.2环境温度 (11)4.3供电电压时序要求 (11)4.3.1上电时间 (11)4.3.2下降时间 (12)5接口应用说明 (13)5.1USB接口 (13)5.1.1USB接口说明 (13)5.1.2USB接口应用 (13)5.2USIM接口 (13)5.2.1USIM卡信号管脚定义 (13)5.2.2USIM接口应用说明 (14)5.3模拟音频接口 (14)5.3.1音频接口信号定义 (14)5.3.2音频接口应用说明 (14)5.3.3音频通道输出特性 (15)5.4UART接口 (15)5.4.1UART接口定义 (15)5.4.2UART接口应用 (16)5.4.3振铃接指示 (16)5.5Reset信号 (17)5.6LPG信号 (17)5.7W_DISABLE信号 (18)6产品结构 (19)6.1外形尺寸 (19)1 前言1.1 说明本文档阐述了H330 Mini PCIe的电气特性、RF性能、结构尺寸以及应用环境等方面的信息。

在本文档和其他应用须知的帮助下,应用开发者可快速理解H330 Mini PCIe的性能并进行产品开发。

电源时序

∙帮助∙产品服务会员套餐服务华强电子网会员套餐中国制造会员套餐华强LED网会员套餐诚易通华强专项套餐EIM增值产品服务竞价排名ISCP现货认证600条BCP品牌认证旺铺单项产品服务洽洽酷管家超级买家委托交易推广服务在线交易推介竞标∙进入互联商务系统我的供应竞价排名IC上传元器件管理IC管理元器件上传华强LED网搜索推广我的采购求购信息询价管理客户服务预付款用户设置企业网站求职招聘报价管理系统消息∙请登录,免费注册登录搬到楼上了!∙手机版∙电子产业链全程电子商务平台∙旗下网站华强电子网华强LED网华强宝鲜贝网手机配件网中国电子交易中心华强电子检测中心外贸通电子发烧友华强PCB中国安防网English∙上海站北京站∙实体市场华强电子世界[有6502位会员在线][有83106次询价]∙IC/元器件∙旗舰店∙求购信息∙技术资料∙IC百科o IC/二三极管o其他电子元器件o库存呆料收购o IC百科o PDF资料请输入您要找的产品型号...∙∙首页∙供应信息∙中国制造∙求购信息∙诚信交易∙技术资料∙求职招聘∙商情资讯∙商友社区∙洽洽咨询400-887-3118∙位置:首页技术资料电子维基电源时序控制器电子维基[浏览次数:2722次]电源时序控制器电源时序控制器广泛用于电器设备供电电源的自动控制系统。

它精确地监控电压,以正确的时序进行上电和断电同时确保每个电压轨道之间的正确延时。

随着更新、更小工艺几何尺寸的出现,它被设计的越来越精确,目前有4路以上的有8路、16路等电源时序控制器。

目录∙电源时序控制器的特性∙电源时序控制器的作用∙电源时序控制器的参数∙电源时序控制器的特性o 1.提供多路电源每组电源自动延时1秒,对受控的设备起保护作用,确保整个系统的稳定工作每个独立的分组插座允许最大的.∙电源时序控制器的作用o 1.输入电源220~~50HZ 输入通道数8路2.电源输入端口火线零线地线3*4mm2三芯同轴线3.电源输出接口8*标准美式电源插座(10A/250VAC)4.通道负载输出单通道最大输出20A 整机最大输入负载50A5.开关器件继电器30A/250V AC nom6.控制输入2*RS232串口(一个输入,一个级联)7.使用控制接面四键通道控制按键8*通道选择LED指示灯8.8*通道状态LED指示灯9.温度范围-5度至+40度10.湿度范围:0至90%RH11.尺寸45mm*483mm*150mm(高*宽*深)12.重量2KG∙电源时序控制器的参数热门词条:线束连接器聚光灯电阻式传感器IC卡读写器变频器专用进线电抗器平行耦合带通滤波器无线粮情测控系统多普勒超声流量计本页面信息由华强电子网用户提供,如果涉嫌侵权,请与我们客服联系,我们核实后将及时处理。

SH366006 标准版用户手册_V1.0

《电动乘用车共享换电站建设规范-第1部分:总则》征求意见稿

T/CAAMTB XX-20XXICS43.040T26团体标准T/CAAMTB XX—20XX电动乘用车共享换电站建设规范第1部分:总则Construction requirements for EV shared swap stationPart1:General provisions(征求意见稿)20XX-XX-XX发布20XX-XX-XX实施中国汽车工业协会发布I前言《电动乘用车共享换电站建设规范》分为十三个部分:——第1部分:总则;——第2部分:换电平台和装置技术要求;——第3部分:换电电池包通信协议要求;——第4部分:车辆识别系统要求;——第5部分:电池包技术要求;——第6部分:换电机构技术要求;——第7部分:电连接器技术要求;——第8部分:液冷连接器技术要求;——第9部分:充电设备、搬运设备、电池仓储系统要求;——第10部分:数据安全管理,风险预警分析技术要求;——第11部分:安全防护及应急要求;——第12部分:换电站规划布局要求;——第13部分:换电站标识、安全运营、设备运输和安装要求。

本文件为T/CAAMTB XX-20XX《电动乘用车共享换电站建设规范》的第1部分。

本文件按照GB/T1.1—2020《标准化工作导则第1部分:标准化文件的结构和起草规则》的规定起草。

请注意本文件的某些内容可能涉及专利。

本文件的发布机构不承担识别专利的责任。

本文件由中国汽车工业协会提出并归口。

本文件起草单位:。

本文件主要起草人:。

本文件为首次发布。

II电动乘用车共享换电站建设规范总则1范围本文件进行了电动乘用车换电的国内、外相关标准梳理,内容包括标准顶层设计,共享换电站的主框架和技术路线等。

本文件适用于电动乘用车共享换电站系列标准的理解和使用。

2规范性引用文件下列文件中的内容通过文中的规范性引用而构成本文件必不可少的条款。

其中,注日期的引用文件,仅该日期对应的版本适用于本文件;不注日期的引用文件,其最新版本(包括所有的修改单)适用于本文件。

飞腾腾锐 D2000 处理器数据手册说明书

飞腾腾锐D2000系列处理器数据手册(V1.6)2022年4月飞腾信息技术有限公司版权声明:本文档用于指导用户的相关应用和开发工作,版权归属飞腾信息技术有限公司所有,受法律保护。

任何未经书面许可的公开、复制、转载、篡改行为将被依法追究法律责任。

免责声明:本文档仅提供阶段性数据,并不保证该等数据的准确性及完整性。

飞腾信息技术有限公司对此文档内容享有最终解释权,且保留随时更新、补充和修订的权利。

所有资料如有更改,恕不另行通知。

如有技术问题,可联系*******************.cn获取支持,因不当使用本文档造成的损失,本公司概不承担任何责任。

当前版本版本历史V0.2 2020.7.20 完成数据手册初稿V0.5 draft 2020.8.28 公司内部评审后修改版本V1.0 2020.12.29 第一个正式公开版本V1.1 2020.12.30 修正pin 结构图V1.2 2021.04.08 ●增加产品形态,见表1-1●修正图1.1;修正表4-1时钟频率数据●增加低速接口默认状态和默认电平说明●更新低速接口的NC处理方式目录1简介 (1)1.1技术指标 (3)1.2电源管理 (3)1.3功能框图 (4)1.4温度管理 (4)1.5封装 (4)1.6处理器可调试特性 (4)1.7术语 (5)1.8相关文档 (5)2接口说明 (6)2.1接口信号说明 (6)2.1.1引脚列表 (6)2.1.2复用引脚说明 (16)2.2DDR4SDRAM接口 (19)2.3PCI E接口 (29)2.3.1拆分方式 (34)2.3.2AC电容、校准电阻要求 (34)2.4千兆以太网(RGMII)接口 (34)2.4.1千兆以太网(RGMII)接口信号说明 (34)2.4.2千兆以太网(RGMII)接口电特性 (35)2.5I2C接口 (38)2.5.1I2C接口信号说明 (38)2.5.2I2C接口电特性 (38)2.6QSPI接口 (40)2.6.1QSPI接口信号说明 (41)2.6.2QSPI接口电特性 (42)2.7SPI接口 (43)2.7.1SPI接口信号说明 (43)2.7.2SPI接口电特性 (44)2.8UART接口 (44)2.8.1UART接口信号说明 (44)2.8.2UART接口电特性 (45)2.9GPIO接口 (45)2.9.1GPIO接口信号说明 (45)2.9.2GPIO接口电特性 (47)2.10SD接口 (47)2.10.1SD接口信号说明 (47)2.10.2SD接口电特性 (48)2.11CAN接口 (49)2.12WDT (49)2.13S YSTEM IO接口 (49)2.14调试接口 (50)2.14.1总体结构 (50)2.14.2调试功能 (51)2.14.3使用方法 (51)2.15保留引脚 (52)3技术 (54)3.1硬件安全技术 (54)3.2支持SCPI协议 (54)4时钟管理 (55)4.1时钟频率配置 (55)4.2时钟需求 (55)5电源管理 (56)5.1电源状态 (56)5.1.1S4/S5→S0 (56)5.1.2S0→S4/S5 (57)5.1.3S0→S3 (58)5.1.4S3→S0 (59)5.2电源参数 (61)5.3电源关断 (62)5.3.1动态关断 (62)5.4动态频率调节 (63)6温度管理 (64)6.1热参数 (64)7电气特性 (65)7.1极限工作条件 (65)7.2典型工作参数 (65)7.3通用引脚DC电气特性 (65)7.4PCI E引脚电气特性 (66)7.4.1公用模块电气特性 (67)7.4.2发送模块电气特性 (67)7.4.3公共模块电气特性 (68)7.4.4校准外接电阻参考说明 (68)8封装特性说明 (69)8.1封装尺寸 (69)8.2扣合力 (69)8.3信号位置分布 (69)9产品标识 (71)图目录图 1.1 D2000 功能框图 (4)图 2.1 D2000处理器接口信号框图 (6)图 2.2 外部校准电阻 (34)图 2.3 GMAC开关特性图 (36)图 2.4 MDIO写操作时序 (37)图 2.5 MDIO读操作 (37)图 2.6 MDIO读建立和保持时间 (37)图 2.7 RGMII发送通道时序 (37)图 2.8 RGMII接收通道时序 (37)图 2.9 RX数据端口采样时序图 (38)图 2.10 I2C接收时序 (40)图 2.11 I2C发送时序 (40)图 2.12 启动流程 (42)图 2.13 QSPI总线时序 (43)图 2.14 SPI时序图 (44)图 2.15 UART时序图 (45)图 2.16 GPIO中断结构图 (46)图 2.17 GPIO开关特性图 (47)图 2.18 SD卡时钟数据输入输出时序图(标准模式) (48)图 2.19 SD卡时钟数据输入输出时序图(高速模式) (49)图 2.20 D2000软件调试结构 (51)图 2.21 trace32连接PC进行调试 (52)图 5.1 S4/S5→S0开机时序图 (56)图 5.2 S0→S4/S5关机时序图 (58)图 5.3 S0→S3休眠时序图 (59)图 5.4 S3_OK和S3_OK_Clear信号链路 (60)图 5.5 S3→S0唤醒时序图 (61)图 5.6 时序图 (62)图 8.1 封装机械尺寸 (69)图 8.2 BGA MAP 分布图 (70)图 8.3 BGA MAP 结构图 (70)图 9.1 Marking1 (71)图 9.2 Marking_2 (71)表目录表1-1 D2000产品形态及参数 (2)表1-2 术语和缩略语表 (5)表2-1 D2000 DDR4 SDRAM 引脚信息 (6)表2-2 D2000 PCIe 引脚信息 (10)表2-3 D2000 RGMII 引脚信息 (13)表2-4 D2000 其他功能接口引脚信息 (13)表2-5 D2000 电源引脚信息 (14)表2-6 引脚复用表 (16)表2-7 支持的DDR4时序参数组合 (20)表2-8 支持的LPDDR4时序参数组合 (20)表2-9 支持的DDR4器件参数组合 (20)表2-10 支持的LPDDR4器件参数组合 (21)表2-11 DDR4模式接口信号说明 (21)表2-12 LPDDR4模式接口信号说明 (25)表2-13 PCIe接口描述 (29)表2-14 PCIe拆分模式表 (34)表2-15 千兆以太网(RGMII)信号说明 (34)表2-16 RGMII接口电特性 (36)表2-17 I2C接口描述 (38)表2-18 I2C接口电特性 (38)表2-19 常用命令汇总 (41)表2-20 QSPI接口描述 (42)表2-21 QSPI接口电特性 (42)表2-22 SPI接口描述 (43)表2-23 SPI接口电特性 (44)表2-24 UART接口描述 (44)表2-25 UART接口电特性 (45)表2-26 GPIO接口描述 (46)表2-27 专用GPIO说明 (47)表2-28 GPIO接口电特性 (47)表2-29 SD接口描述 (48)表2-30 总线时序参数值(标准模式) (48)表2-31 总线时序参数值(高速模式) (48)表2-32 接口电气特性 (49)表2-33 CAN接口描述 (49)表2-34 System接口描述 (49)表2-35 调试接口信号说明 (50)表2-36 调试环境支持 (50)表2-37 保留引脚描述 (52)表4-1 频率配置范围 (55)表4-2 时钟需求 (55)表5-1 电源状态 (56)表5-2 S4/S5→S0时序控制表 (56)表5-3 S0→S4/S5下电时序控制表 (57)表5-4 S0→S3休眠下电时序控制表 (59)表5-5 S3→S0唤醒上电时序控制表 (60)表5-6 电源管理协议 (62)表5-7 时序要求 (62)表5-8 功耗模式 (62)表7-1 典型工作参数 (65)表7-2 通用pad引脚电气特性 (65)表7-3 PCIe引脚电气特性 (66)表7-4 外部参考时钟电平规范 (67)表7-5 发送模块电气特性 (68)表7-6 公共模块电气特性 (68)表7-7 校准外接电阻参考说明 (68)表9-1 丝印说明1 (71)表9-2 Marking_2丝印说明 (71)1简介飞腾腾锐D2000系列处理器主要面向桌面应用、高端嵌入式和低端服务器领域的应用,该系列包含8 款产品,各产品的基本性能参数详见表1-1。

信号 开机分析图

3. 数据阶段 交换的数据阶段是指某一段时间﹐在该段时间里﹐Initiator与Target之间有一个数据对象 被传输﹒在某 一个数据阶段里﹐被传输的数据字节数是由Initiator 在该数据阶段里所设定的指令/字节 致能讯号数目来决定﹒每一个数据阶段持续的时间至少在一个PCI时钟周期﹒Initiator与 Target都必须表示它们准备完成该数据阶段﹐或者用一个PCI时钟周期的等待状态来延长数据 阶段﹐为此﹐PCI总线定义了Initiator(IRDY#)与Target(TRDY#)所使用的准备(ready)信号 线. 4. 交換期間 Initiator不会传送传输次数给Target﹒相反﹐在每一个数据阶段里﹐它都会表示是否是最 后一个数据项﹒在地址阶段的开始﹐FRAME#会被驱动到低电平﹐并且持续驱动﹐直到 Initiator(IRDY#)完成最后一个数据阶段为止﹒当Target在资料阶段中取样到IRDY#被驱动到 低电平﹐并且FRAME#被反驱动到高电平时﹐它就知道这是最后一个数据阶段﹒但﹐数据阶 段必须直到Target把TRDY#讯号驱动到低电平﹐才宣告完成﹒ 5. 交换完成且总线回到闲置状态 Initiator以反驱动FRAME#到高电平﹐以及驱动IRDY#到低电平﹐指示(BURST传输的) 最后一次数据传输正在进行中﹒在最后一次数据传输完成后.Initiator会以反驱动其准备 (IRDY#)到高电平的方式﹒让PCI总线回到闲置状态﹒假设有另一个BUS MASTER被PCI 总线仲裁器授予总线的拥有权﹐并且正在等待目前的Initiator 让出总线使用权﹐它就可以在同 一个PCI时钟周期的上升边缘(时钟9的上升边缘)侦测FRAME#及IRDY#是否被反驱动到 高电平﹒来侦测总线是否已经回到闲置状态﹒

KT2 维修流程 上电时序。 1.1 維修一般流程 一般来说,维修工程师拿到一块功能不良板时,不要急于动用维修设备,首先全面目测M/B看是否有严重的 外观问题,如连锡(在RMA中很少),虚焊或明显的断线等,如果有相应现象,则可以减少大量的维修时间(指 维修该板的时间)及不必要的物料损耗.如果目测无发现问题,则看明维修流程卡的所写的故障现象,接着 根据故障插上相应的维修设备,针对无显示的M/B,最好先不插CPU(谨防由于CPU的工作电源过高而烧毁 CPU),先用示波器或万用表测量CPU的工作电压是否正常,等正常后再插CPU验证故障现象,然后根据现象 查相关电路图,测量相关信号.直至查出故障的原因.维修中不涉及BGA的元器件一自己更换,凡是涉及到要 更换BGA的功能不良板则由专门的操作员更换..在更换芯片时应注意芯片的方向,在测试之前,应检查焊过的 芯片是否有虚焊,短路之现象。在送测试之前应仔细检查是否有损件,残留物,锡渣,锡尖等外观问题,提高维修效率 1.2 上电自检一般时序 上电后电脑会自动检测主要硬件 POST是如何进行自检测的? 主板在接通电源后,系统首先由(Power On Self Test,上电自检)程序来对内部各个设备进行检查。在我们按 下起动键(电源开关)时,系统的控制权就交由BIOS来完成,由于此时电压还不稳定,主板控制芯片组会向 CPU发出并保持一个RESET(重置)信号,让CPU初始化,同时等待电源发出的POWER GOOD信号(电源准备 好信号)。当电源开始稳定供电后(当然从不稳定到稳定的过程也只是短暂的瞬间),芯片组便撤去RESET信号(如 果是手动按下计算机面板上的Reset按钮来重启机器,那么松开该按钮时芯片组就会撤去RESET信号),CPU马 上就从地址FFFF0H处开始执行指令,这个地址在系统BIOS的地址范围内,无论是Award BIOS还是AMI BIOS, 放在这里的只是一条跳转指令,跳到系统BIOS中真正的启动代码处。系统BIOS的启动代码首先要做的事情就是 进行POST(Power On Self Test,加电自检),由于电脑的硬件设备很多(包括存储器、中断、扩展卡),因此要 检测这些设备的工作状态是否正常。这一过程是逐一进行的,BIOS厂商对每一个设备都给出了一个检测代码 (称为POST CODE即开机自我检测代码),在对某个设置进行检测时,首先将对应的POST CODE写入80H (地址)诊断端口,当该设备检测通过,则接着送另一个设置的POST CODE,对此设置进行测试。如果某个设 备测试没有通过,则此POST CODE会在80H处保留下来,检测程序也会中止,并根据已定的报警声进行报警 (BIOS厂商对报警声也分别作了定义,不同的设置出现故障,其报警声也是不同的,我们可以根据报警声的不 同,分辨出故障所在。 PCI DEBUG CARD介紹 利用DEBUG CARD OR 80 PORT可以用来DEBUG上电但无显的MOTHERBOARD 整个微机的开机过程分为硬件启动和软件启动﹐硬启动是指POWER的动作过程﹒而软启动部分是指BIOS的 POST过程﹒先是硬件启动而后是软件启动了解微机的开机过程,对主板功能维修是很重要的,因为很多功能不良板 ﹐特别是当机板,可以根据开机的顺序从而判断系统检测哪部分有问题﹐如果是无显示的板﹐可以从DEBUGE CARD上诊断系统运行的地址﹒可以使分析问题做到有的放失,不至于瞎子摸象

高云 GW1N 系列 FPGA 产品 数据手册

GW1N系列FPGA产品数据手册DS100-1.8, 2019-07-02版权所有© 2019广东高云半导体科技股份有限公司未经本公司书面许可,任何单位和个人都不得擅自摘抄、复制、翻译本文档内容的部分或全部,并不得以任何形式传播。

免责声明本文档并未授予任何知识产权的许可,并未以明示或暗示,或以禁止发言或其它方式授予任何知识产权许可。

除高云半导体在其产品的销售条款和条件中声明的责任之外,高云半导体概不承担任何法律或非法律责任。

高云半导体对高云半导体产品的销售和/或使用不作任何明示或暗示的担保,包括对产品的特定用途适用性、适销性或对任何专利权、版权或其它知识产权的侵权责任等,均不作担保。

高云半导体对文档中包含的文字、图片及其它内容的准确性和完整性不承担任何法律或非法律责任,高云半导体保留修改文档中任何内容的权利,恕不另行通知。

高云半导体不承诺对这些文档进行适时的更新。

版本信息目录目录 (i)图目录 (iv)表目录 (vi)1 关于本手册 (1)1.1 手册内容 (1)1.2 适用产品 (1)1.3 相关文档 (1)1.4 术语、缩略语 (1)1.5 技术支持与反馈 (3)2 产品概述 (4)2.1 特性概述 (4)2.1.1 特性..................................................................................................... 错误!未定义书签。

2.2 产品信息列表 (6)2.3 封装信息列表 (7)3 结构介绍 (8)3.1 结构框图 (8)3.2 可配置功能单元 (9)3.2.1 可配置逻辑单元 (10)3.2.2 布线资源单元 (12)3.3 输入输出模块 (12)3.3.1 I/O电平标准 (13)3.3.2 真LVDS设计 (17)3.3.3 I/O逻辑 (19)3.3.4 I/O逻辑工作模式 (21)3.4 块状静态随机存储器模块 (25)3.4.1 简介 (25)3.4.2 存储器配置模式 (26)3.4.3 存储器混合数据宽度配置 (27)3.4.5 校验位功能配置 (28)3.4.6 同步操作 (28)3.4.7 上电情况 (28)3.4.8 存储器操作模式 (28)3.4.9 B-SRAM操作模式 (31)3.4.10 时钟模式 (33)3.5 用户闪存资源(GW1N-1和GW1N-1S) (34)3.5.1 简介 (34)3.5.2 端口信号 (35)3.5.3 数据位宽选择 (36)3.5.4 操作模式 (36)3.5.5 读操作 (36)3.5.6 写操作 (37)3.6 用户闪存资源(GW1N-2/2B/4/4B/6/9) (37)3.6.1 简介 (37)3.6.2 端口信号 (38)3.6.3 操作模式 (39)3.7 数字信号处理模块 (39)3.7.1 简介 (39)3.7.2 DSP操作模式配置 (43)3.8 时钟 (43)3.8.1 全局时钟网络 (43)3.8.2 锁相环 (46)3.8.3 高速时钟 (48)3.8.4 延迟锁相环 (49)3.9 长线 (50)3.10 全局复置位 (50)3.11 编程配置 (50)3.11.1 SRAM编程 (50)3.11.2 Flash编程 (50)3.12 片内晶振 (50)4 电气特性 (52)4.1 工作条件 (52)4.2 ESD性能 (53)4.3 DC电气特性 (56)4.4.1 内部开关特性 (59)4.4.2 外部开关特性 (62)4.5 用户闪存电气特性 (62)4.5.1 DC电气特性1 (62)4.5.2 时序参数1,5,6 (64)4.5.3 操作时序图(GW1N-1/ GW1N-1S) (66)4.5.4 操作时序图(GW1N-2/2B/4/4B/6/9) (67)4.6 编程接口时序标准 (68)4.6.1 JTAG模式接口时序标准 (68)4.6.2 AUTO BOOT模式接口时序标准 (69)4.6.3 SSPI模式接口时序标准 (70)4.6.4 MSPI模式接口时序标准 (72)4.6.5 DUAL BOOT模式 (73)4.6.6 CPU模式 (73)4.6.7 SERIAL模式 (73)5 器件订货信息 (74)5.1 器件命名 (74)5.2 器件封装标识 (75)图目录图3-1 GW1N系列FPGA器件结构示意图 (8)图3-2 CFU结构示意图 (10)图3-3 CLS中的寄存器示意图 (11)图3-4 IOB结构示意图 (12)图3-5 GW1N-1/2/4/2B/4B I/O Bank分布示意图 (13)图3-6 GW1N-6/9器件I/O Bank分布示意图 (14)图3-7 GW1N-1S I/O Bank分布示意图 (14)图3-8真LVDS设计参考框图 (18)图3-9 I/O逻辑输出示意图 (19)图3-10 I/O逻辑输入示意图 (19)图3-11 IODELAY示意图 (19)图3-12 GW1N的I/O寄存器示意图 (20)图3-13 GW1N的IEM示意图 (20)图3-14普通模式下的I/O逻辑结构示意图 (21)图3-15 SDR模式下的I/O逻辑结构示意图 (21)图3-16 I/O逻辑的DDR输入示意图 (22)图3-17 I/O逻辑的DDR输出示意图 (22)图3-18 I/O逻辑的IDES4输入示意图 (22)图3-19 I/O逻辑的OSER4输出示意图 (23)图3-20 I/O逻辑的IVideo输入示意图 (23)图3-21 I/O逻辑的OVideo输出示意图 (23)图3-22 I/O逻辑的IDES8输入示意图 (23)图3-23 I/O逻辑的OSER8输出示意图 (24)图3-24 I/O逻辑的IDES10输入示意图 (24)图3-25 I/O逻辑的OSER10输出示意图 (24)图3-26 I/O逻辑的IDES16输入示意图 (24)图3-27 I/O逻辑的OSER16输出示意图 (25)图3-28单端口存储模式框图 (28)图3-29双端口存储模式框图 (29)图3-30伪双端口存储模式框图1 (30)图3-31只读模式存储框图 (31)图3-32单端口、伪双端口及双端口模式下的流水线模式 (32)图3-33独立时钟模式 (33)图3-34读写时钟模式 (34)图3-35单端口时钟模式 (34)图3-36 GW1N-1/GW1N-1S用户闪存端口信号 (35)图3-37 GW1N-2/4/2B/4B/6/9用户闪存端口信号 (38)图3-38 DSP宏单元 (40)图3-39 GCLK象限分布示意 (44)图3-40 DQCE结构示意图 (44)图3-41 DCS接口示意图 (45)图3-42 DCS Rising Edge模式下的时序示意图 (45)图3-43 DCS Falling Edge模式下的时序示意图 (45)图3-44 PLL示意图 (46)图3-45 GW1N-1 HCLK示意图 (48)图3-46 GW1N-2/2B/4 /4B HCLK示意图 (48)图3-47 GW1N-6/9 HCLK示意图 (49)图3-48 GW1N-1S HCLK示意图 (49)图3-49 GW1N的延迟锁相环示意图 (49)图4-1读操作模式 (66)图4-2写入页锁存模式 (66)图4-3清除页锁存模式 (66)图4-4高电平周期 (67)图4-5用户闪存读操作时序 (67)图4-6用户闪存编程操作时序 (67)图4-7用户闪存擦除操作时序 (68)图4-8 JTAG编程模式时序示意图 (68)图4-9重新上电时序图 (70)图4-10 RECONFIG_N触发时序图 (70)图4-11 SSPI编程模式时序图 (71)图4-12 MSPI编程模式时序示意图 (72)图5-1器件命名方法–ES (74)图5-2器件命名方法–Production (75)图5-3器件封装标识示例 (75)表目录表目录表1-1术语、缩略语 (1)表2-1产品信息列表 (6)表2-2产品封装和最大用户I/O信息、LVDS对数 (7)表3-1 CLS中寄存器模块信号说明 (11)表3-2 GW1N系列FPGA产品支持的输出I/O类型及部分可选配置 (15)表3-3 GW1N支持的输入I/O类型及部分可选配置 (16)表3-4 B-SRAM信号功能 (26)表3-5存储器配置列表 (26)表3-6双端口混合读写数据宽度配置列表 (27)表3-7伪双端口混合读写数据宽度配置列表 (27)表3-8单端口存储配置模式列表 (29)表3-9双端口存储配置模式列表 (29)表3-10伪双端口存储配置模式列表 (30)表3-11只读配置模式列表 (31)表3-12时钟模式配置列表 (33)表3-13用户闪存模块信号说明 (35)表3-14输出位宽选择 (36)表3-15输入位宽选择 (36)表3-16操作模式选择 (36)表3-17用户闪存模块信号说明 (38)表3-18用户模式真值表 (39)表3-19 DSP端口描述 (41)表3-20内部寄存器描述 (41)表3-21 PLL端口定义 (47)表3-22 GW1N-2/2B/4/4B片内晶振的输出频率选项 (51)表3-23 GW1N-1/1S/6/9片内晶振的输出频率 (51)表4-1绝对最大范围 (52)表4-2推荐工作范围 (52)表4-3热插拔特性 (53)表目录表4-4 GW1N ESD - HBM (53)表4-5 GW1N ESD – CDM (54)表4-6推荐工作范围内的直流电气特性 (54)表4-7静态电流(Static Supply Current) (55)表4-8 I/O推荐工作条件 (56)表4-9 IOB单端DC电气特性(IOB Single‐Ended DC Electrical Characteristic) (57)表4-10 I/O差分DC电气特性(IOB Differential Electrical Characteristics) (58)表4-11 CFU 内部时序参数 (59)表4-12 B-SRAM内部时序参数 (61)表4-13 DSP内部时序参数 (61)表4-14 Gearbox内部时序参数 (61)表4-15外部开关特性 (62)表4-16片内晶振输出频率 (62)表4-17锁相环相关参数 (62)表4-18 GW1N-1/ GW1N-1S器件用户闪存DC电气特性 (63)表4-19 GW1N-2/2B/4/4B/6/9器件用户闪存DC电气特性 (63)表4-20 GW1N-1/ GW1N-1S器件用户闪存时序参数 (64)表4-21 GW1N-2/2B/4/4B/6/9器件用户闪存时序参数 (64)表4-22 JTAG编程模式时序参数 (68)表4-23重新上电和RECONFIG_N触发时序参数 (70)表4-24 SSPI编程模式时序参数 (71)表4-25 MSPI编程模式时序参数 (72)1关于本手册 1.1手册内容1关于本手册1.1手册内容GW1N系列FPGA产品数据手册主要包括高云半导体GW1N系列FPGA产品特性概述、产品资源信息、内部结构介绍、电气特性、编程接口时序以及器件订货信息。

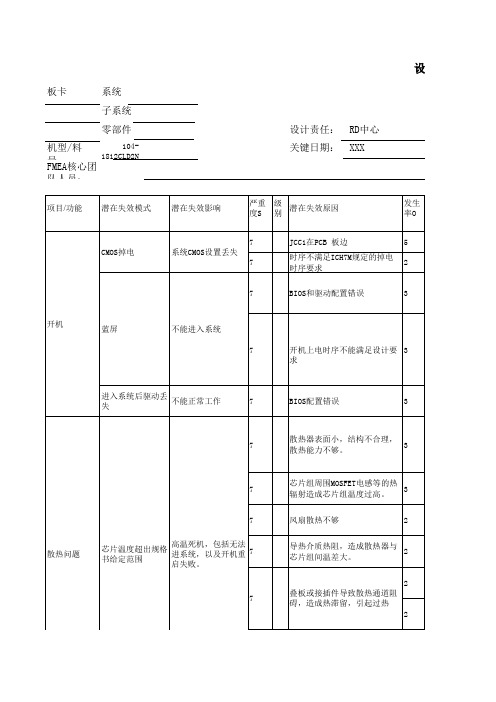

嵌入式工控板卡DFMEA范例

芯片组本身实际抗高温与规格 书不符合(或策划采用筛选的 2 办法来过高温) PCB布局不合理导致散热器设 计受结构限制,主板上大热源 3 间距小互相影响。

MOS选取不满足要求

2

其他元器件选取不满足要求 2

PCB走线不当

3

内存时钟带负载能力不够

3

CF接口设计没有DMA功能

2

7

显示芯片电源纹波太大

3

显示

2

42 / 28 / 28 /

沈晖 沈晖

1.用测试开发板验证 2.根据实际样板结果更改

2

参与PCB布局和评审,合理解 决散热结构问题。

2

仔细计算所选MOS能否满足功 耗需求,参考以前成熟项目

3

选用规格符合温度范围的要 求的元件

2

1:PCB走线尽量按照design

guide的要求,实在不能满足

的参考其他成熟方案。

XXXX 版本:XX

行动结果 已采取的行动

S O D RP N

XXX 版本:XX

6

网络灯 电源IC 电源 CPU

网络灯接反

网络灯异常

5

TPS51116为新导入 IC,没有验证过

无法满足内存供电需 求

8

无法满足主板上电 时序要求

主板无法正常工作

9

纹波电流大

系统在运行过程中不

稳定,特别是跑大的 8

系统时,容易死机

网络变压器的电源与RTL8111C 冲突

3

设计规范和实际指示灯的连接 不一致,或线材连接反

2

IC供货来源

2

新导入的IC,设计中存在缺陷 4

全新chipset,没有验证

3

电源纹波控制没有满足芯片的 要求

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

【是3VPCU待机电压正常后,EC发出电压给晶振】,晶振起振后,给EC待机时提供一个时钟,复位是有一个电阻和一个充电电容延迟以后产生复位【LREST】,当EC的待机、时钟、复位满足以后,EC发出片选信号选中BIOS,从BIOS芯片中读取程序,去配置EC中的GPIO的引脚定义,当EC待机条件满足后,程序的代码也读取出来了,EC就可以上电了!

5.xx上电时序详解:

首先产生+3VA +5VA +12VA的线性电压其中+3VA经过转换成+3VA_EC给EC供电接着EC复位当EC的供电时钟复位正常后EC发出vsus_ON开启3vsus 5vsus 12vsus电感电压开启完毕后发出sus_PWRGD信号给EC此时3vsus5vsus给南桥供电接着EC发出rsmrst#给南桥完成待机等待客户按下开关键。

当用户按下开关键触发EC,EC发出EC_ON#高电平紧接着EC发出PBTN_OUT#使南桥响应接着南桥发出s5 s3信号开启syson susp#最后发出VR_ON紧接着发出cpu电源好信号VGATE接着EC发出ICH_POK CL_PWROK (由南桥开启时钟电路)H_CPUPWRGD PCIRST# PLTRST# H_RESET# ADS#

DE、xx

10:北桥在供电、时钟、PWROK均满足正常时以及收到PLTRST后,发出CPURST供至CPU

11:南桥发出INIT#初始化信号至CPU

12:CPU开始工作,发出第一个寻址指令信号ADS#

另外备注:

当CPU条件满足以后,CPU就会发出地址信号,先过北桥,通过DMI总线到南桥,通过LPC到EC,通过X—BUS到BIOS,从BIOS里面读取开机自检信息,然后按照原路再返回,最终先将信息载入到内存,然后CPU再到内存一步去读取,对整个系统一个测试,如果测试所有硬件没有问题,那此机器就可以点亮,如果检测有问题就会出现档代码或跑一下就不跑码了

时序步骤:

1:NBSWON#:

开机触发信号,未按开机键之前,此信号有3VPCU上拉电压,按下电源键,此信号被拉至地,形成低电位有效触发至EC

NBSWON#是一个高——低——高的低电位有效触发信号

2:当EC收到有效触发以后,EC就发出一个S5—ON高电位信号,S5—ON一出来就控制将3VPCU电压转换成3V—S5供至南桥:

按下开关pwrsw#触发EC EC发出PWRBTN#给南桥,南桥收到后发出susc# susB#给EC经EC转换SUSC_EC# SUSB_EC#开启相应电压。所有电压开启完毕后发出ALL_SYSTEM_PWRGD给EC EC收到后发出VRON开启cpu供电然后cpu电源好信号cpu-pwrgd给EC EC发出EC_CLK_EN给南桥发出时钟开启信号ck_pwrgd接着EC发出pwrok信号给南北桥当南桥收到此信号后发出复位信号pltrst#复位北桥然后北桥发出H_CPURST复位cpu

备注:

在广达笔记本中,只要其中任意一个PWRGD没有起来,HWPG就会被拉低,HWPG被拉低,EC就检查不到HWPG这个信号,就会停止发出MAINON和SUSON,故障表现为:

掉电

7:其中CPU的VCORE电压正常后,MAX8550发出IMVP—PWG信号(代表CPU的核心电压电源好信号),此信号去到两路:

EC第二个信号:

适配器检测信号(ACIN)

说明:

当适配器插入时,在ACIN处也是有一个电压值的,如果此电压值没有起来,EC就认为适配器没有检测到,那么也是上不了电的.

C:

EC第三个信号:

电池电量低的检测信号(BAT—LOW)

说明:

如果电池电量低,EC也会停止上电,此脚必须有一个高电平,上拉电压,才正常

+3V、+5V),EC将SUSB#信号延时99ms后,发出VRON,用于开启CPU的VCORE电压)

6:在各路电压产生正常以后,各路电压的PWRGOOD信号相连经逻辑相遇后产生HWPG信号供至EC,HWPG给到EC后,EC就发出PWROK更至南桥里面的PWROK信号脚位上(PWROK代表所有系统电压都正常)

3.纬创的上电时序

解析:

纬创的时序先产生5v线性电压5V_AUX_S5

接着由5V_AUX_S5转换成3D3V_AUX_S5此电压仅接着给EC供电,当EC有了供电外接晶振就会起振接着就有EC的复位此时EC发出s5_ENABLE信号开启系统3v 5v电压3D3V_S5和5v_S5分别给南桥的3v待机点和5v待机点供电南桥有了供电外接晶振就会起振此时EC发出RSMRST#给南桥完成待机等待用户按下开关键。当按下开关键触发EC,EC发出PM_PWRBTN#当南桥收到此信号后就会发出s4 s3信号接着发出CPUCORE_ON开启cpu单元电路,cpu电路工作正常后发出VGATE_PWRGD告诉南桥电路开启完毕接着EC发出pwrok告诉南桥各路电压开启正常接着开启时钟电路接着发出H_PWRGD PCIRST CPURST.

4:当南桥供电、时钟、复位条件满足以后以及收到PWRBIN#有效触发后,依次发出高电平的SLP—S3#、SLP—S4#(或S5#)的信号,SLP—S4#更名为:

SUSC#,SLP—S3#更名为:

SUSB#信号发至EC

5:EC收到这两个高电位信号以后,分别将:

SUSC#转换成SUSON(SUSON是用于开启各种SUS电压),将SUSB#转换成MAINON(MAINON是用于开启各种MAIN电压或是正电压开启信号,比如:

VCCSUS3.3(3.3V待机),将5VPCU电压转换成5V—S5供至南桥的V5REFSUS(5V待机),此时南桥有了待机电压3:

(1):

EC发出RSMRST#信号(从低到迟续高电位)至南桥中的RSMRST#脚位,其目的是:

清零xx里面的ACPI控制器的逻辑关系

(2):

EC收到NBSWON#后,延时发出DNBSWON#低电位有效触发至南桥中的PWRBIN#脚位,告知南桥用户已按下电源键

在EC上电之前,还有个前提条件:

(几个信号)

A:

EC第一个信号:

LID—EC#这个信号是S3的休眠开关检测信号

A:

EC第一个信号:

LID—EC#这个信号是S3的休眠开关检测信号

说明:

LID—EC#在正常的情况下,是被上拉的一个信号,如果被强制拉低到一个低电位的话,机器是上不了电的,不能实现通电&

B:

1.上电时序的区别是不同厂家的上电时序在电路图中的电压标识符号不同,电压的开启顺序不同,这是不同时序的最大区别。

2.xx的上电时序

解析:

首先出3v 5v电感电压(3Valw 5vALW)以及vL线性电压,电感电压(3Valw 5vALW)3Valw给EC以及南桥3v待机点5vALW也给南桥5v待机点当EC有了供电之后外接晶振就会起振紧接着EC就会复位当南桥有了供电后外接晶振也会起振,此时EC发出rsmrst#给南桥待机完成等待用户按下开机按键。

一路:

此信号发至南桥的VRMPWRGD脚位,告知南桥此时CPU的核心电压已经常另一路:

此信号发至北桥的PWROK脚位,作为北桥的重要工作条件

8:当南桥里面的PWROK和VRMPWRGD这两个条件满足以后,此两个信号经逻辑相遇产生CPUPWRGD信号供至CPU

9:当南桥发出CPUPWRGD以后,南桥内部经过延时缓冲发出PCIRST#(原始复位)、PLTRST(平台复位),其中PCIRST供给所有PCI设备,PLTRST供给GPU、I

4.xx上电时序详解:

先产生3vpcu 5vpcu电感电压3vpcu给EC供电接着晶振起振复位接着按下开关键触发EC EC发出s5_ON此信号开启3v 5v后继3v_S55V_S5给南桥供电时钟接着EC发出rsmrst#给南桥接着ON MAINON接着发出VR_ON CPU工作正常后发出HWPG给EC接着发出时钟开启信号开启时钟电路另一路imvpok告诉南桥供电开启完毕接着EC发出ECpwrok告诉南桥电压开启完毕接着发出H_PWRGOOG PLTRST#