上电时序

芯片上电时序latch up大电流

芯片上电时序latch up大电流一、概述在现代社会中,芯片技术被广泛应用于各个领域,如通信、计算机、电子设备等。

而芯片在运行过程中可能会出现一些问题,比如Latch-up现象。

Latch-up是指芯片在工作时由于某些原因导致出现异常电流,这种异常电流可能对芯片造成严重损坏。

芯片上电时序Latch-up 大电流成为了一个重要的研究课题。

二、芯片上电时序Latch-up大电流的原因1.器件自身结构缺陷芯片中的器件可能存在结构缺陷,比如P-N结区域不良、金属引线焊点不良等,这些缺陷会导致芯片在上电时出现Latch-up现象。

2.工作环境不良芯片在工作时受到电磁干扰、温度变化等环境因素的影响,这些因素可能会导致Latch-up现象的发生。

3.设计缺陷芯片的设计可能存在缺陷,比如电源线路不合理、过电压保护不足等,这些设计缺陷也会导致Latch-up现象的出现。

三、芯片上电时序Latch-up大电流的影响Latch-up现象会使芯片内部出现异常电流,导致芯片的正常工作受到干扰甚至损坏。

而且Latch-up现象还可能会引发芯片周围其他器件的Latch-up现象,进一步扩大了损害范围,因此芯片上电时序Latch-up大电流对芯片的影响是非常严重的。

四、应对策略1.优化芯片设计在设计芯片时应充分考虑芯片在工作时可能遇到的各种环境因素,保证芯片的电路布局合理、电源线路设计完善,避免因设计缺陷导致Latch-up现象的发生。

2.加强工艺控制在制造芯片时应加强工艺控制,保证芯片中器件的质量,避免器件结构缺陷导致Latch-up现象的出现。

3.优化工作环境对芯片的工作环境进行优化,保证芯片在工作时受到最小的电磁干扰、温度变化等环境因素的影响,降低Latch-up现象发生的可能性。

五、结论芯片上电时序Latch-up大电流是一个复杂的问题,它涉及到芯片本身的结构、工作环境、设计等多个方面。

只有综合考虑这些因素,并在芯片设计、制造、工作过程中采取有效的措施,才能有效地避免Latch-up现象的发生,保障芯片的正常工作和稳定运行。

笔记本上电时序

SB-CLOCK

+VCC_RTC经过三个电阻输入给南桥,则输出RTC-X1,RTC_X2给晶振 X2000产生32.768KHz的频率

反馈给南桥

RTC_RST:复位C-MOS信息.

返回南桥

PM_PWRBTN#

按下SW5605,则PWR_SW# 瞬间拉低

+3VA_EC经过电阻到PWR_SW#,给 PWR_SW#一个高电平

返回

附:比较器

比较器工作原理: 正极 负极 1:当正极大于负极时,输出电 压VCC OUT就等于输入电压VCC IN 2当正极小于负极电压时,输出 电压VCC OUT就等于接地GND + > - VCC OUT=VCC IN GND + < - VCC OUT=GND 比较器一般用于电路中都是固定正 极(或负极)电压电压,利用VCC OUT 来控制负极(或正极)电压

ALL_SYSTEM_PWRGD

二极管在这里的作用:保护SUS_PWRGD,当其他PWRGD有 问题时不会拉低SUS_PWRGD,因为只有SUS_PWRGD工作 正常后南桥才能工作,来开启其他电压

这时VRM_PWRGD还没有 产生

PWR_OK_VGA 由显卡接口发出

这里是个保护电路,上面四个PWRGD为高电平,才会有ALL_SYSTEM_PWR. 发送到EC

放大点击

FORCE_OFF#

与门工作原理:只要有输 入低电平则输出为低电平, 如果PWRGD有问题输出 低电平,则FORCE_OFF# 拉低,则会关机. FOREC_OFF点击

附:High-Low Side

原理:芯片先给High Side的栅极一个高电平,使其打开电压下来,同时给Low Side的 栅极一个低电平使其关闭,产生电压经过电感给电容充电,当电压过高时,则HighLow Side相反工作使电压拉低,维持一个稳定的电压输出. 特点:提高电流,稳定电压 返回

数字ic soc中的上下电时序

一、ic soc中的上下电时序概述IC SOC(System on Chip)是指将多个功能集成在一个芯片上的集成电路系统,它具有高性能和低功耗的特点,广泛应用于电子产品中。

在IC SOC的设计和使用中,上下电时序是非常重要的,它直接影响着芯片的性能和稳定性。

本文将从上下电时序的概念、原理和设计要点等方面进行介绍。

二、上下电时序的概念上下电时序是指IC SOC在工作过程中的上电和下电时序。

上电时序是指芯片在上电过程中各个电源和信号的建立时间。

下电时序是指在断电过程中芯片各个模块的关闭时间。

上下电时序对芯片的正常工作、稳定性和寿命等都有重要影响。

三、上下电时序的原理在IC SOC中,上下电时序的原理主要包括内部模块的电源管理、时钟树的同步和数据传输的稳定等。

在上电时,各个模块需要按照一定的顺序建立电源和信号,以保证芯片整体的稳定和正常工作。

在下电时,各个模块也需要按照一定的时序进行关闭,以避免数据丢失和系统崩溃。

四、上下电时序的设计要点1. 测试和验证:在设计IC SOC时,需要对上下电时序进行充分的测试和验证,以保证芯片在各种情况下都能正常工作。

2. 时序规划:在设计芯片的时候,需要对上下电时序进行合理的规划,以确保芯片的稳定性和可靠性。

3. 约束设置:在设计工具中,需要对上下电时序进行严格的约束设置,以保证芯片的上下电时序满足实际需求。

五、上下电时序的实际应用在实际应用中,上下电时序的设计和验证是IC SOC设计工程师需要重点关注的内容。

只有合理设计和严格验证上下电时序,才能保证芯片的正常工作和稳定性。

六、总结上下电时序是IC SOC设计中的重要环节,它直接关系到芯片的性能和稳定性。

设计工程师需要充分理解上下电时序的概念、原理和设计要点,从而在实际工作中能够合理规划和有效实施上下电时序的设计和验证工作。

只有这样,才能保证IC SOC在各种应用场景下都能够正常工作和稳定运行。

七、上下电时序的调整和优化在实际应用中,为了进一步提高IC SOC的性能和稳定性,设计工程师需要对上下电时序进行调整和优化。

上电时序

什么叫上电时序? 什么叫上电时序?

• 时序其实就是个排程,比如你家的电视、 时序其实就是个排程,比如你家的电视、 DVD、功放、无线话筒发射机之类的,有 、功放、无线话筒发射机之类的, 个电源时序器的话, 个电源时序器的话,把所有设备的供电都 由时序器供电,时序器再接入电源, 由时序器供电,时序器再接入电源,时序 器一开按照设备在时序器接口的先后一个 一个的自动打开设备, 一个的自动打开设备,简而言之主板的上 电时序是为了防止烧某样东西, 电时序是为了防止烧某样东西,按照排程 都设备逐一供电不是同时供电, 都设备逐一供电不是同时供电,也防止瞬 间电流过大~! 间电流过大 !

什么叫上电时序? 什么叫上电时序?

• 待机电压、保护隔离主供电、系统供电、 待机电压、保护隔离主供电、系统供电、 内存供电、 供电等电压。 内存供电、cpu供电等电压。 供电等电压 • 笔记本上这么多电压如何产生,他们是遵 笔记本上这么多电压如何产生, 照一定的顺序产生, 照一定的顺序产生,这个顺序就叫上电时 序。 1.为了省电 为了省电 2.保护相关电路 保护相关电路

• ALW 一直有的供电 • PM_SLP_S5# 关机模式 为低电平 电脑关机 电脑退出关机状态(开机) 为高电平 电脑退出关机状态(开机) • PM_SLP_S3# 休眠模式 为低电平 电脑休眠 为高电平 电脑退出休眠模式

• DDR_VREF_S3/1D8V 1.8V内存电压 内存电压 • 芯片组供电,显卡电压 芯片组供电, 1D5V 显卡电压 1D2V北桥电压 北桥电压 CPUCORE_ON cpu电压开启信号 电压开启信号 CLK_EN# 时钟开启 VGATE_PWRGD 电源好信号 PLT_RST#/PCIRST# 复位信号

atx3.0标准下,上电放电时序

一、引言ATX3.0标准是一种电源管理规范,它规定了计算机的上电放电时序,以保证计算机硬件的正常运转和保护。

本文将详细介绍ATX3.0标准下的上电放电时序,以便读者更好地了解计算机硬件的工作原理。

二、ATX3.0标准概述1. ATX3.0标准是由英特尔公司制定的,它取代了旧版的ATX2.0标准,为计算机硬件的电源管理提供了更加严谨的规定。

2. ATX3.0标准规定了计算机电源的输出电压范围、稳定性要求、上电放电时序等重要参数。

3. 上电放电时序是指计算机电源上电和断电的时间顺序,它对于计算机硬件的正常运转和保护至关重要。

三、上电时序1. 上电时序是指计算机电源在接通电源后,各种电压输出的时间顺序。

2. 根据ATX3.0标准,上电时序应包括以下几个关键步骤:(1) 5VSB上电:在主电源接通后,计算机电源的5VSB线路应首先提供稳定的待机电压,以供主板和其他设备的待机模式使用。

(2) PW_ON信号响应:计算机主板上的PW_ON信号由主机电源按键触发,触发后,主板应向电源发送启动信号。

(3) 主电压输出:在接收到启动信号后,计算机电源应输出各种主要电压(如+12V、+5V等),以供主板和其他设备正常工作。

四、放电时序1. 放电时序是指计算机电源在断开电源后,各种电压输出的时间顺序。

2. 根据ATX3.0标准,放电时序应包括以下几个关键步骤:(1) 主电压输出关闭:在主电源断开后,计算机电源应先关闭各种主要电压的输出。

(2) 5VSB放电:在主电源断开后,计算机电源应在一定时间内将5VSB线路的电压降至安全范围内,以避免对主板和其他设备的损害。

(3) 所有输出关闭:在放电完毕后,计算机电源应确保所有电压输出均已关闭,以保证计算机设备的安全。

五、ATX3.0标准的改进1. 相较于旧版的ATX2.0标准,ATX3.0标准在上电放电时序方面做出了以下改进:(1) 5VSB线路的待机电压更加稳定,能够更好地支持待机模式。

电脑上电时序

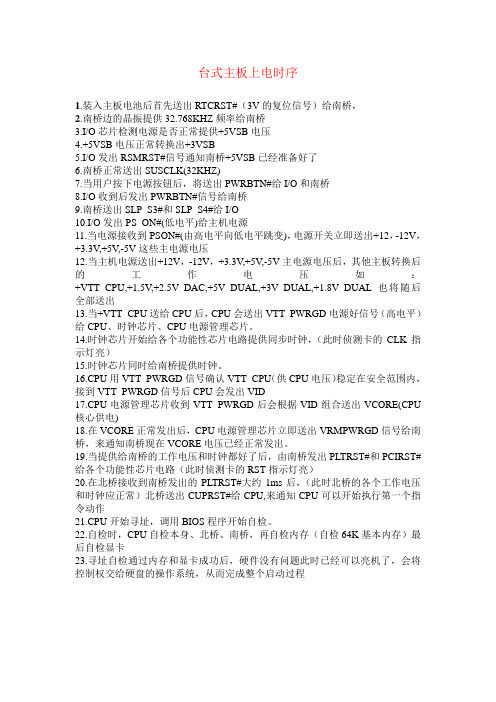

台式主板上电时序1.装入主板电池后首先送出RTCRST#(3V的复位信号)给南桥,2.南桥边的晶振提供32.768KHZ频率给南桥3.I/O芯片检测电源是否正常提供+5VSB电压4.+5VSB电压正常转换出+3VSB5.I/O发出RSMRST#信号通知南桥+5VSB已经准备好了6.南桥正常送出SUSCLK(32KHZ)7.当用户按下电源按钮后,将送出PWRBTN#给I/O和南桥8.I/O收到后发出PWRBTN#信号给南桥9.南桥送出SLP_S3#和SLP_S4#给I/O10.I/O发出PS_ON#(低电平)给主机电源11.当电源接收到PSON#(由高电平向低电平跳变),电源开关立即送出+12,-12V,+3.3V,+5V,-5V这些主电源电压12.当主机电源送出+12V,-12V,+3.3V,+5V,-5V主电源电压后,其他主板转换后的工作电压如:+VTT_CPU,+1.5V,+2.5V_DAC,+5V_DUAL,+3V_DUAL,+1.8V_DUAL也将随后全部送出13.当+VTT_CPU送给CPU后,CPU会送出VTT_PWRGD电源好信号(高电平)给CPU、时钟芯片、CPU电源管理芯片。

14.时钟芯片开始给各个功能性芯片电路提供同步时钟,(此时侦测卡的CLK指示灯亮)15.时钟芯片同时给南桥提供时钟。

16.CPU用VTT_PWRGD信号确认VTT_CPU(供CPU电压)稳定在安全范围内,接到VTT_PWRGD信号后CPU会发出VID17.CPU电源管理芯片收到VTT_PWRGD后会根据VID组合送出VCORE(CPU 核心供电)18.在VCORE正常发出后,CPU电源管理芯片立即送出VRMPWRGD信号给南桥,来通知南桥现在VCORE电压已经正常发出。

19.当提供给南桥的工作电压和时钟都好了后,由南桥发出PLTRST#和PCIRST#给各个功能性芯片电路(此时侦测卡的RST指示灯亮)20.在北桥接收到南桥发出的PLTRST#大约1ms后,(此时北桥的各个工作电压和时钟应正常)北桥送出CUPRST#给CPU,来通知CPU可以开始执行第一个指令动作21.CPU开始寻址,调用BIOS程序开始自检。

必备主板上电时序图,强烈推荐

POWER_CHARGER

输出低电平信号CHG_PDS开启A/D_DOCK_IN转化AC_BAT_SYS 输出低电平信号CHG_PDL开启BAT_CON转化AC_BAT_SYS

ACIN

输入电压

DCIN

ProTek MQC.

POWER PATH A/D_DOCK_IN→AC_BAT_SYS

EC-工作电压

+3VS是SB工作后由 SUSB#_PWR开启

ProTek MQC.

EC-RESET

+3VA_EC输入给芯片U3001产生EC_RST# 从pin19输入 ECProTΒιβλιοθήκη k MQC.EC-CLOCK

当EC接收到工作电压后就开始从pin160发出EC_XOUT 给晶振提供电压使其产生 32.768KHz的频率给EC工作

ProTek MQC.

返回南桥

PM_PWRBTN#

按下SW5605,则PWR_SW# 瞬间拉低

ProTek MQC.

+3VA_EC经过电阻到PWR_SW#,给 PWR_SW#一个高电平

南桥开机最后一个条件 返回南桥

南桥开机条件

+3VSUS PM_RSMRST# +VCC-RTC CLK(32.768KHz) PM_PWRBTN#

ProTek MQC.

PM_RSMRST

南桥开机条件之一 当EC pin54接收到SUS_PWRGD后从pin105发出PM_RSMRST#

ProTek MQC.

返回南桥

+VCC_RTC

南桥开机条件之一

C-MOS电池

+RTCBAT经过电阻R2001经过D2000产生+VCC_RTC

主板上电时序分解

15、时钟芯片收到VTT_PWRGD,且其3.3V电压和14.318MHz都正常后发出各组频率;

12、CPU收到VTT_PWRGD后,发出VID[0:5]组合信号给cpu电源管理芯片VRM;《VID是在CPU得到VTT电压之后,CPU通过它上面的VID脚的接地与不接地,来拉低与置高电源IC上面VID脚的电压,让电源IC知道CPU需要多少V的供电》

13、电源管理芯片,在供电正常和收到VTT_PWRGD和CPU发来的VID组合后,产生VCORE;《VCORE电压是提供给CPU工作的电压,电压转换主要分为两种1)线性电压调变2)PWM调变(也称为脉冲宽度调变)。一般VCORE电压都是通过第二种方法调变得到的》

1、装入电池后首先送出RTCRST#,3V_BAT给南桥;《RTC是Real Time Clock,意为实时时钟;rst是reset,意为复位》(CMOS电池没电或CMOS跳线设为清零时,VCCRTC为低电平(检测点:CMOS跳线1脚),RTCRST#有效,使CMOS电路复位状态,即保存的CMOS消息丢失。《VCCRTC是Real Time Clock VCC的缩写,意为实时时钟(正)电源》)《3V_BAT是电池电压,即VCCRTC,在待机状态中,若此电池没有或者没有电,接通电源后,将首先调用转换出的+3VSB,代替电池3V_BAT

11、当+VTT_CPU一路供给CPU后,另一路会经过电路转换出VTT_PWRGD信号(高电平),给CPU、电源管理芯片、 时钟芯片。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1.PWRBTN#/PWRSW#: Power Button/Power Switch

主板上電按鈕或開關,一般置於主板右下方的PANEL上,以便於組裝機,它需要由一電阻Pull Hign,低電平有效.

2.: Stand by电压,預備.

意義為在機箱電源即主板的A TX Power打開但並未上電的情況下,電源會提供預備電壓,並且主板上會有多個預備上電的電壓存在,若此條件未滿足,主板肯定會無法上電.此些電壓如:12VSB,5VSB,3VSB,2.5VSB,1.8VSB,1.5VSB,1.2VSB,1.05VSB.此些電壓在主板上電後仍會存在,做為工作電壓使用.

3.RSMRST#

為主板控制上電部分的芯片產生發給ICH的信號,意義為通知ICH說明5VSB電壓為ok的,它在有的板子上的名稱為AUXOK. 辟如產生RSMRST#的芯片可能為SMSC,ITE,Winbond,ASUS的Super I/O,或AS016等.

4.SLP_S3#

當它動作時,表示系統進入S3(suspend to RAM)模式,當不是用在STR模式時,此信號可用來控制電源的動作,它一般由南橋發出,在有的板子上的名稱為SUSB#.它們的作用是等同的.

5.32.768KHZ

它是一個圓筒晶振工作時產生的頻率大小,是主板RTC邏輯電路的一部分,RTC邏輯主要由電池,32.768KHZ晶振等組成,起到保存系統時間,日期和CMOS設置的作用

6.PSON#

控制A TX Power 是否輸出電源的訊號,高電平時,電源不會動作,低電平時,電源供出電壓,說明主板已上電.在S3,S5狀態時,它為High,在S1狀態時,它為Low.。