74ls138管脚图及功能真值表

74ls138管脚图及功能

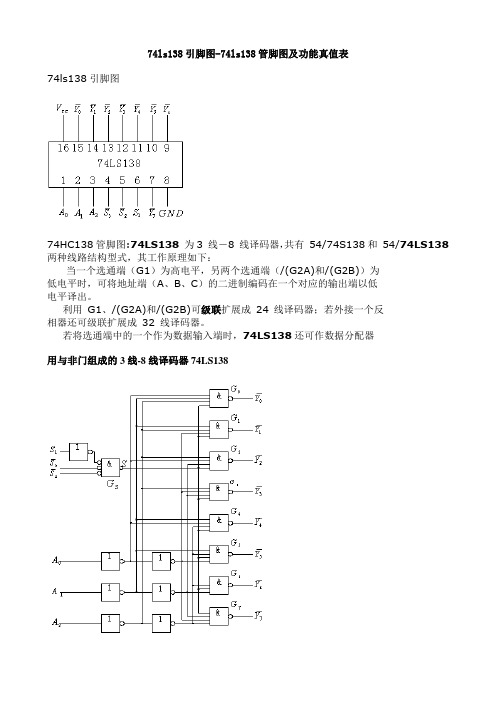

74ls138引脚图-74ls138管脚图及功能真值表74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

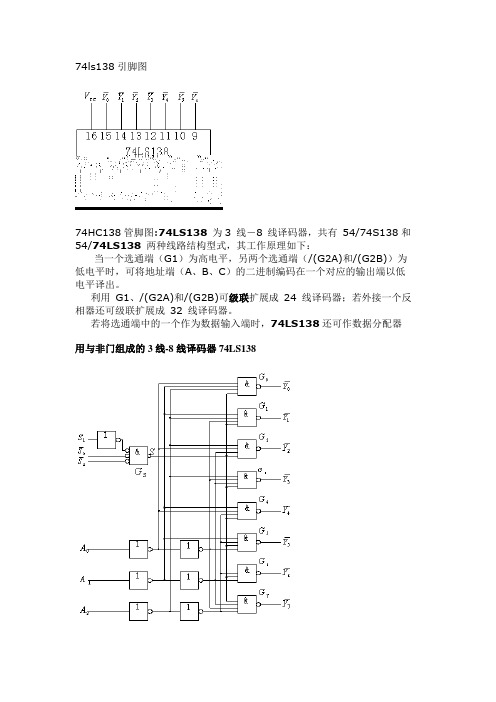

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

74LS138中文资料[1]

![74LS138中文资料[1]](https://img.taocdn.com/s3/m/6ededed2d15abe23482f4d6d.png)

54138/741383线-8线译码器 简要说明: 138为3线-8线译码器,共有54/74S138和54/74LS138两种线路结构型式,其主要电特性的典型值如下:型号T pd (ABC->Y)(3级)P D CT54S138/CT74S1388ns 245mW CT54LS138/CT74LS13822ns32mW当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A 、B 、C )的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24线译码器;若外接一个反相器还可级联扩展成32线译码器。

若将选通端中的一个作为数据输入端时,138还可作数据分配器。

管脚图:引出端符号: A、B、C 译码地址输入端 G1 选通端 /(G2A)、/(G2B) 选通端(低电平有效) Y0~Y7 译码输出端(低电平有效)功能表:ww w.t a i -ya n.c o m/b b s/G2*=G2A+G2B H=高电平 L=低电平 X=任意 极限值 电源电压------------------------------------------------7V 输入电压54/74S138----------------------------------------5.5V 54/74LS138---------------------------------------7V 工作环境温度 54×××------------------------------ -55~125℃ 74×××------------------------------------0~70℃ 贮存温度-------------------------------------- -65~150℃推荐工作条件:CT54S138/CT74S138CT54LS138/CT74LS138最小额定最大最小额定最大单位 544.5 5 5.54.5 5 5.5电源电压Vcc744.75 5 5.254.75 5 5.25 V输入高电平电压V IH 2 2 V 54 0.8 0.7输入低电平电压V IL 740.8 0.8V输出高电平电流I OH -1000 -400 µA 54 20 4输出低电平电流I OL74208mA逻辑图ww w.t a i -ya n.c o m/b b s静态特性(T A 为工作环境温度范围)`S138 `LS138 参数 测试条件【1】 最小最大最小最大 单位 VIK 输入钳位电压Vcc 最小 IIK=-12mA-1.2 -1.5 V 54 2.52.5VOH 输出高电平电压 Vcc=最小,VIH=2V,VIL=最大,IOH=最大 74 2.7 2.7 V54 0.50.4 VOL 输出低电平电压 VCC=最小,VIH=2V,VIL=最大,IOL=最大 740.50.5 VVI=5.5V 1II 最大输入电压时输入电流 Vcc=5VVI=7V0.1 mA IH 输入高电平电流Vcc=5V,VIH=2.7V 50 20 μA VI=5.5V 1II 最大输入电压时输入电流 Vcc=最大VI=7V0.1 mA IIH 输入高电平电流 Vcc=最大 VIH=2.7V50 20 μA VIL=0.4V -0.4 VIL 输入低电平电流 Vcc=最大VIL=0.5V-2 mA 54-40 -100-6 -40 IOS 输出短路电流Vcc=最大 74-40-100-5 -42 mA Icc 电源电流Vcc=最大7410mA【1】:测试条件中的“最大”和“最小”用推荐工作条件中的相应值。

三位二进制译码器-74LS138

H H H H L H H H H H H

H H H H H L H H H H H

H H H H H H L H H H H

H H H H H H H L H H H

H H H H H H H H L H H

H H H H H H H H H L H

H H H H H H H H H H L

3. 逻辑符号

D1

输

D2 D3 D4 D5

出

D6 D7

使能端 的作用

G1 G 2 A G2 B

× × L H H H H H H H H H × × L L L L L L L L × H × L L L L L L L L

译码 功能

× × × × × × L L L L L H L H H L H L H H H H

&

G=G 1⋅G 2A⋅ G 2B

3线/8线译码器

G 2B

输入 缓冲门

1 1

1 1

1 1

B2 B1 B0

1

G1 G 2A

3功能表

74LS138 的功能表

输 入 B2 B1 B0 D0 × × × L H L H L H L H H H H L H H H H H H H

三位二进制译码器—74LS138

——常用中规模集成译码电路 1. 内部结构 2. 功能表 3. 逻辑符号 4. 扩展 5. 应用—实现逻辑函数 6.管脚排列

1. 74LS138最小项译码器的电路结构

D7 D6 D5 D4 D3 D2 D1 D0

Di = G ⋅ mi

&

&

&

&

&

&

译码器引脚图

74LS138译码器引脚图,逻辑图及功能表74LS138与74HC的引脚图用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出功能介绍:就是38译码器,是TTL系列的,也就是74系列。

有三个输入端A0,A1,A2,其中A2是高位,输出是八个低电平输出Y0 ~ Y7,工作电压一般的5V就可以了,举个例子,你A0,A1,A2依次输入000,输出就是Y0,输入依次是001,输出就是Y1。

74ls381引脚图集成算术/逻辑运算单元(ALU)能够完成一系列算术运算和逻辑运算。

在这里我们介绍一种常用的集成算术/逻辑运算单元74LS381,它是四位算术/逻辑运算单元,管脚图如图3.3所示,A和B是预定的输入状态,根据输入信号S2~S0选择八种不同的功能。

图3.3 74LS381集成算术/逻辑运算单元(a)符号图(b)引脚图下面我们可以通过74LS381的功能表了解其功能。

表3.3 74LS381功能表由表3.3可知,74LS381能够进行六种算术和逻辑运算,并有清零和预置功能。

所谓清零是将各数据输出端的状态全为0;预置是使数据输出端输出预定的状态,进行预置操作时,预定的状态从A和B端输入.74ls00,74ls08引脚图[日期:2009-01-01 ] [来源:net 作者:佚名] [字体:大中小] (投递新闻)74ls00 是常用的2输入四与非门集成电路,他的作用很简单顾名思义就是实现一个与非门。

Vcc 4B 4A 4Y 3B 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐__ │14 13 12 11 10 9 8│Y = AB )│2输入四正与非门74LS00 │1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1B 1Y 2A 2B 2Y GND<74LS00引脚图>74LS00真值表:A=1 B=1 Y=0A=0 B=1 Y=1A=1 B=0 Y=1A=0 B=0 Y=1Vcc 4B 4A 4Y 3B 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐__ │14 13 12 11 10 9 8│Y = AB )│2输入四正与非门74LS00 │1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1B 1Y 2A 2B 2Y GND<74LS08引脚图>是常用的2输入四正与门电路74LS08真值表:a b y0 0 00 1 01 0 01 1 1基本RS触发器原理基本RS触发器原理1 基本RS触发器的工作原理基本RS触发器的电路如图1(a)所示。

实验4组合逻辑器件的应用(I)-译码器及其应用—74LS138、74LS148

数字电子技术实验

实验4 组合逻辑器件的应用(I)译码器及其应用—74LS138、74LS148

电工电子实验中心模电实验室

2009年10月

主要内容 1、实验目的 2、实验原理 3、实验设备与器件 4、实验内容及步骤 5、实验报告要求

1 实验目的

1 实验目的

掌握集成译码器的逻辑功能和使用方法;

2 实验原理

编码、译码、显示

编码、译码、显示电路原理

3 实验设备与器件

3 实验设备与器件

KHM-2B型模拟实验装置

4 实验内容及步 骤

4 实验内容及步骤

实验项目

74LS138译码器逻辑功能测试; 用74LS138构成时序脉冲分配器; *用两片74LS138构成一个4-16线译码器(两组结合); 74LS148优先编码器的逻辑功能测试。 数码显示小实验。

74ls138译码器引脚图和逻辑符号74ls138译码器引脚图和逻辑符号2实验原理变量译码器二进制译码器74ls1382实验原理变量译码器二进制译码器74ls13874ls138集成译码器逻辑图内部结构74ls138集成译码器逻辑图内部结构01270123012601220125012101240120aaayaaayaaayaaayaaayaaayaaayaaay真值表真值表在同一个时间是三个输入变量的全部最小项的译码输出的全部最小项的译码输出在同一个时间是三个输入变量2实验原理74ls138作为数据分配器2实验原理74ls138作为数据分配器如图问译码器各输出端的情况可以用示波器观察输入输出信号的波形情况可以用示波器观察输入输出信号的波形情况如图问译码器各输出端的情况2实验原理74ls138实现逻辑函数2实验原理74ls138实现逻辑函数0127a0a12c3012601220125012101240120aabcaacyaaabyaaayaaayaaayaaayaaayaaayba7210yyyyabccbacbacbacbzabccbacbacbaz2实验原理74ls138组合416译码器2实验原理74ls138组合416译码器如图问第一片和第二片分别负责哪些状态如图问第一片和第二片分别负责哪些状态2实验原理83线优先编码器74ls1482实验原理83线优先编码器74ls14874ls148的逻辑图和引脚图74ls148的逻辑图和引脚图真值表真值表2实验原理数码显示译码器2实验原理数码显示译码器led数码管led数码管a共阴b共阳a共阴b共阳2实验原理数码显示译码器2实验原理数码显示译码器bcd码七段译码驱动器bcd码七段译码驱动器引脚图引脚图2实验原理编码译码显示2实验原理编码译码显示编码译码显示电路原理编码译码显示电路原理333实验设备与器件khm2b型模拟实验装置3实验设备与器件khm2b型模拟实验装置444实验内容及步骤实验项目4实验内容及步骤实验项目74ls138译码器逻辑功能测试用74ls138构成时序脉冲分配器用两片74ls138构成一个416线译码器两组结合74ls148优先编码器的逻辑功能测试

74LS138中文资料P.pdf

74LS138中文资料54LS138和74LS138 为3 线-8 线译码器共有54LS138 和74LS138 两种型式,其主要电特性的典型值如下:54LS138 /74LS138 传播延迟时间22ns 功耗32mW原理:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,138 还可作数据分配器。

图1 引脚图图2 内部逻辑管脚图引脚功能:A、B、C 译码地址输入端G1 选通端/(G2A)、/(G2B) 选通端(低电平有效)Y0~Y7 译码输出端(低电平有效)真值表:建议操作条件:电气参数:符号参数测试条件最大值典型值最大值单位VI 输入钳位电压VCC = Min, II = -18 mA- - -1.5 VVOH 输出高电平电压VCC = Min, IOH = Max,VIL = Max, VIH = Min2.73.4 - VVOL 输出低电平电压VCC = Min, IOL = Max,VIL = Max, VIH = Min- 0.35 0.5V IOL = 4 mA, VCC = Min - 0.25 0.4II 最大输入电压时输入电流VCC = Max, VI = 7V - - 0.1 mAIIH 输入高电平电流VCC = Max, VI = 2.7V - - 20 mA IIL 输入低电平电流VCC = Max, VI = 0.4V - - -0.36 mA IOS 输出短路电流VCC = Max (Note 4) -20 - -100 mA ICC 电源电流VCC = Max (Note 5) - 6.3 10 mA 动态特性表:符号参数To (Output) 时滞RL = 2 kW单位CL = 15pF CL = 50 pF最大值最大值最大值最大值tPLH 低到高电平输出传递延迟时间Select to Output 2 - 18 - 27 nstPHL 高到低电平输出传递延迟时间Select to Output 2 - 27 - 40 nstPLH 低到高电平输出传递延迟时间Select to Output 3 - 18 - 27 nstPHL 高到低电平输出传递延迟时间Select to Output 3 - 27 - 40 nstPLH 低到高电平输出传递延迟时间Enable to Output 2 - 18 - 27 nstPHL 高到低电平输出传递延迟时间Enable to Output 2 - 24 - 40 nstPLH 低到高电平输出传递延迟时间Enable to Output 3 - 18 - 27 nstPHL 传递延迟时间Enable to Output 3 - 28 - 40 ns。

电子线路设计-74LS138译码器的介绍

图 3线-8线译码器逻辑图与引脚图

74LS138的功能表

输入

输出

G1

G2A

G2A

c

B

A

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

X

1

1

X

X

X

1

1

1

1

1

1

1

1

0

X

X

X

X

X

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

1

1

1

1

0

0

1

1

0

1

1

1

1

1

1

1

0

0

0

1

0

1

1

0

1

1

1

1

1

1

0

是CC4514译码输出为高电平有效,而CC4515译码输出为低电平有效。

74LS138译码器的识别与检测

1、识别

2、检测

Thanks

0

0

1

1

1

1

1

0

1

1

1

1

1

0

0

1

0

0

1

1

1

1

0

1

1

1

1

0

0

1

0

1

1

1

1

1

1

0

1

1

1

0

0

74LS138管脚功能的主要 介绍

74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

74ls138引脚图

74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:

当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为

低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低

电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反

相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器

用与非门组成的3线-8线译码器74LS138

3线-8线译码器74LS138的功能表

无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出

由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

解:由图3.3.8可见,74LS138仅有3个地址输入端。

如果想对4位二进制代码,只能利用一个附加控制端(当中的一个)作为第四个地址输入端。

取第(1)片74LS138的和作为它的第四个地址输入端(同时令),取第(2)片的作为它的第四个地址输入端(同时令),取两片的、、,并将第(1)片的和接至,将第(2)片的接至,如图3.3.9所示,于是得到两片74LS138的输出分别为

图3.3.9 用两片74LS138接成的4线-16线译码器

式(3.3.8)表明时第(1)片74LS138工作而第(2)片74LS138禁止,将的0000~0111这8个代码译成8个低电平信号。

而式(3.3.9)表明时,第(2)片74LS138工作,第(1)片74LS138禁止,将的1000~1111这8个代码译成8个低电平信号。

这样就用两个3线-8线译码器扩展成一个4线-16线的译码器了。

同理,也可一用两个带控制端的4线-16线译码器接成一个5线-32线译码器。

例2.74LS138 3-8译码器的各输入端的连接情况及第六脚()输入信号A的波形如下图所示。

试画出八个输出引脚的波形。

解:由74LS138的功能表知,当(A为低电平段)译码器不工作,8个输出引脚全为高电平,当(A为高电平段)译码器处于工作状态。

因所以其余7个引脚输出全为高电平,因此可知,在输入信号A的作用下,8个输出引脚的波形如下:

即与A反相;

其余各引脚的输出恒等于1(高电平)与A的波形无关。