2012年数字逻辑期末复习题

2012-2013-2《数字逻辑设计及应用》期末考试题-A参考解答

电子科技大学2012 -2013学年第二学期期末考试 A 卷课程名称:_数字逻辑设计及应用__ 考试形式:闭卷考试日期:20 13 年07 月05 日考试时长:_120___分钟课程成绩构成:平时30 %,期中30 %,实验0 %,期末40 %本试卷试题由___七__部分构成,共__7___页。

I. Fill out your answers in the blanks (3’ X 10=30’)1. If a 74x138 binary decoder has 110 on its inputs CBA, the active LOW output Y5 should be ( 1 or high ).2. If the next state of the unused states are marked as “don’t-cares” when designing a finite state machine, this approach is called minimal ( cost ) approach.3.The RCO_L of 4-bit counter 74x169 is ( 0 or low ) when counting to 0000 in decreasing order.4. To design a "001010" serial sequence generator by shift registers, the shift register should need ( 4 ) bit at least.5. One state transition equation is Q*=JQ’+K’Q. If we use T flip-flop with enable to complete the equation,the enable input of T flip-flop should have the function EN=( JQ’+KQ ).6. A 4-bit Binary counter can have ( 16 ) normal states at most, 4-bit Johnson counter with no self-correction can have ( 8 ) normal states, 4-bit linear feedback shift-register (LFSR) counter with self-correction can have ( 16 ) normal states.7. If we use a ROM, whose capacity is 16 × 4 bits, to construct a 4-bit binary code to gray code converter, when the address inputs are 1001, ( 1101 ) will be the output.8. When the input is 10000000 of an 8 bit DAC, the corresponding output voltage is 2V. The output voltage is ( 3.98 ) V when the input is 11111111.II. Please select the only one correct answer in the following questions.(2’ X 5=10’)1. If a 74x85 magnitude comparator has ALTBIN=1, AGTBIN=0, AEQBIN=0, A3A2A1A0=1101, B3B2B1B0=0111 on its inputs, the outputs are ( D ).A) ALTBOUT=0, AEQBOUT=0, AGTBOUT=0 B) ALTBOUT=1, AEQBOUT=0, AGTBOUT=0C) ALTBOUT=1, AEQBOUT=0, AGTBOUT=1 D) ALTBOUT=0, AEQBOUT=0, AGTBOUT=12. As shown in Figure 1, what would the outputs of the 4-bit adder 74x283 be ( B ) when A3A2A1A0=0100, B3B2B1B0=1110 and S/A=1.A) C4=1, S3S2S1S0=0010 B) C4=0, S3S2S1S0=0110 C) C4=0, S3S2S1S0=1010D) C4=0, S3S2S1S0=1110Figure 13. Which of the following statements is INCORRECT? ( A )A) A D latch is edge triggered and it will follow the input as long as the control input C isactive low.B) A D flip flop is edge triggered and its output will not change until the edge of thecontrolling CLK signal.C) An S-R latch may go into metastable state if both S and R are changing from 11 to 00simultaneously.D) The pulse applying to any input of an S -R latch must meet the minimum pulse width requirement.4. The capacity of a memory that has 13 bits address bus and can store 8 bits at each address is ( B ).A) 8192 B) 65536 C) 104 D) 2565. Which state in Figure 2 is NOT ambiguous ( C ).A) A B) B C) C and D D) CABCD WX W+Y ZZ ’X ’+YYZ1X ’Z ’Figure 2III. Analyze the sequential-circuit as shown in Figure 3, D Flip-Flop with asynchronouspreset and clear inputs. [15’]1.Write out the excitation equations, transition equations and output equation. [5’]2.Assume the initial state Q 2Q 1=00, complete the timing diagram for Q 2 ,Q 1 and Z. [10’]Figure 3参考答案:激励方程: D 1=Q 2/,D 2= Q 1转移方程:Q 1 *= D 1=Q 2/,Q 2 *=D 2= Q 1 输出方程:Z= (CLK+Q 2)/参考评分标准:1. 5个方程正确得5分;每错一个扣1分,扣完5分为止;2. Q 1、Q 2、Z 的波形边沿判断正确,得3分,错一个,扣1分,扣完3分为止;每个上升沿和下降沿各0.5分,错1处扣0.5分,扣完7分为止。

《数字逻辑》期末考试A卷参考答案

《数字逻辑》期末考试 A 卷参考答案、判断题:下面描述正确的打’/,错误的打‘X’(每小题1分,共10 分)1、为了表示104个信息,需7位二进制编码[V ]2、BCD码能表示0至15之间的任意整数[X ]3、余3码是有权码[X ]4、2421码是无权码[X ]5、二值数字逻辑中变量只能取值6、计算机主机与鼠标是并行通信7、计算机主机与键盘是串行通信8、占空比等于脉冲宽度除于周期0和1,且表示数的大小[X ][X ][V ][V ]9、上升时间和下降时间越长,器件速度越慢[V ]10、卡诺图可用来化简任意个变量的逻辑表达式[X ]、写出图中电路的逻辑函数表达式。

(每小题5分,共10分)1、F=A B2、F= AB CD2分,共20分)1、在图示电路中.能实现逻辑功能F = ATH 的电路是 A °TTL 电路(A) F = ABCD(B) F = AH ・ CD -(C) F= A + B + C + D(D) F = A + B • C + D (E) F= A BCD4 . 己知F 二ABC + CD ■可以肯定使F = 0的情况是 _°(A) A=0, BC= 1; (B) B= 1 , C= 1 } (C) AB= 1, CD=Q.(D) BC= 1 , D= 15、逻辑函数A B+BCD+A C+ B C 可化简为A,B,C,D 。

(A) AB + AC + BC (B) AB + C (A4-B)(C) AB + CABA — O ?=11 QA |— I1 F •-&1 Q AB L Il —(B)悬0----空。

—A — &Bo —Co- &BA3 •满足如图所示电路的输岀函数F 的表达式为丄3B 1 o — VOF(D) AB +C (E) 19.图示电路中,当各触发器的状态为C 时.再输入一个CP 脉冲,融发器的 状态为QiQ 严0 0。

2012年数字逻辑复习题

2012数字逻辑复习提要一、选择题1.若ABCDEFGH 为最小项,则它有逻辑相邻项个数为( A )A. 8B. 82C. 28D. 162.如果编码0100表示十进制数4,则此码不可能是(B )A. 8421BCD 码B. 5211BCD 码C. 2421BCD 码D. 余3循环码3.构成移位寄存器不能采用的触发器为( D )A. R-S 型B. J-K 型C. 主从型D. 同步型5.以下PLD 中,与、或阵列均可编程的是(C )器件。

A. PROMB. PALC. PLAD. GAL6.函数F(A,B,C,D)=∑m(1,3,4,6,8,10),它的卡诺图如右图所示。

函数的最简与或表达式F= A 。

A . B . C .D . 7.组合电路是指 B 组合而成的电路。

A .触发器 B .门电路 C .计数器 D .寄存器8.电路如右图所示,经CP 脉冲作用后,欲使Q n+1=Q ,则A ,B 输入应为 AB 。

A .A=0,B=0 B .A=1,B=1C .A=0,B=1D .A=1,B=09.一位十进制计数器至少需要 4个触发器。

A .3B .4C .5D .10DB A D B A D B A ++DB A DC A C B A ++D C A D B A C B A ++DB A D B A D B A ++10.n 个触发器构成的扭环计数器中,无效状态有 D 个。

A .n B .2n C .2n-1 D .2n -2n11.GAL 器件的与阵列 ,或阵列 D 。

A .固定,可编程B .可编程,可编程C .固定,固定D .可编程,固定12.下列器件中是 C 现场片。

A .触发器B .计数器C .EPROMD .加法器13.IspLSI 器件中,缩写字母GLB 是指 B 。

A . 全局布线区B .通用逻辑块C .输出布线区D .I/O 单元14. 在下列逻辑部件中,不属于组合逻辑部件的是D 。

数字逻辑期末复习题汇总

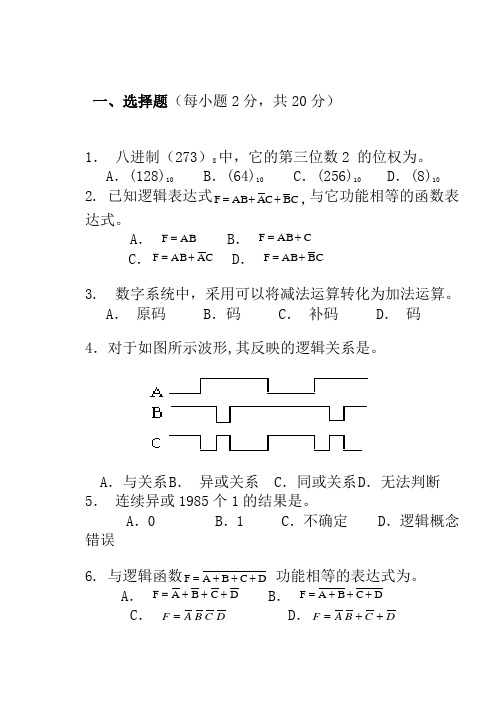

一、选择题(每小题2分,共20分)1. 八进制(273)8中,它的第三位数2 的位权为。

A .(128)10B .(64)10C .(256)10D .(8)102. 已知逻辑表达式C B CA AB F ++=,与它功能相等的函数表达式。

A .AB F = B .C AB F +=C .C A AB F +=D .C B AB F +=3. 数字系统中,采用可以将减法运算转化为加法运算。

A . 原码B .码C . 补码D . 码4.对于如图所示波形,其反映的逻辑关系是。

A .与关系B . 异或关系C .同或关系D .无法判断 5. 连续异或1985个1的结果是。

A .0B .1C .不确定D .逻辑概念错误6. 与逻辑函数D C B A F +++= 功能相等的表达式为。

A . D C B A F +++= B .D C B A F +++=C .D C B A F = D .D C B A F ++=7.下列所给三态门中,能实现0时,AB ;1时,F 为高阻态的逻辑功能的是。

8. 如图所示电路,若输入脉冲的频率为100,则输出Q 的频率为。

A . 500B .200C . 100D .509.下列器件中,属于时序部件的是。

A . 计数器B . 译码器C . 加法器D .多路选择器10.下图是共阴极七段数码管显示译码器框图,若要显示字符“5”,则译码器输出a~g应为。

A. 0100100 B.1100011 C. 1011011 D.0011011二、填空题(每小题2分,共20分)11电路的电源是5,高电平1对应的电压范围是2.4-5。

12个输入端的二进制译码器,共有N2个输出端。

对于每一组输入代码,有1个输出端是有效电平。

13.给36个字符编码,至少需要6位二进制数。

14.存储12位二进制信息需要12个触发器。

15.按逻辑功能分类,触发器可分为、、、等四种类型。

16.对于D触发器,若现态 0,要使次态1=0,则输入0。

数字逻辑期末复习题

数字逻辑期末复习题⼀、选择题(每⼩题2分,共20分)1.⼋进制(273)8中,它的第三位数2 的位权为___B___。

A .(128)10B .(64)10C .(256)10D .(8)102. 已知逻辑表达式C BC A AB F ++=,与它功能相等的函数表达式_____B____。

A .AB F = B .C AB F +=C .C A AB F +=D .C B AB F +=3. 数字系统中,采⽤____C____可以将减法运算转化为加法运算。

A .原码B .ASCII 码C .补码D . BCD 码4.对于如图所⽰波形,其反映的逻辑关系是___B_____。

A .与关系B .异或关系C .同或关系D .⽆法判断 5.连续异或1985个1的结果是____B_____。

A .0B .1C .不确定D .逻辑概念错误6. 与逻辑函数D C B A F +++= 功能相等的表达式为___C_____。

A . D C B A F +++= B . D C B A F +++=C .D C B A F = D .D C B A F ++=7.下列所给三态门中,能实现C=0时,F=AB ;C=1时,F 为⾼阻态的逻8. 如图所⽰电路,若输⼊CP 脉冲的频率为100KHZ ,则输出Q 的频率为_____D_____。

A . 500KHzB .200KHzC . 100KHzD .50KHz9.下列器件中,属于时序部件的是_____A_____。

A .计数器B .译码器C .加法器D .多路选择器 10.下图是共阴极七段LED 数码管显⽰译码器框图,若要显⽰字符“5”,则译码器输出a ~g 应为____C______。

A . 0100100B .1100011C . 1011011D .0011011⼆、填空题(每⼩题2分,共20分)11.TTL 电路的电源是__5__V ,⾼电平1对应的电压范围是__2.4-5____V 。

(完整word版)数字逻辑和设计基础-期末复习题

1.采用3-8线译码器74LS138和门电路构成的逻辑电路如图所示, 请对该电路进行分析, 写出输出方程, 并化解为最简与-或式。

(10分)1.解: 分析此图, 可知: F1= ,F2=4567m m m m +++ 化简过程: 由卡诺图及公式化简均可, 此处略 化简得: (2分)2F A =2.已知逻辑函数: , 试用一片4选1数据选择器和门电路实现该逻辑函数, 要求采用代数法, 写出设计全过程, 并画出电路图。

(10分)A 1ST YD 0D 1D 2D 3A 0① 写出逻辑函数F 的表达式(2分)==F A B C AB C ABC A BC ABCA B C AB C C A BC ABCA B C AB A BC ABC=+++++++++++()② 写出4选1数据选择器输出端逻辑函数Y 的表达式(2分)100101102103Y A A D A A D A A D A A D =+++③令 , 比较 和 两式可得: (2分)01231D C D D D C ====④ 根据上式画出的逻辑图。

(4分)五、 画出下列各触发器Q 端的波形: (设Q = 0)(10 分, 每小题5 分) 1、已知JK 触发器输入信号J 和K 、时钟脉冲CP 、异步置位端 和 的波形如下图所示, 试画出触发器输出端Q 的波形, 设初始状态为0。

(5分)QCPJS S DR DK J2.下图由边沿D 触发器构成的触发器电路, 设其初始状态为0。

输入信号如右图所示, 试画出Q 端的输出波形。

(5分)CP QD R D R六、 小规模时序逻辑电路设计(15分)1.分析下图所示电路。

(15分)要求: 1)、写出驱动方程、状态方程、输出方程;2)、列出状态转换真值表, 画出状态转换图; 3)、说明电路的逻辑功能及启动特性。

Y解: 1.写方程式10202110102012121 Y=n n n n n n n nn n n D Q Q Q D Q Q Q Q Q D Q Q Q +++⎧⎧==⎪⎪⎪⎪==⎨⎨⎪⎪==⎪⎪⎩⎩驱动方程状态方程输出方程2.列状态转换真值表CP 脉冲序列2nQ 1nQ 0nQ +10n Q +11n Q +12n Q 000000112345001011011111111110110100100000001101111Y00010001无效状态3.画状态转换图电路为同步模6计数器, 不能自启动74LS161采用置数法实现十进制计数器的逻辑图。

《数字逻辑》——期末复习题及答案

《数字逻辑》——期末复习题及答案中国⽯油⼤学(北京)远程教育学院《数字逻辑》期末复习题⼀、单项选择题1. TTL 门电路输⼊端悬空时,应视为( )A. ⾼电平B. 低电平C. 不定D. ⾼阻2. 最⼩项D C B A 的逻辑相邻项是()A .ABCDB .D BC A C .CD AB D .BCD A3. 全加器中向⾼位的进位1+i C 为( )A. i i i C B A ⊕⊕B.i i i i i C B A B A )(⊕+C.i i i C B A ++D.i i i B C A )(⊕4. ⼀⽚⼗六选⼀数据选择器,它应有()位地址输⼊变量A. 4B. 5C. 10D. 165. 欲对78个信息以⼆进制代码表⽰,则最少需要()位⼆进制码A. 4B. 7C. 78D. 106. ⼗进制数25⽤8421BCD 码表⽰为()A.10 101B.0010 0101C.100101D.101017. 常⽤的BCD 码有()A:奇偶校验码 B:格雷码 C:8421码 D:ASCII 码8. 已知Y A AB AB =++,下列结果中正确的是()A:Y=A B:Y=B C:Y=A+B D: Y A B =+9. 下列说法不正确的是()A:同⼀个逻辑函数的不同描述⽅法之间可相互转换B:任何⼀个逻辑函数都可以化成最⼩项之和的标准形式C:具有逻辑相邻性的两个最⼩项都可以合并为⼀项D:任⼀逻辑函数的最简与或式形式是唯⼀的10. 逻辑函数的真值表如下表所⽰,其最简与或式是()A: ABC ABC ABC ++ B: ABC ABC ABC ++ C: BC AB + D: BC AC +11.以下不是逻辑代数重要规则的是( ) 。

A. 代⼊规则B. 反演规则C. 对偶规则D. 加法规则12.已知函数E)D (C B A F +?+=的反函数应该是( ) 。

A. [])E (D C B A F +?+?= B. [])E D (C B A F +?+?= C. [])E (D C B A F +?+?=D. [])E D (C B A F +?+?=13.组合逻辑电路⼀般由()组合⽽成。

(完整word版)数字逻辑期末考试题

数字逻辑考试题数字逻辑考试题(一)一、填空(共17分,每空1分)1。

(1011。

11)B =( ) D =( )H 2. (16)D =( )8421BCD 码。

3。

三态门的输出有 、 、 三种状态。

6。

ABC C B A C AB C B A Y ++=),,( 的最简式为Y= 。

7. 由n 位寄存器组成的扭环型移位寄存器可以构成 进制计数器。

10. 四位环型计数器初始状态是1000,经过5个时钟后状态为 。

11. 在RS 、JK 、T 和D 触发器中, 触发器的逻辑功能最多。

12。

设一个包围圈所包围的方格数目为S ,消去的变量数目为N ,那么S 与N 的关系式应是 。

13. 在卡诺图化简逻辑函数时,圈1求得 的最简与或式,圈0求得 的最简与或式。

二、选择(共10分,每题1分)1。

DE BC A Y +=的反函数为Y =( )。

A 。

E D CB A Y +++⋅= B 。

E DC B A Y +++⋅=C 。

)(ED C B A Y +++⋅= D 。

)(E D C B A Y +++⋅= 3. 十进制数25用8421BCD 码表示为( )。

A 。

10101B 。

0010 0101C 。

100101 D. 101014。

若用1表示高电平,0表示低电平,则是( )。

A 。

正逻辑B 。

负逻辑C 。

正、负逻辑 D. 任意逻辑 5. 下逻辑图的逻辑表达式为( ).A. AC BC AB Y = B 。

BC AC AB Y ++= C. BC AC AB Y ++= D. BC AC AB Y = 6. 三态门的逻辑值正确是指它有( )。

A. 1个B. 2个C 。

3个D. 4个 9。

组合逻辑电路在电路结构上的特点下列不正确的是( )。

A 。

在结构上只能由各种门电路组成B. 电路中不包含记忆(存储)元件C. 有输入到输出的通路 D 。

有输出到输入的反馈回路10. 已知74LS138译码器的输入三个使能端(E 1=1,022==B A E E )时,地址码A 2A 1A 0=011,则输出07~Y Y 为( ).A. 11111101B 。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《数字逻辑》复习题一选择题1.逻辑表达式Y=AB可以用 ( C ) 实现。

A.正或门B.正非门C.正与门D.负或门2.在( A )的情况下,“或非”运算的结果是逻辑 1 。

A.全部输入是0 B.全部输入是1C.任一输入为0,其他输入为1D.任一输入为13.CMOS数字集成电路与TTL数字集成电路相比突出的优点是( A )。

A. 微功耗B. 高速度C. 高抗干扰能力D. 电源范围宽4.在下列逻辑电路中,不是组合逻辑电路的有( D )。

A. 译码器B. 编码器C. 全加器D. 寄存器5.一块数据选择器有三个地址输入端,则它的数据输出端最多应有( D )。

A.3B.6C.7D.86.组合逻辑电路的特点是( B )。

A. 输出与以前输入有关B. 输出只由当时输入决定C. 输出与原来输出有关D.输出由当时和以前输入共同决定7.若在编码器中有90个编码对象,则要求输出二进制代码位数为( C )位。

A.5 B.6 C.7 D.88.数据选择器,某瞬间在选择变量作用下,从多路信号中选出( C )。

A.2路B.全部C.1路D. 4路9.八路数据分配器,其地址输入端有( C )个。

A.1B.2C.3D.4E.810.同步计数器和异步计数器比较,同步计数器的显著优点是( A )。

A.工作速度高B.触发器利用率高C.电路简单D.不受时钟CP控制11.8 位移位寄存器,串行输入时经( D )个脉冲后,8位数码全部移入寄存器中。

A.1B.2C.4D.812.只读存储器ROM中的内容,当电源断掉后又接通,存储器中的内容( D )。

A.全部改变B.全部为0C.不可预料D.保持不变13.基本的逻辑运算是( C )。

A. 异或B.与非C. 与、或、非D. 或非14.格雷码的特点是位置相邻的数码中只有( A )。

A. 一位不同B. 二位不同C. 高位相同,其他全不同D. 各位全不同15.函数F= <!--[if !vml]--><!--[endif]-->的反函数是( A )。

A. <!--[if !vml]--><!--[endif]-->B. <!--[if !vml]--><!--[endif]-->C. <!--[if !vml]--><!--[endif]-->D.<!--[if !vml]--><!--[endif]-->16. 三极管可作为无触点开关用,当它处于截止状态时,相当于开关处于( B )。

A. 闭合状态B. 断开状态C. 时断时开D.先断后开17. 要区分60个数符,至少需( C )位二进制代码。

A.4 B5 C.6 D.719.下列电路中属于组合逻辑电路的是( B )。

A. 同步D触发器B.译码器C. 寄存器D. 计数器20.一个8选1数据选择器的数据输入端有( D )个。

A.1B.2C.4D.821.同步时序电路和异步时序电路比较,其差异在于后者( B )。

A.没有触发器B.没有统一的时钟脉冲控制C.没有稳定状态D.输出只与内部状态有关22.一位8421BCD码计数器至少需要( B )个触发器。

A.3B.4C.5D.1023.只读存储器ROM在运行时具有( A )功能。

A.读/无写B. 无读 /写C.读/写D. 无读 /无写26.四变量的卡诺图,每个小方格最多有( C )相邻小方格。

A.2个B.3个C. 4个D.5个27 .在下列逻辑电路中,不是组合逻辑电路的有( D )。

A. 译码器B. 编码器C. 全加器D. 计数器28.三位二进制编码器的8个输入端<!--[if !vml]--><!--[endif]-->~<!--[if !vml]--><!--[endif]-->中,如果只有<!--[if !vml]--><!--[endif]-->是低电平,其余输入端均为高电平,则其输出状态<!--[if !vml]--><!--[endif]-->( D )。

A.111B.000C.101D.11029.四路数据分配器,其地址输入端有( B )个。

A.1B.2C.3D.4E.830.全加器有(B )个输出端。

A.1B.2C.3D.431.下列逻辑电路中为时序逻辑电路的是( C )。

A.译码器B.加法器 C寄存器 D.数据选择器32.随机存取存储器具有( A )功能。

A.读/写B. 无读 /写C.只读D.只写33 ‘A’、‘0、’和‘a’的ASCII码分别是(A)A . 65 、48 和61HB . 41 、30 和61C . 41H 、30 和61D . 41H 、30H 和61二、判断题(在括号中划√或×,然后填入下表与号对应的框中,否则不计分)1.集电极开路门有高电平、低电平、高阻等状态。

( x )2.若两个函数具有不同的真值表,则两个逻辑函数必然不相等。

(√)3.一般TTL 门电路的输出端可以直接相连,实现线与。

( x )4.组合逻辑电路中产生竞争冒险的主要原因是输入信号受到尖峰干扰。

( x )5.同步时序电路具有统一的时钟 CP 控制。

(√)6.计数器的模是指构成计数器的触发器的个数。

( x )7.三态门的三种状态分别为:高电平、低电平、不高不低的电压。

( x )8.若两个函数具有不同的逻辑函数式,则两个逻辑函数必然不相等。

( x )9.CMOS OD 门(漏极开路门)的输出端可以直接相连,实现线与。

(√)10.用数据选择器可实现时序逻辑电路。

( x )11.编码与译码是互逆的过程。

(√)12.时序电路不含有记忆功能的器件。

( x )13.计数器的核心元件是触发器。

(√)14.若两个函数具有相同的真值表,则两个逻辑函数必然相等。

(√)15.TTL OC门(集电极开路门)的输出端可以直接相连,实现线与。

(√)16.共阴接法的七段显示器,要用有效输出为高电平的显示译码器来驱动。

(√)17.二进制译码器相当于是一个最小项发生器,可以用其实现组合逻辑电路。

(√)18.异步时序电路的各级触发器类型不同。

( x )19.同步二进制计数器的电路比异步二进制计数器复杂,所以实际应用中较少使用同步二进制计数器。

( x )20.TTL电路可直接驱动CMOS电路。

(x)21. CMOS电路可直接驱动TTL电路。

(√)22 一个真值表可能对应多个逻辑函数表达式 (√)23门电路多余输入端的处理方法是:与门的多余端上拉到电源或多并接;或门的多余端接地(√)三、填空题数据转换部分:1.(10110010.1011 )2=( 262.54 )8=( B2.B )16(43)D =(101011)2=(53)8(127)D =(1111111)2=(177)8(254.25)D =(11111110.01)2=(376.2)8(2.718)D =(10.10110111)2=(2.54)8(101001)B =(0010 1011)2=(29)16(11.01101)16=(0011.0110 1000)2=(3.68)16(0111 1000)8421BCD = ( 1001110 )2= ( 78 )10补码部分:1.–81和+81的8位二进制补码分别为: 10101111和 010100012.补码为 00101011和11111100对应的数分别为: 43和-4ASCII码部分:‘A’、‘0、’和‘a’的ASCII码分别是(A)A . 65 、48 和61HB . 41 、30 和61C . 41H 、30 和61D . 41H 、30H 和613.八路数据分配器,其地址输入端有 3 个。

4.触发器有 2 个稳态,存储8位二进制信息要 8 个触发器。

6.一个8选1的数据选择器的数据输入端有____8 个。

7.触发器有 2 个稳态,实现九进制计数器,最少用 4 个触发器。

9.101 键盘的编码器输出 7 位二进制代码。

第七,八章部分1消去竞争冒险的方法有消去互补乘积项、增加乘积项以避免互补项相加、输出端并联电容等2施密特触发器可用于波形变换、波形整形与抗干扰、幅度鉴别等3单稳态电路可应用于定时,延时和消除噪声等4.存储器2716为2K×8位的EPROM,有11 条地址线,有 8 条数据线。

5.存储器2732为4K×8位的EPROM,有 12 条地址线,有 8 条数据线。

6.用2716(2K×8)构成容量为(8K×16)的存储器,需要8 片2716。