阻抗板制作设计指引汇总

PCB阻抗设计参考

前言为保证信号传输质量、降低EMI干扰、通过相关的阻抗测试认证,需要对PCB 关键信号进行阻抗匹配设计。

本设计指南是综合常用计算参数、电视机产品信号特点、PCB Layout实际需求、SI9000软件计算、PCB供应商反馈信息等,而最终得出此推荐设计。

适用于大部分PCB供应商的制程工艺标准和具有阻抗控制要求的PCB板设计。

一、双面板阻抗设计100欧姆差分阻抗推荐设计①、包地设计:线宽、间距 7/5/7 mil地线宽度≥20mil信号与地线距离6mil,每400mil内加接地过孔;②、不包地设计:线宽、间距 10/5/10mil差分对与对之间距离≥20mil(特殊情况不能小于10mil建议整组差分信号线外采用包地屏蔽,差分信号与屏蔽地线距离≥35mil(特殊情况不能小于20mil。

90欧姆差分阻抗推荐设计①、包地设计:线宽、间距 10/5/10mil地线宽度≥20mil信号与地线距离6mil或5mil,每400mil内加接地过孔;②、不包地设计:线宽、间距 16/5/16mil差分对与对之间距离≥20mil建议整组差分信号线外采用包地屏蔽,差分信号与屏蔽地线距离≥35mil(特殊情况不能小于20mil。

要领:优先使用包地设计,走线较短并且有完整地平面可采用不包地设计;计算参数:板材FR-4,板厚1.6mm+/-10%,板材介电常数4.4+/-0.2,铜厚1.0盎司(1.4mil阻焊油厚度 0.6±0.2mil,介电常数 3.5+/-0.3图1 包地设计图2 不包地设计二、四层板阻抗设计100欧姆差分阻抗推荐设计线宽、间距 5/7/5mil差分对与对之间距离≥14mil(3W准则注:建议整组差分信号线外采用包地屏蔽,差分信号与屏蔽地线距离≥35mil(特殊情况不能小于20mil。

90欧姆差分阻抗推荐设计线宽、间距 6/6/6mil差分对与对之间距离≥12mil(3W准则要领:在差分对走线较长情况下,USB的差分线建议两边按6mil的间距包地以降低EMI风险(包地与不包地,线宽线距标准一致。

PCB阻抗设计及计算教程

PCB阻抗设计及计算教程PCB阻抗设计及计算是电路设计与布局中的重要一环,它对于保证电路性能、抑制信号干扰和提高系统稳定性具有至关重要的作用。

本文将介绍PCB阻抗的基本概念,阻抗设计的目标和方法,并详细解释如何进行PCB阻抗计算。

1.基本概念:在PCB设计中,阻抗是指电流或信号在电路板上的传输时遇到的阻碍。

阻抗主要由导线、平面、空气等介质的特性决定。

常见的阻抗有单端阻抗和差分阻抗。

2.阻抗设计的目标:(1)确保信号完整性:通过控制阻抗,避免信号的反射和损耗,确保信号的完整性,避免信号失真以及噪声和串扰的引入。

(2)抑制系统的电磁辐射:通过设计合适的阻抗,减少电流的回流路径,降低系统的电磁辐射水平,提高抗干扰能力。

(3)提高系统的工作稳定性:通过阻抗设计和匹配,使得信号传输更加稳定,避免因阻抗不匹配引起的系统不稳定和故障。

3.阻抗设计的方法:(1)常规PCB布局:根据电路需求和信号速度,尽量避免使用过长过窄的线路,减小阻抗不匹配和信号失真的可能性。

(2)地线的设计:地线是设计阻抗的重要因素之一,它应该尽量宽而平,以减小阻抗,提高地线的传输能力。

(3)控制环境因素:根据设计需求,合理选择PCB板材和层间距,控制介质常数,进而控制阻抗值。

(4)信号层堆叠:通过合理的层次规划和PCB板厚度选择,控制信号层之间的间距和层间介质特性,达到要求的阻抗。

4.PCB阻抗计算:(1)阻抗计算规则:根据线宽、线距和介质常数等参数,可以使用在线计算软件或公式进行阻抗计算。

常用的公式有微带线和线间微带线的计算公式。

(2)使用在线计算软件:目前市面上有许多免费的在线阻抗计算软件,只需输入所需参数即可得到计算结果。

(3)使用电磁仿真软件:对于复杂的PCB设计,可以使用电磁仿真软件进行阻抗计算,如ADS、CST等软件。

仿真软件可以更加准确地计算阻抗,并考虑复杂的环境因素。

总结:PCB阻抗设计及计算是PCB设计中不可忽视的一环,它对电路性能和系统稳定性具有重要影响。

阻抗制作规范操作指引

1、目的:为规范制作阻抗PCB的阻抗计算和阻抗图形设计方法,确保成品的阻抗符合规定,使阻抗制作标准化,简单化。

2、范围:适用于本厂客户要求阻抗控制的PCB阻抗设计及CAM制作的阻抗图形设计。

3、参考文件无4、定义4.1特性阻抗(Characteristic Impedance)当一条导线与大地绝缘后,导线与大地彼此之间的阻抗。

4.2 差分阻抗(Differential Impedance)二条平行导线与大地绝缘后的阻抗,两条导线与大地彼此之间的阻抗。

5、职责5.1 PE工程部:负责客户阻抗资料的确认和设计制作;5.2 PROD生产部:按照操作指示和制作指示进行生产;5.3 QA品保部:阻抗板在制作过程中的品质监控及确认;5.4 ME工艺部:为阻抗板在制作中提供技术支持。

6、作业内容6.1 客户资料确认6.1.1确认客户压合结构可否满足阻抗控制要求。

6.1.2确认阻抗控制范围是否合理,一般情况下公差标准为±10%。

6.1.3阻抗层控制阻抗线粗设计是否合理,无阻抗线层尽量不做阻抗控制,以降低制作难度。

6.1.4评估客户阻抗控制有否特殊要求,厂内能力能否满足客户要求。

6.2阻抗设计基本原则6.2.1抗设计计算采阻抗计算软件进行计算,根据客户阻抗要求,分别输入介电常数、铜厚、线宽、线距、介电层厚度等相关参数,然后根据我司生产能力制作我司生产工作指示(MI),以指导现场生产。

6.2.2压合结构的确认根据客户要求设计压合结构,除客户指定的压合结构外,压合结构设计的一般原则如下: 6.2.1优先选用厚度较大的基板(尺寸稳定性较好);6.2.2优先选用低成本(或低成本组合)PP;备注:对于同种玻璃布型prepreg,树脂含量高低基本不影响价格,pp厚度与价格无必然联系,特殊PP(如2113,2112,3113,1506,106)价格一般较普通PP(7628, 7630,1080,2116)贵30%以上,为节约成本,在保证压合品质的前提下,PP张数尽量少用,尽量避免使用特殊PP。

PCB阻抗设计参考

PCB阻抗设计参考在PCB设计中,阻抗是一个非常重要的参数,尤其对于高频信号传输和数字信号传输。

正确设计PCB阻抗可以确保信号的稳定传输和减少信号衰减。

一般来说,要设计PCB的阻抗,需要考虑以下几个方面:1.材料特性:首先要了解所使用的PCB板材的介电常数和介磁常数。

这些参数会对阻抗产生影响,例如常用FR-4板材的介电常数在4.2~4.5之间。

2.PCB层结构:多层板的设计中,每一层的布线方式会影响阻抗。

通过选择合适的层次安排来控制阻抗。

两层板可以使用不同的宽度和间距的微带线或者分界线以控制阻抗,而对于多层板可以考虑使用阵列线、共面线、差分线等方式控制阻抗。

3. 线宽和间距的选择:根据所需的阻抗值和PCB的板厚,可以通过一些公式来选择合适的线宽和间距。

常用的公式有美国电气工程协会(IEEE)和Roger Ghirardi等提出的公式。

4.主要参数计算:对于常用的阻抗控制线如微带线、分界线和差分线,可以根据它们的几何特性和材料参数计算出所需的阻抗。

例如对于一条微带线,阻抗可以根据线宽、线距、介电常数等参数,使用公式计算得出。

5.仿真工具:使用仿真工具对阻抗进行验证也是一种常用的方法。

通过在仿真软件中建立PCB的模型,可以模拟信号在PCB中的传输情况,从而验证设计所得阻抗的准确性。

6.实际布局:在进行实际布局时,要确保实际线宽和间距与设计要求相符。

可以使用追踪宽度测量工具来检查PCB上的线宽,并使用追踪间距工具来检查线间距。

此外,还要注意信号线和地线的排列,以尽可能减小信号线的距离地线的距离。

通过合理的PCB阻抗设计,可以使得信号在PCB上得到稳定传输,减少信号衰减,提高系统的性能和可靠性。

(注:此回答基于2024年的知识,并不包括当前最新的技术和趋势,如有需要请参考最新资料和指导。

阻抗板工程设计规范

1.0 工程设计阻抗值应保证在阻抗要求值的+/-5%之内,不在公差范围之内的均不合格。

2.0阻抗板最终测试合格标准:

2.0.1阻抗要求值50以下,则其允许公差为+/-5欧姆;

2.0.2阻抗要求值50以上,则其允许公差为+/-10%;

3.0.1 不在公差范围之内的均判定为不合格;

3.0.2阻抗设计合格标准+/-5%。

4.0.制作程序:

4.0.1 计算阻抗时,对参数调整的顺序:优先调整介质厚度,其次线宽/间距。

介质厚度调整2mil

以内可不与客户确认,阻抗线调整0.5mil可不用确认;

5.0 规范内容:

5.1阻抗设计相关参数:

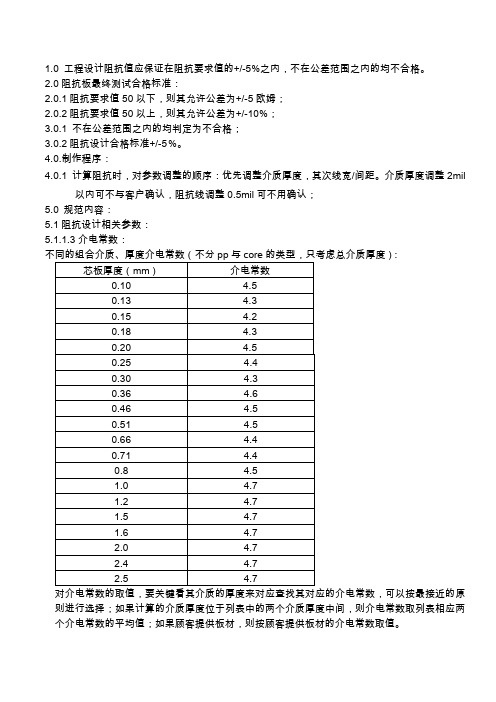

5.1.1.3介电常数:

:

对介电常数的取值,要关键看其介质的厚度来对应查找其对应的介电常数,可以按最接近的原则进行选择;如果计算的介质厚度位于列表中的两个介质厚度中间,则介电常数取列表相应两个介电常数的平均值;如果顾客提供板材,则按顾客提供板材的介电常数取值。

5.1.2线宽/线距

常规下侧蚀因子在2.0-2.5左右。

为了方便计算,在常规板制作计算时,使用计算线宽如下表:(对于非常规铜厚时则需要参考侧蚀因子进行计算及与工艺人员进行确认)。

使用计算间距(S)为顾客设计间距。

=顾客设计线宽)

(注:W

5.1.3铜厚

常规下,内层基铜厚为1OZ、0.5OZ、2OZ,外层基铜铜厚为HOZ、1OZ、2OZ。

常规情况下内层的基铜厚就是其成品的计算厚度。

以上仅供参考。

PCB阻抗设计指南

PCB阻抗设计指南PCB阻抗设计指南是用于帮助工程师在设计印刷电路板(PCB)时确保正确匹配信号和传输线的阻抗的一系列准则和建议。

阻抗匹配是指通过选择适当的线宽、距离和材料来确保信号在传输线上的传输中不发生反射和损耗,并最大程度地减少信号的衰减和失真。

以下是一些PCB阻抗设计指南:1.选择合适的材料:PCB的材料参数,例如介电常数和损耗因子,对于阻抗匹配至关重要。

选择低损耗的材料和符合要求的介电常数,可以降低信号的衰减和失真。

2.线宽和距离的计算:阻抗的大小与传输线的几何形状密切相关。

根据所选材料的介电常数和期望的阻抗值,可以使用PCB设计软件或在线阻抗计算器来计算适当的线宽和距离。

这些计算应该考虑到信号层和地平面层之间的间隔以及相邻信号层之间的层间解耦电容。

3.保持对称性:为了避免信号的不对称性引起的互相干扰和失真,应该尽量保持PCB中信号层和地平层之间的对称性。

这意味着在布局和布线时,相邻信号层之间的线的宽度和间距应保持一致。

4.地平面设计:地平面起到混合信号的屏蔽作用,对于信号的保护和防止互相干扰非常重要。

在PCB设计中,应该尽量使用连续的地平面和分割地平面来避免信号层之间的串扰。

5.差分信号和单端信号的阻抗匹配:在设计高速差分信号传输线时,应该注意差分对之间的阻抗匹配,以避免信号的共模噪声和失真。

单端信号线也需要进行阻抗匹配,以保证信号的完整性。

6.穿越电流和返回路径:穿越电流是指信号从一个地方流到另一个地方的路径。

为了减少穿越电流引起的互相干扰和电磁辐射,应该通过正确的布局和布线来确保返回路径尽可能接近信号路径,并确保良好的地引和供电。

7.强调阻抗控制的重要性:在PCB设计中,阻抗控制对于高速信号传输和减少信号衰减、失真至关重要。

设计师应该明确了解所需阻抗值,并确保在整个设计过程中始终监测和验证阻抗。

总结起来,PCB阻抗设计指南是建议工程师在设计印刷电路板时遵循的一系列准则。

通过合适的材料选择,准确的线宽和距离计算,保持对称性和良好的地平面设计,差分信号和单端信号的阻抗匹配,以及正确的穿越电流和返回路径控制,可以有效地确保信号的完整性和传输质量。

PCB特性阻抗设计指导

PCB特性阻抗设计指导电路板的高频阻抗控制,对于许多客户而言应不陌生,但就特性阻抗是如何设计而来或者特性阻抗在线路设计时有何限制,甚至高频特性阻抗传输线又应设计多长才能达到,最好的传输匹配环境,等多方面的问题,这里就电子学的领域出发解析影响高频特性阻抗品质。

〝谐振 resonance 〞所谓的谐振意指可发生于任一物理系统中只要该系统具有相对形式之贮能零件,当贮存于这些零件中之能量作相互交换时,就不需再自能源取得额外之能量,而将有谐振存在。

我们都知道,当驾驶一前轮不平衡之车辆时,在某些特定速率下不平衡的轮子之振动率等于前端悬吊者之自然谐振频率,则存在在一系统中之弹箕及质量中之能量,可彼此互作交换,导致一大的振动及方向盘之移动,这些情形司机常见到。

在本文中,我们将讨论在电路中之谐振特性及一些应用,电路中之谐振要求电抗量必须能互相抵消,在一串联 RLC电路中,此需电抗性电压降抵消,在一并联RLC电路中,则需电抗性电流互相抵消。

一串联电路的阻抗为电阻值及电抗值之向量和,在一串联RLC电路中,将有一频率,在该频率下,可使其电感抗及电容抗相等,此频率称为谐振频率。

可使电抗值互相抵消,导致净电抗值为 0 ,在谐振频率(f0),|XL|=|XC| 其中所言的 RLC 电路即指电阻、电感、电容组件所组合而成的电子回路。

所以了解何为特性阻抗之前,甚至何谓谐振频率应先就其材料特性加以了解,就电阻而言,电阻器(resistor)在高频电路中应用甚广,但是一般对电阻特性的了解仍多局限于电阻在直流电路中,所呈现的阻尼特性。

实际上,电阻在高频电路中,因受信号频率的影响,不仅电阻值会随之改变,更可能会呈现电感或电容的特性。

如图所示电阻器在高频时的等效电路,R 为电阻器的电阻值, L 为其两端引线的电感,C 为存在于电阻器内所有杂散电容的总和。

杂散电容形成的原因随电阻器结构的不同而异,以碳粒合成电阻(carbon composite resistor)为例,由于其结构为以微小碳粒压合而成,故在各碳粒之间都存有电容,此即为等效电路中杂散电容 C 的来源之一。

特性阻抗板工程制作规范

特性阻抗板工程制作规范1目的规范特性阻抗板工程设计和制作。

2适用范围适用于特性阻抗板的工程设计和制作。

3职责MI人员负责阻抗板的流程设计、叠层设计和阻抗计算;5.常见阻抗的类型5.1 单端阻抗常见类型5.1差分阻抗常见类型内层单端下线宽对应参考层6. 阻抗产品审核细则与注意事项1)记录客户阻抗与叠层要求:包括:阻抗控制层数,线宽/间距,屏蔽层,阻抗要求值与公差. 2) 按顾客要求与实际文件进行核对:找阻抗线----确定单端或差分----确定屏蔽层----是否共面地模式----是否覆盖阻焊.3) 根据顾客提供叠层初步计算,如需调整,按以下优先顺序进行(如果能电话沟通的最好先沟通清楚)-----调整叠层-----调整线宽-----建议顾客按理论计算值控制-----不作阻抗控制-----以上都不行则建议调整板厚.4) 如果相同层不能同时满足单端与差分阻抗要求,先满足差分,单端可建议客户按计算值控制. 5) 如果屏蔽层能够屏蔽大部分阻抗线,小部分不能屏蔽的情况下,如有其它问题,与客户说明确认,如果没有其它确认可以不确认;屏蔽层只能屏蔽小部分阻抗线的情况下必须与客户确认; 内层阻抗屏蔽层只能屏蔽小部分阻抗线时最好与客户确认相邻两层作参考层,因为隔层参考很难控制,同时如只有一个参考层时需确保不能隔太多层.(如8层板第3层有阻抗,尽量与客户确认两个参考层,同时最好是相邻层,不要隔层参考,不能第3层只参考第2层而无上参考层,即无上参考层的介质厚度为第3-8层的介质厚度,这介质厚度对阻抗是有很大影响的)6) 在审核后线宽需要加粗的情况下,必须确保间距足够;间距允许情况下尽量调大线宽制作,对于差分,线宽/间距小于0.10MM 时,尽量调大线宽,同时调大间距.(阻抗与线宽成反比,间距成正比,两个参数同时加大阻抗是可以不变的)7) 在间距足够情况下,对于差分阻抗或共面地阻抗,尽量线宽和间距一起调整,线宽调整多少,间距就调整多少,保证阻抗线易于调整.(如LW:0.20MM/L to L:0.20MM, 调整时LW:0.15MM/L to L:0.25MM, 即线宽缩小0.05mm,间距相应加大0.05mm)7.材料的选择7.1 材料选择考虑等级7.2 材料选择考虑的因素1) Tg 值(材料的玻璃转化点温度);(“无铅”兼容考虑,无铅多用高TG 材料) 2) Td 值或T260、T288 (材料的热分解温度);(“无铅”兼容考虑) 3) Er 值与Tan δ (Dk 与Df )(介质损耗与介质损耗角正切) 4) 卤素含量(是否为无卤素材料) 5) 客户产品使用频率值6) 其他考虑因素:UL 等级(阻燃)、CTI (漏电起痕指数)、CTE-Z(Z 轴澎涨系数)、专用高频材料.8.叠层的设计:8.1顾客叠层要求>阻抗要求>板厚要求>填胶要求>制作要求>成本要求>其他要求.8.2 如果客户有叠层的要求或叠层图时,按客户的叠层计算阻抗,同时确保完成板厚要求.8.3 按客户的要求或自行设计叠层时,如果实在无法满足客户所有的阻抗要求,优先满足所有层的差分,单端按实际计算值制作,但设计时单端阻抗值与实际要求不能相差太远,应小于10欧,如果可以,先和客户电话沟通,事先确认,再发问客,避免重复工作.8.4 客户没有叠层要求和叠层图时, 简单产品可以用手工计算叠层,如阻抗较为复杂,采用Polar 自动化软件计算出其叠层,再把叠层和调整后的线宽/线距提供给客户确认.8.5半固化片厚度使用考虑流胶后的厚度:(残铜率按单元的残铜率即可)类型一:芯板与铜箔之间(单面填胶)类型二:内层芯板之间(双面填胶)类型一:实测厚度=理论厚度-铜厚*(1-残铜率) (表层的残铜率取100%,光板残铜率为0)类型二:实测厚度=理论厚度-铜厚1*(1-残铜率1)-铜厚2*(1-残铜率2)8.6半固化片使用原则1)应优先满足流胶问题,然后考虑其生产成本。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

目录序号内容页数1.0 目的 32.0 范围 33.0 定义 34.0 职责 35.0 程序3-126.0 相关文件127.0 参考文件128.0 记录表格129.0 附录121.0目的建立PE-MI对阻抗板进行阻抗设计时的规范设计方法。

2.0范围本指引适用于上海美维电子有限公司所有有阻抗要求的线路板。

本指引规定MI对阻抗板进行阻抗设计时的计算公式,标准设计参数,及根据反馈调整设计的方法。

3.0定义无4.0职责4.1PE负责执行,维护和更新本程序。

4.2ME负责确认程序中需要的相关参数及修正反馈计算方法。

4.3生产部负责控制介质厚度、线宽、间距及铜厚。

4.4QM负责反馈相关的测试数据。

4.5 QM负责批准本程序。

5.0程序5.1检查客户资料,明确客户的阻抗线路层,阻抗类别, 阻抗要求值及公差,接地参考层,介质材料,介质厚度要求,线宽间距及公差等基本信息。

5.2根据阻抗类别,使用软件CITS25中对应的公式,输入对应的相关参数进行核算调整。

5.2.1 材料的介电常数:根据阻抗反馈的实际统计结果, 阻抗计算时材料的介电常数按下表进行,可能与原材料供应商提供的标称介电常数有所不同。

特殊材料的介电常数必须提出讨论。

5.2.2 阻抗计算铜层厚度:阻抗计算时线路铜的厚度按下表计算,与层压计算板厚时采用的参数有所不同。

5.2.3 线宽顶部与底部宽度差值:根据内外层铜厚不同按下表设定线宽差值。

内层铜厚10um 15um 25um 30um 61um线底线顶差值5um 10um 20um 20um 38um外层线路铜厚35um 43um 61um 81um 96um线底线顶差值25um 30um 38um 43um 51um中外层线路铜厚。

当线路铜厚不在表中所列时按表中最接近的线路铜厚计算。

5.2.4 介质厚度计算:新产品及没有介质厚度反馈的产品,层与层之间的介质厚度按DPM-27201-19层压工序指示规程中所指定的计算方法计算(含铜厚计算方法);但当内层有电镀层时,电镀层铜厚按上表二计算。

5.2.5 计算公式:选择对应的计算公式,输入对应的参数,采用插值法调整参数,注意各参数所用单位保持一致。

选取一组能获得目标阻抗值的同时符合客户要求的最佳数据(线宽,介厚,铜厚,介电常数)作为过程控制目标中值,控制目标公差:内层线宽+/-0.4mil (10um). 介质厚度+/-10%且在+/- 1.0 mil (25um)内,外层线宽参考公差+/-0.4 mil, 铜厚公差+/-0.32 mil (8um),当阻抗可测时控制阻抗值优先于控制阻抗线线宽。

5.2.5.1 表面特性阻抗计算:图一表面特性阻抗计算公式根据阻焊前后阻抗值变化规律及阻抗计算公式偏差特点,外层阻抗计算按图一公式计算,并按表四修正。

客户要求的最终的外30Ω40Ω50Ω60Ω70Ω层完成阻抗中值公式计算阻抗对应值29Ω40Ω53Ω63Ω74Ω欧姆,计算参数如图一所示。

5.2.5.2 内层半屏蔽特性阻抗计算:图二内层半屏蔽特性阻抗计算公式Array表五内层特性阻抗计算修正对应表客户要求的最终的内30Ω40Ω50Ω60Ω70Ω层完成阻抗中值公式计算阻抗对应值28Ω39Ω50Ω60Ω70Ω如图二所示:H=127+58+18; Er=4*127/(127+58+18)+ 3.6*(58+18)/(127+58+18)。

5.2.5.3 内层屏蔽特性阻抗计算:图三内层屏蔽特性阻抗计算公式例:6mil(H/H)芯板,7628H半固化片,Hoz Ground层,要求中间阻抗线60+/-6欧,计算如图三所示。

阻抗修正同表五。

5.2.5.4 特性阻抗测试条的设计如图四所示,SME标准的阻抗测试条宽度为7.62mm,长度为177.8mm,在空间不够的条件下也可适当减少测试条的长度到127mm. 若相邻层有阻抗线,则需注意,COUPON 上这两层的信号线在垂直方向(板厚度方向)不宜重合。

图四中的上图为测试线路层示意图,下图为屏蔽地层示意图。

测试孔刀径1.0mm; 水平间距0.1”,垂直间距0.1”,上排孔接测试线,下排孔接Ground 层,测试探针为二针脚,固定间距为0.1414”,测试时一脚接线另脚接地。

在阻抗测试条外层的对应接线孔位置需写上阻抗线所在层号,空白位写SME产品编号(除内部版本号),并留出书写序列号的空白区域并做阻焊开窗如图五所示。

图四普通特性阻抗测试条示意图一根测试条上的同一层也可以设置两根测试线,此时测试条左端的测试孔上排接线下排接地、右端的测试孔上排接地下排接线,测试线另一端悬空不接孔,测试条宽度可设置为0.4”如图五之上图所示。

通常不建议在同一层上于阻抗测试条的同一侧布置多根阻抗测试线,当由于拼版空间的限制而有必要采用此种形式设计时(测试条只能为0.3”宽时),为避免阻抗线之间相互干扰两根测试线之间的距离不宜小于15mil如图五之下图所示。

图五特性阻抗测试条在同一层设两根测试线不同层上的阻抗线若对应的接地参考层相同则应尽可能将阻抗线在垂直方向(厚度方向)上相互错开(边到边错开距离>=15mil),若其中任一层的阻抗线线宽>8mil 则两层的阻抗线不应放在同一测试条的同一侧。

5.2.5.5 外层差分阻抗:根据阻焊前后阻抗值变化规律及阻抗计算公式偏差特点,外层差分阻抗计算按图四公式计算,并按表六修正。

表六外层差分阻抗计算修正对应表外层完成阻抗中值70Ω80Ω90Ω100Ω110Ω120Ω130Ω公式计算阻抗对应值73 84 95 107 119 131 143图六外层差分阻抗计算公式图六例:外层2116半固化片,内层0.5oz Ground层,差分线12mil中心距,完成阻抗100+/-10欧。

5.2.5.6 内层半屏蔽差分阻抗计算:图七内层半屏蔽差分阻抗计算公式图七例:内层8mil(1/1oz)芯板,外层7628半固化片,差分线中心距10mil, 完成阻抗要求100+/-10欧。

内层差分阻抗计算值不需修正。

5.2.5.7 内层屏蔽差分阻抗:图八内层屏蔽差分阻抗计算公式图八例:内层10mil(H/Hoz)芯板,外层7628半固化片,差分线中心距15mil, 完成阻抗要求115+/-11.5欧。

内层差分阻抗计算值不需修正。

5.2.5.8差动阻抗测试条的设计如图九所示,SME标准的阻抗测试条宽度为12.7mm,长度为203.2mm,图九中的上图为测试线路层示意图,下图为屏蔽地层示意图。

若相邻层也有阻抗线,则需注意,COUPON 上这两层的信号线在垂直方向(板厚度方向)不宜重合。

测试孔刀径1.0mm; 水平间距0.1”,垂直间距0.1”,左端上排孔接测试线,下排孔接Ground 层,右端相反。

测试探针为四针脚,上排二测线脚固定间距为0.2”,下排二接地脚固定间距0.4”上下两排针脚垂直间距0.1”。

图九普通差动阻抗测试条5.2.5.9 对于其它类型的阻抗设计需提出讨论后再决定其计算方法及测试条的设计。

必要时,阻抗测试条的宽度可以小于0.5”。

如带屏蔽地线差动阻抗的测试条可设计如图十所示,该类差动阻抗的计算公式也有所不同。

图十带屏蔽线差动阻抗测试条示意图5.2.5.10 对于实际板由于阻抗不合格而需反馈调整阻抗时按以下方法调整:记:客户要求阻抗值(或按表四、表五、表六修正后应该需要的值)为Z0,实测阻抗值为Z1,按切片数据(线宽、介厚、铜厚数据)及表一中理论介电常数Er计算阻抗值为Z2。

5.2.5.10.1 无法获得切片数据的情况(应尽可能取得切片数据):即只有实测阻抗值Z1反馈。

调整方法:调整线宽、介质厚度控制值,使得计算值为Z0-(Z1-Z0), 即将实际和初始理论的差额全部补偿。

例如:某一款板,Z0=50, Z1=54,则调整线宽、介质厚度控制值,使得计算值为Z0-(Z1-Z0)=46 ohm.5.2.5.10.2 获得切片数据的情况。

通常认为切片数据是可信的,且是有代表性的。

若切片数据的介质厚度与原先DPM-27201-19层压工序指示规程中理论的介质厚度相差超过10%,或超过25.4 um (1.0mil)。

则需提出APQP,确认改变配方以得到原先的设定的介质厚度;然后,按APQP给出的配方的理论介厚,调整线宽,使得计算目标值为Z0,即按APQP结果重新以新板处理。

若切片数据的介质厚度与理论的介质厚度相差在10%之内,同时也在25.4 um (1.0mil)之内。

则第一步,按切片数据(线宽、介厚、铜厚数据)Z2,调整介电常数Er'至以使得计算阻抗值为Z1,即回归算出修正后的介电常数Er'。

第二步,调整线宽,使用切片的介厚、铜厚、介电常数Er',使得计算的阻抗值为Z0。

这种情况为多数情形,举例如下:某一款板,客户要求成品外层线单线阻抗50+/-5 ohm. 初始设计为(介厚,线顶,线底,铜厚,介电常数)= (5,7.15,8.35,1.7,4.0)CITS25→ Z0 =53-3=50. 实际做板反馈,切片数据(介厚,线顶,线底,铜厚)= (5.4,6.7,8.0,1.7),实测COUPON的阻抗值Z1=54,修正后阻焊前为57.第一步,调整介电常数至3.85, 使得按切片数据(5.4,6.7,8.0,1.7,3.85)CITS25→57=按前面表四修正后的实测阻抗值, 即求得介电常数Er'=3.85;第二步,调整线宽,使用切片的介厚、铜厚、介电常数Er',(5.4,8.0,9.2,2.0,3.85)CITS25→53=计算的目标阻抗值。

于是,调整后的线宽目标为线顶8.0+/-0.4mil, 线底为9.2+/-0.4 mil. (必要时注意向客户确认线宽可以调整)图十一阻抗调整示意图6.0相关文件6.1DPM-27201-01 制造能力规范6.2DPM-27201-19层压工序指示规程6.3DPM-27201-59内层干膜制作规程DPM-27201-15外层干膜工序制作规程7.0参考文件无8.0记录表格6.1 PE-MI-002 PCL9.0附件无修订日期新版本号更改版本内容简述修改人2004-09-06 A 新建立。