2 实验二三态门实验

简单的物理实验初步认识物质三态及变化规律

简单的物理实验初步认识物质三态及变化规律物质的三态是指固态、液态和气态,它们之间存在着相互转化的规律。

通过进行简单的物理实验,我们可以初步认识到这些物态的特点以及它们之间的变化规律。

1. 实验一:冰的熔化过程材料:冰块、温度计、容器、火柴实验步骤:将冰块放入容器中,使用温度计测量冰块的温度。

然后,点燃火柴,将火焰放在冰块上方。

观察冰块的变化过程,并及时记录观察结果。

实验结果与讨论:初始状态下,冰块的温度为零度。

随着火焰的接近,冰块开始融化,温度逐渐上升。

当冰块全部融化成水时,温度不再上升。

通过实验我们可以得出结论,固态物质在一定温度下会转化为液态物质。

2. 实验二:水的沸腾过程材料:水、酒精灯、温度计、容器实验步骤:将水倒入容器中,使用温度计测量水的初始温度。

然后,将酒精灯放在容器底部,点燃酒精灯。

观察水的变化过程,并记录观察结果。

实验结果与讨论:初始状态下,水的温度为室温。

随着酒精灯的加热,水开始加热并逐渐升温。

当水温达到一定温度时,水表面开始冒泡并产生水蒸气。

这时,水正在沸腾。

通过实验我们可以得出结论,液态物质在一定温度下会转化为气态物质。

3. 实验三:水的冷凝过程材料:热水、温度计、玻璃杯、冰块实验步骤:将热水倒入玻璃杯中,使用温度计测量水的初始温度。

然后,将冰块放入热水中。

观察水的变化过程,并记录观察结果。

实验结果与讨论:初始状态下,热水温度较高。

在冰块的作用下,热水开始冷却并逐渐降温。

当温度降低到一定程度时,水蒸气开始凝结,形成水滴。

这时,水正在冷凝为液态物质。

通过实验我们可以得出结论,气态物质在一定温度下会转化为液态物质。

综上所述,通过上述实验我们初步认识到了物质的三态及其变化规律。

固态物质可以通过加热转化为液态物质,液态物质可以通过加热转化为气态物质,气态物质可以通过降温转化为液态物质。

这些物质态之间的相互转化是由温度的变化引起的。

通过继续深入学习和实践,我们可以更加全面地了解物质三态的性质及其变化规律,从而更好地应用于实际生活和科学研究中。

三态门、oc门实验报告 湖南大学数字逻辑

实验二三态门,OC门的设计与仿真一、实验目的熟悉三态门、OC门的原理,用逻辑图和VHDL语言设计三态门、OC门,并仿真。

二、实验内容1.用逻辑图和VHDL语言设计三态门,三态门的使能端对低电平有效。

2.用逻辑图和VHDL语言设计一个OC门(集电极开路门)。

三、实验原理1.三态门,又名三态缓冲器(Tri-State Buffer)用途:用在总线传输上,有效而又灵活地控制多组数据在总线上通行,起着交通信号灯的作用。

功能:三态逻辑输出三种不同的状态,其中两种状态常见的逻辑1和逻辑0,第三个状态高阻值,称为高阻态,用Hi-Z或者Z或z表示三态缓冲器比普通缓冲器多了一个使能输入EN,即连接到缓冲器符号底部的信号。

从真值表可以看出,如果是EN=1.则OUT等于IN,就像普通缓冲器一样。

但是当EN=0时,无论输入的值什么,输出结果为高阻态(Hi-Z)。

逻辑图真值表EN A OUT0 0 Hi-Z0 1 Hi-Z1 0 01 1 1波形图2.OC门,又名集电极开路门(opndrn)用途:集电极开路门(OC门)是一种用途广泛的门电路。

典型应用是可以实现线与的功能。

逻辑图真值表A B0 01 Hi-Z波形图四、实验方法与步骤实验方法:采用基于FPGA进行数字逻辑电路设计的方法。

采用的软件工具是QuartusII软件仿真平台,采用的硬件平台是Altera EPF10K20TI144_4的FPGA试验箱。

实验步骤:1、编写源代码。

打开QuartusⅡ软件平台,点击File中得New建立一个文件。

编写的文件名与实体名一致,点击File/Save as以“.vhd”为扩展名存盘文件。

VHDL 设计源代码如下:三态门:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY tri_s ISPORT (enable,datain:IN STD_LOGIC;dataout:OUT STD_LOGIC);END tri_s;ARCHITECTURE bhv OF tri_s ISBEGINPROCESS (enable,datain)BEGINIF enable='1' THEN dataout<=datain;ELSE dataout<='Z';END IF;END PROCESS;END bhv;OC门:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY oc ISPORT(datain:IN STD_LOGIC;dataout:OUT STD_LOGIC);END oc;ARCHITECTURE bhv OF oc ISBEGINPROCESS (datain)BEGINIF (datain='0') THEN dataout<='0';ELSE dataout<='Z';END IF;END PROCESS;END bhv;2、按照实验箱上FPGA的芯片名更改编程芯片的设置。

实验二逻辑门及三态门 电子技术基础实验模拟数字

(1) 表示生产芯片公司名称 (2) 表示芯片系列(属民用产品) (3) 表示导电形式(TTL) (4) 表示芯片型号代码 (4输入双与非门) (5) 表示工作温度范围( 0~70℃ ) (6) 表示封装结构 (双列塑封)

数字电子技术实验

四川大学 电气信息学院 电工电子基础教学实验中心

四川大学电工电子实验1中心

实验二 集成逻辑门与三态门 电路的测量

主要内容

•数字集成芯片基础知识

1、数字集成芯片的识别 2、集成芯片的命名 3、集成芯片的分类 4、集成芯片的使用规则

•本实验所涉及集成电路芯片介绍 •实验内容及注意事项

四川大学电工电子实验2中心

不允许并联连接(三态门除外)

四川大学电工电子实验8中心

CMOS集成电路的使用规则

1、电源电压为3~18V(VDD接电源正极,VSS接 地)

2、多余输入端处理 按逻辑要求接VDD或VSS 与使用输入端并联 不允许悬空处理(否则会引起逻辑混乱甚至损坏

器件) 3、输出端处理 不允许直接接电源或接地 不允许并联连接(三态门除外)

数字集成芯片的识别

•芯片封装结构 1、扁平结构 2、双列直插结构

四川大学电工电子实验3中心

数字集成芯片的识别

• 芯片引脚排列

以芯片上一个缺口或小圆点置于使用者左侧 时为正方向,器件的左下脚为第一脚,依次按 逆时针方向读出其它引脚。

四川大学电工电子实验4中心

集成芯片的命名规则 国际通用TTL芯片命名

输出Y 与 或非

由输入(A B)输出(Y)之间的逻辑关系,用 与非门74LS00完成其逻辑功能

四川大学电工电子实验19中心

实验二集电极开路门电路及三态门电路的研究

实验二集电极开路门电路及三态门电路的研究实验目的:

1.掌握集电极开路门电路及三态门电路的工作原理;

2.通过实验验证集电极开路门电路及三态门电路的工作状态;

3.思考电路中不同元器件参数的变化对电路工作状态的影响。

实验原理:

1.集电极开路门电路:

集电极开路门电路是由晶体管单管实现的基本逻辑电路,其原理是通过晶体管的放大作用,实现输入信号与输出信号的逻辑关系。

当输入为高电平时,晶体管处于饱和状态,输出为低电平;当输入为低电平时,晶体管为截止状态,输出为高电平。

而当输入为浮空时,晶体管的控制端处于开路状态,整个电路无法判断输出状态。

实验器材及元器件:

集电极开路门电路实验:电源、电容、电阻、三极管、万用表。

三态门电路实验:电源、电容、电阻、三极管、二极管、万用表。

实验步骤:

1.集电极开路门电路实验:

(1)按照电路图连接电路,注意器件的极性。

(2)将控制端接入电源的正极和负极,分别记录输出电压的高低电平值。

(3)将控制端不接入电源,即处于浮空状态,记录输出电压值并分析原因。

实验结果及分析:

1.集电极开路门电路实验:

(1)控制端输入高电平时,输出为低电平;控制端输入低电平时,输出为高电平。

(2)控制端浮空时,晶体管无法放大,整个电路处于不稳定状态,输出值也不能确定。

实验分析:

1.集电极开路门电路工作原理简单,但在实际应用中容易受到噪声等因素的干扰,造成输出不稳定。

2.三态门电路具有较好的输出稳定性和电路适应性,在数字集成电路、计算机等领域应用广泛。

实验2-三态门实验

实验二三态门实验一、实验目的1、掌握三态门逻辑功能和使用方法。

2、掌握三态门构成总线的特点和方法。

3、初步学会用示波器测量简单的数字波形。

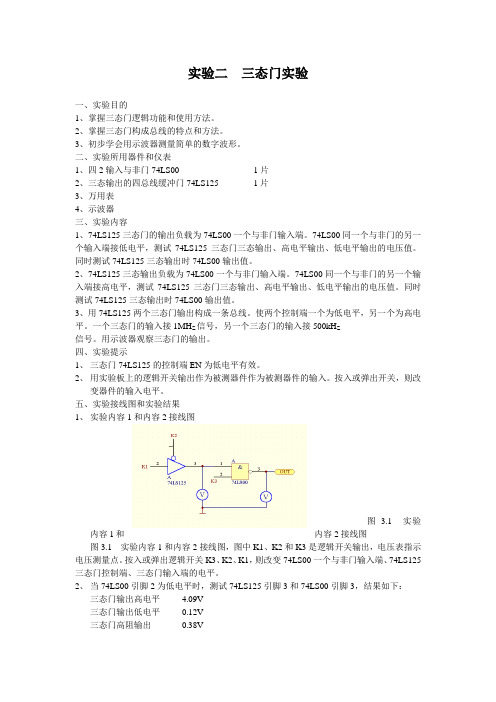

二、实验所用器件和仪表1、四2输入与非门74LS00 1片2、三态输出的四总线缓冲门74LS125 1片3、万用表4、示波器三、实验内容1、74LS125三态门的输出负载为74LS00一个与非门输入端。

74LS00同一个与非门的另一个输入端接低电平,测试74LS125三态门三态输出、高电平输出、低电平输出的电压值。

同时测试74LS125三态输出时74LS00输出值。

2、74LS125三态输出负载为74LS00一个与非门输入端。

74LS00同一个与非门的另一个输入端接高电平,测试74LS125三态门三态输出、高电平输出、低电平输出的电压值。

同时测试74LS125三态输出时74LS00输出值。

3、用74LS125两个三态门输出构成一条总线。

使两个控制端一个为低电平,另一个为高电平。

一个三态门的输入接1MH Z信号,另一个三态门的输入接500kH Z信号。

用示波器观察三态门的输出。

四、实验提示1、三态门74LS125的控制端EN为低电平有效。

2、用实验板上的逻辑开关输出作为被测器件作为被测器件的输入。

按入或弹出开关,则改变器件的输入电平。

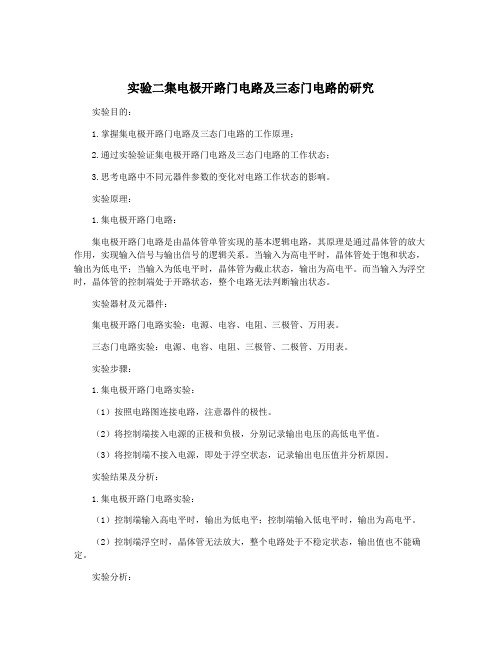

五、实验接线图和实验结果1、实验内容1和内容2接线图图 3.1 实验内容1和内容2接线图图3.1 实验内容1和内容2接线图,图中K1、K2和K3是逻辑开关输出,电压表指示电压测量点。

按入或弹出逻辑开关K3、K2、K1,则改变74LS00一个与非门输入端、74LS125三态门控制端、三态门输入端的电平。

2、当74LS00引脚2为低电平时,测试74LS125引脚3和74LS00引脚3,结果如下:三态门输出高电平 4.09V三态门输出低电平0.12V三态门高阻输出0.38V74LS00引脚3输出 4.04V3、当74LS00引脚2为高电平时,测试74LS125引脚3和74LS00引脚3,结果如下:三态门输出高电平 4.09V三态门输出低电平0.12V三态门高阻输出 1.50V74LS00引脚3输出0.10V4、用三态门构成总线接线图图3.2 三态门构成总线用三态门74LS125构成总线时,只要将三态门输出并联即可,在任何时刻,构成总线的三态门中只允许一个控制端为低电平,其余控制端均为高电平。

集成门电路功能测试(三态门)

集成门电路功能测试实验报告一实验内容1 三态门的静态逻辑功能测试。

2 动态测试三台门。

并画出三态门的输出特性曲线。

输入为CP矩形波。

3 测试三态门的传输延迟时间。

4 动态测试三态门的电压传输特性曲线。

输入为三角波。

二实验条件硬件基础实验箱,函数信号发生器,双踪示波器,数字万用表,74LS125。

三实验原理1 首先测试实验箱上提供的频率电源参数是否正确。

打开实验箱电源,把分别把5MHz的脉冲接入红表笔上,黑表笔接地。

观察示波器显示波形的频率是否为5MHz,经过观察计算,波形频率接近5M。

误差很小,从下图可以看出,ch1为输入波形一个周期占四个格子,可计算得到f=5MHz。

2 三态门的静态逻辑功能测试。

(后面四个实验都是通过示波器在同一时刻测试3动态测试三台门。

并画出三态门的输出特性曲线。

输入为CP矩形波。

使能端无效是波形:使能端有效时输出波形4 测试三态门的传输延迟时间。

通过测量同一时刻的输入输出波形,可以观察到三态门的输出延迟。

得到波形图为CH1,CH2分别为输入输出波形,可以看出在上升沿的输出延迟为10ns然而下降沿的时候的截图已经丢失了,依稀记得在实验时候,测得是数据下降沿的输出延迟与上升沿的不一致,并且比上升沿的短。

为9.6ns,其传输延迟为两个延迟的平均值9.8ns。

5 测试三态门的电压传输特性曲线。

输入为三角波。

得到输入输出波形为:CH1为输入,CH2为输出。

得到阀值电压为0.92V。

四总结这次实验基本上和上次实验的方法一样,没遇到什么大的问题。

就是还是粗心。

五评价实验效果挺好。

巩固了对逻辑器件的功能测试的方法和操作。

三态门实验报告

三态门实验报告三态门实验报告引言:在科学研究中,实验是获取真实数据和验证理论的重要方法之一。

本次实验旨在研究三态门的工作原理和应用。

通过实验,我们能够深入了解三态门的特性,并进一步探究其在现实生活中的应用。

一、实验目的本次实验的目的是通过搭建三态门电路,观察和分析三态门的工作原理,探究其在数字电路中的应用。

二、实验材料和仪器本次实验所需材料和仪器如下:1. 电路板2. 三态门芯片3. 连接线4. 电源5. 开关6. LED灯三、实验步骤1. 将三态门芯片插入电路板中,并用连接线连接芯片和其他元件。

2. 将电源接入电路板,确保电路板正常供电。

3. 通过开关控制输入信号,观察LED灯的亮灭情况。

四、实验结果和分析通过实验观察和数据记录,我们得出以下实验结果和分析:1. 当输入信号为低电平时,LED灯熄灭。

2. 当输入信号为高电平时,LED灯点亮。

3. 当输入信号为无效电平时,LED灯保持上一状态。

根据实验结果,我们可以得出以下结论:三态门是一种数字逻辑门,具有三个输入端和一个输出端。

它的工作原理是根据输入信号的不同状态,输出相应的电平。

当输入信号为低电平时,输出为低电平;当输入信号为高电平时,输出为高电平;当输入信号为无效电平时,输出保持上一状态。

五、三态门的应用三态门在数字电路中有广泛的应用。

以下是一些常见的应用场景:1. 数据总线控制:在计算机系统中,三态门常用于数据总线的控制,实现数据的传输和共享。

2. 内存芯片:三态门可以用于内存芯片的控制线路,实现数据的读取和写入。

3. 多路选择器:三态门可以用于多路选择器的实现,根据输入信号的不同状态,选择不同的输入通路。

4. 缓冲器:三态门可以用作缓冲器,将信号从一个电路传递到另一个电路,保持信号的强度和波形。

六、实验总结通过本次实验,我们深入了解了三态门的工作原理和应用。

三态门作为一种重要的数字逻辑门,在现代电子技术中起着重要的作用。

通过进一步研究和实践,我们可以更好地应用三态门,推动数字电路技术的发展。

数字电路实验报告实验二

2、利用六反相器CD4069测量逻辑门电路的时 利用六反相器CD4069 CD4069测量逻辑门电路的时

延参数。 CD4069中的六个非门依次串联连接, 延参数。将CD4069中的六个非门依次串联连接, 中的六个非门依次串联连接 在输入端输入250KHz TTL信号 250KHz的 信号, 在输入端输入250KHz的TTL信号,用双踪示波器 测总的延时, 测总的延时,计算每个门的平均传输延迟时间 的值。 的tpd的值。

&

&

&

&

74LS03(集电极开路门)引脚图

数字逻辑箱

三、实验内容

1、对CD4070的逻辑功能的测试 (1)用逻辑箱观测4070的逻辑功能并完成下表 逻辑开关 输 入 引脚 引脚 ( )( ) 0 0 1 1 0 1 0 1 指示灯 输 出 引脚 ( )

(2)、对CD4069的逻辑功能的测试 、 的逻辑功能的测试 用逻辑箱观测4069的逻辑功能并完成下表 用逻辑箱观测 的逻辑功能并完成下表 逻辑开关 输 入 0 1 指示灯 输 出

二、实验原理

1. CMOS常用门电路 常用门电路

≥1

≥1

≥1

≥1

≥1

CD4001(四2输入或非门)引脚图

&

&

&

&

CD4011(四2输入与非门)引脚图

1

1

1

1

1

1

CD4069(六反相器)引脚图

=1 1=

1=

1=

CD4070(四异或门)引脚图

1

1 ▽

EN EN

1 ▽

EN EN

1 ▽

▽

74LS125(三态门)引脚图

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验二、三态门实验

一、实验目的

1、掌握三态门逻辑功能和使用方法。

2、掌握用三态门构成总线的特点和方法。

3、初步学会用示波器测量简单的数字波形。

二、实验所用仪器和芯片

1、四二输入与非门74LS00 1片

2、三态输出的四总线缓冲门74LS125 1片

3、TEC-5实验系统 1台

4、示波器 1台

三、实验内容

1、74LS125三态门的输出负载为74LS00的一个与非门输入端。

74LS00同一个与非门的另一个输入端接低电平,测试74LS125三态门的三态(高阻)输出、高电平输出、低电平输出的电压值。

同时测试74LS125三态输出时74LS00的输出值。

2、74LS125三态门的输出负载为74LS00的一个与非门输入端。

74LS00同一个与非门的另一个输入端接高电平,测试74LS125三态门三态(高阻)输出、高电平输出、低电平输出的电压值。

同时测试74LS125三态输出时74LS00的输出值。

*3、用74LS125两个三态门输出构成一条总线。

使两个控制端一个为低电平,另一个为高电平。

一个三态门的输入接50kHz信号,另一个三态门的输入接

500KHz信号。

用示波器观察三态门的输出。

四、实验提示

1、三态门74LS125的控制端C为低电平有效。

2、用实验台的电平开关输出作为被测器件的输入。

拨动开关,则改变器件的输入电平。

五、实验报告要求

1、画出实验的逻辑电路图。

2、分析每个实验的实验现象。

3、分析实验1和实验2中三态门输出电压不同的原因。

*4、用三态门74LS125构成总线时,三态门输出应怎样连接?为什么在任何时刻,构成总线的三态门中只允许一个控制端为低电平,其余控制端应为高电平。