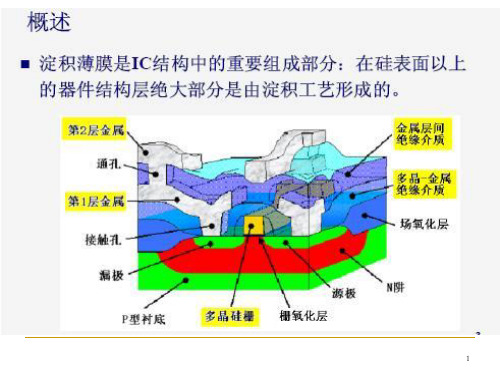

第六章 薄膜淀积

合集下载

微电子工艺原理-第6讲薄膜工艺物理气相淀积-68页PPT文档资料

半导体工艺设备一般工作在初、中真空度。而在通入工作气 体之前,设备先抽至高、超高真空度。

20

气体G流---动-在及体积导率----气体动力学

V内气体的质量

ρ ----质量密

质量流速qm度(g/s):

qm

dG dt

d(ρV) dt

阀门

气体流量Q (L·atm/min):

Q

qm

p g

气流用标准体积来测量,指相同气体, 在0℃和1atm下所占的体积。

(cold pump | cryogenic pump | cryovacuum pump | low temperature pump)

利用低温表面冷凝气体真空 泵,又称冷凝泵。

抽气原理 在低温泵内设

有由液氦或制冷机冷却到极

低温度的冷板。它使气体凝

结,并保持凝结物的蒸汽压

力低于泵的极限压低温力泵,是从获得而清洁真空的极限压力最低、

25.11.2019

4

25.11.2019

5

25.11.2019

6

25.11.2019

7

25.11.2019

8

25.11.2019

9

25.11.2019

10

薄膜工艺主要内容

一、物理气相淀积 二、化学气相淀积 三、外延生长技术

25.11.2019

11

一、物理气相淀积(PVD)

21

气体传导率C

C Q P1 P2

C与电导率一样并联相加;串联时倒数相加 若大量气体流过真空系统,要保持腔体压

力接近泵的压力,就要求真空系统有大的 传导率----管道直径;泵放置位置

•泵的抽速Sp----体积置换率

20

气体G流---动-在及体积导率----气体动力学

V内气体的质量

ρ ----质量密

质量流速qm度(g/s):

qm

dG dt

d(ρV) dt

阀门

气体流量Q (L·atm/min):

Q

qm

p g

气流用标准体积来测量,指相同气体, 在0℃和1atm下所占的体积。

(cold pump | cryogenic pump | cryovacuum pump | low temperature pump)

利用低温表面冷凝气体真空 泵,又称冷凝泵。

抽气原理 在低温泵内设

有由液氦或制冷机冷却到极

低温度的冷板。它使气体凝

结,并保持凝结物的蒸汽压

力低于泵的极限压低温力泵,是从获得而清洁真空的极限压力最低、

25.11.2019

4

25.11.2019

5

25.11.2019

6

25.11.2019

7

25.11.2019

8

25.11.2019

9

25.11.2019

10

薄膜工艺主要内容

一、物理气相淀积 二、化学气相淀积 三、外延生长技术

25.11.2019

11

一、物理气相淀积(PVD)

21

气体传导率C

C Q P1 P2

C与电导率一样并联相加;串联时倒数相加 若大量气体流过真空系统,要保持腔体压

力接近泵的压力,就要求真空系统有大的 传导率----管道直径;泵放置位置

•泵的抽速Sp----体积置换率

第六章_薄膜气相淀积工艺

35

36

二、氮化硅薄膜

1.氮化硅薄膜在集成电路中的主要应用,有三个方

面: (1)用作为硅选择氧化和等平面氧化的氧化掩膜; (2)钝化膜; (3)电容介质。

氮化硅的化学汽相淀积:中等温度(780~820℃)的 LPCVD或低温(300℃) PECVD方法淀积

37

2. 低压化学气相淀积氮化硅薄膜

27

CVD 过程中使用等离子体的好处

1. 更低的工艺温度 (250 – 450℃); 2. 对高的深宽比间隙有好的填充能力 (用高密度等 离子体);

3. 淀积的膜对硅片有优良的黏附能力;

4. 高的淀积速率; 5. 少的针孔和空洞,因为有高的膜密度; 6. 工艺温度低,因而应用范围广。

28

各种类型 CVD 反应器及其主要特点

A、氮化硅的低压淀积方程式: 氮化硅的低压化学气相淀积主要通过硅烷、二氯二 氢硅与氨在700-8000C温度范围内反应生成。主要反 应式如下 LPCVD 3SiH2Cl2+7NH3Si3N4 +3NH4CL +3HCl +6H2 PECVD 3SiH4 + 4NH3 Si3N4 + 12H2

21

APCVD生长速率快,但成膜均匀性不好,容易产 生影响薄膜质量的微粒,基本不应用于集成电路 制造。LPCVD反应系统一般要求温度在650℃以上, 不能应用到后段。 后段工艺中薄膜生长的反应温度较低,需引入额 外的非热能能量或降低反应所需激活能以得到足 够反应能量。

22

前者代表是PECVD和HDPCVD,等离子体提供 的能量大大降低反应所需热能,从而降低反 应温度到400℃以下;后者代表是采用TEOS 与O3反应系统的SACVD,由于O3在较低温度下 就可以提供氧自由基,反应所需激活能小于 TEOS与O2 系统,因此较低温度下也可以提 供足够的淀积速率。

第六章化学气相淀积

>2000,湍流型(要尽. 量防止)。

6.1.3 Grove模型

.

6.1 CVD模型

? 6.1.3 Grove 模型

①假定边界层中反应剂的浓度梯度为线性近似,则

流密度为: F1=h g(Cg-Cs)

hg-气相质量转移系数, Cg-主气流中反应剂浓度, CS-衬底表面处反应剂浓度;

②表面的化学反应淀积薄膜的速率正比于 Cs,则 流密度为: F2=ksCs

第六章 化学气相淀积

主 讲:毛 维

mwxidian@ 西安电子科技大. 学微电子学院

概述

? 化学气相淀积:CVD——Chemical Vapour Deposition 。 ? 定义:一种或数种物质的气体,以某种方式激活后,在衬

底发生化学反应,并淀积出所需固体薄膜的生长技术2H2(g) ,

②掩蔽膜:用于选择性氧化;

③DRAM 电容的绝缘材料;

④MOSFETs 中的侧墙;

⑤浅沟隔离的CMP 停止层。 ? Si3N4薄膜的特性: ①扩散掩蔽能力强,尤其对钠、水汽、氧;

②对底层金属可保形覆盖;

可作为钝化层的原因

③针孔少;压应力可以很低(PECVD) ;

④介电常数较大:(εSi3N4=6-9,εSiO2 =4.2. ) ,不能作层间的绝缘层。

? 硅烷和N2O(NO) :PECVD 淀积机理 : SiH 4+N2O 200-400℃ SiO2+N2+H2O

? 原位掺P:形成PSG

淀积机理 : PH 3(g)+5O 2=2P2O5(固)+6H 2 优点: 温度低;反应机理简单。

缺点: 台阶覆盖差。

.

6.4 CVD二氧化硅

②液态TEOS 源:PECVD ? 淀积机理: Si(OC 2H5)4+O 2 250-425℃ SiO 2+H2O+C XHY ? 优点:安全、方便;厚度均匀;台阶覆盖好。 ? 缺点:SiO 2膜质量较热生长法差;

6.1.3 Grove模型

.

6.1 CVD模型

? 6.1.3 Grove 模型

①假定边界层中反应剂的浓度梯度为线性近似,则

流密度为: F1=h g(Cg-Cs)

hg-气相质量转移系数, Cg-主气流中反应剂浓度, CS-衬底表面处反应剂浓度;

②表面的化学反应淀积薄膜的速率正比于 Cs,则 流密度为: F2=ksCs

第六章 化学气相淀积

主 讲:毛 维

mwxidian@ 西安电子科技大. 学微电子学院

概述

? 化学气相淀积:CVD——Chemical Vapour Deposition 。 ? 定义:一种或数种物质的气体,以某种方式激活后,在衬

底发生化学反应,并淀积出所需固体薄膜的生长技术2H2(g) ,

②掩蔽膜:用于选择性氧化;

③DRAM 电容的绝缘材料;

④MOSFETs 中的侧墙;

⑤浅沟隔离的CMP 停止层。 ? Si3N4薄膜的特性: ①扩散掩蔽能力强,尤其对钠、水汽、氧;

②对底层金属可保形覆盖;

可作为钝化层的原因

③针孔少;压应力可以很低(PECVD) ;

④介电常数较大:(εSi3N4=6-9,εSiO2 =4.2. ) ,不能作层间的绝缘层。

? 硅烷和N2O(NO) :PECVD 淀积机理 : SiH 4+N2O 200-400℃ SiO2+N2+H2O

? 原位掺P:形成PSG

淀积机理 : PH 3(g)+5O 2=2P2O5(固)+6H 2 优点: 温度低;反应机理简单。

缺点: 台阶覆盖差。

.

6.4 CVD二氧化硅

②液态TEOS 源:PECVD ? 淀积机理: Si(OC 2H5)4+O 2 250-425℃ SiO 2+H2O+C XHY ? 优点:安全、方便;厚度均匀;台阶覆盖好。 ? 缺点:SiO 2膜质量较热生长法差;

6.LPCVD

清洗流量计(N2)

工艺开始执行至结束

调压(N2, NH3, O2)

抽流量计

抽本体真空

清洗流量计(N2)

抽流量计

回填(N2)

2、Exercises-设备操作流程

9、打开炉门, 小心取出硅片, 关上炉门 10、抽真空 11、停止加热 12、关工艺气体(TEOS源)

(足够高真空以后) 13、关罗兹泵 14、关机械泵 15、关主机 16、关加热电源 17、关主电源 18、关冷却水、压缩空气

1、Fundamentals-薄膜质量评价

晶粒(大小、晶向等)

与淀积温度、掺杂类型、热处理工艺有很大关系 温度对多晶硅晶粒的影响: <590℃,无定形态 >610℃,晶体态 590~610℃,中间态

晶粒大小对表面粗糙度的影响:

1、Fundamentals-薄膜质量评价

应力与应力梯度

应力:拉应力、压应力 来源、影响、测量、控制

热偶报警

表示控制系统的零点跳动大

超温报警(系统自动转到保温状态) TEOS源液位报警 表示炉膛温度超过极限超温报警值(系统将自动关掉炉子的加 热电源)

TEOS源温度报警 压力差报警(当实际压力值与设定值之差超过某一固定值时)

F3: * 表示故障;- 表示正常

1、Fundamentals-薄膜淀积之LPCVD

氧化硅薄膜(Silicon dioxide)

1、Fundamentals-薄膜淀积之LPCVD

氮化硅薄膜(Silicon Nitride)

用途:电气/热绝缘层、钝化层、掩膜层、刻蚀阻止层 反应方程式:

3SiH4 + 4NH3 -> Si3N4 + 12H2 x SiCl2H2 + y NH3 -> SixNy + 2xHCl + 3y/2H2

工学第六章薄膜工艺课件

约为10-3Torr,铝的密度2.7g/cm3,半径40cm,代入上式得:源自R d=17.4埃 /min

作业

• 希望用一台单源蒸发台淀积Ga和Al的混合 物,如果淀积温度是1000℃,坩埚内的初 始混合物是1:1,两种成分黏滞系数都为1, 则蒸发初期膜的组成将是怎样?膜的组成 如何随时间变化?

1.4 物理淀积-溅射

简单平行板溅射系统腔体 晶片上形成薄膜。

离子入射到到晶片表面时,可能产生的结果

反射:入射离子能量很 低;

吸附:入射离子能量小 于10eV; 离子注入:入射离子能 量大于10KeV; 溅射:入射离子能量为 10 - 10KeV 。 一 部 分 离 子能量以热的形式释放; 一部分离子造成靶原子 溅射。

高真空

10-8 - 10-4 Torr 10-6 -10-2 Pa

超高真空 <10-8 Torr

<10-6 Pa

真空泵

1. 真空的产生要依靠真空泵。而在低真空和高真 空情形下,要分别使用不同的泵。

2. 低真空下一般使用机械泵,其抽真空过程可以 分为三个步骤:捕捉气体,压缩气体,排除气 体。比如:活塞泵,旋转叶片真空泵,罗茨泵 等。

• 溅射的物理机制:是利用等离子体中的离 子对靶材料进行轰击,靶材料原子或原子 团被发射出来,堆集在晶片衬底上形成薄 膜。

• 与蒸发工艺相比:台阶覆盖性好,容易制 备合金或复合材料薄膜。

靶-接负极

晶片-置于正极

进气-氩气(用于产生等离 子)

工作原理:高压产生等离子 体之后,正离子在电场作用 下向负极运动,轰击靶电极, 激发出来的二次电子向正极 运动,维持等离子体。而被 轰击出来的靶原子则堆集在

• 温度:实际上确定了蒸气压。温度越高,蒸气压 越大,淀积速率越快,但需要控制淀积速率不能 太大,否则会造成薄膜表面形貌变差。

第六章化学气相淀积CVD

厚度的均匀性

薄膜厚度要求均匀性,材料的电阻会随膜厚度的 变化而变化,同时膜层越薄,就会有更多的缺陷,如 针孔,这会导致膜本身的机械强度降低,因此我们希 望薄膜有好的表面平坦度来尽可能减小台阶和缝隙。

高纯度和高密度

高纯度的膜意味着膜中没有那些会影响膜质量的 化学元素或者原子。要避免沾污物和颗粒。 膜的密度也是膜质量的重要指标,它显示了膜层中针 孔和空洞的多少。

原位掺杂

杂质原子在薄膜淀积的同时被结合到薄膜 中,一步完成薄膜淀积和掺杂 薄膜厚度、掺杂的均匀性淀积速度的控制 复杂

6.4 CVD SiO2

1.SiO2的用途

淀积

淀积

•非掺杂SiO2: 用于离子注入或扩散的掩蔽膜, 多层金属化层之间的绝缘,增加场区氧化层之 间的厚度。 •掺杂SiO2: 用于器件钝化,磷硅玻璃回流,掺 杂扩散源,与非掺杂SiO2结合作为多层金属化层 之间的绝缘层。

采用一条带或传输装置来传送硅片,通过流 动在反应器中部的反应气体。

应用:用于SiO2的淀积和掺杂的氧化 硅(PSG、BSG等)

SiH4+O2=SiO2 +H2O

100mm:10片,125mm:8片 Time:15min Temp:380~450℃6℃ 厚度均匀:< 5%

APCVD缺点

淀积温度℃ 平均晶粒直径(nm) 600 55 635 62 650 72 675 74 700 78 725 86

6.3 .2多晶硅的化学气相淀积

多晶硅的化学气相淀积采用LPCVD,因为 LPCVD淀积的薄膜均匀性好、高纯度等优点。

反应方程式:SiH4 → Si+2H2 550~650℃ 由N2或Ar携带SiH4 20%+ N2 80% 淀积速率:100~200Å/min

薄膜厚度要求均匀性,材料的电阻会随膜厚度的 变化而变化,同时膜层越薄,就会有更多的缺陷,如 针孔,这会导致膜本身的机械强度降低,因此我们希 望薄膜有好的表面平坦度来尽可能减小台阶和缝隙。

高纯度和高密度

高纯度的膜意味着膜中没有那些会影响膜质量的 化学元素或者原子。要避免沾污物和颗粒。 膜的密度也是膜质量的重要指标,它显示了膜层中针 孔和空洞的多少。

原位掺杂

杂质原子在薄膜淀积的同时被结合到薄膜 中,一步完成薄膜淀积和掺杂 薄膜厚度、掺杂的均匀性淀积速度的控制 复杂

6.4 CVD SiO2

1.SiO2的用途

淀积

淀积

•非掺杂SiO2: 用于离子注入或扩散的掩蔽膜, 多层金属化层之间的绝缘,增加场区氧化层之 间的厚度。 •掺杂SiO2: 用于器件钝化,磷硅玻璃回流,掺 杂扩散源,与非掺杂SiO2结合作为多层金属化层 之间的绝缘层。

采用一条带或传输装置来传送硅片,通过流 动在反应器中部的反应气体。

应用:用于SiO2的淀积和掺杂的氧化 硅(PSG、BSG等)

SiH4+O2=SiO2 +H2O

100mm:10片,125mm:8片 Time:15min Temp:380~450℃6℃ 厚度均匀:< 5%

APCVD缺点

淀积温度℃ 平均晶粒直径(nm) 600 55 635 62 650 72 675 74 700 78 725 86

6.3 .2多晶硅的化学气相淀积

多晶硅的化学气相淀积采用LPCVD,因为 LPCVD淀积的薄膜均匀性好、高纯度等优点。

反应方程式:SiH4 → Si+2H2 550~650℃ 由N2或Ar携带SiH4 20%+ N2 80% 淀积速率:100~200Å/min

第6章CVD化学气相淀积ppt课件

低气压下反应剂容易凝聚。 工艺改进:直接气化系统,液态源直接注入法

6.2.2 质量流量控制系统—直接控制气流流量 包括质量流量计和阀门,位于气体源和反应室之间 每分钟1cm3的气体流量—温度为273K、1个标准大气

压下,每分钟通过体积的1cm3气体。 6.2.3 CVD反应室的热源 热壁式CVD系统:TW=TS 冷壁式CVD系统:TW﹤TS

薄膜淀积过程存在两种极限情况:

①hg﹥﹥ks, Cs趋向于Cg,淀积速率受表面化学反应速率控制。 反应剂数量:主气流输运到硅片表面的﹥表面化学反应所需 要的

② hg﹤﹤ks, Cs趋于0,淀积速率受质量输运速率控制。反应 剂数量:表面化学反应所需要的﹥主气流输运到硅片表面的

N1-单位体积薄膜所需要的原子数量(原子/cm3)

PWS-5000: SiH4+O2=SiO2 +H2 O 100mm:10片, 125mm:8片 Time:15min Temp:380~450℃ 6℃ 厚度均匀: < 5%

2.低压化学气相淀积

5

特点:气压较低〔133.3Pa),淀积速率受表面反应控制,

要精确控制温度(±0.5°C),保证各个硅片表面上的反应

2.淀积速率与气流速率的关系 如图6.7 条件:质量输运速率控制 根据菲克第一定律和式6.5推导,得到

hg=Dg/δg

hgL Dg

=

3 Re 2

气流速率﹤1.0L/min,淀积速率与主气流速度Um的 平方根成正比。↑气流速率,可以↑淀积速率。 气流速率持续↑,淀积速率达到一个极大值,与气 流速率无关。 气流速率大到一定程度,淀积速率转受表面化学反 应速率控制,且与温度遵循指数关系。

薄膜淀积速率G=

F1 N1

6.2.2 质量流量控制系统—直接控制气流流量 包括质量流量计和阀门,位于气体源和反应室之间 每分钟1cm3的气体流量—温度为273K、1个标准大气

压下,每分钟通过体积的1cm3气体。 6.2.3 CVD反应室的热源 热壁式CVD系统:TW=TS 冷壁式CVD系统:TW﹤TS

薄膜淀积过程存在两种极限情况:

①hg﹥﹥ks, Cs趋向于Cg,淀积速率受表面化学反应速率控制。 反应剂数量:主气流输运到硅片表面的﹥表面化学反应所需 要的

② hg﹤﹤ks, Cs趋于0,淀积速率受质量输运速率控制。反应 剂数量:表面化学反应所需要的﹥主气流输运到硅片表面的

N1-单位体积薄膜所需要的原子数量(原子/cm3)

PWS-5000: SiH4+O2=SiO2 +H2 O 100mm:10片, 125mm:8片 Time:15min Temp:380~450℃ 6℃ 厚度均匀: < 5%

2.低压化学气相淀积

5

特点:气压较低〔133.3Pa),淀积速率受表面反应控制,

要精确控制温度(±0.5°C),保证各个硅片表面上的反应

2.淀积速率与气流速率的关系 如图6.7 条件:质量输运速率控制 根据菲克第一定律和式6.5推导,得到

hg=Dg/δg

hgL Dg

=

3 Re 2

气流速率﹤1.0L/min,淀积速率与主气流速度Um的 平方根成正比。↑气流速率,可以↑淀积速率。 气流速率持续↑,淀积速率达到一个极大值,与气 流速率无关。 气流速率大到一定程度,淀积速率转受表面化学反 应速率控制,且与温度遵循指数关系。

薄膜淀积速率G=

F1 N1

第六章 薄膜淀积

低温,快速淀积,好的 台阶覆盖能力,好的间 隙填充能力

要求 RF 系统,高成 本,压力远大于张力, 化学物质(如 H2)和 颗粒沾污

高的深宽比间隙的填充, 金属上的 SiO2,ILD-1,ILD, 为了双镶嵌结构的铜籽晶 层,钝化( Si3N4).

连续加工的APCVD 反应炉

反应气体 1 惰性分隔气体 膜 反应气体 2 硅片

p+ silicon substrate

引

言

从MSI到LSI时代,芯片的设计和加工相对较 为直接,上图给出了制作一个早期 CMOS所需的淀 积层。图中器件的特征尺寸远大于 1µm。如图所 示,由于特征高度的变化,硅片上各层并不平坦 ,这将成为VLSI时代所需的多层金属高密度芯片 制造的限制因素。 随着特征尺寸越来越小,在当今的高级微芯 片加工过程中,需要 6 层甚至更多的金属来做连 接 , 各金属之间的绝缘就显得非常重要,所以, 在芯片制造过程中,淀积可靠的薄膜材料至关重 要。薄膜制备是硅片加工中的一个重要工艺步骤 。

优点

缺点

台阶覆盖能力差, 有颗粒沾污 低产出率 高温,低的淀积速率, 需要更多的维护,要求 真空系统支持

应用

低温二氧化硅 (掺杂或不掺杂).

LPCVD (低压 CVD) 等离子体辅助 CVD: 等离子体增强 CVD (PECVD) 高密度等离子体 CVD (HDPCVD)

高温二氧化硅 (掺杂或不 掺杂),氮化硅、多晶硅等

p-well p- Epitaxial layer

p+ Silicon substrate

• 用TEOS-O3淀积SiO2

TEOS 是正硅酸乙脂。分子式为 Si(C2H5O4) , 是一种液体。臭氧(O3)包含三个氧原子,比氧气 有更强的反应活性,因此,这步工艺可以不用等离 子体,在低温下(如 400℃)进行,因为不需要等 离子体,O3就能是TEOS分解,因此反应可以在常 压( APCVD,760 托)或者亚常压 (SACVD , 600 托 ) 下。淀积的二氧化硅薄膜改善了台阶覆盖轮廓,均 匀性好,具有作为绝缘介质优异的电学特性。 优点:对于高的深宽比槽有良好的覆盖填充能力。 缺点: SiO2 膜多孔,因而通常需要回流来去掉潮气 并增加膜密度。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

在更低的反应温度和压力下,由于只有更 少的能量来驱动表面反应,表面反应速度会降 低。最终反应物达到硅片表面的速度将超过表 面化学反应的速度。在这种情况下。淀积速度 是受化学反应速度限制的,此时称表面反应控 制限制。

CVD 气流动力学

CVD气流动力学对淀积出均匀的膜很重要。 所谓气体流动,指的是反应气体输送到硅片表 面的反应区域(见下图)。CVD气体流动的主 要因素包括,反应气体从主气流中到硅片表面 的输送以及在表面的化学反应速度。

p+ Silicon substrate

芯片中的金属层

薄膜淀积

半导体器件工艺中的“薄膜”是一种 固态薄膜。 薄膜淀积是指任何在硅片衬底上物理 淀积一层膜的工艺,属于薄膜制造的一种 工艺,所淀积的薄膜可以是导体、绝缘材 料或者半导体材料。比如二氧化硅(SiO2 )、氮化硅(Si3N4)、多晶硅以及金属( Cu、W).

p-well p- Epitaxial layer

p+ Silicon substrate

• 用TEOS-O3淀积SiO2

TEOS 是正硅酸乙脂。分子式为 Si(C2H5O4) , 是一种液体。臭氧(O3)包含三个氧原子,比氧气 有更强的反应活性,因此,这步工艺可以不用等离 子体,在低温下(如 400℃)进行,因为不需要等 离子体,O3就能是TEOS分解,因此反应可以在常 压( APCVD,760 托)或者亚常压 (SACVD , 600 托 ) 下。淀积的二氧化硅薄膜改善了台阶覆盖轮廓,均 匀性好,具有作为绝缘介质优异的电学特性。 优点:对于高的深宽比槽有良好的覆盖填充能力。 缺点: SiO2 膜多孔,因而通常需要回流来去掉潮气 并增加膜密度。

p+ silicon substrate

引

言

从MSI到LSI时代,芯片的设计和加工相对较 为直接,上图给出了制作一个早期 CMOS所需的淀 积层。图中器件的特征尺寸远大于 1µm。如图所 示,由于特征高度的变化,硅片上各层并不平坦 ,这将成为VLSI时代所需的多层金属高密度芯片 制造的限制因素。 随着特征尺寸越来越小,在当今的高级微芯 片加工过程中,需要 6 层甚至更多的金属来做连 接 , 各金属之间的绝缘就显得非常重要,所以, 在芯片制造过程中,淀积可靠的薄膜材料至关重 要。薄膜制备是硅片加工中的一个重要工艺步骤 。

优点

缺点

台阶覆盖能力差, 有颗粒沾污 低产出率 高温,低的淀积速率, 需要更多的维护,要求 真空系统支持

应用

低温二氧化硅 (掺杂或不掺杂).

LPCVD (低压 CVD) 等离子体辅助 CVD: 等离子体增强 CVD (PECVD) 高密度等离子体 CVD (HDPCVD)

高温二氧化硅 (掺杂或不 掺杂),氮化硅、多晶硅等

1. 产生化学变化,这可以通过化学反应或热分解; 2. 膜中所有的材料物质都源于外部的源; 3. 化学气相淀积工艺中的反应物必须以气相形式参 加反应。

化学气相淀积的设备

CVD 化学过程

1. 高温分解: 通常在无氧的条件下,通过加热化

合物分解(化学键断裂); 2. 光分解: 利用辐射使化合物的化学键断裂分解; 3. 还原反应: 反应物分子和氢发生的反应; 4. 氧化反应: 反应物原子或分子和氧发生的反应;

物理气相淀积 (PVD)或溅射

直流二极管

蒸发

旋涂方法

旋涂玻璃 s (SOG) 旋涂绝缘介 质(SOD)

灯丝和电子束

射频 (RF)

分子束外延 (MBE)

直流磁电管

离子化金属等离子 体 (IMP)

化学气相淀积

化学气相淀积( CVD )是通过气体混合的化 学反应在硅片表面淀积一层固体膜的工艺。硅片 表面及其邻近的区域被加热来向反应系统提供附 加的能量。包括以下特点:

CVD 中的气流

气流

反应物的 扩散

反应副产物

淀积的膜 硅衬底

硅片表面的气流

气流

气流

边界层

滞留层

CVD 反应中的压力 如果CVD发生在低压下,反应气体通过边 界层达到表面的扩散作用会显著增加。这会增 加反应物到衬底的输运。在CVD反应中低压的 作用就是使反应物更快地到达衬底表面。在这 种情况下,速度限制将受约于表面反应,即在 较低压下CVD工艺是反应速度限制的。 • CVD 过程中的掺杂 CVD 淀积过程中,在 SiO2 中掺入杂质对硅 片加工来说也是很重要。例如,在淀积SiO2的 过程中,反应气体中加入 PH3 后,会形成磷硅 玻璃。化学反应方程如下:

固态薄膜

厚

宽 与衬底相比 薄膜非常薄

Oxide Silicon substrate

薄膜特性

好的台阶覆盖能力

填充高的深宽比间隙的能力 好的厚度均匀性 高纯度和高密度 受控制的化学剂量 高度的结构完整性和低的膜应力 好的电学特性 对衬底材料或下层膜好的黏附性

膜对台阶的覆盖

PSG 回流后平坦化的表面

回流前

回流后

PSG

PSG

金属或多晶硅

LPCVD

与 APCVD 相比, LPCVD 系统有更低的成本、 更高的产量及更好的膜性能,因此应用更为广泛 。为了获得低压,必须在中等真空度下阿(约 0.1 ~5托),反应温度一般在300~900℃,常规的氧 化炉设备就可以应用。 LPCVD 的反应室通常是反应速度限制的。在 这种低压条件下,反应气体的质量传输不再限制 反应的速度。 不同于APCVD的是,LPCVD 反应中的边界层 由于低压的缘故,距离硅片表面更远(见下图) 。边界层的分子密度低,使得进入的气体分子很 容易通过这一层扩散,是硅片表面接触足够的反 应气体分子。一般来说, LPCVD 具有优良的台阶 覆盖能力。

1) 2) 3) SiH4(气态) SiH2(气态) + H2(气态) (高温分解) Si2H6(气态) (反应半 (最终产 SiH4(气态) + SiH2(气态) 成品形成) Si2H6(气态) 品形成)

2Si (固态) + 3H2(气态)

以上实例是硅气相外延的一个反应过程

• 速度限制阶段

在实际大批量生产中,CVD反应的时间长 短很重要。温度升高会促使表面反应速度增加 。基于CVD反应的有序性,最慢的反应阶段会 成为整个工艺的瓶颈。换言之,反应速度最慢 的阶段将决定整个淀积过程的速度。 CVD的反应速度取决于质量传输和表面反 应两个因素。在质量传输阶段淀积工艺对温度 不敏感,这意味着无论温度如何,传输到硅片 表面加速反应的反应气体的量都不足。在此情 况下,CVD工艺通常是受质量传输所限制的。

5. 氧化还原反应: 反应3与4地组合,反应后形成两

种新的化合物。

例如,用硅烷和氧气通过氧化反应 淀积 SiO2 膜。反应生成物 SiO2 淀积在硅 片表面,副产物事是氢。 SiH4 + O2 SiO2 + 2H2

CVD 反应

• CVD 反应步骤 基本的化学气相淀积反应包含8个主要步骤, 以解释反应的机制。 1)气体传输至淀积区域; 2)膜先驱物的形成; 3)膜先驱物附着在硅片表面; 4)膜先驱物黏附; 5)膜先驱物扩散; 6)表面反应; 7)副产物从表面移除; 8)副产物从反应腔移除。

低温,快速淀积,好的 台阶覆盖能力,好的间 隙填充能力

要求 RF 系统,高成 本,压力远大于张力, 化学物质(如 H2)和 颗粒沾污

高的深宽比间隙的填充, 金属上的 SiO2,ILD-1,ILD, 为了双镶嵌结构的铜籽晶 层,钝化( Si3N4).

连续加工的APCVD 反应炉

反应气体 1 惰性分隔气体 膜 反应气体 2 硅片

3. 和后续高温工艺的兼容性;

ULSI硅片上的多层金属化

钝化层

ILD-6

压点金属

ILD-5 M-4 ILD-4 M-3 ILD-3 M-2 ILD-2 M-1 Via Poly gate LI metal n+ p+ n-well p+ LI oxide STI n+ p-well n+ p+ ILD-1

p- Epitaxial layer

计算机终端 工作接口

气流控制器

LPCVD

炉温控制器

炉 三温区 加热器

压力控制器

温度控制器

尾气

真空泵

N2

O2

加热器

TEOS

Key Reasons for the Use of Doped Polysilicon in the Gate Structure

1. 通过掺杂可得到特定的电阻;

2. 和二氧化硅优良的界面特性;

深宽比

=

深度 宽度

深宽比

=

500 Å

250 Å

=

2

1

D

500 Å

W

250 Å

高的深宽比间隙

Photograph courtesy of Integrated Circuit Engineering

薄膜生长的步骤

气体分子

成核

凝聚

连续的膜

Substrate

膜淀积技术

化学工艺 化学气相淀积 (CVD)

(a) 气体注入类型

反应气体

N2 N2 N2 N2 N2 N2

硅片 加热器

(b) 通气类型

APCVD TEOS-O3改善后的台阶覆盖

Trench fill by chemical vapor deposition TEOS-O3

Trench CVD oxide Nitride

n-well

Liner oxide

硅片表面的边界层

连续气流

反应物扩散

边界层

淀积膜 硅衬底

LPCVD Reaction Chamber for Deposition of Oxides, Nitrides, or Polysilicon