数字电子与逻辑设计期末试卷A卷)

数字电子技术期末试卷标准答案及评分标准(A卷)

班级:__________ 学号: __________姓名: __________阅卷教师: _____________ 成绩: _______________一、判断题(将答案添入下表,每题1分,共10分。

正确选“√”,错误选“×”) 1 2 3 4 5 6 7 8 9101.在时间和幅度上都断续变化的信号是数字信号,因为说话时语音是断续的,所以是数字信号。

( )2.若两个函数具有不同的逻辑函数式,则两个逻辑函数必然不相等。

( ) 3.N 变量逻辑函数全部2N 个最大项之积恒等于1。

( ) 4.因为逻辑表达式A+B+AB=A+B 成立,所以AB=0成立。

( )。

5.TTL 集电极开路门输出为1时由外接电源和电阻提供输出电流。

( ) 6.异步时序电路是指的各级触发器类型不同的电路。

( )7.D 触发器的特征方程Q n+1=D ,而与Q n 无关,所以,D 触发器不是时序电路。

( ) 8.D/A 转换器的最大输出电压的绝对值可达到基准电压V REF 。

( )9.施密特触发器可用于将正弦波变换成三角波。

( )10.SRAM 是指静态RAM ,DRAM 是指动态RAM ;对相同容量的SRAM 和DRAM 而言,前者造价高,响应速度也快。

( )二、试将下列函数化为最简与或形式(10分,每题5分,要有解题步骤,否则不给分)(1)D C B A D C B A D B A AD Y +++=(2)化简逻辑函数D C B A BCD A D C B A D C B A F ⋅⋅++⋅⋅=),,,(;给定约束条件:0=+++⋅+⋅++⋅D C B A D ABC ABCD D C B A D C AB D C B A CD B A三、已知电路如图所示,写出F1、F2、F3、F 与输入变量A 、B 、C 、D 之间的逻辑表达式。

(本题10分)阅卷教师: _____________ 成绩: _______________四、设计一个能被2 或3 整除的逻辑电路,其中被除数A、B、C、D是8421BCD编码。

电子科技大学期末数字电子技术考试题a卷-参考答案

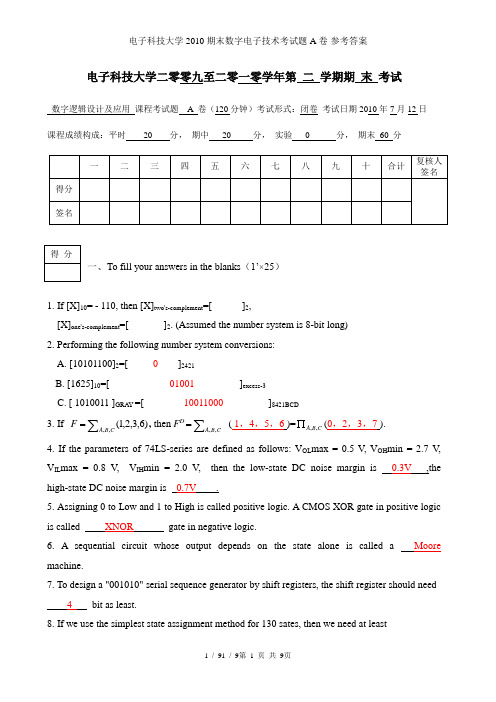

电子科技大学二零零九至二零一零学年第 二 学期期 末 考试数字逻辑设计及应用 课程考试题 A 卷(120分钟)考试形式:闭卷 考试日期2010年7月12日课程成绩构成:平时 20 分, 期中 20 分, 实验 0 分, 期末 60 分一、To fill your answers in the blanks (1’×25)1. If [X]10= - 110, then [X]two's-complement =[ ]2,[X]one's-complement =[ ]2. (Assumed the number system is 8-bit long) 2. Performing the following number system conversions: A. [10101100]2=[ 0 ]2421B. [1625]10=[01001 ]excess-3C. [ 1010011 ]GRAY =[10011000 ]8421BCD3. If ∑=C B A F ,,)6,3,2,1(, then F D ∑=C B A ,,( 1,4,5,6 )=C B A ,,∏(0,2,3,7 ).4. If the parameters of 74LS-series are defined as follows: V OL max = 0.5 V , V OH min = 2.7 V , V IL max = 0.8 V , V IH min = 2.0 V , then the low-state DC noise margin is 0.3V ,the high-state DC noise margin is 0.7V .5. Assigning 0 to Low and 1 to High is called positive logic. A CMOS XOR gate in positive logic is called XNOR gate in negative logic.6. A sequential circuit whose output depends on the state alone is called a Moore machine.7. To design a "001010" serial sequence generator by shift registers, the shift register should need 4 bit as least.8. If we use the simplest state assignment method for 130 sates, then we need at least8state variables.9. One state transition equation is Q*=JQ'+K'Q. If we use D flip-flop to complete the equation, the D input terminal of D flip-flop should be have the function D= JQ'+K'Q.10.Which state in Fig. 1 is ambiguous D11.A CMOS circuit is shown as Fig. 2, its logic function z= A’B’+ABFig. 1 Fig. 212.If number [A]two's-complement =01101010 and [B]one's-complement =1001, calculate [A-B]two's-complement and indicate whether or not overflow occurs.(Assumed the number system is 8-bit long)[A-B]two's-complement = 01110000, overflow no13. If a RAM’s capacity is 16K words × 8 bits, the address inputs should be 14bits; We need 8chips of 8K ⨯8 bits RAM to form a 16 K ⨯ 32 bits ROM..14. Which is the XOR gate of the following circuit A .15.There are 2n-n invalid states in an n-bit ring counter state diagram.16.An unused CMOS NOR input should be tied to logic Low level or 0 .17.The function of a DAC is translating the Digital inputs to the same value of analogoutputs.二、Complete the following truth table of taking a vote by A,B,C, when more than two of A,B,C approve a resolution, the resolution is passed; at the same time, the resolution can’t go through if A don’t agree.For A,B,C, assume 1 is indicated approval, 0 is indicated opposition. For the F,A B C F三、The circuit to the below realizes a combinational function F of four variables. Fill in the Karnaugh map of the logic function F realized by the multiplexer-based circuit. (6’)四、(A) Minimize the logic function expressionF = A·B + AC’ +B’·C+BC’+B’D+BD’+ADE(H+G) (5’)F = A·B + AC’ +B’·C+BC’+B’D+BD’ = A·(B ’C )’ +B’·C+BC’+B’D+BD’= A +B’·C+BC’+B’D+BD’+C ’D (或= A +B’·C+BC’+B’D+BD’+CD ’)= A +B’·C+BD’+C ’D (或= A + BC’+B’D +CD ’)(B) To find the minimum sum of product for F and use NAND-NAND gates to realize it (6’)),,,(Z Y X W F Π(1,3,4,6,9,11,12,14)------3分 F= X ’Z ’+XZ -----2分 =( X ’Z ’+XZ)’’=(( X ’Z ’)’(XZ)’)’ ------1分五、Realize the logic function using one chip of 74LS139 and two NAND gates.(8’)∑=)6,2(),,(C B A F ∑=)3,2,0(),,(E D C GF(A,B,C)=C’∑(1,3) ---- 3分 G(C,D,E)=C’∑(0,2,3) ----3分-六、Design a self-correcting modulo-6 counter with D flip-flops. Write out the excitation equations and output equation. Q2Q1Q0 denote the present states, Q2*Q1*Q0* denote the next states, Z denote the output. The state transition/output table is as following.(10’)Q2Q1Q0Q2*Q1*Q0*Z000 100 0100 110 0110 111 0111 011 0011 001 0001 000 1激励方程式:D2=Q0’(2分,错-2分)D1=Q2 (2分,错-2分)D0=Q1 (2分,错-2分)修改自启动:D2=Q0 +Q2Q1’(1分,错-1分)D1=Q2+Q1Q0’(1分,错-1分)D0=Q1+Q2Q0 (1分,错-1分)输出方程式:Z=Q1’Q0 (1分,错-1分)得分七、Construct a minimal state/output table for a moore sequential machine, that will detect the input sequences: x=101. If x=101 is detected, then Z=1.The input sequences DO NOT overlap one another. The states are denoted with S0~S3.(10’)For example:X:0 1 0 1 0 0 1 0 1 0 1 1 0 1 1 0 0 0 1 1 ……Z:0 0 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0 ……state/output table八、Please write out the state/output table and the transition/output table and theexcitation/output table of this state machine.(states Q2 Q1=00~11, use the state name A~D )(10’)Transition/output table State/output table Excitation/output table(4分) (3分) (3分)评分标准:转移/输出表正确,得4分;每错一处扣0.5分,扣完4分为止;由转移/输出表得到状态/输出表正确,得3分;每错一处扣0.5分,扣完3分为止;激励/输出表正确,得3分;每错一处扣0.5分,扣完3分为止。

电子技术及数字逻辑试卷A及答案

绝密★启用前黑龙江外国语学院继续教育学院 2014 年 秋 季学期《电子技术及数字逻辑》试卷( A 卷)一、 填空题(本大题共 9小题,每空 1分,共 15分)1.N 型半导体是在本征半导体中掺入 价元素,其多数载流子是 ,少数载流子是 。

2.稳压管的稳压区是其工作在 。

3.数字系统使用 的物理元件,与此相对应,采用的记数制和编码制也都以 数 为基础。

4.使用布尔代数定律时,利用 规则. 规则. 规则可得到更多的公式。

5.放大电路必须加上合适的 才能正常工作。

6.运放的共模抑制比定义为 。

7.直接写出函数F=[(AB+C)D+E]B 的反演函数为 。

8.三极管工作在饱和区时,发射结应为 偏置,集电结应为 偏置。

9.为提高放大电路的输入电阻,应引入 反馈;为降低放大电路输出电阻。

二、选择题(本大题共15小题,每题2分,共30分)1.当温度升高时,二极管的反向饱和电流将 。

A .增大 B.减小 C.不变2.互补输出级采用共集形式是为了使 。

A.电压放大倍数大B.不失真输出电压大C.带负载能力强3.测试放大电路输出电压幅值与相位的变化,可以得到它的频率响应,条件是 。

A. 输入电压幅值不变,改变频率B. B.输入电压频率不变,改变幅值C.输入电压的幅值与频率同时变化 4.交流负反馈是指 。

A .阻容耦合放大电路中所引入的负反馈B .只有放大交流信号时才有的负反馈C .在交流通路中的负反馈5.功率放大电路的最大输出功率是在输入电压为正弦波时,输出基本不失真情况下,负载上可能获得的最大 。

A .交流功率B .直流功率C .平均功率 6.滤波电路应选用 。

A .高通滤波电路 B. 低通滤波电路 C. 带通滤波电路7.放大电路中,测得某三极管三个电极电位U 1.U 2.U 3分别为U 1=3.3V ,U 2=2.6V ,U 3=15V 。

由此可判断该三极管为 。

A .NPN 硅管 B. NPN 锗管 C. PNP 硅管 d.PNP 锗管8.与八进制数(47.3)8等值的数为 。

第一学期《数字电子技术》课程期末考试试卷A和答案数字电路与逻辑设计

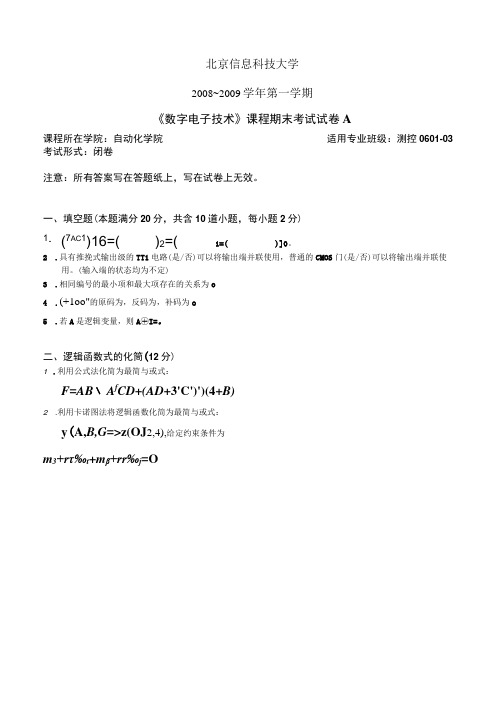

北京信息科技大学2008~2009学年第一学期《数字电子技术》课程期末考试试卷A课程所在学院:自动化学院适用专业班级:测控0601-03考试形式:闭卷注意:所有答案写在答题纸上,写在试卷上无效。

一、填空题(本题满分20分,共含10道小题,每小题2分)1∙(7AC1)16=( )2=( 1=( )]0。

2.具有推挽式输出级的TT1电路(是/否)可以将输出端并联使用,普通的CMOS门(是/否)可以将输出端并联使用。

(输入端的状态均为不定)3.相同编号的最小项和最大项存在的关系为o4.(+1oo"的原码为,反码为,补码为o5.若A是逻辑变量,则A㊉I=。

二、逻辑函数式的化筒(12分)1 .利用公式法化简为最简与或式:F=AB∖A f CD+(AD+3'C')')(4+B)2 .利用卡诺图法将逻辑函数化简为最简与或式:y(A,B,G=>z(OJ2,4),给定约束条件为m3+rτ‰t+mβ+rr‰j=O下面电路图中,写出输出信号是什么状态(高电平、低电平或高阻态),已知乂为74系四、试用一片8选1数据选择器74HC151产生逻辑函数:Y=AB r CD÷48(C÷r>)+ABXCΦZ))÷ABC r 要求给出设计的全过程,并画出逻辑电路图。

(12分)s ,A2A4YO O O OO O O1O∣O O1O D1O O11O1O OO1O1/人O11O2O11151X X X高阻五、TT1主从JK触发器的输入波形如图所示,画出输出端Q的波形(12分)CP六、分析如图时序逻辑电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,说明电路的功能以及能否自启动。

(14分)CP七、 试用一片4位同步二进制计数器741S163接成十进制计数器(允许附加必要的门电路,采用清零法),并作简要说明。

741S163的引脚图如下所示。

期末考试数字电子技术试题及答案(DOC)

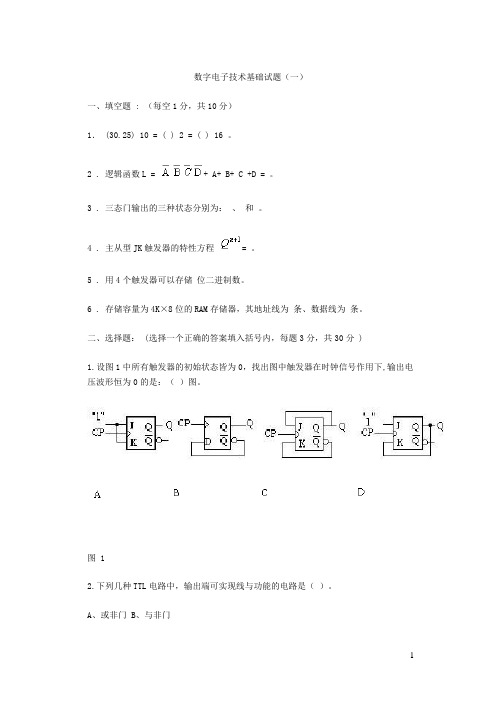

数字电子技术基础试题(一)一、填空题 : (每空1分,共10分)1. (30.25) 10 = ( ) 2 = ( ) 16 。

2 . 逻辑函数L = + A+ B+ C +D = 。

3 . 三态门输出的三种状态分别为:、和。

4 . 主从型JK触发器的特性方程= 。

5 . 用4个触发器可以存储位二进制数。

6 . 存储容量为4K×8位的RAM存储器,其地址线为条、数据线为条。

二、选择题: (选择一个正确的答案填入括号内,每题3分,共30分 )1.设图1中所有触发器的初始状态皆为0,找出图中触发器在时钟信号作用下,输出电压波形恒为0的是:()图。

图 12.下列几种TTL电路中,输出端可实现线与功能的电路是()。

A、或非门B、与非门C、异或门D、OC门3.对CMOS与非门电路,其多余输入端正确的处理方法是()。

A、通过大电阻接地(>1.5KΩ)B、悬空C、通过小电阻接地(<1KΩ)D、通过电阻接V CC4.图2所示电路为由555定时器构成的()。

A、施密特触发器B、多谐振荡器C、单稳态触发器D、T触发器5.请判断以下哪个电路不是时序逻辑电路()。

图2A、计数器B、寄存器C、译码器D、触发器6.下列几种A/D转换器中,转换速度最快的是()。

图2A、并行A/D转换器B、计数型A/D转换器C、逐次渐进型A/D转换器D、双积分A/D转换器7.某电路的输入波形 u I 和输出波形 u O 如图 3所示,则该电路为()。

图3A、施密特触发器B、反相器C、单稳态触发器D、JK触发器8.要将方波脉冲的周期扩展10倍,可采用()。

A、10级施密特触发器B、10位二进制计数器C、十进制计数器D、10位D/A转换器9、已知逻辑函数与其相等的函数为()。

A、B、C、D、10、一个数据选择器的地址输入端有3个时,最多可以有()个数据信号输出。

A、4B、6C、8D、16三、逻辑函数化简(每题5分,共10分)1、用代数法化简为最简与或式Y= A +2、用卡诺图法化简为最简或与式Y= + C +A D,约束条件:A C + A CD+AB=0四、分析下列电路。

《数字逻辑》期末考试A卷参考答案

《数字逻辑》期末考试 A 卷参考答案

一、判断题:下面描述正确的打‘√’,错误的打‘×’ (每小题1 分,共 10 分)

1、为了表示 104 个信息,需 7位二进制编码 [√ ]

2、 BCD码能表示0 至 15 之间的任意整数[× ]

3、余 3码是有权码[× ]

4、 2421 码是无权码 [ × ]

5、二值数字逻辑中变量只能取值0 和 1,且表示数的大小 [ × ]

6、计算机主机与鼠标是并行通信[× ]

7、计算机主机与键盘是串行通信[√ ]

8、占空比等于脉冲宽度除于周期[√ ]

9、上升时间和下降时间越长,器件速度越慢

10、卡诺图可用来化简任意个变量的逻辑表达式[√]

[×]

二、写出图中电路的逻辑函数表达式。

(每小题 5 分,共10 分)

1、 F=A B

2、 F=AB CD

三、选择题:(多选题,多选或少选不得分,每小题 2 分,共 20 分)。

济南大学数字电子技术期末考AB卷及参考答案

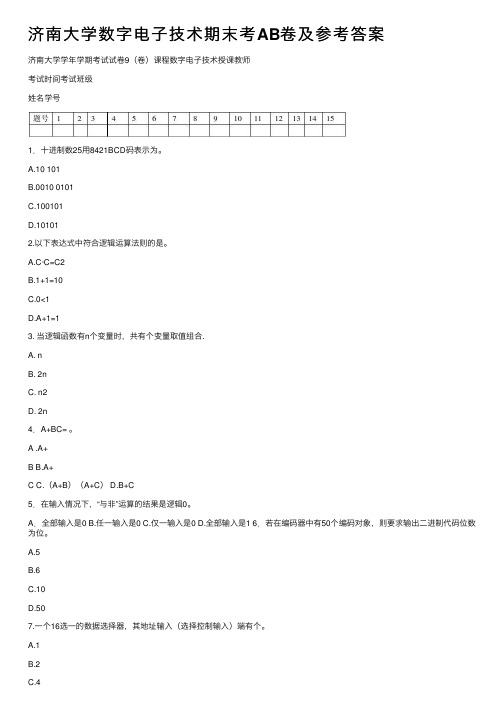

济南⼤学数字电⼦技术期末考AB卷及参考答案济南⼤学学年学期考试试卷9(卷)课程数字电⼦技术授课教师考试时间考试班级姓名学号1.⼗进制数25⽤8421BCD码表⽰为。

A.10 101B.0010 0101C.100101D.101012.以下表达式中符合逻辑运算法则的是。

A.C·C=C2B.1+1=10C.0<1D.A+1=13. 当逻辑函数有n个变量时,共有个变量取值组合.A. nB. 2nC. n2D. 2n4.A+BC= 。

A .A+B B.A+C C.(A+B)(A+C) D.B+C5.在输⼊情况下,“与⾮”运算的结果是逻辑0。

A.全部输⼊是0 B.任⼀输⼊是0 C.仅⼀输⼊是0 D.全部输⼊是1 6.若在编码器中有50个编码对象,则要求输出⼆进制代码位数为位。

A.5B.6C.10D.507.⼀个16选⼀的数据选择器,其地址输⼊(选择控制输⼊)端有个。

A.1B.2C.4D.168.四选⼀数据选择器的数据输出Y与数据输⼊Xi和地址码Ai之间的逻辑表达式为Y= 。

A.3XAAXAAXAAXAA121111+++ B.1X C.11XAA D.3XAA19.在下列逻辑电路中,不是组合逻辑电路的有。

A.译码器B.编码器C.全加器D.寄存器10.⽤三线-⼋线译码器74LS138和辅助门电路实现逻辑函数122AAAY+=,应。

A.⽤与⾮门,76541YYYYYYY= B.⽤与门,32YYY=C.⽤或门,32YYY+= D.⽤或门,76541YYYYYYY+++++=11.⼀位8421BCD码计数器⾄少需要个触发器。

A.3B.4C.5D.1012.⼀个容量为1K×8的存储器有个存储单元。

A.8B.8KC.8000D.819213.⼀个容量为512×1的静态RAM具有。

A.地址线9根,数据线1根B.地址线1根,数据线9根C.地址线512根,数据线9根D.地址线9根,数据线512根14.图1⽰为采⽤共阴极数码管的译码显⽰电路,若显⽰码数是2,译码器输出端应为。

大学数字电路与逻辑设计考试试题

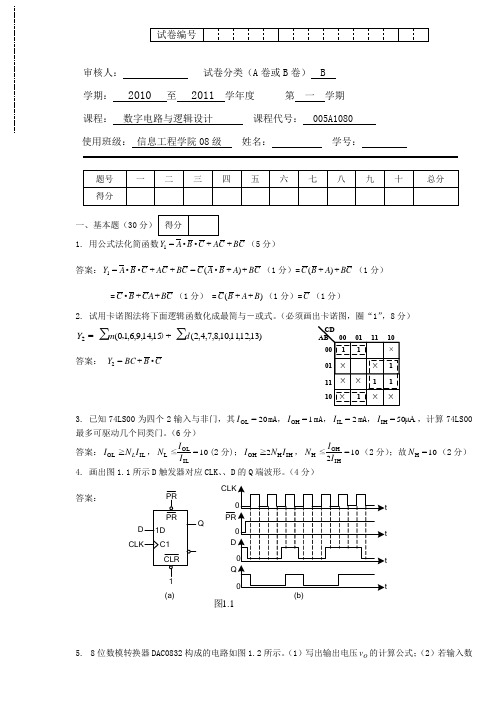

审核人: 试卷分类(A 卷或B 卷) B 学期: 2010 至 2011 学年度 第 一 学期 课程: 数字电路与逻辑设计 课程代号: 005A1080 使用班级: 信息工程学院08级 姓名: 学号:一、基本题(301. 用公式法化简函数C BC A C B A Y ++••=1(5分)答案:C B A B A C C B C A C B A Y +)+•(=++••=1(1分)=C B A B C +)+((1分) =C B A C B C ++•(1分) =)++(B A B C (1分)=C (1分)2. 试用卡诺图法将下面逻辑函数化成最简与-或式。

(必须画出卡诺图,圈“1”,8分)∑∑)13,12,11,10,8,7,4,2(+15,14,9,6,10(=2d m Y ),答案: C B BC Y •+=23. 已知74LS00为四个2输入与非门,其20=OL I mA ,1=OH I mA ,2=IL I mA ,μA 50=IH I ,计算74LS00最多可驱动几个同类门。

(6分)答案:IL OL ≥I N I L ,10=≤IL OL L I I N (2分);IH H OH 2≥I N I ,10=2≤IH OH H I IN (2分);故10=H N (2分)4. 画出图1.1所示D 触发器对应CLK 、、D 的Q 端波形。

(4分)答案:AB CD0001111010001101111111××××××××1.1图Q PR PR(a)字量为100000时,输出模拟电压O v 为3.6V ,计算输入数字量为10101000时,输出电压时多少?(7分) 答案:(1)=O v -ii i D V 22∑78REF (3分) (2)=6.3-78REF2×2V ;=REFV -7.2V (2分)输入数字量为10101000时, =O v -V 725.4=)2+2+2(22.73578(2分)二(10分)、图2(a )由集成3线-8线译码器74HC138构成的逻辑电路,试分析其逻辑功能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

湖州师范学院求真学院 2010 — 2011学年第 二 学期

《数字电子与逻辑设计》期末考试试卷(A 卷)

适用班级 102831/102832 考试时间 120 分钟

学院 班级 学号 姓名 成绩

一、(每小题3分,共27分)选择题

1.下列四个数中与十进制数(163)10不相等的是 。

(A )(A3)16 (B )(10100011)2 (C )(000101100011)8421BCD (D )(100100011)8 2.将TTL 与非门作非门使用,则多余输入端应做 处理。

(A )全部接高电平 (B )部分接高电平,部分接地 (C )全部接地 (D )部分接地,部分悬空

3.由或非门构成的基本RS 触发器,输入S 、R 的约束条件是 。

(A )SR=0 (B )SR=1 (C )S+R=0 (D )S+R=1 4.T 触发器,在T=1时,加上时钟脉冲,则触发器 。

(A )保持原态 (B )置0 (C )置1 (D )翻转 5.下列等式不成立的是 。

(A )B A B A A +=+

(B )BC A C A B A +=++))(( (C )BC AB BC C A AB +=++ (D )1=+++B A AB B A B A 6.如果编码0100表示十进制数4,则此码不可能是( )。

(A.) 8421BCD 码 (B.) 5421BCD 码 (C.) 2421BCD 码 (D.) 余3码

7.下逻辑图的逻辑表达式为( )。

(A )Y=AB·CD (B) Y=AB+CD (C) Y=AB+CD (D) Y= AB·CD 8.下列关于异或运算的式子中,不正确的是( )。

(A.) A ⊕A = 0 (B.) A ⊕A = 1 (C.) A ⊕0 = A (D.) A ⊕1 = A 9.标准与或是是由( )构成的逻辑表达式。

(A.)与项相或 (B.) 最小项相或 (C.) 最大项相与 (D.) 或项相与

二、(14分)如图所示为一工业用水容器示意图,图中虚线表示水位,A 、B 、C 电极被水浸没时会有信号输出,试用与非门构成的电路来实现下述控制作用:水面在A 、B 间,为正常状态,亮绿灯G ;水面在B 、

C 间或在A 以上为异常状态,点亮黄灯Y ;水面在C 以下为危险状态,

点亮红灯R 。

要求用最少的与非门画出逻辑电路图。

A

B C

三、(12分)电路如图所示,请画出在输入信号作用下,对应的输出Q1,Q2,L3的波形。

(设触发器均为边沿触发器,且初态为0)

四、(9分)试画出用3线—8线译码器74HC138和门电路产生如下多

输出逻辑函数的逻辑图。

B

“1” C C

A

B

C

Q1

Q2

L3

1D

C1

A

Q2

Q2

=

1J

C1

A

Q1

Q1

1K

1

B

C

五、(8分)试写出该电路的逻辑表达式。

得分

A

1

2

3

B

C D 1 2 3 4 5 6 7 8 9 10 1 2 3

4 5 6

7 8 9

10 11 12

1 2 3 4 5 6 7 8 9 10

六、(15分)译码器真值表如下表所示,试用74HC138实现该译码器。

真值表

选择输入

D C B A

译码输出0 1 2

3 4 5 6 7 8 9

0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1

0 1 0 0

1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 0 1 1 1 1 1 1 1 1 1

1 0 1 1 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 0

七、(15分)分析下图,写出各触发器的激励方程、电路的状态方程

和输出方程,画出状态表和状态图,概述电路的逻辑功能。