微机原理与接口技术(1)

《微机原理与接口技术》试题及答案(一)

《微机原理与接口技术》试题及答案(一)微机原理与接口技术这一门课程大家有把握应对考试了吗?下面是为大家推荐一些微机原理与接口技术试题及答案,希望大家有用哦。

一、填空。

(30分1分/空)1.符号数-8192的补码用十六进制数表示为E000H。

2.8位补码数CBH的真值用十进制表示为-53。

3.十进制数1025所对应的十六进制数为401H;所对应的压缩BCD数为1025H;所对应的ASCII码为31303235。

4.将8为无符号数A2H扩展为16位形式,则应为00A2H;将8为补码数F3H扩展为16位形式,则应为FFF3H。

5.在8086/8088的通用寄存器AX、BX、CX、DX中,用作存储器间址的寄存器为BX;用作I/O端口间址的寄存器为DX;用作循环控制指令(LOOP)的寄存器为CX。

6.8086/8088有4段寄存器。

其中用来存放数据段段首地址的段寄存器为DS;用来存放代码段段首地址的段寄存器为CS;用来存放堆栈段段首地址的段寄存器为SS。

7.若DS=095FH时,物理地址是11820H。

当DS=2F5FH时,物理地址为37820H。

8.8086/8088微处理器堆栈的伸展方向是高地址向低地址。

堆栈的操作是以字为单位进行的。

9.AX中有一个负数,欲求其绝对值,若该数为补码,则用指令NEGAX;若该数为原码,则用指令ANDAX,7FFFH。

在循环程序设计中,对于控制循环的DECCX和JNZAGAIN两条语句可合并用一条语句LOOPAGAIN代替。

10.写出执行下列程序段的中间结果:MOVAX,0809HMOVDL,10XCHGAH,DLMULAH;AX=005AHAAM;AX=0900HADDAL,DL;AX=0908H11.现要用6116(2K×8位)静态RAM芯片构成8K×32位的存储器,共需此种芯片16片。

12.8086/8088微处理器对I/O设备的管理是利用IN和OUT指令来实现的。

微机原理与接口技术试题

一、单选题(一) CPU1、8086CPU的指令队列为 ( ) 个字节。

CA 2B 4C 6D 82、标志寄存器的标志位ZF=1表示运算结果()。

AA为零 B 为负 C 不为零 D 有进位3、如果算术或逻辑运算结果不为0,则()。

AA ZF=0B ZF=1C SF=0D SF=14、在8086CPU的延长总线周期中,在()状态之后插入Tw状态。

CA T1B T2C T3D T44、8086/8088读/写总线周期,微处理器是在()状态采样READY信号,以便决定是否插人Tw。

CA T1B T2C T3D T45、8086CPU可插入()DA 1个等待周期B 2个等待周期C 3个等待周期D 任意多个等待周期6、关于8086CPU的非可屏蔽中断,下列说法正确的是()。

CA受中断允许标志IF的影响 B 可用软件屏蔽C 对应的中断类型号为2D 在整个系统中可以有多个7、8086CPU有16根数据线和20根地址线,故可寻址的最大地址空间为()。

BA 64KB B 1MBC 1KBD 64MB8、对可编程接口芯片进行读/写操作的前提条件是 ( )。

BA RD=0B CS=0C WR=0或RD=0D WR=012、如果允许CPU接收可屏蔽中断请求,则标志位()。

AA IF=1B IF=0C CF=1D CF=013、8086CPU要求复位信号RESET至少维持()个时钟周期的高电平。

BA 2B 4C 5D 614、()是微型计算机的核心。

AA CPUB RAMC ROMD 内存15、8086CPU复位时,代码寄存器CS和指令指针寄存器IP分别初始化为()。

CA 0000H,0000HB 0000H,FFFFHC FFFFH,0000HD FFFFH,FFFFHM/为高电平,表示()。

B16、在最小模式下,如果8086CPU的引脚IOA CPU和I/O接口之间进行数据传输B CPU和存储器之间进行数据传输C 存储器和存储器之间进行数据传输D 存储器和I/O接口之间进行数据传输17、关于8086CPU 的信号INTA ,下列说法正确的是( )。

微机原理和接口技术第一、二章作业和答案

8. 两个不压缩BCD码分别存放在3000H和 3001H单元的低4位,高4位均为0。将两个不 压缩的BCD码组合成为一个压缩的BCD码, 前者放在低4位,后者放在高4位,存放在 3002H单元。例如初值为: (3000H)=07H, (3001H)=05H, 要求结果为(3002H)=57H 9. 将4000H和4001H单元的两个ASCII码分别转 换为相应的十六进制数,然后共同存放在 4002H单元,前者放在低4位,后者放在高4 位。例如初值为: (4000H)=42H=‘B’, (4001H)=36H=‘6’, 要求结果为(4002H)=6BH

10. 微机某内存单元的内容为C5H,若它表示的是一个 无符号数,该数对应的十进制数是多少?若它表示 的是一个带符号数,该数对应的十进制数是多少?

3

11. 将下列十进制数分别转化为二进制数(保留4位小 数)、十六进制数(保留4位小数)和压缩BCD数

(1)125.74 1)101011.101 3)1001.11001 1)5A.26 3)6AB.24 (2)513.85 2)110110.1101 4)100111.0101 2)143.B5 4)E2F3.2C (3)742.24

24

3-3、试编写求两个无符号双字长数之和的程序。两数 分别放在MEM1和MEM2单元中,和放在SUM单元 中 3-4、假设数据项定义如下: DATA1 DB ‘HELLO! GOOD MORNING!’ DATA2 DB 20 DUP(?) 用串操作指令编写程序段,使其分别完成以下功能: (1)从左到右将DATA1的字符串传送到DATA2中 (2)传送完后,比较DATA1和DATA2中的内容是否 相同 (3)把DATA1中的第3和第4个字节装入AX (4)把AX的内容存入DATA2+5开始的字节单元中。 25

微机原理及接口技术第一章概述

三、微型计算机的分类

按处理器同时处理数据的位数或字长分:

8位机

按其结构分:

16位机

32位机

64位机

PC机、

单片微型机、 单板微型机

1.2

微型计算机组成

现代计算机结构仍然是在冯· 诺依曼提出 的计算机逻辑结构和存储程序概念基础上建 立起来的。

一、微型计算机的硬件结构

微型计算机由微处理器、存储器、输入/输 出接口构成,它们之间由系统总线连接。

地址总线 (AB)

只读存储器 ROM 随机存储器 RAM

I/O接口

I/O设备 数据总线 (DB) 控制总线 (CB)

CPU

1. 微处理器

整个微机的核心是微处理器(up, MPU),也 称CPU。它包含算术逻辑部件ALU、寄存器组 及控制部件。

ALU : 算术运算、逻辑运算

寄 存 器:存放操作数、中间结果、地址、标 志等信息 控制部件:整个机器控制中心,包括程序计 数器IP、指令寄存器IR、指令译 码器ID、控制信息产生电路。

外部设备

I/O接口电路

存储器 RAM ROM 总线

控制部件

算术逻辑部件

寄存器组

MPU

2. 存储器 微机的存储器分为:主存和辅存 主存(内存):用于存放当前正在运行的程序和正 待处理数据。(CPU内部cache,主 板上的内存, 造价高,速度快,存 储容量小) 辅存(外存):存放暂不运行的程序和输入处理的 数据,(主机箱内或主机箱外,造 价低,容量大,可长期保存,但 速度慢)

办公自动化

信息高速公路

仪器仪表

将传感器与计算机集 成于同一芯片上,智能

传感器不仅具有信号检

测、转换功能,同时还 具有记忆、存储、解析、 统计、处理及自诊断、 自校准、自适应等功能。

微机原理与接口技术课后习题答案[1]

![微机原理与接口技术课后习题答案[1]](https://img.taocdn.com/s3/m/41c342c02cc58bd63186bdb5.png)

1 思考与练习题一、选择题1.计算机硬件中最核心的部件是( )。

CA.运算器B.主存储器C.CPUD.输入/输出设备2.微机的性能主要取决于( )。

A(B——计算机数据处理能力的一个重要指标)A.CPUB.主存储器C.硬盘D.显示器3.计算机中带符号数的表示通常采用( )。

CA.原码B.反码C.补码D.BCD码4.采用补码表示的8位二进制数真值范围是( )。

CA.-127~+127B.-1 27~+128C.-128~+127D.-128~+1285.大写字母“B”的ASCII码是( )。

BA.41HB.42HC.61HD.62H6.某数在计算机中用压缩BCD码表示为10010011,其真值为( )。

CA.10010011BB.93HC.93D.147二、填空题1.微处理器是指_CPU_;微型计算机以_CPU_为核心,配置_内存和I/O接口_构成;其特点是_(1)功能强 (2)可靠性高 (3)价格低 (4)适应性强 (5)体积小 (6)维护方便_。

P8 P52.主存容量是指_RAM和ROM总和_;它是衡量微型计算机_计算机数据处理_能力的一个重要指标;构成主存的器件通常采用_DRAM和PROM半导体器件_。

P5 P93.系统总线是_CPU与其他部件之间传送数据、地址和控制信息_的公共通道;根据传送内容的不同可分成_数据、地址、控制_3种总线。

P94.计算机中的数据可分为_数值型和非数值型_两类,前者的作用是_表示数值大小,进行算术运算等处理操作_;后者的作用是_表示字符编码,在计算机中描述某种特定的信息_。

P125.机器数是指_数及其符号在机器中加以表示的数值化_;机器数的表示应考虑_机器数的范围、机器数的符号、机器数中小数点位置_3个因素。

P15 P166.ASCII码可以表示_128_种字符,其中起控制作用的称为_功能码_;供书写程序和描述命令使用的称为_信息码_。

P18 P19三、判断题1.计算机中带符号数采用补码表示的目的是为了简化机器数的运算。

微机原理与接口技术答案(含详解)

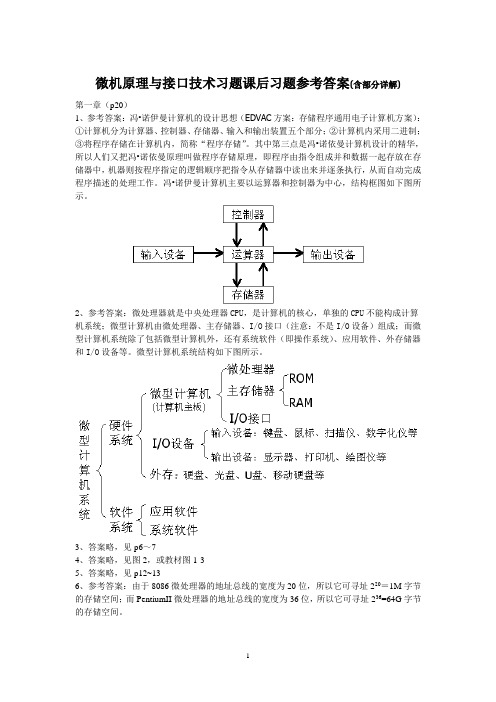

微机原理与接口技术习题课后习题参考答案(含部分详解)第一章(p20)1、参考答案:冯•诺伊曼计算机的设计思想(EDVAC方案:存储程序通用电子计算机方案):①计算机分为计算器、控制器、存储器、输入和输出装置五个部分;②计算机内采用二进制;③将程序存储在计算机内,简称“程序存储”。

其中第三点是冯•诺依曼计算机设计的精华,所以人们又把冯•诺依曼原理叫做程序存储原理,即程序由指令组成并和数据一起存放在存储器中,机器则按程序指定的逻辑顺序把指令从存储器中读出来并逐条执行,从而自动完成程序描述的处理工作。

冯•诺伊曼计算机主要以运算器和控制器为中心,结构框图如下图所示。

2、参考答案:微处理器就是中央处理器CPU,是计算机的核心,单独的CPU不能构成计算机系统;微型计算机由微处理器、主存储器、I/O接口(注意:不是I/O设备)组成;而微型计算机系统除了包括微型计算机外,还有系统软件(即操作系统)、应用软件、外存储器和I/O设备等。

微型计算机系统结构如下图所示。

3、答案略,见p6~74、答案略,见图2,或教材图1-35、答案略,见p12~136、参考答案:由于8086微处理器的地址总线的宽度为20位,所以它可寻址220=1M字节的存储空间;而PentiumII微处理器的地址总线的宽度为36位,所以它可寻址236=64G字节的存储空间。

7、参考答案:①PCI(Peripheral Component Interconnect:外围设备互联),是Intel公司1992年发布486微处理器时推出的32/64位标准总线,数据传输速率位132MB/s,适用于Pentium 微型计算机。

PCI总线是同步且独立于微处理器的具有即插即用(PNP:Plug and play,所谓即插即用,是指当板卡插入系统时,系统会自动对板卡所需资源进行分配,如基地址、中断号等,并自动寻找相应的驱动程序)的特性.PCI总线允许任何微处理器通过桥接口连接到PCI 总线上。

微机原理和接口技术第一、二章作业和答案

3-5、执行下列指令后,AX寄存器中的内容是多 少? TABLE DW 10,20,30,40, 50 ENTRY DW 3 … MOV BX, OFFSET TABLE ADD BX, ENTRY MOV AX, [BX] 3-6、假设一个48位数存放在DX:AX:BX中,试 编写程序段,将该48位数乘以2。

20

10. 将BL寄存器中的无符号数乘以128,高位放 在BH寄存器,低位放在BL寄存器,要求执 行速度尽量快(移位和循环指令实现)。 11、一个4位十进制数以压缩BCD码形式存放在 偏移地址为DATA和DATA+1的内存单元中, DATA单元存放个位和十位,DATA+1单元 存放百位和千位。要求将其转换为相应的 ASCII码,存放到以BUFF为首地址的4个内 存单元。例如初值: (DATA)=47H, (DATA+1)=92H, 要求结果为: (BUFF)=‘7’, (BUFF+1)=‘4’, (BUFF+2)=‘2’, (BUFF+3)=‘9’ 12、将立即数100推入堆栈

26

3-7、编写程序段,把从BUFFER控制的100个字节的内 存区域初始化成55H、0AAH、55H、0AAH、 ……. 55H、0AAH。 3-8、请用子程序结构编写如下程序:从键盘输入一个 二位十进制数的月份数(01~12),然后显示出相 应的英文缩写名。(交软件) 3-9、请在屏幕上显示斐波那契数列的前20个值。斐波 那契数列的定义如下: (交软件) F(0)=0 F(1)=1 F(n)=F(n-1) +F(n-2), n≥2 27

12. 将下列二进制数分别转化为十进制数和十六进制数

13. 将下列十六进制数分别转化为二进制数和十进制数

14. 求A95BH与8CA2H之和;并写出运算后标志寄存 器中SF、ZF、CF、OF、PF、AF的值。

微机原理及接口技术_1复习

二、选择(KEY)

1. D;2. B;3. C;4. A;5. C;6.B;7. D;8. D;9. D 10. C;

五、综合题 1 . 计数器/定时器8253,振荡器(频率为1MHZ)连线如 下图所示,其中振荡器的脉冲输出端接通道0的计数输入 端CLK0,设8253的端口地址为180H~186H。

请完成以下任务: (1)该电路中通道0的OUT0输出2KHZ连续方波,通道0的计 数初值为多少(写出计算式)?GATE0应接何电位?在图上画 出。(2)若要8253的OUT1端,能产生周期为1秒的连续方波, 该如何解决?在图上画出。(3)写出实现上述功能的8253初 始化程序。

计数器1:MOV DX,186H MOV AL,01110111B OUT DX,AL MOV DX,182H MOV AL,00H OUT DX,AL MOV AL,10H OUT DX,AL

2 .通过8259A产生中断使8255A的端口A经过反相驱动器连 接一共阴极七段发光二极管显示器;端口B是中断方式的输 入口。设8259A的中断类型码基值是32H。8255A口地址为 60H-63H,8259A端口地址为20H、21H。试完成以下任务:

微机原理与接口技术

(习题课)

主讲人 : 黄传波

国防科技学院

一、填空 1.MOV DL,86H ADD DL,0AAH 上述两条指令执行后,标志寄存器中各标志位和DL的 值是: DL CF= OF= AF= SF= ZF= 2.设(CS)=4000H,(SS)=6000H,(IP)=200H, 则IP所指的物理地址为 。 3.设堆栈指针(SP)=0110H,顺序执行下面三条指令 后,PUSH AX;PUSH BX;POP AX。SP的内容 是 。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1

28

2

27

3

26

4

25

5

24

6

23

7 8

8259A

22 21

9

20

10

19

11

18

12

17

13

16

14

15

VCC(+5V) A0 INTA

IR7 IR6 IR5 IR4 IR3 IR2 IR1 IR0 INT

SP/EN

CAS2

从片INT端。

图7-11a 8259A芯片引脚

02.12.2020

医学PPT

址,符合了8259A的编程要求。

注意:8086系统中数据总线为16位,CPU传送数据时,低8 位数据总线传送到偶地址端口,高8位数据总线传送到奇地 址端口。当8位I/O接口芯片与8086CPU16位数据总线相连 接时,既可以连到低8位数据总线,也可以连到高8位数据总 线。

02.12.2020

医学PPT

医学PPT

12

5.中断屏蔽寄存器IMR

中断屏蔽寄存器是一个8位寄存器,用来存放对各级中断 请求的屏蔽信息。

当用软件编程使IMR寄存器中某一位置“0”时,允许IRR寄 存器中相应位的中断请求进入中断优先级判别器。

02.12.2020

医学PPT

4

INTA: CPU给8259A的中断响应信号,输入。8259A要求两 个负脉冲的中断响应信号,第一个是CPU响应中断的信号,第 二个INTA结束后,CPU读取8259A送去的中断类型号。

SP/EN: 编程/双向使能缓冲。 作为输入使用时,用来决定本片8259A是主片还是从片: 若SP/EN=1,则为主片;若SP/EN=0,则为从片。

高阻 高阻

指令 OUT IN

高位地址译码后送CS作片选信号。

A0连地址总线A0或A1,用来选择8259A的两个I/O端口,一个为 奇地址,另一个偶地址。

读写操作由这4个信号控制来实现的,使8259A接收CPU送来的

初始化命令字和操作命令字,或将内部状态信息送给CPU。

02.12.2020

医学PPT

8

实际设计时,8259A的D7~D0与CPU数据总线低8位相连。 为了保证CPU与8259A用低8位传输数据,CPU的A1连 8259A的A0。这样对CPU来说A0=0,A1可以为1或为0, CPU读写始终是用偶地址。对8259A来说A1可以为1或为0, 给8259A的端口分配了两个地址,一个奇地址,一个偶地

02.12.2020

医学PPT

10

② 非缓冲方式:单片8259A或少量8259A级联时,可以将 8259A直接与数据总线相连,称为非缓冲方式。

非缓冲方式下,8259A的SP/EN端作输入端,控制 8259A作为主片还是从片。

SP=1,表示此8259A为主片。 SP=0,表示此8259A为从片。 单片8259A时,SP/EN接高电平。 由初始化命令字ICW4来设置缓冲方式或非缓冲方式。

3

RD:读命令信号,输入,低电平有效,用来控制数据由 8259A读到CPU。 WR: 写命令信号,输入,低电平有效,原来控制数据由 CPU写到8259A。 CS:片选信号,输入,通过译码电路与高位地址总线相连。 A0:选择8259A的两个端口,输入,连低位地址线。 INT:向CPU发出的中断请求信号,输出,与CPU的INTR端 相连。 CAS2~CAS0:双向级联信号线。8259A作主片时,为输出 线,作从片时,为输入线。与SP/EN配合实现8259A级联。

02.12.2020

医学PPT

11

4.中断请求寄存器

中断请求寄存器是一个8位寄存器,存放外部输入的中断请 求信号IR7~IR0。

当某个IR端有中断请求时,IRR相应的某位置“1”。 可以允许8个中断请求信号同时进入,此时IRR寄存器被

置成全“1”。 当中断请求被响应时,IRR的相应位复位。

02.12.2020

医学PPT

6

1. 数据总线缓冲器

数据总线缓冲器是8位双向三态缓冲器,是8259A与系统 数据总线接口,通常连接低8位数据总线D7~D0。 CPU编程控制字写入8259A、8259A的状态信息读出、 及中断响应时8259A送出的中断类型号,都经过它传送。

2. 读写控制电路

读写控制电路接收CPU送来的读/写命令RD、WR,片选信 号CS及端口选择信号A0 。

微型计算机原理与接口技术

第七章 微型计算机中断系统

02.12.2020

朱亚萍 杭州电子科技大学自动化学院

医学PPT

§7-4 可编程中断控制器 8259A

一、功能和引脚

1.主要功能

具有8级优先级控制,通过级联可以扩展到64级优先级 控制。 每一级中断可由程序单独屏蔽或允许。 可提供中断类型号传送给CPU。 可以通过编程选择多种不同工作方式。

作为输出使用时,启动8259A到CPU之间的数据总线驱 动器。

SP/EN作为输入还是输出,决定于8259A是否采用缓冲

方式工作,若采用缓冲方式工作,则SP/EN作为输出,若

采用非缓冲方式,SP/EN作为输入。

02.12.2020

医学PPTຫໍສະໝຸດ 5二、内部结构图7-11b 8259A内部结构

02.12.2020

02.12.2020

医学PPT

2

2. 引脚

D7~D0:双向数据线,

CS WR

三态,它直接或通过总 RD

线驱动器与系统的 数

D7 D6

据总线相连。

D5

IR7~IR0:外设的中断

D4 D3

请求信号输入端,输入, D2

中断请求信号可以是电

D1 D0

平触发或边沿触发。中

CAS0 CAS1

断级联时,连接8259A GND

9

3. 级联缓冲/比较器

① 缓冲方式:在多片8259A级联的系统中,8259A通过总 线驱动器和数据总线相连,这就是缓冲方式。

在缓冲方式下,8259A的SP/EN端与总线驱动器允许端 相连,控制总线驱动器启动,SP/EN作为输出端。

当EN=0时,8259A控制数据从8259A送到CPU; 当EN=1时,控制数据从CPU送到8259A。

02.12.2020

医学PPT

7

8259A的读写功能

CS RD WR A0 D4 D3 0 1 0 01× 0 1 0 1 ×× 0 1 0 000 0 1 0 001

0010 0011 1 × ×× ×1 1 ×

读写操作

CPU至ICW1 CPU至ICW2,ICW3,ICW4,OCW1 CPU至OCW2 CPU至OCW3 IRR/ISR至CPU IMR至CPU