ncverilog入门教程1

verilog教程

verilog教程Verilog是一种硬件描述语言(HDL),用于描述数字系统的行为和结构。

它是一种流行的HDL,广泛用于硬件设计和验证领域。

本教程将介绍Verilog的基本概念和语法,以帮助初学者入门。

一、Verilog的基本概念1.1 什么是VerilogVerilog是一种描述数字系统的语言,它可以用来描述硬件电路、验证设计的正确性以及进行电路仿真。

1.2 Verilog的应用领域Verilog广泛应用于硬件设计和验证领域,包括用于开发ASIC(应用特定集成电路)、FPGA(现场可编程门阵列)以及其他数字系统的设计。

1.3 Verilog的版本Verilog有多个版本,包括Verilog-1995、Verilog-2001以及最新的Verilog-2005、这些版本之间有一些语法和功能上的差异。

二、Verilog的语法结构2.1模块和端口在Verilog中,所有的电路描述都是由模块(module)组成的。

模块是电路的基本组成单元,可以看作是一个黑盒子,它接受一些输入,产生一些输出。

2.2信号声明在Verilog中,我们需要声明所有的输入和输出信号。

可以使用`input`和`output`关键字来声明这些信号。

2.3电路实现Verilog允许使用多种语句和结构来描述电路的行为和结构。

这些语句包括顺序语句、条件语句、循环语句以及层次结构。

2.4实例化模块在一个模块中,我们可以实例化其他的模块。

这样可以将一个大的电路拆分成多个小的模块,方便编写和测试。

三、Verilog的仿真和验证3.1静态验证Verilog语言本身提供了很多语法和语义层面的验证功能,对于语法和类型错误会有相应的提示。

3.2激励设计在进行电路验证时,我们需要为输入信号提供激励。

Verilog提供了一种称为`testbench`的特殊模块,用于生成输入信号并将其应用到待验证的电路中。

3.3波形仿真在Verilog中,我们可以使用仿真器来模拟电路的行为,并生成波形图来验证电路是否按预期工作。

cadence_ldv即ncverilog安装方法

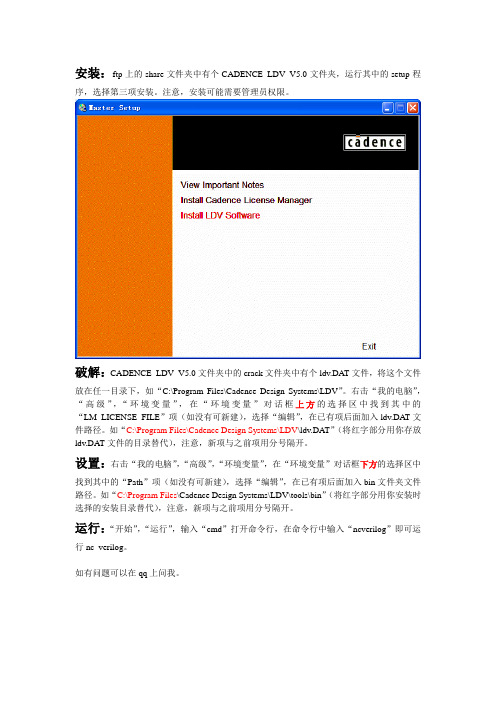

安装:ftp上的share文件夹中有个CADENCE_LDV_V5.0文件夹,运行其中的setup程

序,选择第三项安装。

注意,安装可能需要管理员权限。

破解:CADENCE_LDV_V5.0文件夹中的crack文件夹中有个ldv.DAT文件,将这个文件

放在任一目录下,如“C:\Program Files\Cadence Design Systems\LDV”。

右击“我的电脑”,“高级”,“环境变量”,在“环境变量”对话框上方的选择区中找到其中的“LM_LICENSE_FILE”项(如没有可新建),选择“编辑”,在已有项后面加入ldv.DA T文件路径。

如“C:\Program Files\Cadence Design Systems\LDV\ldv.DAT”(将红字部分用你存放ldv.DAT文件的目录替代),注意,新项与之前项用分号隔开。

设置:右击“我的电脑”,“高级”,“环境变量”,在“环境变量”对话框下方的选择区中

找到其中的“Path”项(如没有可新建),选择“编辑”,在已有项后面加入bin文件夹文件路径。

如“C:\Program Files\Cadence Design Systems\LDV\tools\bin”(将红字部分用你安装时选择的安装目录替代),注意,新项与之前项用分号隔开。

运行:“开始”,“运行”,输入“cmd”打开命令行,在命令行中输入“ncverilog”即可运行nc_verilog。

如有问题可以在qq上问我。

Ncverilog命令使用详解

Ncverilog命令使用详解NCVerilog是一种用于模拟、调试和分析Verilog和SystemVerilog 代码的命令行工具。

以下是对NCVerilog命令使用的详细解释。

1. `ncverilog`命令:启动NCVerilog编译器。

语法如下:```ncverilog [options] <file_list>```- `options`:附加的编译选项,例如`-sv`表示编译SystemVerilog 代码。

- `file_list`:包含要编译的源文件的列表。

2. `+access+r`选项:允许模拟工具读取源代码中的注释。

这对于调试和分析时非常有用。

3. `+define+<macro>`选项:定义一个宏。

这可以用于在模拟期间改变代码的行为。

例如:```+define+DEBUG```4. `+incdir+<dir>`选项:指定包含库文件的目录。

这对于使用外部库或模块时非常有用。

5. `+define+<macro>={value}`选项:为宏指定一个值。

例如:```+define+WIDTH=8```6. `+libext+<ext>`选项:指定库文件的扩展名。

可以用于指定Verilog或SystemVerilog库文件的不同扩展名。

``````8. `+vcs`选项:指定使用VCS编译器的系统Verilog代码。

这对于一些特定的系统Verilog代码可能是必需的。

9. `-y <dir>`选项:指定一个目录,其中包含其他用户定义的Verilog或SystemVerilog库文件。

10. `-v <file>`选项:指定一个要编译的单独的库文件。

11. `-f <file>`选项:指定一个包含文件列表的文件。

这可以用于指定要编译的多个源文件。

12. `-fsmdebug`选项:在编译期间为FSM(有限状态机)创建调试信息。

NCveriog安装指南

Ncverilog 安装指南一。

eda安装环境的搭建(建议)1 在主文件夹下建立soft文件夹,里面建立edasoft文件夹,在edasoft下建立source.source文件用来保存软件的配置。

2打开source.source文件,输入下面内容:关闭保存。

3在终端执行:打开用户bash的配置文件,在文件最后新起一行,输入:保存关闭。

二。

安装IUS(或者IFV)(内含ncverilog)工具需要的工具:Float_Cadence_LicGen.tar IUS09.20.007L1P1.tar.gz如下图:安装环境:ubuntu11.10,已经安装了可能需要的一些包(在旋风处可以获取)。

1.分别解压两个包,进入IUS09.20.007L1P1,在此目录下打开终端,运行:然后再:就会如下图所示:点击enter键直到出现:在后面输入你要安装的目录,如:~/soft/edasoft/IUS回车继续:下来惠询问安装路径:然后会跳出图形界面安装InstallScape:点击next直到下图,选上所有安装项(除去含64bit字样的,那个是64bit的):下一步安装:安装完会提示是否配置,选yes:选上所有进行配置。

在询问是否配置lisence时选否:之后完毕,close。

2、现在配置lisence。

进入刚解压出来的Float_Cadence_LicGen文件夹:修改all.dat的内容,只修改第二行,注意和你的IUS安装目录对应:回到Float_Cadence_LicGen文件夹,在该文件夹下打开终端,输入如下指令:如下:执行后会产生key.cadence文件。

重命名为cadencelisence.dat,放到你的安装目录下:编辑source.source文件,加入如下内容:注意上面有两个license,使用了冒号进行分隔。

如果你只有一个lisence,写一个就好。

创建缓存空间,在终端执行:保存关闭所有终端。

IUS9.2_ncverilog安装

下载ius9.2解压后一共六个文件打开超级终端,进入到此六个文件目录下第一步:./SETUP.SH第二步:设定安装目录(即安装到哪里)第三步:输入y第四步:设定安装源文件的目录(即,一开始解压的六个文件的那个目录)第五步:【与第三步一样】输入y第六步:【与第四步一样】设定安装源文件的目录(即,一开始解压的六个文件的那个目录)第七步:第六步后会弹出窗口,路径就是刚才第四步与第六步设定的路径,不要改,点NEXT>第八步:点NEXT>第九步:路径就是刚才第二步设定的路径,不要改,点NEXT>第十步:全部勾选,点NEXT>第十一步:点install第十二步:等待(直到100%安完),点close第十三步:弹出窗口,点NO第十四步:关掉下面界面,就会回到终端第十五步,进入安装目录,即第二步的目录,在安装目录下给tools.lnx86建一个快捷方式叫tools(使用命令ln -s tools.lnx86 tools)第十六步:复制sfk和patch_cadence(这两个文件是破解文件,到下面网址能下载到,同时也能下载到IUS软件,感谢该网友的无私奉献,/viewthread.php?tid=304428&from=favorites)到IUS安装目录下,执行./patch_cadence第十七步:在windows上面制作license首先打开LicGen.exe软件,点击open,打开Cadence.lpd然后按下图填写,注意Custom后面的那一串是机器的MAC地址,如果是用虚拟机的话,在终端中运行/sbin/ifconfig -a Hwaddr 后面就是虚拟机的MAC!,点击Generate,然后Save成license.dat。

之后用记事本打开license.dat,第一行的SERVER 后面要改成虚拟机的主机名,虚拟机主机名一般默认是localhost.localdomain 。

verilog数字系统设计教程

verilog数字系统设计教程Verilog数字系统设计教程作者:XXX引言:数字系统设计是现代电子工程中非常重要的一部分。

Verilog作为一种硬件描述语言,提供了一种方便且专业的方法来设计和描述数字系统。

本教程旨在为初学者提供关于Verilog数字系统设计的详细介绍和指导。

1. Verilog简介Verilog作为一种硬件描述语言,用于描述数字系统的功能、结构和时序行为。

它类似于C语言,但更专注于硬件级别。

Verilog可以用于设计各种数字系统,例如处理器、嵌入式系统、通信设备等。

2. Verilog基本语法2.1 模块定义Verilog的基本单位是模块。

模块是数字系统的基本组成部分,可以看作是一个独立的功能单元。

模块可以包含输入、输出、内部信号以及其它子模块等。

2.2 信号声明在Verilog中,可以声明各种类型的信号,包括输入信号、输出信号和内部信号等。

信号声明定义了信号的类型、宽度和方向。

3. Verilog建模3.1 组合逻辑建模组合逻辑是数字系统中最基本的部分。

Verilog提供了各种组合逻辑建模的方法,包括逻辑运算、选择结构和多路复用器等。

3.2 时序逻辑建模时序逻辑是数字系统中需要考虑时序关系的部分。

Verilog提供了时序逻辑建模的方法,包括触发器、计数器和时序控制等。

4. Verilog仿真4.1 仿真器介绍仿真器是用于验证数字系统设计的工具。

Verilog可以与各种仿真器配合使用,用于验证设计的正确性和性能。

4.2 仿真流程仿真流程包括编写测试平台和测试用例、编译和仿真等步骤。

本节将介绍基本的仿真流程和相关技巧。

5. Verilog综合5.1 综合概述综合是将Verilog代码转换为逻辑门级描述的过程。

综合器通过将Verilog代码映射到实际的硬件库中,生成能够实现指定功能的逻辑电路。

5.2 综合流程综合流程包括综合前的优化和综合本身两个阶段。

本节将介绍综合的基本流程和主要考虑因素。

NC-verilog 仿真教程和实验实例

Cadence IC设计实验实验六 NC-Verilog Simulator实验实验目的:NC_verilog仿真器的使用,包括编译、运行和仿真。

预备工作:cp /eva01/cdsmgr/ training_IC_data/NCVlog_5_0.tarZ .tar -vxfZ NCVlog_5_0.tarZLab1。

运行一个简单的Verilog设计[1]、设置设计环境1.cd NCVlog_5_0/lab1-mux这个目录包含了用来描述一个多路选择器和其测试平台的verilog 模块。

以下是mux_test.v模块内功能模块的端口框图。

建议:如果有时间,你最好看一看各模块(module)的Verilog代码!2.创建cds.lib文件,vi cds.lib(回车)按小写”i”切换到编辑模式,在其中写入:Define lab1muxlib ./lab1-mux.lib有关vi的编辑命令,请参阅相关资料。

如”Esc”键切换到命令状态,在命令状态下,”x”是删除当前字符,”a”是在当前光标后写入,”:wq”是存盘退出,”:!q”是不保存退出。

存盘退出3.创建(库)文件夹(即目录):mkdir lab1-mux.lib (回车)4.类似步骤1,创建hdl.var文件,在其中写入:Define WORK lab1muxlib存盘退出5.查看verilog源文件。

mux.v是2选1多路选择器MUX2_1 的门级建模源文件,mux_test.v是mux.v的测试台,包含了输入激励信号和监控程序运行的任务语句。

[2]、编译源文件(ncvlog命令):当前目录应为。

/你的学号/NCVlog_5_0/lab1-mux。

1.ncvlog mux.v –messages ,这条指令是编译mux.v。

2.vi hdl.var打开hdl.var文件,在其中添加:Define NCVLOGOPTS –messages 存盘退出注:用NCVLOGOPTS变量定义常用的ncvlog命令行操作,从而避免每次都敲入同样的命令行。

Verilog入门

第五章 Verilog 语言

Verilog 语法与实例

• 数字表示:整数,实数 整数:+/- <位宽> ‘<基数符号> <数值>

<位宽>:指定整数的大小,以bit为单位。

<基数符号>:指定整数的基数,可以是b(binary)二进

制;o(octal)八进制;d(decimal)十进制;h(hex-

adecimal)十六进制。

第五章 Verilog 语言

Verilog 语法与实例

• Verilog的四种逻辑状态: 0:逻辑零、逻辑非、低电平 1:逻辑1、逻辑真、高电平 x或X:不定态 z或Z:高阻态

第五章 Verilog 语言

《NCverilog教程》课件

覆盖率

覆盖率是测试验证中的一个重要概念, 它描述了测试用例覆盖了多少代码。覆 盖率可以分为多种类型,如语句覆盖率 、分支覆盖率、条件覆盖率等。

VS

断言

断言是Verilog中用于描述程序行为的一 种方式。断言可以用于检查程序中的某些 条件是否满足,如果不满足则产生错误。 断言通常用于验证程序的正确性。

详细描述:通过中等难度的实例,帮助学习者深入理解 Verilog的编程原理和技巧,提高编程能力。

详细描述:通过中等难度的实例,让学习者实践编写较 复杂的Verilog代码,掌握高级编程技巧和方法。

复杂实例解析

在此添加您的文本17字

总结词:高级应用

在此添加您的文本16字

详细描述:通过复杂的Verilog代码实例,介绍Verilog在 硬件设计中的应用和实践,包括数字系统设计、硬件测试 等。

05

NCVerilog调试与优化

Chapter

调试工具与技巧

调试工具

使用NCVerilog的调试工具,如仿真 器、调试器等,可以帮助开发者定位 和解决代码中的问题。

调试技巧

在调试过程中,可以采用断点、单步 执行、变量监视等技巧,以便更好地 观察和了解代码的执行情况。

优化策略与技巧

优化策略

优化NCVerilog代码时,可以采用一些常见的优化策 略,如流水线化、并行化、减少计算复杂度等。

它基于Verilog语言,并扩展了其功能 ,支持高性能的数字系统设计。

NCVerilog的特点

支持高性能数字系统设计

NCVerilog提供了高性能的硬件描述语言,支 持大规模数字系统的设计和实现。

高效仿真和综合

NCVerilog具有高效的仿真和综合工具,能够 快速验证和实现设计。

VerilogHDL语言基础教材教学课件

1990年代,Verilog HDL成为IEEE标准,并不断发展完善。

新版本

随着数字电路设计的发展,Verilog HDL不断推出新版本,支持更高级的硬件描述和验证功能。

Verilog HDL的历史和发展

01

02

03

04

ASIC设计

在ASIC设计中,Verilog HDL用于描述数字电路的结构和行为。

FPGA设计

在FPGA设计中,Verilog HDL用于描述逻辑块、路由和IO接口等。

仿真验证

Verilog HDL还用于数字电路的仿真验证,通过模拟电路的行为来检测设计中的错误和缺陷。

学术研究

在数字电路和系统设计领域,Verilog HDL广泛应用于学术研究、教学和实验中。

Verilog HDL的应用领域

测试平台编写是指编写用于测试Verilog设计的测试平台代码。测试平台代码可以使用Verilog语言编写,并使用仿真测试平台进行测试和验证。

仿真测试平台

测试平台编写

仿真和测试平台

Verilog HDL设计实例

04

组合逻辑设计

总结词:组合逻辑设计是Verilog HDL中最基础的设计之一,主要用于实现逻辑函数。

02

数字系统设计涉及逻辑门、触发器、寄存器、组合逻辑、时序逻辑等基本数字逻辑单元的设计和组合,Verilog HDL语言能够方便地描述这些结构和行为。

03

数字系统广泛应用于计算机、通信、控制等领域,通过Verilog HDL语言可以实现高效、可靠的数字系统设计。

01

Verilog HDL的未来发展

发展趋势和挑战

THANKS

ASIC设计涉及逻辑设计、电路设计、物理实现等环节,Verilog HDL语言能够描述硬件结构和行为,为ASIC设计提供强大的支持。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

input clk , rst_b; input [3:0] i_a; input [3:0] i_b; input i_sign; output [4:0] o_c; reg [3:0] a , b; reg [4:0] c; reg sign; always @ (posedge clk or negedge rst_b ) begin if (~rst_b) begin a <= 4'b0; b <= 4'b0; end else begin a <= i_a; b <= i_b; sign <= i_sign; end end always @ (posedge clk or negedge rst_b ) begin if (~rst_b)

begin c <= 5'b0; end else if (sign) begin c <= a + b; end end assign o_c = c;

endmodule

新建一个文件,加入以下代码 ,作为 testbench, module adder_t; parameter clock = 10; reg [3:0] a,b; reg sign; wire [4:0] c; reg clk,rst_b;

选 择 OK

启动 仿真器中。。。。。。。。。。。。

选 中左边 的 adder

选 定探测 点,

如上设 置,然后选 择 OK. 然后最后进 入关 键 步 骤 :仿真. 选 择 想看节 点:

注意,选 了多少节 点,浏 览 器里面就会出来多少波形,如下图 所示,他们 是对 应 的

选 择 Multiple Step 出来界面后选 择 最初运行文件和 testbench 所在目录 ,然后选 择 Create cds.lib File

点击 OK. 点击 Save. 因为 是 Verilog,所以选 择 第三项 ,选 择 OK. 回到刚 才的界面,

选 择 OK. 弹 出如下对 话 框,

initial #0 clk =0; always #(clock/2) clk = ~clk;

initial begin rst_b = 0; #10 rst_b = 1; sign = 1; a = 4'd3; b = 4'd4; #30 sign = 1;

a = 4'd5; b = 4'd10; #30 sign = 0; a = 4'd5; b = 4'd10; end initial begin #100 $finish; end adder adder( .clk(clk), .rst_b(rst_b), .i_a(a), .i_b(b), .i_sign(sign), .o_c(c) ); endmodule 保存后退出,把文件名字重命名为 adder_t.v 把 adder.v 和 adder_t.v 保存至/home/appleyuchi/Cadence/Projects_HDL 然后启动 IUS,命令是 nclaunch

按住 Ctrl,同时 选 中mplier

看下方有没有红 色的报 错 信息,如果没有,则 表示编 译 通过

然后选 择 右边 adder_t 的 module,选 择 上方 Tools 中的 Elaborator

如上设 置,选 择 OK. 选 择 生成的 module,然后选 择 上方 Tools 中的 Simulator