PCB VLab 提取寄生参数方法

VLSI版图验证系统中参数提取方法的研究

VLSI版图验证系统中参数提取方法的研究

胡庆生;林争辉

【期刊名称】《微电子学与计算机》

【年(卷),期】1997(14)3

【摘要】本文研究了VLSI版图验证系统中电阻及电容提取的方法,总结了各种方法的优缺点,并给出了当前参数提取方面的研究动向和发展趋势。

【总页数】4页(P38-41)

【关键词】VLSI;CAD;版图验证;参数;提取

【作者】胡庆生;林争辉

【作者单位】上海交通大学大规模集成电路研究所

【正文语种】中文

【中图分类】TN470.2

【相关文献】

1.面向高精度寄生参数提取与时延分析的集成电路版图数据转换方法 [J], 齐明;赵陈粟;张超;喻文健

2.VLSI版图规划中的单元时延优化方法 [J], 戚肖宁;冯之雁

3.VLSI版图参数提取的分布式并行算法 [J], 胡庆生;汪晓岩;庄镇泉

4.VLSI版图设计中的一种优化总体布线方法 [J], 孙国恩;郑宁;朱青

5.VLSI 版图的电阻参数提取 [J], 胡庆生;林争辉

因版权原因,仅展示原文概要,查看原文内容请购买。

寄生参数素材课件

目录 Contents

• 寄生参数概述 • 寄生电阻 • 寄生电容 • 寄生电感 • 寄生参数提取技术 • 寄生参数在电路设计中应用案例

01

寄生参数概述

定义与分类

定义

在电子电路中,除元件本身的电 阻、电容和电感等基本参数外, 还存在一些附加参数,称为寄生 参数。

分类

主要包括寄生电阻、寄生电容和 寄生电感等。

降低电路效率

寄生电感可能增加电路中的无功功率,降低电路 的工作效率。

减小寄生电感方法

1 2

优化布线

合理布局导线,减小导线长度和回路面积,降低 寄生电感。

使用低电感元件

选择引脚电感较小的电子元件,降低寄生电感的 影响。

3

采用多层板结构

利用多层板结构,将电源线和地线分别布置在不 同层,减小互感。

05

提高接触质量

优化导体之间的接触质量 ,如采用镀金、镀银等工 艺,降低接触电阻。

优化焊接工艺

改进元器件引脚的焊接工 艺,确保焊接质量良好, 降低引脚电阻。

03

寄生电容

寄生电容产生原因

导线之间电容

由于导线之间存在电场,导线之间会形成电容,即导线间寄生电 容。

元件引脚与地之间电容

元件引脚与地之间存在电场,形成引脚与地之间的寄生电容。

寄生参数影响

01

02

03

04

信号完整性

寄生参数可能导致信号失真、 衰减和噪声增加,影响信号完

整性。

电源完整性

寄生参数可能引起电源波动、 纹波和噪声,影响电源完整性

。

电磁兼容性

寄生参数可能产生电磁干扰( EMI)和电磁兼容性(EMC)

问题。

电路性能

一种用于功率半导体模块动态特性建模的封装寄生参数高效提取方法

粤遭泽贼则葬糟贼:With the development of arc welding inverter to high frequency and high power density,the influences of parasitic parameters

窑100窑 耘造藻糟贼则蚤糟 宰藻造凿蚤灶早 酝葬糟澡蚤灶藻

焊接设备

何亚宁:一种用于功率半导体模块动态特性建模的封装寄生参数高效提取方法

第6期

0 前言

弧焊电源是满足弧焊工艺要求的特殊电源,为 焊接电弧提供能量。焊接工艺的发展对逆变弧焊电 源的性能与可靠性提出了越来越高的要求,在性能 优化、电磁兼容性 EMC 及安全可靠性设计等方面, 电子设计自动化 EDA 的重要性和高效性日益突 显[1-7]。为使仿真能够有效指导系统开发,功率半导 体器件的精确建模成为核心问题[8-10]。

模方法的有效性。

关键词:高频;封装寄生参数;部分单元等效电路 PEEC;ANSYS Q3D;双脉冲测试

中图分类号:TM46

文献标志码:A

文章编号:员园 园员原圆猿园猿(圆园员9)06原园100-07

阅韵陨:10.7512/j.issn.1001-2303.2019.06.21

A high efficiency parasitic parameters extraction method for dynamic characteristic modeling of power semiconductor modules

何亚宁

(成都熊谷加世电器有限公司,四川 成都 611731)

calibre提取寄生参数

calibre提取寄生参数

Calibre是Mentor Graphics公司开发的一款用于集成电路设计的验证和签核工具,它可以帮助工程师进行电路仿真、布局与版图验证、物理验证、时序分析等任务。

在Calibre中提取寄生参数的方法如下:

1. 打开Calibre软件,并导入待提取寄生参数的版图文件。

2. 在Calibre界面中,选择“Physical”菜单,然后选择“Extract”选项。

3. 在弹出的对话框中,选择需要提取的寄生参数类型,如电阻、电容、电感等。

4. 点击“OK”按钮,Calibre会自动提取出版图中的寄生参数。

5. 提取完成后,可以在Calibre的报告中查看提取的寄生参数值。

需要注意的是,提取寄生参数需要使用正确的版图文件,并且版图中的元件和互连线应该已经正确地连接在一起。

此外,提取寄生参数需要进行多次迭代和优化,以确保提取结果的准确性和可靠性。

PCB过孔的寄生电容和电感的计算和使用

PCB过孔的寄生电容和电感的计算和使用一、PCB过孔的寄生电容和电感的计算PCB过孔本身存在着寄生电容,假如PCB过孔在铺地层上的阻焊区直径为D2,PCB过孔焊盘的直径为D1,PCB板的厚度为T,基板材介电常数为ε,则PCB 过孔的寄生电容数值近似于:C=1.41εTD1/(D2-D1)PCB过孔的寄生电容会给电路造成的主要影响是延长了信号的上升时间,降低了电路的速度尤其在高频电路中影响更为严重。

举例,对于一块厚度为50Mil 的PCB,如果使用的PCB过孔焊盘直径为20Mil(钻孔直径为10Mils),阻焊区直径为40Mil,则我们可以通过上面的公式近似算出PCB过孔的寄生电容大致是:C=1.41x4.4x0.050x0.020/(0.040-0.020)=0.31pF这部分电容引起的上升时间变化量大致为:T10-90=2.2C(Z0/2)=2.2x0.31x(50/2)=17.05ps从这些数值可以看出,尽管单个PCB过孔的寄生电容引起的上升延变缓的效用不是很明显,但是如果走线中多次使用PCB过孔进行层间的切换,就会用到多个PCB 过孔,设计时就要慎重考虑。

实际设计中可以通过增大PCB过孔和铺铜区的距离(Anti-pad)或者减小焊盘的直径来减小寄生电容。

PCB过孔存在寄生电容的同时也存在着寄生电感,在高速数字电路的设计中,PCB过孔的寄生电感带来的危害往往大于寄生电容的影响。

它的寄生串联电感会削弱旁路电容的贡献,减弱整个电源系统的滤波效用。

我们可以用下面的经验公式来简单地计算一个PCB过孔近似的寄生电感:L=5.08h[ln(4h/d)+1]其中L指PCB过孔的电感,h是PCB过孔的长度,d是中心钻孔的直径。

从式中可以看出,PCB过孔的直径对电感的影响较小,而对电感影响最大的是PCB 过孔的长度。

仍然采用上面的例子,可以计算出PCB过孔的电感为:L=5.08x0.050[ln(4x0.050/0.010)+1]=1.015nH如果信号的上升时间是1ns,那么其等效阻抗大小为:XL=πL/T10-90=3.19Ω。

实验八寄生参数提取(PE)及信号完整性分析(SI)

实验八寄生参数提取(PE)及信号完整性分析(SI)一、实验目的1.了解寄生参数的产生及对电路的影响。

2.掌握寄生参数提取和信号完整性分析的流程和意义。

二、实验内容1. 寄生参数提取(1)在Zeni LE窗口中,选择V erification->Layout V erification,在弹出的对话框中,选择Tool->Zeni V eri。

(2)在Command file栏里,浏览输入以下路径/zeni/v4627/demo/veri/PE_demo/pe_demo.pe,该文件是Zeni系统中PE_demo样本库所提供的用于PE提取的规则命令文件。

(3)将Custom Operation前的方框选中,选择PE选项卡。

(4)按下Appy键或OK键,Zeni开始运行PE分析。

报告结果存放在工作路径中的<cellname>.veri.log文件中。

注意:PE分析完成后,Zeni将在工作路径下生成一个以<cellname>.spi为名称的SPICE网表文件。

打开该文件可以看到,PE过程将按照提取规则,提取出版图中存在的所有器件,而不仅仅是寄生电阻和寄生电容,用户自己设计的晶体管及电容电阻等也会被一起提取出来。

该文件的名字和设计原理图时生成的网表一样,所以在PE进行时,原理图的spi网表将被覆盖。

如果需要保留,应该在PE之前将原spi网表文件换一个名字保存。

2. 局部寄生参数提取(Partial PE)(1)Partial PE执行的过程和全局PE是一样的,采用同样的PE规则命令文件。

只是在Custom Operation选项处,选择Partial PE选项卡,如下图所示。

3. 信号完整性分析(SI)在版图进行寄生参数提取(PE)之后,应该进行信号完整性分析(SI Analysis),以考察寄生参数对信号的影响程度,是否达到不可接受的程度。

目前,Zeni SI工具可以提供以下分析:Time Delay(时延分析)RC-Reduction(R,C值分析)Noise Analysis(噪声分析)(1)在PE进行完成之后,在LE窗口中,选择主菜单栏-verification,在下拉菜单中选择SI Analysis。

寄生参数提取

寄生参数提取寄生参数提取(Parasitic Parameter Extraction,PPE)是一种常用的电路测试技术,它通过分析从已经存在的物理结构中提取出的参数来发现和测量电路的功能模块。

它主要应用于设计原理图上的电路元件的参数测试和识别,以及系统模块的研发及测试。

由于参数提取不需要对电路进行任何修改,因此可以大大减少测试成本。

寄生参数提取的基本原理是,通过在电路中引入外部激励,使电路产生指定的反应,并通过测量这些反应来提取电路内部参数。

首先,将外部激励注入到电路中,如信号源、时间域反射(TDR)、电容源或分立元件,然后测量电路反应,如电压、电流或开关时间,最后根据相关理论和算法,利用测量得到的参数求解电路内部参数。

当前,寄生参数提取技术已经广泛应用于IC与PCB的测试,可用于测量电容、电阻、耦合电容、直流偏置、单端高频等参数。

特别是在复杂的IC和PCB设计中,可以减少测试时间和成本,提高效率。

在IC设计中,寄生参数提取技术可用于测量封装的静态参数,例如电容、电阻和直流偏置,以及动态参数,如感应和耦合电容。

另外,它还可以用于测量组件内部电容和电阻的参数,从而提高了IC设计的准确性。

在PCB设计中,寄生参数提取技术可用于测量电缆、芯片或接口的参数,包括介电常数、阻抗、直流偏置电压和相关的单端高频参数等。

此外,还可以用于PCB上的元件之间的连接参数测量,包括连接器、PCB芯片和电缆之间的耦合电容和直流偏置电压等。

由于寄生参数提取技术可以快速、准确地测量电路参数,因此被广泛应用于电子产品的测试和设计中,例如手机、电脑、汽车、航空航天等。

随着科技的发展,寄生参数提取技术也在不断改进和发展,例如增加参数测量的精度和准确性,增加对复杂电路的测量能力,以及增加外部激励的种类等。

基于ansys Q3D仿真软件的寄生参数提取方法

基于ansys Q3D仿真软件的寄生参数提取方法

在电子电路中难免存在寄生电感、寄生电容等参数,这时需要将PCB文件导出成.anf文件,再导入至ansys slave软件,现来具体描述寄生参数的提取过程

1.安装ansys electronic desktop 安装完成后会自动安装一

系列的插件

图标如图所示

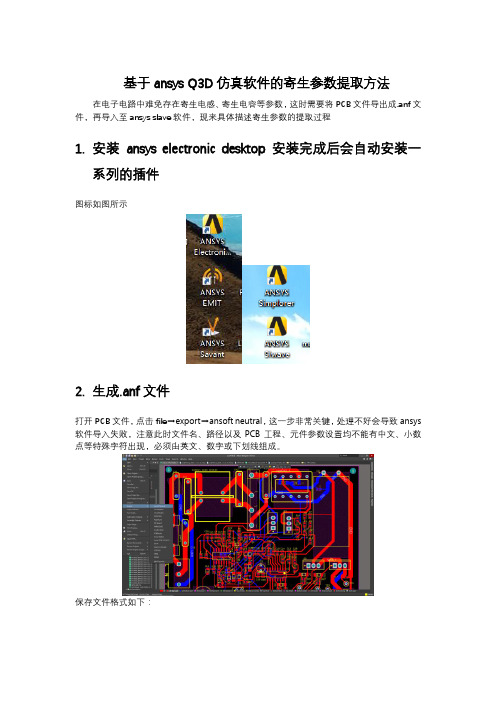

2.生成.anf文件

打开PCB文件,点击file➡export➡ansoft neutral,这一步非常关键,处理不好会导致ansys 软件导入失败,注意此时文件名、路径以及PCB工程、元件参数设置均不能有中文、小数点等特殊字符出现,必须由英文、数字或下划线组成。

保存文件格式如下:

3.打开ANSYS SLAVE 软件

其界面如图所示

点击import ANF,选择刚刚保存的ANF文件打开后点击上方的export菜单中的Q3D软件

导入成功之后如下图所示

对需要仿真的net选择,然后添加source和sink,再设置analysis setup,点击对号检查,检查无误后点击叹号即可仿真。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1、打开EMCoS PCB VLab

2、打开ODB++文件

点File选择new,from ODB++archive(*.zip)如图:

这里随便选个例子里的模型,ODB++文件一般的电路板仿真软件都可以生成3、导入模型如下图所示

4、选择显示bottom层(因为是两层的板子,top层为地平面,这样后面容易定义端口)如下

图

5、Click Create Port button on Model and Analysis Toolbar;

PCB上面直接选取两点,然后点ok即可。

再选一处(可以多个位置选择)

这样在history栏里能看到生成了两个“Port”

6、点击“check model”,Check Model button

查看没有错误,如下图

7、定义计算频率(寄生参数与频率对应的嘛),点击Task Definition button

点ok

8、点击计算

这时提示该保存了!当然最好开始建立模型后就保存!

保存为“exp1.epcb”文件

9、开始计算了

还挺慢!笔记本上计算的,忍吧!

10、仿真完毕

悲剧了c盘空间不够用了!!!

怎么办?

11、选择tools\options,定义如下把临时文件保存到d盘

12、……

看错了,d盘空间还是不够!

13、先做到这儿吧!(后面的计算完,自动弹出结果!)

14、小结:

用PCB VLab提取寄生参数的方法大概就是这个流程,计算完毕后自动弹出结果。

这个有什么用?

我们现在看了大量的电磁兼容设计的书籍,都谈到在PCB布线时地和电源尽量粗、尽量短,以减少寄生参数。

但是有么有一个衡量标准呢,这个答案应该是肯定的,一般通过简单的计算可以确定寄生参数的阈值,我们实际完用软件仿真一下验证PCB上的寄生参数不要超过这个值就ok了。

(个人理解的,欢迎指正!)

本来以为不太复杂,结果做了两个小时,还由于硬件原因没有完成。

还是希望给大家带来一些帮助,欢迎大家来交流,谢谢了!。