集成电路版图设计基础第六章:寄生参数

寄生参数素材课件

目录 Contents

• 寄生参数概述 • 寄生电阻 • 寄生电容 • 寄生电感 • 寄生参数提取技术 • 寄生参数在电路设计中应用案例

01

寄生参数概述

定义与分类

定义

在电子电路中,除元件本身的电 阻、电容和电感等基本参数外, 还存在一些附加参数,称为寄生 参数。

分类

主要包括寄生电阻、寄生电容和 寄生电感等。

降低电路效率

寄生电感可能增加电路中的无功功率,降低电路 的工作效率。

减小寄生电感方法

1 2

优化布线

合理布局导线,减小导线长度和回路面积,降低 寄生电感。

使用低电感元件

选择引脚电感较小的电子元件,降低寄生电感的 影响。

3

采用多层板结构

利用多层板结构,将电源线和地线分别布置在不 同层,减小互感。

05

提高接触质量

优化导体之间的接触质量 ,如采用镀金、镀银等工 艺,降低接触电阻。

优化焊接工艺

改进元器件引脚的焊接工 艺,确保焊接质量良好, 降低引脚电阻。

03

寄生电容

寄生电容产生原因

导线之间电容

由于导线之间存在电场,导线之间会形成电容,即导线间寄生电 容。

元件引脚与地之间电容

元件引脚与地之间存在电场,形成引脚与地之间的寄生电容。

寄生参数影响

01

02

03

04

信号完整性

寄生参数可能导致信号失真、 衰减和噪声增加,影响信号完

整性。

电源完整性

寄生参数可能引起电源波动、 纹波和噪声,影响电源完整性

。

电磁兼容性

寄生参数可能产生电磁干扰( EMI)和电磁兼容性(EMC)

问题。

电路性能

集成电路常用器件版图 ppt课件

PPT课件

40

(1)反相输出 I/O PAD

考虑到电子迁移率比空穴约大2.5 倍,所以, PMOS 管的尺寸比NMOS 管大,这样可使倒 相器的输出波形对称。

PPT课件

16

5.2 电阻常见版图画法

PPT课件

17

5.2 电阻常见版图画法

PPT课件

18

5.2 电阻常见版图画法

PPT课件

19

5.2 电阻常见版图画法

对于无法使用串、并联关系来构建的电阻, 可以在单元电阻内部取部分进行构建。

图7.18的实现方式。

PPT课件

20

电阻匹配设计总结

(1)采用同一材料来制作匹配电阻

电容值。

做在场氧区,电容值较小。

PPT课件

24

5.3 电容版图设计

(4)MIM电容 金属层之间距离较大,因此电容较小。

减小电容面积、提高电容值:叠层金属电容 器,即将多层金属平板垂直的堆叠在一起, 将奇数层和偶数层金属分别连在一起,形成 两个梳状结构的交叉。图7.21

PIP和MIM电容由于下极板与衬底距离较远, 寄生电容较小,精度较好。

5.2 电阻常见版图画法

2、电阻的版图设计

(1)简单的电阻版图

电 电阻阻的 的阻 阻值 值=电R阻的WL方dd 块R■数×方块电阻。

这种阻值计算比较粗糙,没有计入接触孔电阻 和头区电阻。

PPT课件

12

5.2 电阻常见版图画法

(2)高阻值第精度电阻版图 对上拉电阻和下拉电阻:对电阻阻值以及匹

capgen 寄生参数-概述说明以及解释

capgen 寄生参数-概述说明以及解释1.引言1.1 概述概述寄生参数(CapGen)是一种在电子系统设计中非常重要的概念。

它指的是由于设计或组装中的各种因素而引入的额外元件或电路的参数。

这些参数通常不可避免地出现在电路中,会对整个系统的性能产生潜在的影响。

因此,正确理解和考虑寄生参数是确保电路工作正常并提高系统性能的关键之一。

寄生参数可以包括电感、电容、电阻和导线等元件的额外参数。

它们可能是由于元器件之间的物理接触导致的,也可能是由于布线方式或封装工艺等因素引入的。

这些参数可能会导致电路的不稳定性、干扰或信号失真等问题,甚至影响整个系统的可靠性和性能。

在设计电路和系统时,我们需要充分考虑和评估这些寄生参数。

通过合理的布线和封装方式,可以减少不必要的干扰和失真。

此外,合理选择元器件和组件也是至关重要的,例如选择具有低寄生参数的元件,可以显著提高系统的性能。

然而,寄生参数并非完全可以消除。

相反,它们往往是电路中不可避免的一部分。

因此,理解和掌握如何分析和补偿寄生参数对于电子系统设计工程师来说至关重要。

只有通过深入研究和实践,我们才能更好地理解和应对寄生参数对系统性能的影响,并有效地提高电路和系统的可靠性和性能。

在接下来的部分中,我们将详细讨论寄生参数的定义和意义,以及影响寄生参数的因素。

通过深入理解这些内容,我们将能够更好地应对寄生参数带来的挑战,并为实际的电子系统设计提供有价值的指导。

1.2文章结构文章结构是指文章的组织框架和层次,它对于一个长文的撰写非常重要。

一个良好的文章结构可以使读者更容易理解文章的内容,并能够有条理地阅读整篇文章。

在本文中,我们将按照以下结构来撰写文章:1. 引言1.1 概述1.2 文章结构1.3 目的2. 正文2.1 寄生参数的定义和意义2.2 寄生参数的影响因素3. 结论3.1 寄生参数的应用价值3.2 未来研究方向在引言部分的概述中,我们将对寄生参数进行简要介绍,为读者提供一个对主题的整体认识。

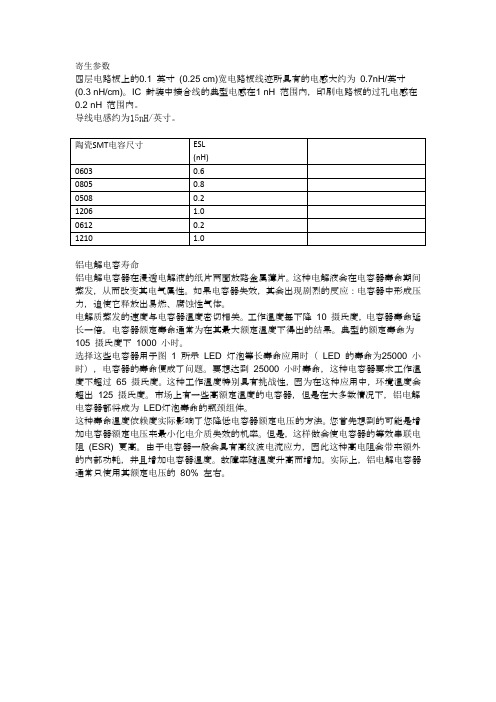

寄生参数

寄生参数四层电路板上的0.1 英寸(0.25 cm)宽电路板线迹所具有的电感大约为0.7nH/英寸(0.3 nH/cm)。

IC 封装中接合线的典型电感在1 nH 范围内,印刷电路板的过孔电感在0.2 nH 范围内。

导线电感约为15nH/英寸。

铝电解电容寿命铝电解电容器在浸透电解液的纸片两面放臵金属薄片。

这种电解液会在电容器寿命期间蒸发,从而改变其电气属性。

如果电容器失效,其会出现剧烈的反应:电容器中形成压力,迫使它释放出易燃、腐蚀性气体。

电解质蒸发的速度与电容器温度密切相关。

工作温度每下降10 摄氏度,电容器寿命延长一倍。

电容器额定寿命通常为在其最大额定温度下得出的结果。

典型的额定寿命为105 摄氏度下1000 小时。

选择这些电容器用于图1 所示LED 灯泡等长寿命应用时(LED 的寿命为25000 小时),电容器的寿命便成了问题。

要想达到25000 小时寿命,这种电容器要求工作温度不超过65 摄氏度。

这种工作温度特别具有挑战性,因为在这种应用中,环境温度会超出125 摄氏度。

市场上有一些高额定温度的电容器,但是在大多数情况下,铝电解电容器都将成为LED灯泡寿命的瓶颈组件。

这种寿命温度依赖度实际影响了您降低电容器额定电压的方法。

您首先想到的可能是增加电容器额定电压来最小化电介质失效的机率。

但是,这样做会使电容器的等效串联电阻(ESR) 更高。

由于电容器一般会具有高纹波电流应力,因此这种高电阻会带来额外的内部功耗,并且增加电容器温度。

故障率随温度升高而增加。

实际上,铝电解电容器通常只使用其额定电压的80% 左右。

图1 这种105℃电容器可能不会达到其声称的23 年寿命图2 低温下ESR 性能急剧下降。

lvs drc 寄生参数

lvs drc 寄生参数

LVS(Layout vs. Schematic)DRC(Design Rule Check)是集成电路设计中非常重要的步骤,它用于检查版图和原理图之间的一

致性,以确保设计的正确性和可制造性。

在LVS DRC中,寄生参数

是指版图中未直接连接到原理图中的器件或电气元件。

这些寄生参

数可能会对电路的性能产生影响,因此需要进行适当的检查和处理。

从版图设计角度来看,寄生参数可能包括电容、电感、电阻等。

这些参数可能是由于器件之间的布局、金属层的叠加、接线等因素

导致的。

在进行LVS DRC时,需要对这些寄生参数进行分析,确保

它们不会对电路的功能产生负面影响。

同时,设计人员还需要考虑

寄生参数对电路性能的影响,可能需要进行一些补偿或优化的措施。

另一方面,从原理图设计角度来看,寄生参数可能会影响电路

的工作频率、稳定性等性能指标。

因此,在进行LVS DRC时,需要

对原理图中的器件参数与版图中的实际参数进行比对,确保它们之

间的一致性。

如果发现寄生参数超出了设计规范,可能需要进行相

应的调整或修正。

总的来说,寄生参数在LVS DRC中是一个重要的考虑因素,需

要从版图设计和原理图设计两个角度进行全面的分析和处理,以确保电路设计的正确性和可制造性。

同时,也需要密切关注寄生参数对电路性能的影响,采取必要的措施进行优化和调整。

第6章---寄生参数

parameter

cutoff

linear

saturation

Cgb C0= Cox*WL Cgs 0 Cgd 0 Cg= Cgb+ Cgs+ Cgd C0

0 C0/2 C0/2 C0

寄生电容

由于尺寸很小,因此这些寄生参数的值也很小。 对于对电容不敏感的电路,不必担心; 不管是CMOS还是双极型,只要涉及高频,寄生会成为问题。Leabharlann 忽略寄生参数会毁掉你的芯片。

导线尽可能短 减少寄生电容的方法: 采用电容最低的金属层 绕过电路走线

寄生电容

减少寄生电容的方法 - 选择金属层

起主要作用的电容通常是导线与衬底间的电容。 如下图,寄生参数可以把电路1的噪声通过衬底耦合到电路2,所 以要设法使所有的噪声都远离衬底。

寄生电阻

为了降低寄生电阻,就需要确保使用最厚的金属层。正如我们了解 的, 一般情况下, 最厚的金属线具有最低的方块电阻。 如果遇到 相同的金属层厚度,也可以将这几条金属重叠形成并联结构,大大 降低了电阻。 因此, 并联布线是降低大电流路径电阻的有效方法, 而且还能节省一定的面积。

寄生电感

当电路是在一个真正的高频的情况下工作时, 导线也开始存在了 电感效应。 解决寄生电感的方法就是试着去模拟它, 把它当成电 路中的一部分。 首先需要尽早的完成布局,好让电路设计者较早的看到导线究竟能 有多长,然后估计出可能引起的电感。版图设计过程中尤其注意不 要因为电感耦合而影响其它部分。

寄生电容

减少寄生电容的方法 - 选择金属层

第6章集成电路版图设计概述-PPT课件

版图之一

版图之二

上面的版图有些复杂,看不清图形的细节,下面 我们先从认识简单的单元电路的版图开始,学习 版图的设计方法.

NMOS 管的版图

Poly-silicon N select

Active

P select

Metal

P-sub

PMOS

Nwell

CMOS-工艺的 横向-PNP

N-Well

第6章 版图设计概述及L-Edit简介

集成电路版图设计工作非常复杂,掌握集成电路 的版图设计技术不可能毕其功于一役,必须循序 渐进。在学习中不可能一次将所有细节都搞清楚, 有时我们需要忽略一些细节,而只关心问题的主 要方面,细节问题待以后学习。 下面我们先认识一下实际版图。 看两个用L-Edit设计的版图的例子:

Device Extract

组件特性提取器,可以生成电路串接文件,可以从布局 图形中,提取组件特性,包括电阻、电容、组件长度、 组件宽度和面积。 L-Edit/Extract 可将由 L-Edit 所画出的 layout 生成出 SPICE netlist,用来作 LVS 比对或者是用 T-SPICE 去做 layout 后段仿真。它能够提取出组件和使用者自己定义 的子电路,支持 90 度和 45 度的对象。电路中去标示组 件及节点对于寻找layout 里面的元素可以达到快速的提 取。 对 于 大 多 数 共 同的组 件 参数都 可 提取出 来 , 像 是 MOSFET 长 , 宽, 源极/ 汲极面积和周长。 Diodes, BJTs, MESFETs, JFETs 的面积。对于有阶层的子电路也能提 取,还包含电容和电阻。

APR (Standard Cell Place & Route)

集成电路中的晶体管及其寄生

电路的工作。 2. NPN工作于截止区或正向工作区——寄生PNP截止。

三、EM模型

如果令I3=0或ISS=0,就可得出三层二结结构NPN晶体管的EM 方程 :

集成双极晶体管的有源寄生效应

假定隔离结始终处于反偏,并取晶体管的参数如下;

在进行rC1的计算时,假定其图形是一个上下底为矩形且 相互平行的锥体,其上底为有效集电结面积S,即Sc.eff = SE(发射结面积),并作以下近似:

①上底、下底备为等位面; ②锥体内的ห้องสมุดไป่ตู้流只在垂直方 向流动; ③在上、下面上的电流分布 是均匀的。

这样结构的电阻可用公式求得:

公式的适用范围:

不能再认为电流再锥体内是垂

集成电路中的晶体管 及其寄生

理想本征集成双极晶体管的埃伯斯-莫尔模型

一、要点

通过隔离把硅片分成一定数目的相互绝缘的隔 离区;

在各个隔离区制作晶体管,电阻等元件; 制作互连线,把各个元件按照一定功能连接起

来。 多维效应——集成电路中的双极晶体管为四层

三结结构,各电极均从上面引出,而且各结面 积不同。

对EM模型作简化:

① PN结正偏工作时, PN结反偏工作时,

V F 0 ,e V F /V t 1 e V F /V t

V R 0 ,e V R /V t 1 1

②在电流叠加时只计算exp ( V F / V t)项.即可以忽略反偏 电流,当全部结都反偏时,只考虑ISS项

③VSC总是小于零,所以

寄生PNP管的存在对NPN管的电流基本上没 有影响,只是增加了IB及IC中的反向漏 电.同时增加一项衬底漏电流IS’ 。

在模拟集成电路中,NPN管一般工作在正向 工作区,所以寄生PNP管的影响可以忽略。

PCB过孔概念、寄生参数介绍

PCB过孔概念、寄生参数介绍 2003-11-18 上海泰齐科技网一、过孔的概念过孔(via)是多层PCB的重要组成部分之一,钻孔的费用通常占PCB制板费用的30%到40%。

简单的说来,PCB上的每一个孔都可以称之为过孔。

从作用上看,过孔可以分成两类:1、用作各层间的电气连接。

2、用作器件的固定或定位。

如果从工艺制程上来说,这些过孔一般又分为三类,即盲孔(blind via)、埋孔(buried via)和通孔(through via)。

盲孔位于印刷线路板的顶层和底层表面,具有一定深度,用于表层线路和下面的内层线路的连接,孔的深度通常不超过一定的比率(孔径)。

埋孔是指位于印刷线路板内层的连接孔,它不会延伸到线路板的表面。

上述两类孔都位于线路板的内层,层压前利用通孔成型工艺完成,在过孔形成过程中可能还会重叠做好几个内层。

第三种称为通孔,这种孔穿过整个线路板,可用于实现内部互连或作为元件的安装定位孔。

由于通孔在工艺上更易于实现,成本较低,所以绝大部分印刷电路板均使用它,而不用另外两种过孔。

以下所说的过孔,没有特殊说明的,均作为通孔考虑。

从设计的角度来看,一个过孔主要由两个部分组成,一是中间的钻孔(drill hole),二是钻孔周围的焊盘区,见下图。

这两部分的尺寸大小决定了过孔的大小。

很显然,在高速,高密度的PCB设计时,设计者总是希望过孔越小越好,这样板上可以留有更多的布线空间,此外,过孔越小,其自身的寄生电容也越小,更适合用于高速电路。

但孔尺寸的减小同时带来了成本的增加,而且过孔的尺寸不可能无限制的减小,它受到钻孔(drill)和电镀(plating)等工艺技术的限制:孔越小,钻孔需花费的时间越长,也越容易偏离中心位置;且当孔的深度超过钻孔直径的6倍时,就无法保证孔壁能均匀镀铜。

比如,现在正常的一块6层PCB板的厚度(通孔深度)为50Mil左右,所以PCB厂家能提供的钻孔直径最小只能达到8Mil。

版图设计中的寄生参数分析

版图设计中的寄生参数分析1.引言正如我们了解的,工艺层是芯片设计的重要组成部分。

一层金属搭在另一层金属上面,一个晶体管靠近另一个晶体管放置,而且这些晶体管全部都是在衬底上制作的。

只要在工艺制造中引入了两种不同的工艺层,就会产生相应的寄生器件,这些寄生器件广泛地分布在芯片各处,更糟糕的是我们无法摆脱它们。

寄生器件是我们非常不希望出现的,它会降低电路的速度,改变频率响应或者一些意想不到的事情发生。

既然寄生是无法避免的,那么电路设计者就要充分将这些因素考虑进去,尽量留一些余量以便把寄生参数带来的影响降至最低。

2.寄生参数的种类寄生参数主要包括了电容寄生、电阻寄生,和电感寄生。

2.1 寄生电容图1所呈现的是在不同金属层之间以及它们与衬底之间产生的电容情况:图(1) 无处不在的寄生电容由上图我们可以看到寄生电容无处不在。

不过需要了解的是即使寄生电容很多,但是如果你的电路设计对电容不十分敏感的时候,我们完全可以忽略它们。

但当电路的设计要求芯片速度很快的时候,或者频率很高时,这些寄生的电容就显得格外重要了。

一般来说,在一个模拟电路中,只要频率超过20MHz 以上,就必须对它们给予注意,否则,它有可能会毁掉你的整个芯片。

减少寄生电容可以从以下几个方面入手:(1)导线长度如果你被告知某个区域的寄生参数要小,最直接有效的方法就是尽量减小导线长度,因为导线长度小的话,与它相互作用而产生的电容例如金属或者衬底层的电容就会相应地减小,这个道理显而易见。

(2)金属层的选择另一种解决的办法则是你的金属层选择。

起主要作用的电容通常是导线与衬底之间的电容,图2则说明了衬底电容对芯片的影响。

Noisy Quiet图(2) 衬底电容产生的噪声影响如上所示,电路1和电路2都对地产生了一个衬底电容,衬底本身又有一个寄生电阻,这样一来电路1的噪声就通过衬底耦合到电路2上面,这是我们不希望看到的。

(设法使所有的噪声都远离衬底)因此我们改变一下金属层,通常情况下,最高金属层所形成的电容总是最小的。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

parameter

cutoff

linear

saturation

Cgb C0= Cox*WL Cgs 0 Cgd 0 Cg= Cgb+ Cgs+ Cgd C0

0 C0/2 C0/2 C0Biblioteka 0 2C0/3 0 2C0/3

school of phye

basics of ic layout design

16

器件的寄生参数

CMOS晶体管 -

栅电容:边缘交叠电容

The gate also has fringing fields terminating on the source and drain, this leads to addition overlap capacitance, called “Cgs(fringing) /Cgd(fringing) ”. Cgs(fringing) = Cgsfr * W Cds(fringing) = Cdsfr * W

school of phye

basics of ic layout design

11

寄生电阻

IR压降: 假设导线的方块电阻Rsqu是0.05Ω, 则 R = Rsqu*L/W = 0.05Ω*(2mm/2um) = 50 Ω V = IR = 50Ω*1mA = 50 mV 所以计算得知电压为50毫伏。 它对于一个电压非常敏感的电路 来讲就会有很大的影响。如果这条导线的压降不能超过10毫伏, 显然这个设计就是失败的。所以这就意味着我们必须增加导线宽 度才能满足这一要求。

intrinsic capacitance (a parallel plate capacitor)

school of phye basics of ic layout design 15

器件的寄生参数

CMOS晶体管 -

栅电容:

Cgb is necessary to attract charge to invert the channel, so high gate capacitance is required to obtain high Ids. Cgb = Cox * WL = Cpermicron * W Cpermicron = Cox*L = (εs/tox) *L

Comparing to a long channel nMOS transistor, we can find that Cgd does not go to 0 in saturation of a shorter channel transistor, because the fringing overlap component Cds(fringing) is significant. The fringing overlap capacitance becomes relatively more important for shorter channel transistors because it is a large fraction of the total.

basics of ic layout design

9

寄生电容

减少寄生电容的方法 – 绕过电路走线

school of phye

basics of ic layout design

10

寄生电阻

通过电流密度可以选择导线宽度,电流大小孩影响单元间的布线 方案。 翻开工艺手册,我们经常能看到每层金属线能够承载的电流。通过 这个参数我们可以计算所需要的金属层宽度。例如,有一根信号线 需要承载 1毫安的电流,而工艺手册注明每微米可以走 0.5毫安的 电流, 那么这根金属层的宽度至少要2微米。

能否利用寄生参数?

从整体来说,不可以利用寄生参数得到好处。 因为寄生参数可以正负相差50%,无法很好地控制。 然而,可以利用寄生参数得到一点小外快。如把电源线和地线互 相层叠起来就可以得到免费的电源去耦电容。

basics of ic layout design 14

school of phye

器件的寄生参数

5

寄生电容

减少寄生电容的方法 - 选择金属层

可以通过改变金属层来获得较小的至衬底的电容,通常最高金属 层所形成的电容总是最小的。 另外值得注意的是并不是所有工艺的最高层金属与衬底产生的寄 生电容都最小,它还与金属层的宽度等其它因素有关。有些工艺中 或许是 M2对地的电容要比 M4的对地电容大,所以我们不能只凭 直觉来判断, 一定要通过具体的计算来确认。 Metal Min. Width Cap/Unit Area (fF/um2) Cap 10um wire M1 0.8 5 40 M2 0.8 3 24 M3 2.4 2.5 66 M4 6.5 1.5 97.5

basics of ic layout design 8

school of phye

寄生电容

减少寄生电容的方法 – 绕过电路走线

在某些电路的上面布金属线,这是在数字自动布局布线中经常会遇 到的情况。 各层金属相互交叠,所以在反相器、触发器等都存在 寄生电容。如果不加以干预的话, 只是由布线器来操作, 那么就有 可能毁了你的芯片。

school of phye

basics of ic layout design

7

寄生电容

减少寄生电容的方法 - 选择金属层

widening a wire leads to less than a proportional increase in capacitance, but a proportional reduce in resistance, so the RC delay product improves. Widening wires also increase the fraction of capacitance of the top and bottom plates, which somewhat reduces coupling noise from adjacent wires. Increasing spacing between wires reduces capacitance to the adjacent wires and leaves resistance unchanged. This improve the RC delay to some extent and significantly reduces coupling noise.

在模拟电路版图设计中,我们经常会人为的将敏感信号隔离开来, 尽量避免在敏感电路上面走线,而只是将金属线走在电路之间,这 样寄生的参数就小一些且相对容易控制。 在数字版图中,90%的导线一起布臵,不必关心它们的功能; 而在模拟版图中,对于某些功能可以不在乎寄生电容,而另一些 必须注意。

school of phye

school of phye

basics of ic layout design

13

寄生电感

当电路是在一个真正的高频的情况下工作时, 导线也开始存在了 电感效应。 解决寄生电感的方法就是试着去模拟它, 把它当成电 路中的一部分。 首先需要尽早的完成布局,好让电路设计者较早的看到导线究竟能 有多长,然后估计出可能引起的电感。版图设计过程中尤其注意不 要因为电感耦合而影响其它部分。

CMOS晶体管

MOS器件本身存在两种电容:栅电容和扩散电容。 栅电容: 平行板电容: Cgb = Cunit/area x A 源漏交叠电容: Cgs、 Cgd 总的栅电容: Cg = Cgb + Cgs + Cgd

Cgs(fringing) Cgd(fringing)

overlap capacitance

school of phye

basics of ic layout design

6

寄生电容

减少寄生电容的方法 - 选择金属层

Modern processes have six or more metal layers. The lower layers are thin and optimized for a tight routing pitch. Middle layers are often slightly thicker for lower resistance and better current-handling capability. Upper layers may be even thicker to provide a lowresistance power grid and fast global interconnect. Layer Metal 1 Metal 2/3 Metal 4/5 Metal 6 Purpose Interconnect within cells Interconnect between cells within units Interconnect between units, critical signals I/O pads, clock, power, ground

school of phye

basics of ic layout design

4

寄生电容

减少寄生电容的方法 - 选择金属层

起主要作用的电容通常是导线与衬底间的电容。 如下图,寄生参数可以把电路1的噪声通过衬底耦合到电路2,所 以要设法使所有的噪声都远离衬底。