PCB与信完整性工程设计原理及方法

ADS 的设计系统克服信号和电源完整性的10种方法

是德科技ADS 克服信号和电源完整性挑战的10 种方法技术概述Keysight EEsof EDA 的先进设计系统(ADS)软件是全球闻名的电子设计自动化软件,是射频、微波和高速数字应用的理想选择。

为了提高效率,ADS 采用了一系列新技术,其中包括两个电磁(EM)软件解决方案,专门用于帮助信号和电源完整性工程师提高 PCB 设计中的高速链路性能。

以下列出了 ADS 帮助工程师克服信号和电源完整性挑战的 10 种方法。

1. ADS 为您的 SI EM 表征提供出色的速度和准确性.....................................................第 2 页2. ADS 简化部件 S 参数文件的使用................................................................................第 4 页3. ADS 提供先进的通道仿真器技术................................................................................第 6 页4. ADS 立身于技术(如 PAM-4)潮头 .............................................................................第 9 页5. ADS 加速 DDR4 仿真方法 ...........................................................................................第 12 页6. ADS 将电源交到设计人员(PI 分析)手中 ...................................................................第 15 页7. ADS 可实现平坦的 PDN 阻抗响应 ..............................................................................第 18 页8. ADS 提供电热仿真 .......................................................................................................第 21 页9. ADS 有一个互连工具箱(Via Designer 和 CILD)..............................................................第 22 页10. ADS 传递是德科技理念:人力资源、硬件和软件资源的结合,开启测量新视野..................................................第23 页1. ADS 为您的 SI EM 表征提供出色的速度和准确性在精确表征高速通道的损耗和耦合时,通常会使用电磁(EM)技术。

pcb工程师前景

pcb工程师前景PCB(Printed Circuit Board)工程师是电子行业中的关键职位之一。

随着电子产品的快速发展,PCB工程师的需求也日益增长。

本文将着重讨论PCB工程师的前景,并介绍该职位所涵盖的技能和职责。

一、PCB工程师的职责PCB工程师负责设计和开发电子产品中的印刷电路板。

他们需要理解电子电路原理,并将电子设备的功能转化为适用于印刷电路板的布局和设计。

PCB工程师的职责包括但不限于以下几个方面:1. PCB设计:根据产品规格书和客户要求,进行电路板的设计和布局。

他们需要选择合适的材料、元件和连接方式,并考虑电磁兼容性和信号完整性等因素。

2. PCB制造:与PCB制造商合作,确认电路板的制造流程并监督样板板的制作。

他们还需要进行可行性分析,以确保电路板的生产符合成本和质量标准。

3. 故障排除:在电子产品开发和生产过程中,可能会出现电路故障和问题。

PCB工程师需要运用相关工具和方法,进行故障排查并提供解决方案。

二、PCB工程师的技能要求成为一名优秀的PCB工程师需要具备以下几项核心技能:1. 电子电路设计与分析:熟悉各种电子元器件及其特性,并能理解电路图纸和原理图。

掌握常见电路分析软件和EDA(Electronic Design Automation)工具的使用。

2. PCB设计软件:熟练使用主流的PCB设计软件,如Altium Designer、Cadence Allegro等。

能够根据设计要求进行电路板的绘制、布局和打样。

3. 电磁兼容性(EMC)和信号完整性(SI):了解EMC和SI的基本原理,具备电磁场和信号传输特性的分析能力。

掌握规避EMC和SI 问题的方法。

4. 制造工艺和工程技术:理解PCB的制造工艺和生产流程,熟悉常见的表面贴装技术和多层板工艺。

具备解决制造问题和提高工艺效率的能力。

三、PCB工程师的发展前景1. 就业市场需求旺盛:随着电子产品的快速发展,PCB工程师的需求量逐年增加。

信号完整性工程设计原理

SI设计是系统工程

解决一个问题需要多种措施相互辅佐,共同作用 解决一个问题可能恶化其他问题 一套好的SI设计规则就象一个好的中医药方

直觉 理性的艺术

SI设计是平衡的艺术

平衡各种解决措施的冲突,平衡性能与成本 最终的技术指标不能动摇,各个措施要有弹性

基础理论为“本”,工程解决方法为“标”。 固本培元,标本兼治。

电源噪声 信号回流路径 不同频率成 分影响不同

各个频率分量的反射

工程直通车

为什么串联端接阻值影响信号延迟?如何理解这种现象?

工程直通车

通道的优化:仅关注带宽内的频率?

Tr 35 ps BW 0.35 Tr 10GHz Bitrate 10Gbps FFE=9dB

Z out

变化的电磁场引起的

I

信号路径

参考路径

电压:浪头般前进,斜坡占据一定空间跨度。

电路角度

电容 互感

如何理解电容、电感参数? 电流两个方向:电流环路方向、电流传播方向,相互独立。

SI设计的特点

SI设计是个性化的

每个工程都不同,对症下药,没有包治百病的药方

基础的重要性

应急式的解决方法导致支离破碎的知识,似是而非。 长期无法入门 没有基础,无法预判可能的风险 没有基础, SI仿真会变成盲目的试验 没有基础,无法正确解读结果 没有基础,无法进行综合权衡 没有基础,找不到解决措施

SI设计的误区 NO.2

没有针对性,不分轻重 电平?边沿? 前仿仿什么? 后仿仿那些? 问题怎么解决? 一种常见错误观点: 种常见错误观点: 无论是什么电路板,只要把能想到的全做了,就不会有问题?

嵌入式ARM系统PCB设计中信号完整性的研究

两 个 区域 ( 区域 1 区域 2 的交 界 面 时 , 信 号 / 、 ) 在 返 回路径 的导 体 中 , 存 在 一 个 电压 和 一 个 电 流 回 仅

2 0 . 1 , 08  ̄ 1 q q

第1 1期

电 子 测 豇 c

EL CTR0N2 D

No 1 .1

嵌 入 式 ARM 系统 P B设计 中信 号 完 整性 的研 究 C

晁富邦, 潘英俊 , 魏 彪, 解启瞻, 蒋树庆

重庆 4 04 ) 0 0 4

嵌入 式技术

整性 问题 , 确保嵌入式 系统 的安全可靠性 , 也便 成 为嵌入式系统设计 的重中之重 。其 中,C P B布线的 不合理及不适当的端接所造成的信号完整性问题 , 变化时会发生反射 , 这主要缘于信号进入到瞬态阻 抗未尽 匹配的区域 , 信号到达 瞬态阻抗不同的 即,

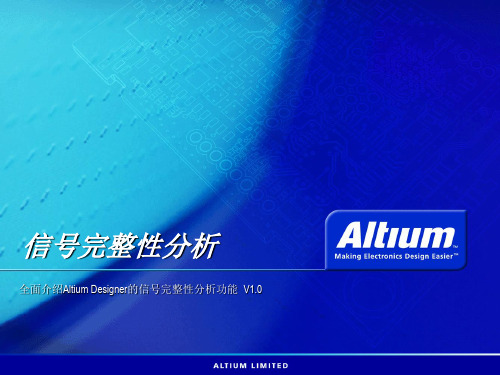

Altium Designer信号完整性分析

在图4所示的模型配置界面下,能够看到每个器件所对应的信号完整性模型,并且每 个器件都有相应的状态与之对应,关于这些状态的解释见图8:

图8

19

Altium Designer的信号完整性分析

修改器件模型的步骤如下:

1、双击需要修改模型的器件(U1)的Status部分,弹出相应的窗口如图9 2、在Type选项中选择器件的类型, 3、在Technology选项中选择相应的驱动类型, 4、也可以从外部导入与器件相关联的IBIS模型,点击 Import IBIS,选择从 器件厂商那里得到的IBIS 模型即可。 5、模型设置完成后选择OK,退出。

四、图11为分析后的网络状态窗口,通过此窗口中左侧部分可以看到网络是 否通过了相应的规则,如过冲幅度等,通过右侧的设置,可以以图形的方式 显示过冲和串扰结果。

选择左侧其中一个网络TXB,右键点击,在下拉菜单中选择Details…,在弹 出的如图12所示的窗口中可以看到针对此网络分析的详细信息。

22

图20

33

Altium Designer的信号完整性分析

11

Altium Designer的信号完整性分析

布线后(即PCB版图设计阶段)SI分析概述 - 用户如需对项目PCB版图设计进行SI仿真分析, Altium Designer要求 必须在项目工程中建立相关的原理图设计。此时,当用户在任何一个原 理图文档下运行SI分析功能将与PCB版图设计下允许SI分析功能得到相 同的结果。

- 当建立了必要的仿真模型后,在PCB编辑环境的菜单中选择Tools -> Signal Integrity命令,运行仿真。

- 当遇到个别原理图元器件符号并未放置在PCB版图设计,用户可以利用 Altium Designer提供的器件关联功能,即菜单Project -> Component Links命令;在PCB版图设计SI分析中,未布线的网络将采用曼哈顿 (Manhattan)长度算法计算引脚间的传输线长度。

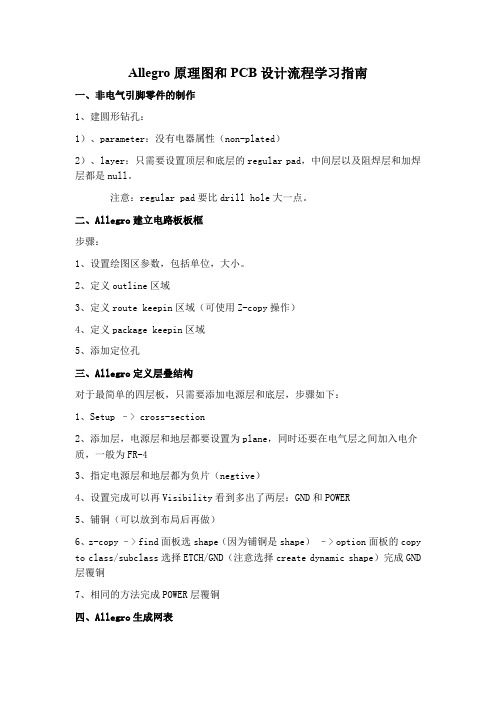

Allegro原理图和PCB设计流程学习指南

Allegro原理图和PCB设计流程学习指南一、非电气引脚零件的制作1、建圆形钻孔:1)、parameter:没有电器属性(non-plated)2)、layer:只需要设置顶层和底层的regular pad,中间层以及阻焊层和加焊层都是null。

注意:regular pad要比drill hole大一点。

二、Allegro建立电路板板框步骤:1、设置绘图区参数,包括单位,大小。

2、定义outline区域3、定义route keepin区域(可使用Z-copy操作)4、定义package keepin区域5、添加定位孔三、Allegro定义层叠结构对于最简单的四层板,只需要添加电源层和底层,步骤如下:1、Setup –> cross-section2、添加层,电源层和地层都要设置为plane,同时还要在电气层之间加入电介质,一般为FR-43、指定电源层和地层都为负片(negtive)4、设置完成可以再Visibility看到多出了两层:GND和POWER5、铺铜(可以放到布局后再做)6、z-copy –> find面板选shape(因为铺铜是shape)–> option面板的copy to class/subclass选择ETCH/GND(注意选择create dynamic shape)完成GND 层覆铜7、相同的方法完成POWER层覆铜四、Allegro生成网表1、重新生成索引编号:tools –> annotate2、DRC检查:tools –> Design Rules Check,查看session log。

3、生成网表:tools –> create netlist,产生的网表会保存到allegro文件夹,可以看一下session log内容。

五、Allegro导入网表1、file –> import –> logic –> design entry CIS(这里有一些选项可以设置导入网表对当前设计的影响)2、选择网表路径,在allegro文件夹。

Altium Designer 14原理图与PCB设计

Altium Designer 14原理图与PCB设计本文将介绍《Altium Designer 14原理图与PCB设计》的大纲,提供背景信息和目的。

在本文中,将介绍Altium Designer 14软件的基本原理图与PCB设计功能,并深入探讨其使用方法和技巧。

Altium Designer 14简介原理图设计界面概述元件库管理连接和布线信号捕获和逻辑判别设计规则检查输出文件生成PCB设计界面概述元件布局和走线层次设计和分层规划信号完整性与电磁兼容性考虑设计规则检查输出文件生成实例分析原理图设计实例PCB设计实例注意事项和常见问题解答结论Altium Designer 14是一款专业的电子设计自动化工具,广泛应用于电子工程师和PCB设计师的原理图与PCB设计过程中。

在本文中,我们将重点介绍Altium Designer 14软件中原理图与PCB设计的相关功能和特点,以帮助读者更好地理解和使用该软件。

本文的目的旨在提供关于《Altium Designer14原理图与PCB设计》的详细大纲,以引导读者逐步研究和掌握使用Altium Designer 14进行原理图与PCB设计的基本知识和技能。

通过阅读本文,读者将了解到Altium Designer 14软件在电子设计中的核心功能和应用方法,并能够应用这些知识进行实际工程项目的设计和开发工作。

概述Altium Designer 14的主要功能和特点,如原理图设计、PCB设计、仿真等本文档为使用Altium Designer 14进行原理图与PCB设计提供指南。

其中包括软件界面介绍、操作步骤、常见问题解答等内容。

Altium Designer 14是一款强大的电子设计自动化软件,为电路原理图和PCB设计提供了全面的支持。

下面是软件界面的主要组成部分:工具栏:包含了常用的工具和命令,可以快速访问并执行相应的操作。

项目导航器:显示当前项目的文件结构和层次关系,方便管理和导航文件。

protel dxp 原理图以及PCB设计

在原理图中放置电源和接地符号,为电路提 供稳定的电源和接地。

原理图的检查与修改

检查原理图的完Leabharlann 性检查原理图是否完整,是否包含了所 有必要的元件和功能模块。

检查连接关系

检查元件之间的连接关系是否正确, 是否有遗漏或错误的连接。

检查电气规则

根据设定的电气规则,检查原理图中 的错误和潜在问题。

06

案例分析

案例一

总结词:简单实用

详细描述:小型电路板通常用于简单的电子设备,如遥控器、计算器等。在 Protel DXP 中,可以使用标准元件库和封装库进 行原理图和 PCB 设计。设计过程相对简单,主要考虑元件布局和布线规则。

案例二

总结词:高集成度

详细描述:复杂多层板通常用于高集成度的电子设备,如手机、平板电脑等。在 Protel DXP 中,需 要使用高级元件库和封装库进行原理图和 PCB 设计。设计过程需要考虑多层布线、信号完整性、电源 完整性等问题,以确保电路性能和可靠性。

高速电路设计规则检查

高速规则检查

Protel DXP 支持高速电路设计规则检查,确保电路板在高速 条件下具有良好的性能表现。通过规则检查,用户可以发现 潜在的信号完整性问题,并进行相应的优化。

信号完整性分析

Protel DXP 还提供信号完整性分析功能,通过仿真分析电路 板的信号质量,帮助用户预测和解决潜在的信号问题。

原理图设计流程

创建新项目

在Protel DXP中创建一个新的 项目,为原理图和PCB设计提 供一个统一的管理环境。

添加注释和说明

在原理图中添加必要的注释和 说明,以清晰地表达设计意图。

确定设计目标

明确原理图设计的目的和要求, 确定所需元件和功能模块。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

PCB与信号完整性分析基础目录前言Array信号完整性(Signal Itegrity)概念信号完整性(Signal Itegrity)原理信号完整性仿真技术信号完整性工程设计应用高速系统带来的挑战Digital Clock Frequencies are Increasing: doubling every 2 years!All noise effects increase as rise times decrease and clock frequencies increase现在的设计有成百上千的高速信号。

各种工艺、器件和信号类型有不同的信号质量要求:3.3V 器件由不同于5V器件的噪声裕量时钟信号由不同于总线的时序要求PCI总线由不同于ISA总线的过冲限制印制板上的互连线对信号有明显的影响,必须加以分析。

没有任何一种设计指南完全覆盖现在的所有设计。

对标准设计指南的强制应用,必将造成过头的设计,增加了制造成本和复杂程度。

关键信号和总线必须基于实际情况加以设计和分析。

现实世界的现状信号完整性设计工程就是解决以上问题50 MHzNO5MHz 20MHz 随着系统速度的提高问题将更加复杂何时判断是否高速设计今天电子设计师们正在从事100MHz 以上的电路设计,总线的工作频率也已经达到或者超过50MHz,有的甚至超过100MHz。

这类型的电子系统要求高速、高效、高度集成且具备高可靠性,这是一个新的领域,称为高速系统设计(HssD,High Speed System Design)。

高速电路有两个方面的含义:一是频率高,通常认为如果数字逻辑电路设计的频率达到或者超过45MHz~50MHz,而且工作在这个频率的电路已经占整个电子系统一定的份量(例如三分之一),则称为高速电路设计。

另外一个含义是指数字信号的上升与下降(或称信号的跳变)非常之快,当信号的上升时间小于6倍(一说4倍)信号传输延时(电长度)时即认为信号是高速信号,而与信号的频率无关。

SI:新概念,旧方法SI应用的是传统的传输线、电磁学等理论,以及复杂的算法,解决以下几个方面的问题:*反射;*串扰;*过冲、振铃、地弹、多次跨越逻辑电平错误;*阻抗控制和匹配*EMC; *热稳定性;*时序分析 *芯片封装设计;.............必须注意,信号完整性设计不仅是PCB上如何走线,它是一个逻辑的、机械的和电气的元素的有机整体,信号完整性工程师要具有"系统的概念"。

信号完整性分析作用提高系统性能、可靠性与稳定性优化验证,减少投板次数减少与简化,有效降低成本缩短开发周期提高产品竞争力解决高速系统设计(HSSD)的唯一有效途径目录前言信号完整性(Signal Integrity)原理信号完整性仿真技术信号完整性工程设计应用信号完整性(SI)定义SI(SIGNAL INTEGRITY),即信号完整性,是近几年发展起来的新技术。

SI解决的是信号传输过程中的质量问题,尤其是在高速领域,数字信号的传输不能只考虑逻辑上的实现,物理实现中数字器件开关行为的模拟效果往往成为设计成败的关键。

信号完整性问题分类传输延时(Propagation Delay)信号失真(反射、振铃、损耗、散射)串扰(Crosstalk)电源/地弹(Ground Bounce)EMC目录前言信号完整性(Signal Itegrity)概念信号完整性(Signal Itegrity)原理信号完整性仿真技术信号完整性工程设计应用为什么用传输线进行SI分析PCB板上的信号传输速率越来越高,PCB走线已经表现出传输线的性质,在集总电路中视为短路线的连线上,在同一时刻的不同位置的电流电压已经不同,所以不能再用集总参数来表示,必须采用分布参数传输线理论来处理。

传输线的模型可以表示如下图:图一:单根传输线模型单根传输线的分析方法对于(图一)传输线的性质可以用电报方程来表达,电报方程如下: dU/dz = ( R + jwL) I dI/dz = ( G +jwC) U电报方程的解为:U=Ae rz+Be−rzI=Ae rz/Zo−Be−rz/Zo通解中的为传播常数r=(R+jwL)(G+jwC)为特征阻抗Zo=(R+jwL)+(G+jwC)由于R, G 远小于 jwL、jwC,所以通常所说的阻抗是指:Zo=L/C从通解中可以看到传输线上的任意一点的电压和电流都是入射波和反射波的叠加,传输因此传输线上任意一点的输入阻抗值都是时间、位置、终端匹配的函数,再使用输入阻抗来研究传输线已经失去意义了,所以引入了特征阻抗、行波系数、反射系数的概念描述传输线。

特征阻抗的物理意义就是:入射波的电压和入射波的电流的比值,或反射波的电压和反射波电流的比值。

电磁波在介质的中的传输速度只与介质的介电常数或等效介电常数有关。

FR4带状线的典型传输速度为180ps/inch单根传输线的分析方法(续)耦合传输线分析由于信号之间存在耦合,就引出了有效特征阻抗的概念:若传输线加相反激励,则有效特征阻抗为:Zo= Z(1-K),即奇模阻抗;若传输线加相同激励,则有效特征阻抗为:Ze= Z(1+K),即偶模阻抗。

差分阻抗就是奇模阻抗的两倍。

K为两根传输线之间的耦合系数。

t 导线介质地平面导线介质地平面A、微带线:B、嵌入式微带线:几种PCB设计常用的传输线结构(一)几种PCB 设计常用的传输线结构(二)导线介质地平面地平面导线介质地平面地平面h h 1t C 、对称带状线:D 、:不对称带状线几种PCB设计常用的传输线结构(三)导线介质地平面导线介质地平面地平面E、微带线边对边耦合:F、带状线边对边耦合:几种PCB 设计常用的传输线结构(四) G、对称上下耦合:H 、不对称上下耦合:导线介质地平面地平面导线介质地平面地平面阻抗的控制1、为什么要进行阻抗控制?阻抗匹配不但可以消除信号的反射,还可以降低串扰、EMI问题的发生。

而阻抗匹配的前提是良好的阻抗控制。

2、哪些因素对阻抗有影响?走线类型、介质厚度、线宽、线间距、介质材料等都对阻抗有贡献,需要综合考虑这些影响。

简单的讲,就是所有影响信号耦合的因素3、现在能够进行阻抗控制的工具有哪些?现在我们所有的分析工具都可以进行阻抗控制。

基本上都是用二维场提取的方式进行阻抗计算。

阻抗的测试1、阻抗测试的原理:现在比较常用的阻抗测试仪采用TDR原理,即向被测走线输出一个阶跃信号,由于信号在阻抗变化点发生反射,测试仪通过采集到的不同点的反射,计算出各点的阻抗。

为了保证阻抗测试的准确性,必须保证被测线段的足够长度2、阻抗测试设备:11801C采样示波器+SD24采样/TDR/TDT探头反射·产生的原因:电磁波沿信号路径传播,在阻抗不连续点产生反射阻抗不连续点产生反射反射的计算:·信号在始端和末端来回反射·由于损耗的存在,反射信号逐渐减弱,最后达到平衡(Zs-Zo)/(Zs+Zo)(ZL-Zo)/(ZL+Zo)常见匹配方法串联端接匹配接收端开路或输入阻抗很大时放置RS=Z0 -R0(一般要小一点)在源端。

优点:没有直流通路,因此不用备用的电源和没有高电平衰减,RS可以集成在芯片内部。

缺点:典型的情况下只能用于单负载结构;如果时序允许的话,增加的负载要放在线的末端附近。

当Z0 和R0不好控制或者当一些过冲和下冲能够被容忍的时候,通常RS<<Z0 -R0。

)常见匹配方法(续并联端接匹配匹配电阻在负载端连接到电源或地,优点:和串联匹配相比只有一半的容性延迟。

缺点:增加了直流功耗;输出摆幅不再是全摆幅。

改进方式是thevenin等效匹配,对TTL 3V 偏置的匹配R1/R2=2/3; R1||R2=Z0。

交流并联匹配是通过牺牲信号质量来换取直流功耗的减小。

常见匹配方法(续)二极管端接匹配在接受端放置肖特基二极管到电源或地优点:二极管限制了过冲(小于或等于1V);二极管可以集成在每一个接受器的芯片内部;不需要直流通路来消耗直流功耗。

缺点:二极管匹配的缺点之一就是在线路上存在多径反射而影响到下一个数据的开始,因此需要在变化频率下校对二极管的响应。

为了很好地的利用这种匹配的优点,你必须选择Ton,Vf,Trr时间小的肖特基二极管。

常见匹配方法(续)AC匹配(RC匹配)优点:在于终端电容阻止直流电流,因此节省了相当可观的功率。

选择适当的电容值会使得终端的波形具有最小的过冲和下冲并且是一个接近理想的方波。

缺点:一是要求了两个器件,在高密板时布局时无放置空间;二是在传输线上的数据会有时间的抖动,依赖于前一个数据的模式串扰与耦合当两个网络靠近时,一个网络的电流变化会引起另外一个网络的电流变化,即产生串扰。

也就是两个网络之间的电磁场耦合产生。

串扰只在上升、下降沿电流变化时产生。

串扰与耦合机理串扰模型:电感耦合模型(感性串扰)和电容耦合模型(容性串扰)。

串扰与耦合机理感性串扰的特点:受害网络与侵害网络之间互感的影响象一个变压器,侵害网络上的电流在受害网络上诱导出与侵害电流相反极性的电流。

这个电流在受害网络上向两个方向扩散。

受害网络向远端和近端流动的电流的相位相同,且信号跳变方向与侵害网络相反。

串扰与耦合机理容性串扰的特点:受害网络向远端和近端流动的电流的相位相反,向远端传播的电流与侵害网络的跳变方向一致。

串扰与耦合机理前向串扰: 1/2Ic-IL后向串扰: 1/2Ic+IL在理想情况下,前向串扰是相抵消的,通常IL比Ic大。

后向串扰脉冲幅度饱和,宽度是信号在平行耦合线长度上传输时间的两倍,前向串扰脉冲宽度与驱动信号上升时间相同,幅度随耦合长度增加而增加,最终达到饱和。

串扰与耦合机理危害:波形畸变噪声余量减少上升时间变化。

串扰与耦合机理容性串扰电流和感性串扰电流在远端相消。

所以平行走线的网络,如果驱动源都在网络的同一端,则串扰很小;如果驱动源在不同端,则串扰很大。

对于平行走线的网络,容性串扰和感性串扰在近端相加,并从近端反射到远端。

所以对于受害网络的负载来说,最大的串扰来自从近端反射回去的串扰(后向串扰),而不是直接入射的串扰(前向串扰)。

因为源端匹配元件能够较好地吸收后向串扰,所以能够更好地消除总串扰。

影响串扰的因素信号的跃变时间(Tr ,Tf)与频率器件的电压扇出PCB上的线耦合电源、地层与信号层间距相邻信号层间距线间距与并行走线长度回流耦合路径PCB材料信号的耦合模式串扰的控制选择慢变化边沿信号的器件。

选择输出电流小的器件。

为了减少PCB上的线间耦合,可采取以下措施:1)减少电源地层与信号层间距2)提高相邻信号层间距3)减少并行走线长度4)当线长增加到一定限度时串扰饱和,可增加线间距抑制5)增加干扰源上的信号上升时间6)在受害线上采用匹配技术(通过仿真决定)7)关键信号线走STRIPLINE把噪声裕量大的信号放在耦合大的区域(在布局是进行控制)尽量避免信号的同时变化,特别是反向同步变化(在实际中可能性不大)。