candence学习笔记

Candence学习笔记7--第7讲 Cadence原理图中总线的使用方法

第7讲Cadence原理图中总线的使用方法目录1、放置总线 (2)2、放置任意转角的总线 (2)4、把信号连接到总线 (2)5、重复放置与总线连接的信号线 (3)6、总线使用中的注意事项 (4)7、在不同页面之间建立电气连接 (5)8、总结: (6)第7讲总线的使用方法1、放置总线Place--Bus或者快捷键B2、放置任意转角的总线任意走线,走线之前按住shift3、总线命名规则Alias命名规则:baseName[0:N]总线是N+1位,baseName不能以数字结尾;然后将Net Alias放置到总线上。

4、把信号连接到总线信号线通过bus entry和总线相连。

5、重复放置与总线连接的信号线快捷操作:放置1根bus entry线之后,按住F4,可以一直放置bus entry线。

然后将芯片管脚与bus entry相连,在导线上放置net alias快捷操作:重复命名,可以按住ctrl+左键拖动上一根已经命名好的线,这样就能重复命名导线了。

或者按住F4,也能重复上一次动作。

6、总线使用中的注意事项1、总线和信号线之间,它们之间的连接,只能通过net alias这种方式,网络名称的方式连接。

总线名称和信号线名称之间:这两个圈圈处的名字,必须一致。

2、信号线与总线之间,用bus entry的这种方式,连接。

如果Wire与总线直接相连,wire与总线之间实际是没有电气连接的。

总线与总线之间连接,会构成实际的电气连接。

如果两个总线交叉相连,那么系统默认两根线之间是没有电气连接的。

在交叉点处,放置一个junction,两个总线之间就有实际的连接了。

7、在不同页面之间建立电气连接在一个页面中放置Off-page connector,然后在另外一个页面中放置同样名称的off-page Connector。

只要两个页面的off-page connector的名称一样,那么这两个点就已经有电气连接了。

8、总结:理解Cadence软件是使用网络名称建立电气连接的。

Cadence自学笔记笔记

Cadence SPB15.7 快速入门视频教程目录Capture CIS 原理图及元件库部分第1-15讲第1讲课程介绍,学习方法,了解CADENCE软件Cadence下几个程序说明Design Entry CIS 系统级原理图设计Design Entry HDL 芯片设计Layout plus orcad 自带的pcb板布局布线工具,功能不是很强大,不推荐使用Pcb Editor Pcb librarian Cadence带的PCB布局布线封装设计PCB Router pcb自动布线Pcb SI SigXplorer Pcb电路板信号完整性仿真OrCAD Capture CIS 对元件管理更方便相对于OrCAD CaptureI 放大O 缩小页面属性设置options Design Templateoptions Schematic Page Properties第2讲创建工程,创建元件库原理图元件库,某元件分成几个部分,各部分间浏览ctrl+N ctrl+B元件创建完后修改footprint封装,options Package Properties第3讲分裂元件的制作方法1、homogeneous 和heterogeneous 区别homogeneous,芯片包含几个完全相同的部分选择该模式,画好第一个part后,后面的part会自动生成,因为完全一样。

但是引脚编号留空了,要自己再设置引脚编号。

heterogeneous芯片包含几个功能部分,可按照功能部分分成几个部分。

ctrl+N ctrl+B切换分裂元件的各个部分原理图画完之后,要对各元件自动编号,在项目管理窗口选择项目,点击tools annotate,在Action下面选择相应的动作。

2、创建homogeneous类型元件3、创建heterogeneous类型元件第4讲正确使用heterogeneous类型的元件1、可能出现的错误Cannot perform annotation of heterogeneous part J?A(Value RCA_Octal_stack ) part has not been uniquely group(using a common User Property with differing Values) or the device designation has not been chosen2、出现错误的原因分裂元件分成几个part,并且用了多片这样的分裂元件。

CADENCE学习笔记4

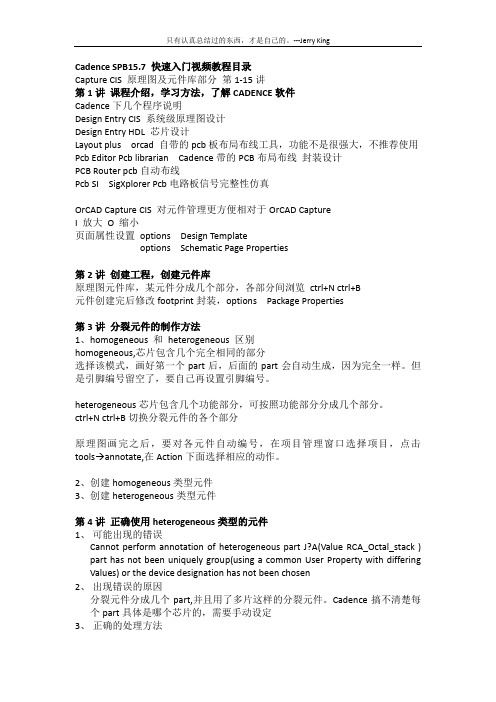

CADENCE学习笔记7布线Grid设置统一设置为5mil7.1手工布线Route-Connect7.2BGA扇出1Route-PCB router–fanout by pick,find选择component,单击bga元件即可;右键-setup,设置扇出方式注意布线宽度采用的是约束管理器-physical中的设置。

2焊盘中间打过孔:route-create fanout,option选择合适的VIA,via direction设置为via in pad,find选择symbol或pin,单击引脚即可。

3route-create fanoutInclude unassigned pins:对没有网络的PIN扇出Include all same net pins:对同一net的所有pin扇出Via选择过孔类型;Via direction:扇出方向,默认是,其他有东西南北,NE东北,NW西北,SE东南,SW西南,via in pad引脚上打孔。

Override line width:设置出线线宽,默认的线宽采用的是约束管理器-physical中的设置。

Pin-via space;如果要打孔在四个BGA焊盘中间,应该选择centeredCurve:走直角线,见下图1。

用于特殊工艺。

Find中可以选择symbol对BGA元件所有pin扇出,pin对一个或多个引脚扇出设置完成后,在PCB中点选或框选有时两个孔叠在一起,无法选中底层或小的过孔,如下图top层的PIN很难选中,首先在idle 模式时选择etch-top,然后使用route-create fanout,就很容易选中top层的PIN了。

7.2利用Constraints Manager实现长度约束规则的设定1在使用constraints Manager设定长度规则前,需给无源器件赋模型及电压值1)给电源地赋电压值操作:点击Logic/Identify DC Nets,在弹出的窗口中选择你要的电源网络名赋电压值即可2)给无源器件分配模型:analyze->model assignment2BUS的创建操作:在Constraints Manager的工作页中选中要创建Bus的Net、Xnet如D0~D7,点击右键,选Create/Bus3Pin pair的创建操作:在工作页中选中要创建Pin pair的一个Net或Xnet,如D0点击右键,选Create/Pin pair,在弹出窗口中First、Second Pins分别选中一个管脚即成一对Pin pair,点击OK即可,若一个Net、Xnet要创建多对Pin pair点击Apply即可继续创建下一Pin pair,而无需退出再进来4Differential Pair的创建操作:在工作页中选中要创建Differential Pair的一对Net或Xnet,如TD+/-,点击右键,选Create/Differential Pair5.不同Bus或Bus中成员的移植操作:拖动左键选中要添加或转移的Net、Xnet,点击右键,选Bus Membership,在弹出的窗口中选你要的Bus名即可7.3设置网络拓扑-T型连接点注意:在约束管理器中经常很多命令不能用,是因为PCB当前处于某个命令状态。

CADENCE学习笔记7

CADENCE学习笔记10PCB常用命令解释注意:无论执行什么操作,有四点需要注意:1当前的模式;在状态栏可看到(次要)2option:重要3find:最重要4右键,经常会有些特殊的功能。

10.1元件选取多次选择或从整体选择中去掉部分idle模式下,右键-application mode-general edit,注意find中的选择对象;方法1:先框选,CTRL+点选或框选,如果新选与原来的选择重叠则减少选择,未重叠则增加选择;方法2:先框选,shift+点选或框选,增加选择;方法3:右键-section set-select by polygon,然后依次单击绘制一个区域选中其中的元件Select by lasso:鼠标任意绘制一个区域,其中元件被选中Select by path:沿路径选择也可以在general edit模式下,使用move等命令,右键-select by polygon,by lasso,by path。

此时option中dim active layer:当前层变暗;dim color assignments:取消高亮颜色。

10.2move1optionsripup etch;移动元件时,相关走线清除slide etch:移动元件时飞线隐藏,已布连线不断开,且自动修线。

stretch etch:选中移动元件时飞线隐藏,已布连线不断开type-incremental:增量方式旋转,可多次选择;absolute;只能一次旋转固定角度;angle设置旋转角度;point表示移动点的选取,user pick表示用户单击PCB的某点作为移动点,sym origin表示封装的原点,body center表示封装中心,sym pin#设置封装某个引脚作为抓取点,如果元件没有引脚1,会导致无法移动,比如mark点,或者以AK定义引脚的二极管,改用user pick 就好了;在placement edit、etch edit模式下,单击元件即可实现move功能。

CADENCE学习笔记5

CADENCE学习笔记8设置约束规则setup-constraint注意:在约束管理器中经常很多命令不能用,是因为PCB当前处于某个命令状态。

设置完规则后,需要update DRC,否则很多DRC标记不消除。

setup-constraint:打开规则管理器,必须设置间距和线宽;net-class:仅用于设置线宽、线距的信号集合;可以同时为physical和spacing约束创建net class,在electrical中看不到;在electrical中创建的net class在其他约束中看不到。

不要对电源地创建net group,可以创建net classnet-group:16.6以后归集某类信号的几个,可以设置所有规则,代替以前版本的bus,创建net group后,在physical、spacing、electrical约束中都可以看到这个网络组;不要对电源地创建net group,可以创建net class。

match-group:仅用于某类信号的等长参数。

给电源和地网络创建了net group后,移动包含电源和地网络的元件,给包含电源和地网络的元件布线都变得非常卡顿,删除这个net group后卡顿消除。

建议电源和地网络使用net class。

添加器件模型后(设置xnet后),很多网络被合并在一起,可以通过下图来查找网络。

在添加器件模型时,不要对所有元件添加模型,建议对具体的元件单个添加模型。

8.1Spacing间距约束必须设置,需要设置有电气属性的布线、引脚、过孔、shape相互之间的间距。

1Spacing constrain set-All layer:可以对所有层设置,也可以单独对每一层设置。

在右侧表格内,default行连续选择多个表格,输入数值,然后按enter键可以实现多个表格统一赋值。

一般间距不要小于6mil,一般板厂都能加工。

注意此间距是走线边沿间的安全间距,不是走线中心间距。

cadence学习笔记

begin layer 正常焊盘regulapadpastemasktop 一样大小加焊层soldermask 阻焊层大0.1Mm通孔焊盘0.7Mm 通孔1mm就好1.先做花焊盘内径外经开口钻孔1mm的话内径比钻孔大6-8mil 1.5mm2.begin layer end 一样3.内层DEFAULT INTERNAL THERMAL 要用Flash焊盘4.sold-- 和pastmask 大点pastmask 和表层一样画好焊盘后,1.place-boud-top add-rectagule courtyad2.silkscreen add-line 和封装一样大3.画角标4. assembly top 直接画5 索引编号标示layout label refdel assembly top 中间qapl963silkscreenshape 矩形etch画圆第一次圆心第二次X半径Y不变错误相容shape merge shapeschret smbortsetup 最后一个设置路径通孔的封装焊盘制作。

通孔比焊盘大10-12mil1.flash 焊盘add-flsh 内圆1.5 外圆1.8 开口0.72做焊盘holetype 圆形plating 孔壁上锡plateddrill diameter 直径drill/slot光会文件时候,形状character 字母with 大小3 geometry-suare 方形圆孔的(第一个脚用的)thermalrelief 一样anti pad 大0.1mm做好后表层拷贝到END layer 表层制作完成4 default internal 花焊盘5pastemask top bottm 和表层一致。

SOLDERMASK 两层和表层大0.1mm之后做外面圆的。

1.添加线创建边框,2.倒角,,manufacture-draft-fillet3.准许布线区域,比边框小点,setup-areas-routekeepin 注意选择shapefill-unfilled不填充4.package-keepin edit-z-kopy 小点5.加固定孔6.setup-cross-section板子层7.铺通,内点层。

CADENCE学习笔记2

CADENCE学习笔记2allegro界面介绍2.1option介绍可以完成所有属性的显示隐藏;1pin引脚2package geometry(封装外形):assembly:装配外框,分为top/bottompin number:引脚号place bound:元件重叠限制区域,分为top/bottomsilkscreen:封装丝印,分为top/bottom,常用2package keepin/keepout,route keepin/keepout:布局布线限制局域,常用3board geometry板图形,常用outline:板外框silkscreen:一些板图形,比如公司标志,一些line线等,分为top/bottom dimension:尺寸,制版说明,技术要求等5REF DES元件号assembly:装配元件号silkscreen:丝印元件号,常用6etch:布线,覆铜等,选择ETCH-top层,将top层显示为当前层,同样可以设置其他层为当前层;7device type:器件型号,封装型号8component value:元件值assembly:装配用元件值silkscreen:丝印元件值9via classFilmmasktop光绘掩膜10via keepout–各层layer禁止放置过孔的区域2.2visiblity控制面板可以控制每层的ETCH-布线覆铜(覆铜属于shape),via-过孔,pin-引脚,DRC的显示隐藏;这些属性在option控制面板中也有。

还有很多属性visiblity控制面板无法控制;Conductors:针对所有布线层开关;planes:内电层;etch:布线;PLAN:GRE开关。

View-color view save:将当前显示的图层保存,可以visibility面板的-views下拉框中可找到。

2.3FIND filter介绍Groups:群组;comps:带有元件序号的Allegro元件;function:一组元件中的一个元件;symbols:元件;Nets:一个网络pin;引脚,包括pad,固定孔(plated或no plated)Vias:过孔或贯穿孔clines:布线,具有电气特性的线段;cline segs:cline中没有拐弯的导线,即线段;line:没有电气特性的线段;other segs:lines中没有拐弯的线,即线段;shape:形状;void:任意多边形的挖空部分;figure:图形符号;DRC errors(违反设计规则的位置及相关信息)text:文本,包括元件标号ratsnests:飞线;rat TS:T形飞线;Find by name中devtype:器件类型;symtype:符号类型;property:属性;group:2.4修改工具栏View-customize toolbar-command中选中一些按钮,拖到工具栏(可以不同工具栏)上即可2.5application mode在placement edit模式下,系统会自动将未摆放的元件列在右侧的options下。

cadence学习笔记

cadence学习笔记1. Allegro中我设置了highlight的颜⾊为⽩⾊,但选中后颜⾊是⽩蓝相间的,很不⽅便查看。

是什么地⽅需要设置,哪位⼤虾告诉哈我?答:setup/user preferences/display/display_nohilitefont 这个选项打勾就⾏了。

2. 不⼩⼼按了Highlight Sov后部分线⾼亮成⽩⾊,怎样取消?答:这个是⽤来检查跨分割的,取消的办法是:如果是4层板的话,在电源层跟地层都铺上地⽹络,然后再按Highlight Sov刷新即可。

3. 如何更改Highlight⾼亮默认颜⾊?答:可以在Display->Color/Visibility->Display->Temporary Highlight⾥修改即可,临时修改颜⾊可以点Display->Assign Color 来实现。

4. 如实现Highlight⾼亮部分⽹络,⽽背景变暗,就像Altium Designer那样?答:可以在Display->Color/Visibility->Display->Shadow Mode打开该模式,并且选中Dim active layer 即可。

5. 快速切换层快捷键答:可以按数字区⾥的“-”或“+”来换层。

6. OrCAD跟Allegro交互时,出现WARNING [CAP0072] Could not find component to highlight 错误等?答:OrCAD输出⽹表,Allegro导⼊⽹表,确保两者对的上号,然后在Orcad选中元件,再右键Editor Select,即可在Allegro中选中该元件;反过来,在Allegro中要先Highlight某元件,在Orcad中变会选中该元件。

1.ORcad :⾸先打开orcad和allegro分别占1/2的窗⼝界⾯。

然后orcad中Tools/creatnetlist/PCB Editor中Create PCB Editor Netlist下的Options中设置导出⽹表的路径。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

主要学习以下内容:

(1)利用OrCAD Capture CIS 进行原理图设计

(2)利用Cadence PCB Editor 进行PCB布局布线

(3)光绘文件(Artwork)制作,如何生成Gerber文件。

1. 工具介绍

PCB Edtor 绘制PCB的工具

PCB Librarian 制作PCB原件库的工具

PCB Router自动布线的工具

PCB SI 和SigXplorar 电路板信号完整性仿真的工具

2 . OrCAD Capture CIS

启动改工具后,会打开如下界面,通常选择OrCAD Capture CIS

OrCAD Capture CIS 与OrCAD Capture相比的优势是,在画原理图时对原理图中所有元件的管理会很方便。

3.

DSN文件,是建立工程的数据库文件,包含了工程的所有数据。

Design Cache,每在原理图中放置一个元件,就会在该文件下将该元件保存下来,当下次再放置同一个文件时,就可以很方便的从这里来选取相关元件。

Library,包含元理图用到的库

4. OrCAD Capture 的菜单是上下文相关的,对不同的窗口操作,菜单是不同的。

5. 原理图文件的创建

(1) 选原理图文件夹,Design---->New Schematic Page----->.........

(2) 选原理图文件夹,右键单击------>New Page--------->...........

6. 原理图文件的删除

(1) 选中要删除的原理图文件,Design---->Delete----->.........

(2) 选中要删除的原理图文件,按Delete键

7. 原理图文件的重命名

(1) 选中要得命名的原理图文件,Design---->Rename----->.........

(2) 选中要得命名的原理图文件,右键单击------>Rename--------->...........

8. 原理图文件的放大和缩小

(1) i:放大o:缩小都是以鼠标所在位置为中心

(2) 通过菜单操作

(3) Ctrl + 鼠标滚轮

选中某元件后,就会以该元件为中心来进行放大或者缩小

1. 打开Orcad capture CIS 后,在创建原理图前,需要做一些设置:

(1)Options------>Design T emplate

2.修改原理图的背景色:

Options---->Preferences------>Background

3.对单个原理图页面设置

Options-------Schematic Page Properties

4.元件库的建立

在OrCAD Capture CIS中,选择File------New-----Library 。

元件库也是以工程的方式来组织的。

建好的库文件默认存在C盘,最后把它放在一个文件夹里,方便以后管理。

方法:选中library1.olb-----右键-----Save as ,选择路径,重命名并保存

5. 原理图元件封装的制作----

(1)选中OLB 文件-----右键-----New Part

把一个元件分成多个部分的画法

注意上图中红色方框中的内容:

Parts Per Pkg:要把一个元件分成几部分画

Homogeneous:分成的几个部分都有相同的结构,画完一个部分,后面的几个部分会自动生成,只是管脚序号是空的,修改一下管脚就可以了。

如下图元件,就可以分成两个homogeneous

Heterogeneous:把一个元件分成几个功能完全不同的几个部分。

把一个元件分成几个部分来画,当画完一个部分后,想要切换到下一个部分,快

捷键:Ctrl+n;想看分立元件的上一部分:Ctrl+b

通常在一个元件的封装中,是不允许有相同编号的管脚存在的。

但是在Homogeneous方式中,允许公用的部分分别出现在各部分中。

如上图,Pin4 &Pin8 分别出在两个部分当中

1. 撤销原理图中元器件编号:选中DSN文件-----Tool----Annotate----Reset part references to "?"

2. 给元理图中元件添加编号:选中DSN文件

-----Tool----Annotate----Incrementalreferenceupdate

3. 如果在一个原理图中,一,多次使用同一个分为几个部分的元件,这时,系统无法确定谁与谁是一个整件,就会出在编号错误的问题。

解决这个问题有以下几步:

(1)File ------Open------Library,打开分立元件所在的库

(2)找到该分立元件,给每一部分都加上一属性

选中A部分----Options------Part Properties----New, Name: package;value:1--------OK

选中B部分----Options------Part Properties----New, Name: package;value:1--------OK

(3)回到原理图中,重新放置这些器件。

双击元件的其中一个部分,打开属性窗口,把是一个整体的各部分的package 属性的值设置为同一个数就可以了。

如,一个元件被分成了两个部分,在一个原理图中两次使用了该元件,就将第一个元件的两个部分的Package 都设置为1,将第二个元件的两个部分的package都设置为2.

POWER_GROUP改为“package”

1. 在原理图中旋转元件:

当元件悬浮于鼠标上的时候,按“R”键就可以逆时针旋转器件

当元件已经放置在原理图上后,选中元件----右键----Roate,就可以旋转元件

2. 画任意角度的线

选中wire或者Bus--------按“Shift”键------放置线的起点,这样就可以朝任意方向拉出线了。

3. 总线的画法:

(1)Busname[0:7] 标识8位总线的网络

(2)Busname的最后一位不能为数字。

如AD0[0:7]这是不合法的。

(3)Busname与【】之间不能有空格。

(4)总线名字要与信号线名字一致。

4. 不同页面之间的连接

例如A页在面有两个信号,要与B页面的两个信号相连

在工具条中,选择下面的Place off-page connector图标,弹出下图窗口,有向左和向右两种图标,任选一种就可以了。

修改Symbol的名字,然后放置在所要连的信号线上。

只要off-page connector的名字相同,软件就会以相连处理。

在编辑原理图的时候,有一个很重要的命令browse.

选中DSN文件------Edit----Browse然后可以选择自己需要查的的项。