Altiumdesigner规则检查常出的问题汇总

AltiumDesigner设计报错问题总结

Altium Desig ner设计报错问题总结在编译原理图时,引脚和连线旁边出现很多红线,提示erro r:signal withn odriv er。

原理图没有加入到Pro ject里。

第一次导入没问题,但是改了个元件的封装,在更新一下(Design—Update SCH),点击导入时出现Unko wnPin。

解决方案一:把第一张PC B删掉,新建一个PC B再倒入。

解决方案二:把改过的元件在PCB中删除,再倒入。

以上问题本应该是没问题的,但是可能是我们使用的盗版软件的原因。

用altiu mdesi gner画完图编译后,出现几百警告,几乎的所有的都是Offgridp in 画的图在项目中去编译,的不能编译,如果文件不在项目中的话,就会出现你说的不在网络的提示。

你的元件没有在原理图上真正形成电气上的连接。

你的元件库没有被软件别。

没有你建一个项目文件,把你的原理图放在里去做编译,这样就不会出错了。

是因为你原理图中的元件引脚尺寸和你设置的栅格尺寸不对应,导致系统无法识别而报错,引脚长度尺寸必需设置成栅格尺寸的整数倍!!!你把你做的原理图元件重新再画一遍,再编译,问题解决!!!双面板应该都有哪些La yer?B ottom Layer底层铜皮,双面板必须要T opLay er顶层铜皮,双面板必须要T opOve rLaye r顶层丝印,一般需要,也有节约成本不做的。

B ottom OverL ayer底层丝印,一般不需要,底层放原件的话,也可以加。

T op/Bottom Solde rmask顶层底层阻焊层,就是“绿油”,一般需要,也有节约成本不做的。

M echin ical1/4机械层1/4,板边以及板内开槽,1无金属化,4有金属化。

ALTIUM DESIGNER 制板 问题集锦

Altium 公开课问题集锦(003)1、如何在原理图库中COPY一个元件到另一个库?答:有些人采用比较拙劣的方法,选中元件的组成部件(包括管脚和图形等),然后COPY,到另一个库中新建一个元件,然后PASTE,这样做除了麻烦之外,还有一个问题就是没法COPY原来元件的那些参数属性。

正确的做法应该是在sch library面板下,选择要COPY的component,可以单选,也可以按住ctrl或shift多选,点右键copy,然后在另一个库中同样通过sch library面板,在components 栏里点右键paste,就可以将刚才选中的器件一次全部copy过来,包括所有的PIN脚,图形,参数,以及指定的PCB封装名称等等所有信息。

2、是否可以将一个原理图库里的所有器件的所有参数信息导出一个类似EXCEL的表格供查阅?答:Altium Designer的库工具提供了三种report功能,在主菜单reports下面可以看到。

Reports->Component可以将当前选中的component的pin和part信息报告出来。

Reports->Library List可以将当前库中所有的component名称列出,并在库文件保存的路径下生成一个同名的.csv文件,这个文件会列出库中所有component的所有参数属性。

Reports->Library Report则会将当前库中所有component的所有信息用一个doc文件图文并茂地详细描述出来,包括pin脚,参数,指向的每个PCB footprint以及仿真模型,3D模型的属性,图形等等。

3、在PCB库中如何建立异形焊盘答:在PCB库中,先放置普通焊盘,而对于异形焊盘的描述可以采用其他元素如fill, line等来实现,这样做好的库封装被调用到PCB设计的时候会产生一个附加的元素无网络的问题,这时候需要在PCB设计环境下使用design->netlist->configure physical nets来对这些无网络的元素进行处理,如下图,执行指定的操作,即可为异形焊盘的附加元素添加与原焊盘一致的网络。

altiumdesigner常见错误及处理

altiumdesigner常见错误及处理电⽓检测时出现Hole Size Constraint (Min=1mil) (Max=100mil) (All)怎么处理最佳答案导致出现这个错误的原因就是由于你的PCB中钻孔的尺⼨与PCB规则中的设定尺⼨冲突。

解决⽅法有两个:1)更改规则检查内容,不再上报钻孔尺⼨错误冲突。

具体⽅法就是:快捷键 T D 打开规则检查窗⼝,在Rules To Check中,将Hole Size后⾯两个框内的勾去掉,这样就不会再报此类错误。

2)更新钻孔尺⼨规则,让你的钻孔正常化。

具体⽅法是:快捷键 D R 打开规则编辑窗⼝,在Design Rules内找到 Hole Siz e 并双击打开进⾏规则编辑;将最⼤值和最⼩值更改为包含你的PCB上钻孔的最⼤尺⼨和最⼩尺⼨后即可。

un-routed net constraint ( (all) )错误T+D,⼯具⾥⾯的设计规则检查ALTIUM DESIGNER 导⼊PCB时提⽰some nets were not able to matched.Try to match these manualy?具体解决⽅案如下:解决⽅案1:然后新建⼀个PCB⽂件,再次更新的时候就会出现这个问题。

发表⼀下个⼈意见,然后你有更改过原理图的某些⽹络。

你原先更新过⼀次PCB,可以将⼯程中的PCB⽂件删除,在确认封装等没有问题的情况下,再UPDATE PCB DOCUMENT就⾏了兄弟我也是⽤AD6的,是个菜鸟解决⽅案2:刚刚试了⼀下,再UPDATE PCB DOCUMENT就⾏了慢慢摸索吧,有些问题很难说请,可以将⼯程中的PCB⽂件删除,然后新建⼀个PCB⽂件,在确认封装等没有问题的情况下silk to silk (clearance=10mil)报错Altium Designer PCB中显⽰SilkToSilkClearance和Silkscreen ComponentPad Clea rance的距离怎么取消?例如字符间距设置的是0.254mm,PCB 字符之间就会出现<0.254mm这样的⽩⾊字。

Altiumdesigner规则检查常出的问题汇总

A l t i u m d e s i g n e r规则检查常出的问题汇总 SANY标准化小组 #QS8QHH-HHGX8Q8-GNHHJ8-HHMHGN#Altium designer 规则检查常出的问题汇总1.Rule Violations Count违反数2.Short-Circuit Constraint (Allowed=No) (All),(All)短路约束=不允许)(全部),(全部)3.Un-Routed Net Constraint ( (All) ) 26Un-Routed净约束(所有)26岁4.Clearance Constraint (Gap=9mil) (All),(All)间隙约束(间隙= 9 mil)(全部),(全部)5.Power Plane Connect Rule(Relief Connect )(Expansion=20mil) (Conductor Width=10mil) (Air Gap=10mil) (Entries=4) (All)功率平面连接规则(救济连接)(扩展= 20 mil)(导体宽= 10 mil)(气隙= 10 mil)(条目= 4)(全部)06.Width Constraint (Min=8mil) (Max=20mil) (Preferred=15mil) (All)宽度约束(Min = 8 mil)( Max= 20 mil)(优先15例mil)(全部)问题应该出在你设置和实际的冲突,你的Protel所设置的最小线宽是25mil,最大线宽也是25mil,默认线宽还是25mil,这本没错,但可能是你的某根GND线不是25mil,或者你用了覆铜,而覆铜的线条(Track Width)也不是25mil,所以才出错!建议在Design 的Rule里设置一下WidthConstraint的最大和最小线宽,调整到合适范围,就不会报错了。

7.Height Constraint (Min=0mil) (Max=1000mil) (Prefered=500mil) (All)高度约束(Min = 0 mil)( Max = 1000 mil)(优先= 500 mil)(全部)8.Hole Size Constraint (Min=1mil) (Max=150mil) (All)孔尺寸约束(Min = 1 mil)( Max = 150 mil)(全部)修改尺寸,设计孔大于你设置的规则的值9.Hole To Hole Clearance (Gap=6mil) (All),(All)洞孔间隙(间隙= 6 mil)(全部),(全部)引脚安全间距问题,一般是封装的问题,如果确定封装没问题,这个错误基本你可以忽略。

Altium Designer常见问题(整理)

1、Altium Designer PCB布线时,如何设置电器删格(注:当我点击交互式布线时,鼠标放在焊盘上,发现焊盘上原来会显示的正六边形没有了,看在哪儿设置能把那个圈圈显示出来呢?)电气栅格,就是你的光标距离某些对象小于一定距离时,会自动吸附过去,这样可以提高光标定位的精度,解决某些对象不在移动栅格上的问题。

a)在PCB页面右键→Options→Board Options...→Electrical Grid勾上Range设置捕捉距离。

b)在PCB页面按快捷键D+O,Electrical Grid勾上2、设置原理图图纸大小。

在PCB页面右键→Options -> sheet…standard style3、altium designer 如何把原理图和pcb图转换成pdffile——smart pdf——next——选择current Document[****.SchDoc]一项——next——在该页面下选择你的原理图文件或者连你的pcb文件也一同选上——next——next——next——next——在这个页面下你看你个人喜好了,如果不想多生成什么文件的话就把下面那个save setting to output job document的对勾去掉——finish,之后就好了。

pdf文件就保存在你的工程文件夹下4、altium designer 9怎么画斜线Shift+Space将走线方式更改至Any Angle(任意角度)后即可拉斜线。

如果切换走线方式不出现Any Angle的话,检查Preferences中是不是勾选了Restrict to 90/45°。

请问Restrict to 90/45°在哪能找到在PCB编辑器界面下,快捷方式T、P,在preferences里面找5、Altium Designer技巧:如何确定PCB板大小选择【Design】->【Board Shape】->【Define from selected objects】6、altium designer 如何在pcb时把底板增大Design >> Board Shape >> Redefine Board Shape7、Altium Designer 中在PCB环境下怎么一次性修改元件标号字体大小?在PCB环境下,单击一个TXT,然后右击,find similar object(shift+F)就会弹出你第一个窗口,object kind栏里面选择same 应用确认,发现所有的txt都被选中,然后打开你第二个对话框,就会有Text Height 和Text Width两个栏,然后修改就行了。

Altium-designer-规则检查常出的问题汇总

Altium designer 规则检查常出的问题汇总Altium designer 规则检查常出的问题汇总1.Rule Violations Count违反数2.Short-Circuit Constraint (Allowed=No) (All),(All)短路约束=不允许)(全部),(全部)3.Un-Routed Net Constraint ( (All) ) 26Un-Routed净约束(所有)26岁4.Clearance Constraint (Gap=9mil) (All),(All)间隙约束(间隙= 9 mil)(全部),(全部)5.Power Plane Connect Rule(Relief Connect )(Expansion=20mil) (ConductorWidth=10mil) (Air Gap=10mil) (Entries=4) (All)功率平面连接规则(救济连接)(扩展= 20 mil)(导体宽= 10 mil)(气隙= 10 mil)(条目= 4)(全部)06.Width Constraint (Min=8mil) (Max=20mil) (Preferred=15mil) (All)宽度约束(Min = 8 mil)( Max= 20 mil)(优先15例mil)(全部)问题应该出在你设置和实际的冲突,你的Protel所设置的最小线宽是25mil,最大线宽也是25mil,默认线宽还是25mil,这本没错,但可能是你的某根GND线不是25mil,或者你用了覆铜,而覆铜的线条(Track Width)也不是25mil,所以才出错!建议在Design 的Rule里设置一下Width Constraint的最大和最小线宽,调整到合适范围,就不会报错了。

7.Height Constraint (Min=0mil) (Max=1000mil) (Prefered=500mil) (All)高度约束(Min = 0 mil)( Max = 1000 mil)(优先= 500 mil)(全部)8.Hole Size Constraint (Min=1mil) (Max=150mil) (All)孔尺寸约束(Min = 1 mil)( Max = 150 mil)(全部)修改尺寸,设计孔大于你设置的规则的值9.Hole To Hole Clearance (Gap=6mil) (All),(All)洞孔间隙(间隙= 6 mil)(全部),(全部)引脚安全间距问题,一般是封装的问题,如果确定封装没问题,这个错误基本你可以忽略。

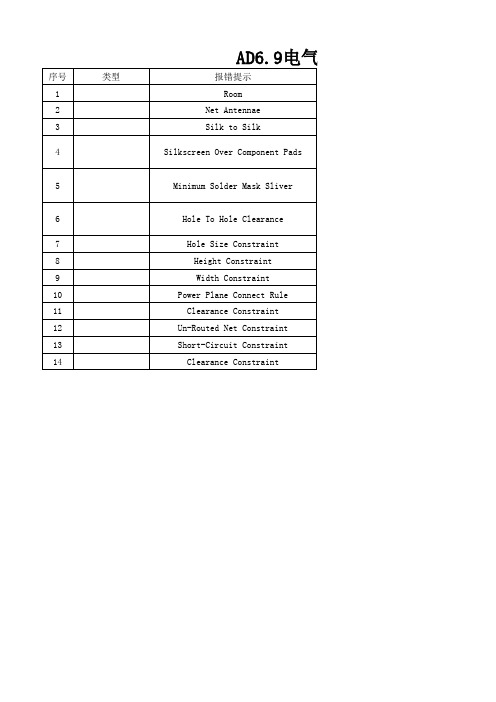

AD6.9电气规则检查报错说明

最低焊接面罩银

洞孔间隙 孔尺寸不在约束范围内 高度不在约束范围内 线径不在约束范围内 功率平面连接规则 线、元器之间距离不在约束范围内 有线路未连接 短路约束 间隙约束

调整线宽 检查未连接的走线,将其连上

AD6.9电气规则检查报错说明

序号 1 2 3 4 类型 报错提示 Room Net Antennae Silk to Silk Silkscreen Over Componiver

6 7 8 9 10 11 12 13 14

Hole To Hole Clearance Hole Size Constraint Height Constraint Width Constraint Power Plane Connect Rule Clearance Constraint Un-Routed Net Constraint Short-Circuit Constraint Clearance Constraint

9电气规则检查报错说明

错误原因 元器件超过Room界线 网络天线 丝印层与丝印层之间的间隙 顶层丝印与元件焊盘距离 有线路独立存在于Room中,未删除或者未连接 两个丝印之间的距离太近,这个错误可以忽略 按D、R将规则中的Silkscreen Over Component Pads 改小一些就可以了 你的某个元件的焊盘间距 大于1mil,你可以选 择该规则或者把封装中的焊盘间距改大一点。 引脚安全间距问题,一般是封装的问题,如果 确定封装没问题,这个错误基本可以忽略 解决办法

altium designer6.9遇到问题及总结

altium designer6.9遇到问题及总结问题现状描述:在PCB中布完线后,要将底层的布线和顶层的布线互换,如果实现?处理问题方法:1、把PCB切换到顶层,然后Edit / select / all on layer选择顶层。

2、Edit / selection memory-store ,选择1。

3、然后切换到底层,Edit / select / all on layer选择底层,然后Edit / selection memory-store ,选择2。

4、按F11用全局编辑把底层变为顶层,再Edit / selection memor y-recall,选择1,按F11用全局编辑把顶层变为底层,即可。

问题现状描述:altium designer 6.9 画的pcb,画好后想改线宽,怎样整体加粗啊?处理问题方法:右键,寻找相似属性,在线的那一栏选择same,这就选择好了所有的线,然后更改,选额左下角选择匹配,再更改就ok问题现状描述:altium designer怎么才能不经过原理图直接在空白pcb上加封装然后画线?处理问题方法:一、自己建立网表这种方法一般很少人用,要建立网表,得知道Altium网表的结构,那么就很好弄了;二、直接放元件,直接连接这种方法也是可以的,关键是在画线的时候把Online DRC关掉,就可以随意连线了,但是这种方法画的PCB如果出错了,系统是查不出来的,就看你自己了;三、在PCB里先写上网络名,再放入元件,再指定每个PIN的网络名Design==》Netlist==》Edit Nets在中间Nets In Class那一栏,点击下面的Add,再输入Net Name 点击OK,就把一个网络名建好了。

指定网络,双击元件的Pin在属性里就可以设置这个Pin的Net,这样就可以了。

这种方法的好处是,可以DRC。

四、当有别的格式的原理图时,就更好办了别的格式的原理图,一般都可以转成Alitum格式的,再导入PCB;如果不想转也可以导出Altium支持的网络表,用Altium打开网络表后,利用Show Differences 功能导入到PCB文件里。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

A l t i u m d e s i g n e r规则检

查常出的问题汇总

Revised by Jack on December 14,2020

Altium designer 规则检查常出的问题汇总

1.Rule Violations Count

违反数

2.Short-Circuit Constraint (Allowed=No) (All),(All)

短路约束=不允许)(全部),(全部)

3.Un-Routed Net Constraint ( (All) ) 26

Un-Routed净约束(所有)26岁

4.Clearance Constraint (Gap=9mil) (All),(All)

间隙约束(间隙= 9 mil)(全部),(全部)

5.Power Plane Connect Rule(Relief Connect )(Expansion=20mil) (Conductor

Width=10mil) (Air Gap=10mil) (Entries=4) (All)

功率平面连接规则(救济连接)(扩展= 20 mil)(导体宽= 10 mil)(气隙= 10 mil)(条目= 4)(全部)0

6.Width Constraint (Min=8mil) (Max=20mil) (Preferred=15mil) (All)

宽度约束(Min = 8 mil)( Max= 20 mil)(优先15例mil)(全部)

问题应该出在你设置和实际的冲突,你的Protel所设置的最小线宽是25mil,最大线宽也是

25mil,默认线宽还是25mil,这本没错,但可能是你的某根GND线不是25mil,或者你用了覆铜,而覆铜的线条(Track Width)也不是25mil,所以才出错!建议在Design 的Rule里设置一下Width Constraint的最大和最小线宽,调整到合适范围,就不会报错了。

7.Height Constraint (Min=0mil) (Max=1000mil) (Prefered=500mil) (All) 高度约束(Min = 0 mil)( Max = 1000 mil)(优先= 500 mil)(全部)

8.Hole Size Constraint (Min=1mil) (Max=150mil) (All)

孔尺寸约束(Min = 1 mil)( Max = 150 mil)(全部)

修改尺寸,设计孔大于你设置的规则的值

9.Hole To Hole Clearance (Gap=6mil) (All),(All)

洞孔间隙(间隙= 6 mil)(全部),(全部)

引脚安全间距问题,一般是封装的问题,如果确定封装没问题,这个错误基本你可以忽略。

10.Minimum Solder Mask Sliver (Gap=1mil) (All),(All)

最低焊接面罩银(间隙= 1 mil)(全部),(全部)

你的某个元件的焊盘间距大于1mil,你可以选择该规则或者把封装中的焊盘间距改大一点。

11.Silkscreen Over Component Pads (Clearance=1mil) (All),(All)

丝网印刷在组件垫(许可= 1 mil)(全部),(全部)

顶层丝印与元件焊盘距离近(小于1mil)按D、R将规则中的Silkscreen Over Component Pads 改小一些就可以了

12.Silk to Silk (Clearance=1mil) (All),(All)

丝印丝印(间隙= 1 mil)(全部),(全部)

两个丝印之间的距离太近,这个错误可以忽略

13.Net Antennae (Tolerance=0mil) (All)

网络天线(耐受= 0 mil)(全部)

14.Clearance Constraint (Gap=6mil) (InComponent(U1)),(All)

间隙约束(间隙= 6 mil)(InComponent(U1)),(所有)

线宽间距超出安全间距。