(完整版)基于FPGA的交织器和解交器的实现

交织/解交织器的FPGA实现

兰 兰 兰 兰 兰

l 1

8 / -

数 据 输 入

BLOCK RAM

一2

据 、 、 J 控制 榆 一

信 号 发生

读 写

写起始控制

读地 址发 生器

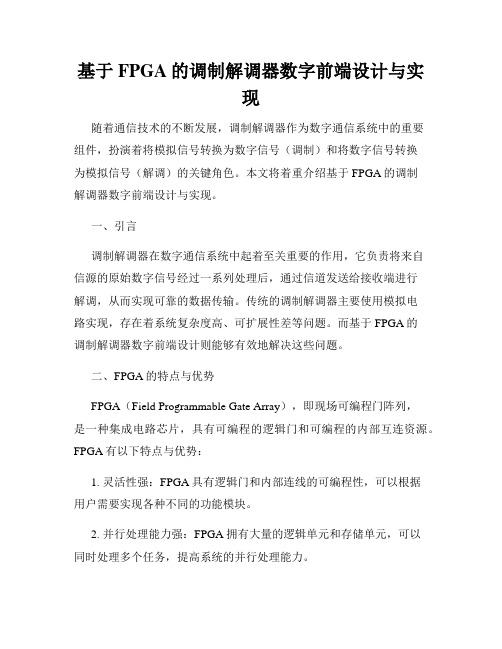

图 2 P A 实现 交织 器 的原 理框 图 F G

如果读、 写地址序列具有较强的规律性, 可以用在 F G P A中构造计数器的方式来直接 产生。如交织器的几个参数分别为 : -29 d 、d=【1一 /] 2 ,则可将 l 位地 n 1、I=8 i 29l 8= 8 = 1

2 交织深度固定的码段交织器实现的原理 . 2

图 3为交织器和解交织器实现的基本原理图,其中 I 表示交织深度。由图可见,共 有1 个通道 , 输入数据依次进入第 0 I 通道, 到 — l 并按照各 自通道上的延时规律输出, 交

织器和解交织器相同通道上的延时是互补的,延时之和均为 M× —) ( 1。这样经过发射机 I 交织器数据输出的先后顺序被打乱,再经过接收机解交织器又被重新恢复。 由于交织和解交织要对数据进行有规律的延时处理 ,所以输入数据首先被存入一双 口 R M 中,然后经过一定时延后被读出。此延时由双 口 R M 的读写地址来控制,因 A A

维普资讯

电信技术研究

20 年第 4 06 期

交织/ 解交织器的 F G P A实现

肖永 辉

摘要:交织和解交织是组合信道纠错 系统的一个重要环节,交织器和解交织器的实 现方法有多种 本文利用 Xl x i 公司开发的软件平台,设计比较通用的实现交织器 i n 和解 交织 器的方案 。

数字通信中常用的交织器按交织方式可分为分组交织器和随机交织器两种 ,按交织

卷积交织器原理及fpga实现

卷积交织器原理及fpga实现卷积交织器是一种用于数字信号处理的算法,它可以将输入信号与卷积核进行卷积运算,并输出卷积结果。

卷积交织器的原理是将输入信号分成多个子信号,每个子信号与卷积核进行卷积运算,然后将所有子信号的卷积结果交织在一起,得到最终的卷积结果。

卷积交织器的实现可以使用FPGA(Field Programmable Gate Array)技术。

FPGA是一种可编程逻辑器件,可以根据需要进行编程,实现各种数字电路。

使用FPGA实现卷积交织器可以提高运算速度和效率,同时也可以减少功耗和成本。

在FPGA实现卷积交织器时,需要进行以下步骤:1. 设计卷积交织器的电路结构。

根据卷积交织器的原理,设计出合适的电路结构,包括输入信号的分割、卷积核的存储、卷积运算和结果交织等模块。

2. 编写卷积交织器的Verilog代码。

Verilog是一种硬件描述语言,可以描述数字电路的行为和结构。

根据电路结构设计,编写Verilog代码实现卷积交织器的功能。

3. 进行仿真和验证。

使用仿真工具对Verilog代码进行仿真,验证卷积交织器的正确性和性能。

4. 进行综合和布局布线。

综合是将Verilog代码转换为FPGA可识别的逻辑网表,布局布线是将逻辑网表映射到FPGA芯片上的物理位置和连接关系。

5. 下载到FPGA芯片上运行。

将综合和布局布线后的设计文件下载到FPGA芯片上,进行实际运行测试。

使用FPGA实现卷积交织器可以提高运算速度和效率,同时也可以减少功耗和成本。

在实际应用中,卷积交织器可以用于图像处理、语音识别、信号处理等领域,具有广泛的应用前景。

基于FPGA的Turbo码交织器的设计与实现

i tr a e s h me i p e e t d,a d t e i lme tt n w t P sg v n n e l v c e s r s n e n h mpe n ai ih F GA i ie .Th i d t n u ig t e s f r e o e smt ai sn h ot e o wa

维普资讯

第2 5卷

第 4期

天

津

工

业

大

学

学

报

V 12 No 4 0. 5 .

Au u t 2 06 g s 0

20 0 6年 8月

J oURNAL oF TI ANJ N I PoL YTECHNI I I C VERS T I Y

o AX + PLUSI ndc ts t tt e c m bn d i e la e a a d a t g ss c sl w i e r rr t fM Ii ia e ha h o ie ntre v rh s m ny a v n a e u h a o bt ro ae,p o r— csigq c l e sn uik y,e s o b dfe n O o a yt e mo iid a d S n. Th r fr h ne l a e shih p a t lv l . e e oe t e i tre v rha g r ci aue ca

要组 成部 分 . 论 研 究 和仿 真 结果 表 明 J 交 织 器 在 理 , T ro 的性 能 中起 到 了关 键 作 用 . 织 器 的设 计 是 ub 码 交

T ro 设 计 中的一个 重要 方 面 , 同交织 器 对于 T r ub 码 不 u*

织器 实 际上是 一个 置换 器 , 最 大程 度 地 置 乱 输 入 信 它

基于FPGA的极化码交织器设计与实现

科技与创新┃Science and Technology &Innovation·22·2019年第12期文章编号:2095-6835(2019)12-0022-03基于FPGA 的极化码交织器设计与实现向明尚,张志华,潘丽艳(东北石油大学,黑龙江大庆163318)摘要:极化码作为信道编码,对于突发的连续错误纠正能力有限,可采用交织技术加以解决。

分析3GPP 交织模式定义和子交织模式的实现算法,以FPGA 为基础,利用ROM 模块设计存储交织模式的模式存储器,利用RAM 模块设计存储编码信息的数据存储器。

根据交织算法设计控制电路,设计和实现了交织器数字电路,经仿真测试电路工作理想,可以实现5G 控制信道短码传输中的交织过程。

关键词:交织模式;交织算法;FPGA ;数字电路中图分类号:TP311文献标识码:ADOI :10.15913/ki.kjycx.2019.12.0081引言Polar 码是基于信道极化现象提出的一种编码方案[1],在设计时并没有考虑码距特性,而是利用了信道联合与信道分裂的过程来选择具体的编码方案[2],是目前理论上证明唯一可以达到香浓极限[3]传输的信道编码方案,已被3GPP 选为5G eMBB 场景控制信道编码标准。

随着5G 技术逐步走向商用,在移动通信过程中对信息安全、可靠的传输要求越来越高。

为保证信息的可靠传输,需要用到各种编码技术来纠正信道中产生的随机错误。

当传输过程中产生突发性的干扰,用纠错编码理论和技术进行纠错需要很长的码字,增加了复杂度且延时较长。

交织技术与纠错编译码技术相结合,可以把突发错误离散成随机错误,在随机错误状态进行译码纠错,可取得良好的效果[4],使突发错误引起的码字个数在规定的安全范围内。

交织编码主要应用于有记忆信道,特别是无线信道,以此来纠正成串发生的比特差错和一些突发错误[5]。

发送端加上交织器,接收端接收到交织后的信息后,按照一定的规律进行解交织,即可还原信息。

基于FPGA的交织器,深圳大学,通信系统中串行数据交织器的设计

深圳大学实验报告课程名称:硬件描述语言与逻辑综合实验项目名称:通信系统中串行数据交织器的设计学院:电子科学与技术学院专业:电子科学与技术指导教师:刘春平报告人学号:班级:电子(2)班实验时间:实验报告提交时间:一、实验原理交织器是通信编码中抗突发干扰的一种重要手段,将突发干扰产生的分布集中的误码分散到信息数据中,以便采用纠错编码的方法进行纠错。

本项目要求设计一个行列交织器,如图所示,PN码发生器模拟数据源产生串行数据,按行写入一m行n列的RAM中,写满后按列读出。

为避免数据丢失,需使用两个这样的RAM交替读写。

即一个读时,另一个写。

一个写时,另一个读,这样交替循环。

因此,会产生一个周期的延时。

这里统一要求m和n都选4.二、源程序module jiaozhiqi(out,waveout,clk);//输出未交织的out和交织后的waveout,输入50Mclk时钟output out,waveout;input clk;reg [0:0]out;reg [0:0]waveout;reg A0,A1,A2,A3;reg mem_A[3:0][3:0];//4*4的二维寄存器型数组mem_Areg mem_B[3:0][3:0];//4*4的二维寄存器型数组mem_Binteger i,j;reg clock,flag;reg[31:0] count;initial//初始化各变量begini<=0;j<=0;A0<=1;A1<=0;A2<=0;A3<=1;flag<=0;count<=0;clock<=0;end//将clk分频,产生交织器所需的频率clockalways @(posedge clk)beginif(count==1)begincount<=0;clock<=~clock;endelsecount<=count+1;endalways @(posedge clock) //伪随机码发生器beginA0<=A0^A3;A1<=A0;A2<=A1;A3<=A2;endalways @(posedge clock)//对mem_A或mem_B中的数据进行交织beginj=j+1;if(j>3) //利用i和j控制mem_A和mem_B按行输入,按列输出beginj=0;i=i+1;endif(i>3)begini=0;flag=~flag;//每输入完16个数据,标志位发生一次变化。

基于FPGA的调制解调器数字前端设计与实现

基于FPGA的调制解调器数字前端设计与实现随着通信技术的不断发展,调制解调器作为数字通信系统中的重要组件,扮演着将模拟信号转换为数字信号(调制)和将数字信号转换为模拟信号(解调)的关键角色。

本文将着重介绍基于FPGA的调制解调器数字前端设计与实现。

一、引言调制解调器在数字通信系统中起着至关重要的作用,它负责将来自信源的原始数字信号经过一系列处理后,通过信道发送给接收端进行解调,从而实现可靠的数据传输。

传统的调制解调器主要使用模拟电路实现,存在着系统复杂度高、可扩展性差等问题。

而基于FPGA的调制解调器数字前端设计则能够有效地解决这些问题。

二、FPGA的特点与优势FPGA(Field Programmable Gate Array),即现场可编程门阵列,是一种集成电路芯片,具有可编程的逻辑门和可编程的内部互连资源。

FPGA有以下特点与优势:1. 灵活性强:FPGA具有逻辑门和内部连线的可编程性,可以根据用户需要实现各种不同的功能模块。

2. 并行处理能力强:FPGA拥有大量的逻辑单元和存储单元,可以同时处理多个任务,提高系统的并行处理能力。

3. 可扩展性好:FPGA的内部资源可以根据需要进行重新编程,方便系统的升级和扩展。

三、调制解调器数字前端设计与实现基于FPGA的调制解调器数字前端设计与实现主要包括以下几个关键步骤:1. 数据采样与量化调制解调器的数字前端首先需要对模拟信号进行采样与量化。

在FPGA中,可以通过使用ADC(Analog-to-Digital Converter)模块对模拟信号进行采样,并将采样值转换为数字信号。

同时,可以通过使用DAC(Digital-to-Analog Converter)模块将数字信号转换为模拟信号。

2. 数字滤波采样与量化之后的数字信号需要进行数字滤波处理,以去除不需要的频率成分,并减小信号的噪声。

在FPGA中,可以通过使用FIR (Finite Impulse Response)滤波器或IIR(Infinite Impulse Response)滤波器等模块来实现数字滤波功能。

(完整版)基于FPGA的交织器和解交器的实现

ftTian jin University of TTechnolo^专业设计报告基于FPGA的交织器和解交器的实现班级: 08集成专业:学院: 电子信息工程指导老师::交织器原理 .........1实现原理… 2 纠错原理交织器的FPGA 实现1 整体结构2 功能分析3 模块设计( 1)计数器模块 2)选择器模块(3) ROM 模块 (4) RAM 模块5)顶层模块设计总结目录.14一:交织器原理1 实现原理 随着通信技术的发展,对系统要求不断提高,在移动通信领域,由于数字信号在传输 途中会随各种干扰,使得信号失真,因此需要利用编码技术来纠正信道中产生的随机错误。

但是, 仅利用纠错编码技术, 对于传输过程中突发性干扰需要借助很长的码字, 这样会很复 杂,同时产生很长的延时, 。

交织技术作为一项改善通信系统性能的方式,将数据按照一定 的规律打乱, 把原来聚集的错误分散, 使得突发错误变为随机错误, 使得突发码字个数在纠 错范围内,接收端就 可以用较短的码字进行纠错。

交织的过程就是将一个数据系列按一定的条件进行位置从新排布。

其逆过程就是解交。

常用交织器主要有三种: 矩阵分组式, 伪随机式, 半伪随机式。

本设计采用矩阵分 组式。

矩阵分组式的原理及实现方式如下:从存储器按行输出, 送入突发差错的信 完成交织与反交织,即按行输入,按列输出。

按行读出x12, x1, x5, x9, x13,…x15)第一个产生与 x0到X12,连错4个,第二个产生于x9到x2,连错三个,则此收到的信号为,([xO] ,[x4] ,[x8],[x12] ,x1,x5, [x9],[X13] , [X2] , X6, X10, X14, X3, X7, X11, X15) (加[] 的为错误信号 )假设发送X =(x1 x2 x3 ..X 16 )首先将 X 送入交织器,此交织器设计为按行取出的 4x4 的阵列存储器。

基于FPGA实现的交织编码器

时 钟输 入

双 端 口R M A

时 钟输 出

写地址产生 >

< 读地址产生

顺序地址 从存储 器 中读 出 。

图 3 交 织 编码 器 工 作 原理 方 框 图

2 交 织编 码 器 的 电 路设 计 及 仿 真 结 果

本设计采用 ‘ 序写入 , 顺 乱序读 出” 的方法。 4 图 是 4 4 织编码 器 的电路图 , x交 双端 口 RA 由“ m M l p lm p 宏 模块构 成 。 ' d' a ’

图 3是利 用双 端 口 RA 实 现的交织 编码器工 M

作原理方框图, 由图可看出, 交织编码器设计的关键

所 谓线性交 织编码 器,是指把 纠错编码 器输 出

信号均匀分成 组, 每个码组由嘏 数据构成, 这 样就构成一个r 肌 / 的矩阵 ,  ̄ 如图 2 所示。 数据 以口 l l。

能, 当用作存储器时 , 其存储数据的宽度和深度可任

意指定 , 甚至还可以把若干个 E B连接起来组成容 A 量更大的存储单元。因此利用存储器可以构造出交

中图分 类号 :N993 T 1.

文献标 识码 : A

文 章 编 号 :0 98 8( 0 8 0 .0 50 1 0 .9 4 2 0 )30 3 .3

广泛 应用 的现场可编 程 门阵列 ( P A) 一种 FG 是 新 兴的可 编程逻辑器 件 , 具有更 高的密度 、 更快 的工 作 速度 和更大 的编程灵 活性 。被广泛 应用于各种 电 子类产 品 中。本文采用 F G P A技术来 克服数字通 信

在于 ‘ / 读 写地址” 的产生 。一 般有 2种设计 ‘ / 地 ‘ 写 { 卖

数据通信中交织与解交织的FPGA实现

是很大的,从而带来较大的时延 。 因此 , 在所需的 时延容限范围内,才可以使用交织。 在本课 题 中 , 传输 的数字 信 号进行 B H3 , 对 C ( 1 交织 ( 或称 为交错 )是 在复合 差错 信道 上使用 1 编 码技 术 的一种 简单 而有效 的方 法 。这种 方法 可 2) 格式的编码与解码 。在发送端,信号源 的信 C 进入交织模块, 以将一条突发信道转换成一条独立差 错的信道, 并 号加上子帧同步码进行 B H编码 ,

收稿 日期 :2 0 -6 1. 0 1 -5 0

c mmu ia i nh sb e i r d c dt e l t h u s- r r o nc t o a e nito u e od a wi l ht eb rter D

i lyc a ne.S v rl d r ̄・e eaintemiu s t iig nr a h n 1 e ea de g n rt e a o e l q e uizn l F GA h sb e o ae n ie se nd ti Co iig P a e nc mp rda ddsu s di eal mb n n teFP h GA e ieo d vc fALnj e ip i , tet- iitrev r RA o la y h btnela e l l h a d enela e b s d i 日) tc n lg h v b e n d itrev r ae Ol A e h oo y a e e n d v lp d a du e ii l y t c esul . e eo e n sdi adgt se s c sf l n as m u y

关键词 :交织器;解 交织器;L M;地址序列 ;F GA P P 中图分类号 :T 1.2 N9 7 1 文献标识码 :A

数字视频广播系统中交织器与解交织器的FPGA实现

在发射端 ,将要发射的输入数据通过交织器 , 其顺序被打乱 ,使得数据序列 的相关性被大大减 弱, 这样做 的突出优点就是可以很好地降低突发性 错误 的危害。而在接收端通过相反 的处理把数据恢

据延迟下 , 卷积交织所需 的存储器 比矩 阵交织减少 半 , 以一般 采用 卷积 交织 。 所

摘要 : 本文首先介绍了交织解交织的基本原理 , 并针对数字视频广播 系统提 出了优化 方案, 着重 分 析 了其 工作原 理及 各组 成模 块 的具体设 计 , 采用 V r g HL编 写程序 , 后用 F G 以 实现 。 e io D l 最 PA加

关键 词 : 字视 频广播 数 交织 解 交织 FG PA

维普资讯

…

…

…

…

…

…

…

…

…

…

…

・

・

集成电s 用 … … … … … ・ n 照 … … … … … …・ ; 摩

A pplcat o i

数 字视 频 广播 系统 中交织 器 与解 交织器 的 F G P A实现

周 加铳

( 同济大学通信软件及专用集成电路设计 中心 2 09) 002

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

d1: in integer range 0 to n-1;

sel:in std_logic;

yout: out std_logic_vector(7 downto 0));

end mux2;

architecture if_march of mux2 is

ram(conv_integer(ad))<=di;

end if ;

end if ;

end process;

end rtl;

(5)顶层模块

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

entity top is

ram_word'("00000000"),

ram_word'("00000000"),

ram_word'("00000000"),

ram_word'("00000000"),

ram_word'("00000000"),

ram_word'("00000000"),

ram_word'("00000000"),

component rom_16_8

port(addr: in integer range 0 to n-1;

clk: in std_logic;

data: out std_logic_vector(7 downto 0));

end component;

component mux2

port(d0:in std_logic_vector(7 downto 0);

专业设计报告

基于FPGA的交织器和解交器的实现

一:交织器原理………………………………………………………………………2

1实现原理………………………………………………………………2

2纠错原理……………………………………………………………2

二交织器的FPGA实现

1整体结构…………………………………………………………………3

(4)RAM模块

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity ram_16_8 is

port (ad:in std_logic_vector(7 downto 0);

2功能分析…………………………………………………………………3

3 模块设计………………………………………………………………4

(1)计数器模块………………………………………………………4

.

(2)选择器模块………………………………………………………5

(3)ROM模块………………………………………………………6

clk :in std_logic ;

di:in std_logic_vector(7 downto 0);

do:out std_logic_vector(7 downto 0);

wr_en: in std_logic:='0';

rd_en: in std_logic :='0');

end ram_16_8;

3模块设计

(1)计数器模块

计数器的作用是,为选择器提供顺序地址,为rom提供地址

VHDL描述如下:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

ty countern is

generic(n:integer:=16);

else

cout<='0';

end if ;

end process;

end rtl;

仿真波形如下:

(2)选择器模块

VHDL描述如下

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

entity mux2 is

generic (n:integer:=16);

use ieee.std_logic_1164.all;

entity rom_16_8 is

generic(n:integer:=16);

port(addr: in integer range 0 to n-1;

clk: in std_logic;

data: out std_logic_vector(7 downto 0));

begin

process(d0,d1,sel)

begin

if(sel='1') then

yout<=conv_std_logic_vector(d1,8);

else

yout<=d0;

end if;

end process;

end if_march;

选择器仿真波形如下图

:

(3)ROM模块

library ieee;

rom_word'("00001011"),

rom_word'("00001111"));

begin process(clk)

begin

if clk'event and clk='1' then

data<=rom(addr);

end if;

end process;

end rtl;

ROM模块仿真波形图

交织的过程就是将一个数据系列按一定的条件进行位置从新排布。其逆过程就是解交。

常用交织器主要有三种:矩阵分组式,伪随机式,半伪随机式。本设计采用矩阵分组式。

矩阵分组式的原理及实现方式如下:

假设发送X=( )首先将X送入交织器,此交织器设计为按行取出的4x4的阵列存储器。送入交织器后,从存储器按行输出,送入突发差错的信道,信道输出在送入反交织器,完成交织与反交织,即按行输入,按列输出。

rom_word'("00000000"),

rom_word'("00000100"),

rom_word'("00001000"),

rom_word'("00001100"),

rom_word'("00000001"),

rom_word'("00000101"),

rom_word'("00001001"),

(4)RAM模块…………………………………………………………7

(5)顶层模块…………………………………………………………9

三设计总结…………………………………………………………………….14

一:交织器原理

1实现原理

随着通信技术的发展,对系统要求不断提高,在移动通信领域,由于数字信号在传输途中会随各种干扰,使得信号失真,因此需要利用编码技术来纠正信道中产生的随机错误。但是,仅利用纠错编码技术,对于传输过程中突发性干扰需要借助很长的码字,这样会很复杂,同时产生很长的延时,。交织技术作为一项改善通信系统性能的方式,将数据按照一定的规律打乱,把原来聚集的错误分散,使得突发错误变为随机错误,使得突发码字个数在纠错范围内,接收端就 可以用较短的码字进行纠错。

architecture rtl of ram_16_8 is

subtype ram_word is std_logic_vector(7 downto 0);

type ram_table is array (0 to 15) of ram_word;

signal ram:ram_table:=ram_table'(

经过交织去交矩阵输出为([x0],x1,[x2],x3,[x4],x5,x6,x7,[x8],x9,x10,x11,[x12],[x13],x14,x15)可以看到原来的四连错和三连错变成了随机性独立差错。

二交织器的FPGA实现

1整体结构

交织器总是按顺序写入数据,然后按交织地址读出数据。解交的过程与此过程相反,按解交地址写入数据,再按顺序读出数据就可以了。因此交织器和解交器可以按相似电路完成。

d1: in integer range 0 to n-1;

sel: in std_logic;

yout:out std_logic_vector(7 downto 0));

endcomponent;

component ram_16_8

port( ad:in std_logic_vector(7 downto 0);

end rom_16_8;

architecture rtl of rom_16_8 is

subtype rom_word is std_logic_vector(7 downto 0);

type rom_table is array(0 to 15) of rom_word;

constant rom :rom_table:=rom_table'(

ram_word'("00000000"),

ram_word'("00000000"));

begin process(clk)