第6章 布局布线

第六章综合布线+水平子系统的设计和安装技术

第六章练习题一.掌握水平子系统的设计原则。

1.性价比最高原则这是因为水平子系统范围广、布线长、材料用量大,对工程总造价和质量有比较大的影响。

2.预埋管原则认真分析布线路由和距离,确定缆线的走向和位置。

新建建筑物优先考虑在建筑物梁和立柱中预埋穿线管,旧楼改造或者装修时考虑在墙面刻槽埋管或者墙面明装线槽。

因为在新建建筑物中预埋线管的成本比明装布管、槽的成本低,工期短,外观美观。

3.水平缆线最短原则为了保证水平缆线最短原则,一般把楼层管理间设置在信息点居中的房间,保证水平缆线最短。

对于楼道长度超过100米的楼层,或者信息点比较密集时,可以在同一层设置多个管理间,这样既能节约成本,又能降低施工难度,因为布线距离短时,线管和电缆也短,拐弯减少,布线拉力也小一些。

4.水平缆线最长原则按照GB50311国家标准规定,铜缆双绞线电缆的信道长度不超过100米,水平缆线长度一般不超过90米。

因此在前期设计时,水平缆线最长不宜超过90米。

5.避让强电原则一般尽量避免水平缆线与36伏以上强电供电线路平行走线。

在工程设计和施工中,一般原则为网络布线避让强电布线。

如果确实需要平行走线时,应保持一定的距离,一般非屏蔽网络双绞线电缆与强电电缆距离大于为30厘米,屏蔽网络双绞线电缆与强点电缆距离大于7厘米。

如果需要近距离平行布线甚至交叉跨越布线时,需要用金属管保护网络布线。

6.地面无障碍原则在设计和施工中,必须坚持地面无障碍原则。

一般考虑在吊顶上布线,楼板和墙面预埋布线等。

对于管理间和设备间等需要大量地面布线的场合,可以增加抗静电地板,在地板下布线。

二.掌握水平子系统的设备安装方法和技巧。

(一)安装施工原则1.埋管最大直径原则预埋在墙体中间暗管的最大管外径不宜超过50mm,预埋在楼板中暗埋管的最大管外径不宜超过25mm,室外管道进入建筑物的最大管外径不宜超过100mm。

2.穿线数量原则不同规格的线管,根据拐弯的多少和穿线长度的不同,管内布放线缆的最大条数也不同。

第六章 MOS电路版图设计讲解

VDD MP Vo MN

(2) 根据负载CL情况和速度 要求(tr和tf) 确定等效的 PMOS管和NMOS管的最小 W/L 。

o增大 Vi

0

V*

VDD

6.1.1 MOS管宽长比(W/L)的确定 2. CMOS逻辑门电路(续) (3) 根据上述结果最终确定等效的 Vi PMOS管和NMOS管的最小W/L。 (4) 根据电路结构和等 效的W/L确定每个管 的W/L 。 无比电路VOL与o无关 nor2

选上升和下降时间都是300ns.

§6-2 版图的布局布线

思考题

1. 布局布线的策略是什么? 2. 复用单元设计有什么好处?

6.2.1 布局 1.布局的基本原则 芯片的布局设计是要解决电路图或逻辑 图中的每个元件、功能单元在版图中的位置 摆布、压焊点分布、电源线和地线以及主要 信号线的走向等。 首先确定电路中主要单元(元件)的位 置,再以主要单元为中心安置次主要单元和 次要单元。 相关单元(包括压点)要尽量靠近,以 主要单元为主调整单元(器件)的形状和位 置,方便布线,缩短布线。

6.2.1 布局 2.布局示例1 电子表芯片

液晶显示译码电路

定时电路

比较电路

走时电路

分频电路 振荡器

报 时 驱 动

调节控制电路

6.2.1 布局 2.布局示例2 存储器模块

读写 控制

输入输出

地址 译码

SRAM存储矩阵

6.2.2 布线 1. 布线基本原则 最常用的布线层有金属、多晶硅和扩 散区,其寄生电阻和寄生电容有所不同。 电源线、地线选择金属层布线,线宽要 考虑电流容量(一般1mA/m)。 长信号线一般选择金属层布线,应尽量 避免长距离平行走线。 多晶硅布线和扩散区布线不能交叉而 且要短。必须用多晶硅走长线时,应同时 用金属线在一定长度内进行短接。

pcb制作课程设计

pcb制作课程设计一、课程目标知识目标:1. 了解PCB(印刷电路板)的基本概念、发展历程及应用领域;2. 掌握PCB设计的基本原则、流程和技巧;3. 熟悉PCB制作过程中涉及的材料、设备和工艺;4. 了解我国在PCB领域的技术现状和发展趋势。

技能目标:1. 学会使用PCB设计软件进行原理图绘制和PCB布局布线;2. 能够根据实际需求设计简单的PCB电路板;3. 掌握PCB制作过程中的关键步骤和注意事项;4. 提高动手实践能力,能够独立完成PCB样品的制作。

情感态度价值观目标:1. 培养学生对电子技术的兴趣和热情,激发创新意识;2. 培养学生的团队协作精神,提高沟通与交流能力;3. 增强学生的环保意识,认识到废弃PCB对环境的危害;4. 培养学生严谨、细致的学习态度,提高分析和解决问题的能力。

课程性质:本课程属于电子技术实践课程,旨在让学生在实际操作中掌握PCB 设计制作的基本技能。

学生特点:学生具备一定的电子技术基础,具有较强的动手能力和探究欲望。

教学要求:结合学生特点,注重实践操作,以学生为主体,充分调动学生的积极性和主动性,实现课程目标。

在教学过程中,将目标分解为具体的学习成果,以便进行教学设计和评估。

二、教学内容1. PCB基本概念:介绍PCB的定义、分类、结构及功能;教材章节:第一章第一节。

2. PCB设计原则与流程:讲解PCB设计的基本原则、设计流程和布局布线技巧;教材章节:第一章第二节。

3. PCB设计软件应用:学习使用主流PCB设计软件进行原理图绘制和PCB布局布线;教材章节:第二章。

4. PCB制作材料与设备:介绍PCB制作过程中涉及的材料、设备和工艺;教材章节:第三章。

5. PCB制作实践:动手实践,完成PCB样品的制作;教材章节:第四章。

6. PCB检测与维修:讲解PCB常见故障的检测与维修方法;教材章节:第五章。

7. PCB发展趋势:介绍我国在PCB领域的技术现状和发展趋势;教材章节:第六章。

第六章 MOS电路版图设计

选上升和下降时间都是300ns.

§6-2 版图的布局布线

思考题

1. 布局布线的策略是什么? 2. 复用单元设计有什么好处?

6.2.1 布局 1.布局的基本原则

芯片的布局设计是要解决电路图或逻辑 图中的每个元件、功能单元在版图中的位置 摆布、压焊点分布、电源线和地线以及主要 信号线的走向等。

MOS管的源漏区具 有可互换性。

CMOS门电路设计举例

• 设计一个双输入端与非门 • 设计考虑四个方面: • 1,高低电平不用考虑; • 2,以工作频率为依据,根据速度和工艺水

平选W/L; • 3,根据W,L校验VNL和VNH; • 4,整个设计均从最坏情况入手。 设计过程是:

f tr ,t f p,n kp.kn

§6-5 版图设计方法

思考题

1.集成电路芯片设计有那些方法?各 种方法的优缺点时什么?

6.5.1全定制(full-custom)设计方法

1.概念及特点

利用人机交互图形系统,由版图设计者针 对具体电路和具体要求,从每个器件的图形、 尺寸开始设计,直至整个版图的布局布线。

可获得最佳的电路性能和最小的芯片尺寸, 有利于提高集成度和降低生产成本,适用于通 用芯片和高性能芯片的设计以及库单元的设计。

芯片设计者只要根据电路的逻辑网表及设 计约束条件,用相关软件调用标准库中的单元 进行布局布线,即可快速形成最终的芯片版图。

由于标准单元库是预先设计好的,不是为 某个芯片专门设计的,因此称为半定制设计方 法(semi-custom design approach)

6.5.2标准单元(Standard Cell)设计方法 2.特点

触发的必要条件:

寄生可控硅一

1.两个发射结均正偏 2.βnpn*βpnp> 1

第六章 选线与定线

1.地形特点

①地面坡度平缓,相对 高差较小(地面横坡, 相对高差小于30m)。 路线纵坡不受限制。

②一般多为耕地,地ቤተ መጻሕፍቲ ባይዱ障碍多。

除泥沼、淤泥、河谷漫滩、草原、戈壁、沙漠等外多为耕 地,良田多,土地贵;居民点较密,各种建筑物分布广。

③沟渠密布,河 网池塘多

一、影响路线方案的因素 1.道路的功能(意义和作用)--主要因素 高速、一级公路除必须经过的控制点外,不宜过多靠近城镇, 路线宜顺直短捷,区域性公路尽量靠近或经过经济控制点。 2.政治经济控制点—重要因素 主要的政治经济控制点,必须考虑通过,困难时,与支线连 接方案比较。 3.沿线自然条件的影响—直接影响(但影响程度随等级变化) 4.主要技术标准和施工条件的影响—一定程度影响

设计标准或设计水平

5.其它 与景点、文物、名胜等的联系

二、预可行性研究阶段路线走向选择

路线方案:是根据指定的路线总方向和道路的功能,考虑社会、经济 因素和复杂的自然条件等拟定的路线走向。 目的是合理地解决设计道路的起迄点和走向。 据点:公路网规划所规定的或上级部门所指定的一条路线的起终点和 中间必经重要城镇或地点。 走向:一系列据点的连线。两个据点之间常有若干可供选择的不同走 向。 预可行性研究阶段主要解决拟建项目起、终点间路线的基本走向问题。

技术设计阶段应在初步设计收集资料的基础上补充收集技术设计所需 的基础资料,测量影响路线线位的控制点和控制断面,采用纸上定线并进 行现场核对。

施工图设计阶段应进一步补充收集基础资料,测量影响路线线位的控 制点和控制断面,根据控制要素进行纸上定线并现场核对,测量放线,并 根据需要进行动态调整。

二、平原区选线

(4)与地方政府部门和相关单位就路线走廊、重要桥梁、隧道方案及 互通式立交的设置等重大事项作进一步协调,基本确定路线走廊方案。 (5)重点考虑路网结构布局合理、路线顺直、带动地方经济发展、方 便区域交通出行、建设条件(地形条件、工程地质条件、建设环境及施 工难易程度等)、环境影响和占用农田、主要工程数量和投资规模、路 线平纵面设计总体技术指标、公路养护、综合管理及运营效益、地方 政府及民众意见,综合进行路线方案比选。 (6)根据不同的路线走廊方案ꎬ在 1:1万地形图(大型控制性工程可采 用 1:5000地形图)上进行概略总体设计。包括路线、路基路面、桥涵、 隧道、立交、交通工程及沿线设施等,估算工程数量,进行投资估算。 (7)推荐路线走廊方案及主要控制点,并推荐路线走廊方案主要技术 指标及工程规模。

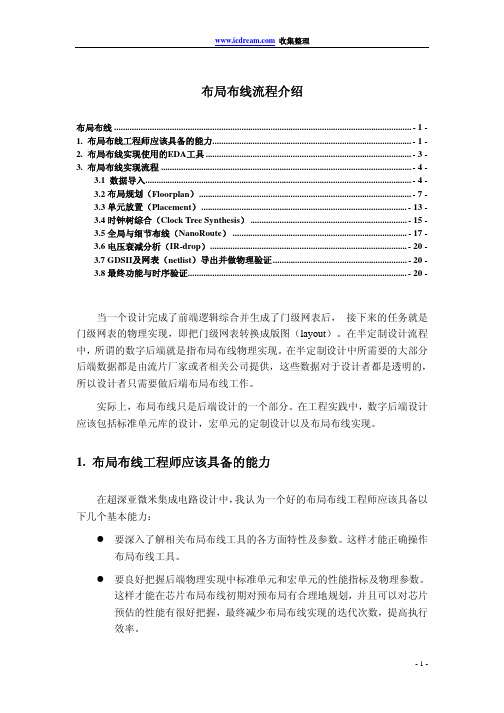

布局布线详细流程说明

布局布线流程介绍布局布线.....................................................................................................................................- 1 -1. 布局布线工程师应该具备的能力.........................................................................................- 1 -2. 布局布线实现使用的EDA工具............................................................................................- 3 -3. 布局布线实现流程................................................................................................................- 4 -3.1 数据导入.......................................................................................................................- 4 -3.2布局规划(Floorplan)...............................................................................................- 7 -3.3单元放置(Placement)............................................................................................- 13 -3.4时钟树综合(Clock Tree Synthesis)......................................................................- 15 -3.5全局与细节布线(NanoRoute)..............................................................................- 17 -3.6电压衰减分析(IR-drop)........................................................................................- 20 -3.7 GDSII及网表(netlist)导出并做物理验证............................................................- 20 -3.8最终功能与时序验证..................................................................................................- 20 -当一个设计完成了前端逻辑综合并生成了门级网表后,接下来的任务就是门级网表的物理实现,即把门级网表转换成版图(layout)。

第六章 MOS电路版图设计

6.2.2 布线 2. 布线示例

6.2.3 优化设计 1. 源漏区面积优化 相邻同型MOS 管源漏区相连接时 采用有源区直接连 接可以减小源漏区 面积,减小寄生电 容和漏电,也减小 了芯片面积。

1

2

6.2.3 优化设计 2. 器件排序优化 通过排序优化可以提高速度,减小漏电。

OUT OUT D A B C

A

D

B

C

OUT

OUT

GND

GND

6.2.3 优化设计 3. 宽沟器件的优化设计

(1)宽沟器件可以由 多个器件合成,方便 布局布线,减小栅极 电阻。 (2)宽沟器件源漏区 开孔要充分,提高沟 道特性的一致性(尤 其是模拟电路)。

6.2.3 优化设计 4. 复用单元的设计

将常用结构的 组合图形(包括电 路单元)按设计规 则要求设计为可复 用的单元,供设计 过程中调用, 减少设计错 误,并便于 修改。

CPU

标准单元dffps

6.5.2标准单元(Standard Cell)设计方法 1.概念 电路基本单元及各种I/O单元都按一定的标 准、依据特定工艺、由专门人员预先设计好存 放于一个统一的库中,称为标准单元库。 芯片设计者只要根据电路的逻辑网表及设 计约束条件,用相关软件调用标准库中的单元 进行布局布线,即可快速形成最终的芯片版图。 由于标准单元库是预先设计好的,不是为 某个芯片专门设计的,因此称为半定制设计方 法(semi-custom design approach)

6.3.3 内部电路的抗闩锁设计 版图示例1 dffpr

6.3.3 内部电路的抗闩锁设计 版图示例2

6.3.3 内部电路的抗闩锁设计 版图示例3

6.3.4 芯片外围电路的抗闩锁设计 外围电路主要是指输入/输出单元电路, 一方面易受高压影响,另一方面工作电流 很大。因此,极易发生闩锁效应,通常都 采用双环保护结构,而且保护环上要充分 开孔,用金属线直接连到电源或地上。

布局布线流程

布局布线流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor. I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!布局布线流程一、准备工作阶段在进行布局布线之前,需要进行充分的准备工作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

接下来,点击Design Imort窗口的Power,填写电源和地线的名字为vdd!和gnd!(见图6-6)。

点击Design Imort窗口的Timing,然后点击Timing Constraint File对应的书形图标,到dc/sdc目录下寻找标准时序约束文件(见图6-7)。

(1) 生成时钟Spec文件

操作方法为点ClockCreate Clock Tree Spec,将弹出图6-23所示窗口,需要将库中生成时钟树使用的cell加进来。

点“OK”后将生成一个文件,其中某些内容来自sdc文件,另一些是系统默认值。

(2)指定使用的时钟Spec文件

操作为ClockSpecify Clock Tree,然后找到需要使用的Spec文件,例如上一步骤生成的。

(5)映射文件

为加快运行速度,Encounter使用一种简化的cell符号进行布线,这种符号只有cell的轮廓和对外的管脚(pin),没有内部细节。在Encounter中也不能看到真正的版图,但Encounter最后可以输出一个GDS文件,将该gds文件导入到ICFB环境下,可以看到完整的版图。为在ICFB环境下正确显示版图信息,需要在输出时使用一个映射文件,该文件一般在库中提供。

第6章布局布线

4.1引言

IC设计的最终交付形式是向芯片制造厂家提供GDS格式的版图文件。逻辑综合以后,设计级别转换到了“门”级,在这个级别,电路是由各种cell构成的。尽管每个cell的版图已经存在,但对于复杂的设计,如何排列和连接这些cell还是十分烦琐的工作,只有使用自动布线工具才能在合理的时间内完成版图设计。在流行的IC设计流程中,自动布局、布线工具主要有两种,一是Synopsys的Astro,另一种是Cadence的Soc Encounter。两种布线工具各有优缺点,Soc Encounter的使用方法相对简单些,本讲义主要介绍基于Encounter的设计流程。

(6)I/O分布文件

如果是完整的芯片布线,必须提供一个有关I/O和电源/地线的PAD位置和方向的文件。如果是电路模块设计,一般也要指定PIN的位置和方向。I/O分布文件需要设计者编写。

有了上述文件,就可以进行基本的版图自动设计了,但在实现复杂的设计时,通常还要有其它的技术文件支持。

库文件存放在/iclibs/CSMCBCD05/se下,其中lef目录下的是LEF文件,TLF下存放的是时序文件。

在默认情况下,版图中“核区”的尺寸由“纵横比”和“核利用率”确定。“纵横比”为1的版图为正方型。默认的“核区利用率”是85%,意味着要保留一定的空间给以后需要插入的BUF,用来修正时钟树和优化时序。Core Margins是指“核区”到I/O PAD的间距,为在“核区”的外围布电源和地线环(rings),必须保留足够的间距。这里设为20μm,可以布下一个4μm的电源环和一个4μm的地线环。

选择FloorplanPower PlaningAdd Rings,将出现图6-13所示的窗口。在弹出窗口的nets一栏中,需要填写网络名称,该名称必须与前面填写电源和地线名称一致,这里是vdd!和gnd!。电源环线条的宽度、间距、与“核区”的间距等也需要设置。点CENTER IN CHANNEL

点OK后,将出现电源环,如图6-14。

(3)综合时钟树

操作为,ClockSynthesize Clock Tree,出现图6-25后,点“OK”,该操作生成时钟树。

(4)显示时钟树

选ClockDisplay可显示时钟树,见图6-26。

(5)报告时钟树

时钟树的详细情况需要在报告中反映。

6.7布线

详细布线使用RouteNanoRoute,出现图6-28后点OK。图6-29是布线结果。

Soc Encounter的功能很强,支持复杂的大规模Soc设计。本章以计数器为例介绍Encounter的基本使用方法。

4.2数据准备

“自动”的版图设计必须要有“门级”电路网表和规定格式的后端标准单元库。使用Encounter进行版图设计至少需要以下几种文件:

(1)物理库文件

物理库就是后端标准单元库。Encounter需要LEF(Libraries Exchange Format)格式的文件,以下简称LEF文件。LEF文件包含标准单元的版图尺寸、使用的金属层、引脚(PIN)的位置等设计信息以及各层之间的电容、电阻等工艺信息。只进行电路模块设计时,可只准备核单元的LEF文件,完整芯片设计还需要I/O单元的LEF文件。LEF文件通常由芯片生产厂家提供。

最小延迟库应选择IC05CScore_55_minbcdv10.tlf。

额定电源电压为3.3V和5V时,库的选择见表6-1。

表6-1核单元时序库

额定电压

3.3V

Max时序库

IC05CScore_30_maxbcdv10.tlf

Typ时序库

IC05CScore_33_typbcdv10.tlf

Min时序库

IC05CScore_36_minbcdv10.tlf

额定电压

5V

Max时序库

IC05CScore_45_maxbcdv10.tlf

Typ时序库

IC05CScore_50_typbcdv10.tlf

Min时序库

IC05CScore_55_minbcdv10.tlf

为确定IO引脚的方向,需要编写一个IO分配文件(已存放在../pin下),该文件可用任何文本编辑器编写,内容如下:

以下以计数器问题为例,介绍具体操作方法。

4.3导入设计

(1)启动Encounter

从socusr登录,进入en目录,打开一个命令输入窗口,输入encounter,回车后可看到图6-1。

(2)导入设计

在图6-1的主菜单上点DesignImport可以看到图6-2所示的窗口。

如果以前曾导入过设计,并将有关操作保存在一个文件中,可以点图6-2中的“Load”加载该文件。如果是首次导入文件,需要逐个添加需要的文件。

在加入时序库时需要根据额定电源电压来选择。由于芯片工作时,一般允许电源电压波动±10%,如果额定电源电压为5V,则最低工作电压为4.5,最高工作电压为5.5V,因此

典型时序(延迟)库应选择IC05CScore_50_typbcdv10.tlf,

最大时序(延迟)库应选择IC05CScore_45_maxbcdv10.tlf,

添加文件的基本方法是先点击文件类型对应的输入窗口右侧的“…”,点击将首先弹出图6-3所示窗口。

以下以添加LEF文件为例介绍后续操作方法。首先点击“LEF Files”右侧的“…”,出现图6-3后,点击其中的“书形”图标,该窗口将自动展开为图6-4。当前路径是/home/socusr/en,由于知道LEF文件在/iclibs/CSMCBCD05/se下,因此需要连续点击“..”,使当前目录改变到根目录,再逐级进入/iclibs/CSMCBCD05/se/lef,窗口中出现的文件如图6-5所示。

为避免每次都重复操作,点图6-7中主菜单的design回到图6-2的状态,点下方的Save,将以上设置方法保存到一个文件中,下次直接调用该文件就可自动完成以上操作。

为使Encounter能够根据时序要求插入BUF或延迟单元,需要Buffer Name和Delay Name,见图6-8。

最后点Design Import窗口下方的“OK”,在Encounter窗口中将出现图6-9所示的版图边界。

(2)电路网表文件

Encounter需要verilog格式的设计网表,该网表可由Design Compiler或其它逻辑综合工具生成,其中所有单元必须在LEF文件中存在。完整的芯片设计需要一个“顶层”文件,该文件也要使用verilog语言编写,必须包含I/O PAD单元及I/O单元与核单元的连接关系。

点“RouteSRoute”将出现图6-17,去掉其中的Block Pin和Pad Pins两个选项,点OK后Encounter将生成电源网格(见图6-18)。

(3)放置“退耦”电容

生成电源网格后,需要放“退耦”电容,方法为,点

PlaceFilterAdd End Cap

然后在弹出窗口(图6-19)中选择滤波cell。完成操作后可看到连接在电源和地线之间的滤波电容(见图6-20)。

点Encounter主菜单上的Tools,然后选Design Browser,可看到图6-10,说明设计已成功导入Encounter。

6.3布局规划

版图规划定义版图的实际形状或纵横比(aspect ratio),全局或细节布线栅格,核单元和I/O单元的排列方法,角单元的位置等信息。

在主菜单下选择FloorplanSpecify floorplan可以看到图6-11所示的窗口。

到此完成了初步布线结果,但这并不是最终的版图,以后需要对布线后的设计进行时序分析,如果存在时序问题,还要重新布局和布线。

(3)时序库文件

Encounter采用“时序驱动”的布线算法,为判断设计是否满足时序要求,必须有描述标准单元的时序关系的文件。Encounter可以读取TLF(.tlf)格式或Synopsys工艺库格式(.lib)的文件。时序文件要由芯片生产厂家提供。

(4)标准(时序)约束文件

为判断布线结果是否满足要求,用户对电路的时序约束也要以规定格式提供给Encounter。Encounter接受Design Compiler或Prime Time生成的标准时序约束文件,即使用write_script或write_sdc命令生成的文件。

假设决定使用3层金属布线,由于目前只想完成电路模块的版图,不需要加入PAD,所以只需要加入IC05CScore_3ltech.lef和IC05CScore_3l.lef两个文件。添加文件是有次序的,一定要先加入IC05CScore_3ltech.lef文件,再加入IC05CScore_3l.lef,因为前者包含了后者需要的工艺信息。