自动布局布线

《自动布局布线》课件

探索自动布局布线的奇妙世界,帮助你提高电路板或芯片的性能,节省时间, 减少错误。

什么是自动布局布线?

自动布局布线是一种方法,用于自动为电路板或芯片设计最佳电线布局。

为什么需要自动布局布线?

手动布线耗时且容易出错,而自动布局布线可以节省时间、减少错误,并提 高电路板或芯片的性能。

2 准确性

避免人为错误,提高电路板或芯片的性能。

4 高效

节省时间,快速完成布线任务。

自动布局布线的挑战

算法复杂度高

处理大规模网络布线的算法复杂度较高。

异常情况处理

对输入异常情况的处理较困难,需要更精细的算法设计。

CPU处理限制

处理大规模网络布线时,仅依靠CPU很难满足要求。

结论

自动布局布线能够帮助我们节省时间、减少错误,并提高电路板或芯片的性 能。

自动布局布线的流程,为后续布线准备。

2

网络构建

将电路元件在网格中建立连接,形成网络。

3

优化网络

对网络进行优化,使其满足性能要求。

4

生成布线

根据优化后的网络,生成最佳的电线布局。

自动布局布线的优势

1 自动化

提高效率,减少人工工作量。

3 可重复性

保持一致的布线质量。

尽管自动布局布线还面临一些挑战,但随着技术发展,我们可以期待它在未 来发挥更大的作用。

ASIC设计cadence自动布局布线工具_图文(精)

本节将使用综合工具(Design Compiler 对一个 8位全加器逻辑综合,并产生一个门级网表;利用该网表使用自动布局布线工具(Silicon Ensemble 生成一个全加器的版图。

首先输入 8位全加器 verilog 代码:module adder8(Cout,S,A,Cin;output Cout;output [7:0]S;input [7:0]A;input [7:0]B;input Cin;reg [8:0]SUM;reg [7:0]S;reg Cout;wire [7:0]A,B;always @(Aor B or CinbeginSUM [8:0]=A+B+Cin;S =SUM [7:0];Cout =SUM [8];endendmodule打开综合工具 DC (psyn_gui&File->Read..读入代码File->Setup..设置 3个相关工艺库将带红色 *号的 3个库设置如下图 Design->CompileDesign.. 编译Schematic->NewDesign Schematic View..可以看到综合后的顶层结构通过双击 C1模块还可以看到全加器的门级结构为了后面自动布局布线的需要, 这里我们要将这个综合结果保存为 adder8_nl.v 门级网表。

在 psyn_gui-xg-t>后输入如下命令下面进行自动布局布线 (一下有路径出现的地方要特别注意打开 Silicon Ensemble (sedsm&File->Import->LEF… 导入库的转换格式注意此文件的路径!File->Import->Verilog… 导入工艺库(此库为 verilog 描述的标准单元,包含各种延时信息这里去掉后面的!继续 File->Import->Verilog… 导入网表 adder8_nl.v(此处要先删掉第一个工艺库这里要加上顶层模块名 adder8Floorplan->InitializeFloorplan…准备工作完成开始布局布线点击 Variables 将里面的 PLAN.LOWERLEFT.ORIGIN 由 FALSE 改为 TUREEdit ->Add ->Row… Area 的区域可以直接点击 Area 并在图上拖拽,并使其大小与芯片核一致File->Saveas… 保存为 fplanRoute->PlanPower… 设置电源环在 Plan Power 窗口中点击 AddRings…Place->Ios…放置输入输出Place->Cells…放置单元Place->FillerCells->AddCells…Route->RoutePower->FollowPins… 添加管脚(金属线宽设为 1.8 Route->Wroute…布线View->DisplayOptions… 检查管脚名设置 Pin 为 ONFile->Export->DEF… 命名为adder8_wrouted.def打开 icfb &再导入 DEF文件之前要确保你有如下图中的一些库文件File->Import->DEF…Enter “ tutorial ” for Library Name, “ adder8” for Cell Name, and “ autoRouted ”for View Name.打开 View 中的autoRoutedDesign->Save..Tool->Layout..将提取图转换为版图,这里需要改变几个参数 Edit->Search..点击Add Criteria然后做如下图的几个改动Apply Replace AllDesign->SaveAs..现在就可以打开 layout 了DRC… 熟悉吧! !。

自动化设备电气布线规范幻灯片课件

自动化设备电气布线规范幻灯片课件一、引言随着工业自动化的不断发展,电气布线的重要性日益凸显。

为了保证自动化设备的稳定运行和安全性,我们必须遵循一定的电气布线规范。

今天,我将以幻灯片课件的形式,为大家讲解自动化设备电气布线的规范。

二、电气布线的基本原则1、安全性:在任何情况下,安全应该是首要考虑。

所有的电气线路和设备都应该安装在安全的环境中,以防止可能的电击、火灾等危险。

2、效率:布线应尽可能简洁、明了,避免线路交叉或冗余,以减少潜在的故障点和维护难度。

3、可维护性:线路应易于检查和维护。

任何故障都应能够方便地检测和修复。

4、兼容性:应确保所使用的线路和设备与自动化设备的其它部分兼容。

三、电气布线的具体规范1、线路颜色编码:根据国际电工委员会的规定,不同颜色的电线应连接到不同的线路上。

例如,红色电线应连接到电源正极,蓝色或黑色电线应连接到电源负极。

2、线路保护:所有电线都应有适当的保护,以防止机械损伤或过载。

例如,可以使用金属套管或塑料护套来保护电线。

3、线路标记:每条线路都应有清晰的标记,以方便识别和维护。

4、接地与屏蔽:所有金属部件和线路都应接地,以防止电磁干扰。

同时,对于可能受到电磁干扰的线路,应使用屏蔽线或光纤传输。

5、电源与信号布线:电源线和信号线应分开布线,以防止电磁干扰。

高电压和低电压的线路也应分开布线。

6、接线端子:所有接线端子都应牢固固定,以防止松动或接触不良。

同时,端子上的螺丝和螺母都应有适当的扭矩。

7、线路弯曲:线路应避免过度的弯曲或扭曲,以防止机械损伤或过载。

8、线路长度:在可能的情况下,应尽量减少线路的长度,以减少电阻和电感的影响。

9、防雷与过电压保护:对于可能受到雷电或过电压影响的线路和设备,应安装适当的保护装置。

10、环保:在设计和安装过程中,应尽量减少对环境的影响。

例如,应使用可回收的包装材料,减少废弃物的产生。

四、结论自动化设备的电气布线是一项重要而复杂的工作。

只有遵循一定的规范和标准,我们才能确保自动化设备的稳定运行和安全性。

第9讲_自动布线

PCB辅助设计第9讲自动布线主要内容一、自动布线步骤二、自动装载网络表与元件三、元件布局四、自动布线设计规则设置五、自动布线六、手工调整七、设计规则检查八、元件重新编号及原理图更新一、自动布线步骤PCB自动布线就是通过计算机自动将原理图中元件间的逻辑连接转换为PCB铜箔连接,PCB的自动化设计实际上是一种半自动化的设计过程,还需要人工的干预才能设计出合格的PCB。

PCB自动布线的流程如下。

⑴绘制电路原理图,生成网络表。

⑵在PCB99SE中,规划印制板。

⑶装载原理图的网络表。

⑷自动布局及手工布局调整。

⑸自动布线参数设置。

⑹自动布线。

⑺手工布线调整及标注文字调整。

⑻输出PCB图。

采用打印机或绘图仪输出电路板图。

二、自动装载网络表与元件规划PCB后,执行Design→Load Nets载入网络表,屏幕弹出一个对话框,单击Browse按钮选择网络表文件(*.net),载入网络表,单击Execute按钮,将网络表文件中的元件调到当前印制板中,如图7-17所示。

图7-17中,载入的元件都散开排列在禁止布线边框之外(Protel99SE SP6之前的版本中,元件堆积在光标处),在布线前还必须进行自动布局。

三、元件布局1.元件布局前的处理⑴元件布局栅格设置执行Design→Options,在弹出的对话框中选择Options选项卡,设置捕获栅格和元件栅格X、Y方向的间距大小。

⑵字符串显示设置执行Tools→Preferences,在弹出的对话框中选择Display选项卡,在Draft thresholds选项区域中,减小Strings中的字符串阀值,完整显示字符串内容。

⑶元件布局参数设置执行Design→Rules,在对话框中选中Placement选项卡,屏幕出现元件布局参数设置对话框。

一般选择默认。

2.元件自动布局进行自动布局前,必须在Keep out Layer上先规划电路板的电气边界,然后载入网络表文件,否则屏幕会提示错误信息。

单片机系统电路的印刷电路板设计(自动布线法)

二、加载网络表,自动调入元件封装

电路中的元器件所用封装一定要和已添加的封装库中的封 装保持一致,否则会出现错误提示。

三、检查并排除装入网络表时的错误

当出现错误时,要看清楚错在哪里,找出原因。一般情况下,先检查一下 所需要的封装库是否都打开,再回到原理图中修改有错元件的封装或者网络连 接的错误,重新生成网络表,再次在PCB图中装入网络表,直至装入网络状态 栏显示All macros validated。

单击Tools/Auto Placement/Auto Placer菜单命令,选中Cluster Place,单击OK。

群集布局,少于 100个元件时

统计布局,大于 100个元件时

快速放置选项

单击OK后开始自动布局,布局过程如下图示

根据元件布局原则,参考电路原理图进行手工调整,手 工调整元件后,结果如图所示。

上述选项卡可对PCB的编辑操作、视图的移动、交互式布线模式、板层颜 色、显示、系统默认值等进行一系列的设置。

四、规划电路板

进入PCB编辑界面,在板层显示状态栏单击KeepOutLayer标签,将当前 板层切换到禁止布线层。选择菜单命令Place/Line,或单击放置工具栏中的连 线图标 ,在禁止布线层上放置导线,划出电路板电气边界,如下图所示。

四、自动调入封装

单击Execute按钮,系统自动装入所有元件封装以及网络表。当正确引 入网络表后,所有元件及其连接关系都会自动调入PCB编辑界面,如下图 所示。

任务三:布局、布线的规则设置

一、布局规则设置

执行菜单命令Design/Rules,在弹出的设计规则对话框中选择Placement 选项卡,在选项卡中Rule Classes区域中共有5项自动布局规则设置。

Protel99自动布线步骤

6/14/2024

30

将 Maximum Hole 项中的 100 改为110 后单击ok项

6/14/2024

31

点击 Run DRC 项

6/14/2024

32

再点击Run DRC

6/14/2024

33

没有显示错误,表示成功完成设计

6/14/2024

34

主要步骤

调入原理图 生成网络表 规划PCB图 调入网络表 自动布局及手工调整 自动布线及手工调整 设计规则检查

6/14/2024

1

调入原理图

点击file菜单下的open项6/14/2024 Nhomakorabea2

打开名为ZBYLT原理图文件

6/14/2024

3

建立设计数据库

6/14/2024

4

打开原理图文件

18

点击所标识的选项开始自动布局

6/14/2024

19

选择自动布局参数

成组布局方式 统计方式

6/14/2024

20

布局过程

注意:此时不要进行任何操作,要等待一下

6/14/2024

21

自动布局完成

6/14/2024

22

手工调整将元件摆放整齐

6/14/2024

23

自动布线

6/14/2024

24

出现参数选择界面后点击Route All

6/14/2024

25

自动布线完成

6/14/2024

26

完成后的提示框

6/14/2024

27

设计规则检查

6/14/2024

28

点击所标识的选项

6/14/2024

29

自动布局布线

RESISTANCE RPERSQ 0.020000 ;

END metal3

VIA M1_POLY1 DEFAULT

# 定义怎样产生通孔,这里生成 metal1 与 poly1 之间的通孔。

# 注意, 这里产生的通孔是在上下两层都是 default width 时产生的, 当上下两层不是

default # width 时,下面有另外的规则定义。

第七章

自动布局布线

7.1

后端(backend)概述

在前面的章节中,讲到了一个 design 从 RTL 级到 netlist 的流程,当一个 design 完成 了 synthesis,生成 netlist 后, 接下来的任务就是 netlist 的物理实现,即把 netlist 转成 layout。这个过程通常称为后端(backend)。

VERSION 5.1 ; NAMESCASESENSITIVE ON ; BUSBITCHARS "<>" ;

# version, # 区分大小写 #bus 标志符 a<1> , a<2> ,... a<n> 将看作 bus

UNITS DATABASE MICRONS 100 ;

END UNITS

下图(T7.2)是 APR 部分的 Timing-Driven design 的 design flow ,

step1

step2 step3 step4 step5 step6 step7 step8 step9 step10 step11

T7.2 Timing-Driven design flow

END metal2

LAYER via2 TYPE CUT ;

AltiumDesigner自动布线规则

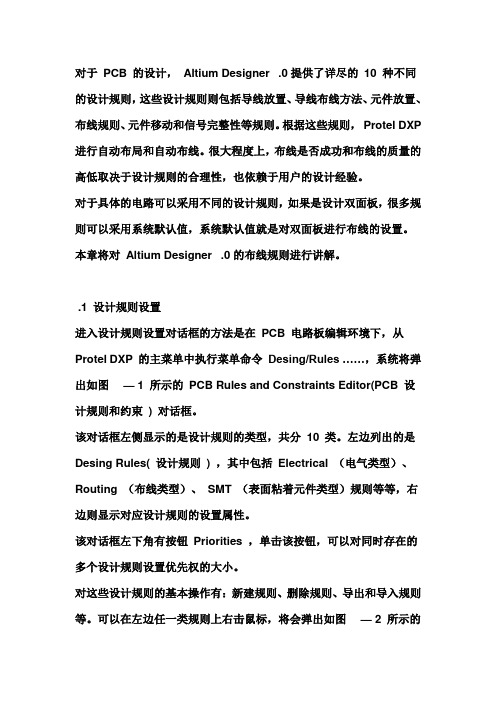

对于PCB 的设计,Altium Designer .0提供了详尽的10 种不同的设计规则,这些设计规则则包括导线放置、导线布线方法、元件放置、布线规则、元件移动和信号完整性等规则。

根据这些规则,Protel DXP 进行自动布局和自动布线。

很大程度上,布线是否成功和布线的质量的高低取决于设计规则的合理性,也依赖于用户的设计经验。

对于具体的电路可以采用不同的设计规则,如果是设计双面板,很多规则可以采用系统默认值,系统默认值就是对双面板进行布线的设置。

本章将对Altium Designer .0的布线规则进行讲解。

.1 设计规则设置进入设计规则设置对话框的方法是在PCB 电路板编辑环境下,从Protel DXP 的主菜单中执行菜单命令Desing/Rules ……,系统将弹出如图— 1 所示的PCB Rules and Constraints Editor(PCB 设计规则和约束) 对话框。

该对话框左侧显示的是设计规则的类型,共分10 类。

左边列出的是Desing Rules( 设计规则) ,其中包括Electrical (电气类型)、Routing (布线类型)、SMT (表面粘着元件类型)规则等等,右边则显示对应设计规则的设置属性。

该对话框左下角有按钮Priorities ,单击该按钮,可以对同时存在的多个设计规则设置优先权的大小。

对这些设计规则的基本操作有:新建规则、删除规则、导出和导入规则等。

可以在左边任一类规则上右击鼠标,将会弹出如图— 2 所示的菜单。

在该设计规则菜单中,New Rule 是新建规则;Delete Rule 是删除规则;Export Rules 是将规则导出,将以 .rul 为后缀名导出到文件中;Import Rules 是从文件中导入规则;Report ……选项,将当前规则以报告文件的方式给出。

图— 2 设计规则菜单下面,将分别介绍各类设计规则的设置和使用方法。

.2 电气设计规则Electrical (电气设计)规则是设置电路板在布线时必须遵守,包括安全距离、短路允许等4 个小方面设置。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

//插入Corner

dbCreateCellInst (geGetEditCell) "" "PCORNERW" "CORNER1" "0" "No" '(0 0) "design_in"

AND2HDLX U1 ( .A(A[0]), .B(B[0]), .Z(carry_1_) ); XOR2HDLX U2 ( .A(B[0]), .B(A[0]), .Z(SUM[0]) );

2020/5/22

共83页

7

2020/5/22

共83页

8

自动布局布线工具—Astro介绍

Astro是Synopsys公司开发的一种基于标准单 元的版图自动生成工具,通过调用标准单元库中 的门单元进行自动布局布线完成版图设计,其前 身是Avanti公司(2002年被Synopsys公司收购) 的Apollo。 2007年以后软件叫ICC 。

翻译

映射

2020/5/22

共83页

4

setup/hold

建立(setup)时间是指触发器的时钟信号上 升沿到来以前,数据稳定不变的时间。

保持(hold)时间是指触发器的时钟信号上升 沿到来以后,数据稳定不变的时间。

裕度(slack):是时序要求与实际时序之间 的差值,反映了时序是否满足要求。裕度为正, 满足要求dat;a 反之不满足。 裕度=clk要求的时间-实际的时间

典型流程

系统功能 不满足

动态仿真正确

时序 不满足

系统结构 不合理

功能 不正确

功能正确

系统规划满足

2020/5/22

共83页

1

典型流程

数字VLSI 流程

模拟IC 流程

功能要求

功能要求

Matlab

系统建模

Modelsim, Questasim, Muxplus II

Design Compiler Astro, Encounter

计的可靠性。能自动处理天线效应修复、孔优化、金 属填充物添加、宽铝开槽等。 高性能的算法及分布式的布线能力大大缩短了设计周 期。

2020/5/22

共83页

10

自动布局布线流程

参考库

时序约束文件

门级网表

数据输入

布局规划

IO管脚排列文件

工艺文件

布线

布局

静态时序分析,后仿真

时钟综合

DRC、LVS

流片

2020/5/22

FAHDLX U1_4 ( .A(A[4]), .B(B[4]), .CI(carry_4_), .CO(carry_5 _), .S(SUM[4]) );

FAHDLX U1_3 ( .A(A[3]), .B(B[3]), .CI(carry_3_), .CO(carry_4 _), .S(SUM[3]) );

//卸载原来的IO顺序定义

tdfPurgePadConstr //定义四个Corner IO的位置

pad "CORNER1" "Bottom" //定义芯片下面一排IO管脚位置顺序,从左到右依次定义

pad "PLBI18N_HostAddr7" "bottom" 1

......... //定义芯片右面一排IO管脚顺序,从下到上依次定义

共83页

11

数据输入

工艺库文件--是Foundry或IP提供商提供的各 种库(标准单元库、IO库、SRAM库和IP库) 和工艺文件 。网站下载

设计文件—网表文件(DC综合得到)和时序 约束文件(SDC格式,DC综合得到)。

管脚排列文件(TDF格式)--手动编写。

2020/5/22

共83页

12

行为设计 (Verilog /VHDL)

不满足 行为仿真

满足 综合、优化

网表 不满足

时序仿真 满足

版图自动 布局、布线

不满足 后仿真

满足

流片、封装、测试

Calibre

系统建模 (Matlab等)

不满足

电路仿真

满足 手工设计

版图 不满足

后仿真

满足

流片、封装、测试

2020/5/22

共83页

Matlab Spectre Virtuoso, laker

2

主要内容

自动布局布线基本概念 自动布局布线工具介绍 Astro布局布线流程

2020/5/22

共83页

3

assign mux_out=!mux_control&mux_in1 |mux_control&mux_in2|mux_in1&mux_in2; //assign mux_out=mux_control ?mux_in1:mux_in2;

2020/5/22

共83页

Байду номын сангаас

9

Astro特点

Astro能够使设计得到更快收敛。 Astro强调设计过程中的超深亚微米效应,在整个设

计过程中考虑了所有的物理效应。 具有很好的时钟树综合机制,能够提高时钟频率,完

成高性能电路的设计。 通过布局控制和早期对时序和拥塞的预估,可以提高

产品率。 能够通过遵循最新、最先进的制造工艺规则来提高设

pad "PLBI16N_TestMode0" "right" 1

……..

2020/5/22

共83页

5

自动布局布线基本概念

版图,GDS,GDS II (Graphic Data System),用来控制集成电路光掩膜绘制 。

自动布局+自动布线=画完版图

2020/5/22

共83页

6

网表文件

FAHDLX U1_5 ( .A(A[5]), .B(B[5]), .CI(carry_5_), .CO(carry_6 _), .S(SUM[5]) );

IO管脚排列文件

定义芯片的IO管脚顺序之外,还要插入一些特 殊的IO单元,如各种类型的电源IO、地IO和 Corner IO。

2020/5/22

共83页

13

//插入给Core供电的电源IO(PVDD1W)和地IO(PVSS1W)

insertPad "VDD" "PVDD1W" "VDD" "VDD"

insertPad "VSS" "PVSS1W" "VSS" "VSS" //插入给IO供电的电源IO(PVDD2W)和地IO(PVSS2W)

dbCreateCellInst (geGetEditCell) "" "PVDD2W" "VDD33" "0" "No" '(0 0) "design_in"