ASIC设计cadence自动布局布线工具_图文(精)

《自动布局布线》课件

探索自动布局布线的奇妙世界,帮助你提高电路板或芯片的性能,节省时间, 减少错误。

什么是自动布局布线?

自动布局布线是一种方法,用于自动为电路板或芯片设计最佳电线布局。

为什么需要自动布局布线?

手动布线耗时且容易出错,而自动布局布线可以节省时间、减少错误,并提 高电路板或芯片的性能。

2 准确性

避免人为错误,提高电路板或芯片的性能。

4 高效

节省时间,快速完成布线任务。

自动布局布线的挑战

算法复杂度高

处理大规模网络布线的算法复杂度较高。

异常情况处理

对输入异常情况的处理较困难,需要更精细的算法设计。

CPU处理限制

处理大规模网络布线时,仅依靠CPU很难满足要求。

结论

自动布局布线能够帮助我们节省时间、减少错误,并提高电路板或芯片的性 能。

自动布局布线的流程,为后续布线准备。

2

网络构建

将电路元件在网格中建立连接,形成网络。

3

优化网络

对网络进行优化,使其满足性能要求。

4

生成布线

根据优化后的网络,生成最佳的电线布局。

自动布局布线的优势

1 自动化

提高效率,减少人工工作量。

3 可重复性

保持一致的布线质量。

尽管自动布局布线还面临一些挑战,但随着技术发展,我们可以期待它在未 来发挥更大的作用。

自动布局布线软件

浙大微电子

11/74

工具界面

命令输入 例如:help “insertPad” 查看insertPad 命令使用方法

浙大微电子

6/74

Astro自动布局布线流程

参考库 门级网表

时序约束文件 数据输入

IO管脚排列文件

工艺文件

布局规划

布线

布局

静态时序分析,后仿真

时钟综合

DRC、LVS

流片

浙大微电子

7/74

数据输入

工艺库文件--是Foundry或IP提供商提供的各 种库(标准单元库、IO库、SRAM库和IP库) 和工艺文件 --网站下载

dbCreateCellInst (geGetEditCell) "" "PCORNERRN" "CORNER3" "0" "No" '(0 0) "fsk0323"

dbCreateCellInst (geGetEditCell) "" "PCORNERRN4;0" "No" '(0 0) "fsk0323"

设计文件—网表文件(.sv文件)和时序约束 文件(.sdc文件)--都是DC综合得到

管脚排列文件(.tdf文件)--手动编写,保存成 XXX.tdf到任意你能找到目录里。

课件中是在软件启动目录下创建了一个data目录来 保存tdf文件

浙大微电子

8/74

IO管脚排列文件

IO顺序 插入一些特殊的IO单元:

pad "en_block" "bottom" 1

第8章ASIC布局布线

布图规划的任务是: • 决定输入输出PAD的位置; • 决定电源PAD的数量和位置; • 决定电源配线的类型; • 决定时钟配线的类型和位置; • 安排芯片上固定功能块、可变功能块的位置; • 规划功能块之间的互连空间; • 减小功能块之间的互连线长度和信号延迟。 布图规划设计的目标是减少芯片面积和减少延迟时间

在结束了布图规划和布局后,我们可以预测模块 间和模块内的电容。这使我们可以为逻辑综合提供更 加准确地估计每个逻辑单元所需驱动的负载电容参数

布局的目标和任务 布局工具的任务就是在芯片的可变模块中安徘所有的逻辑

单元。理想情况下布局阶段的目标是: • 确保布线器能够完成布线。 • 最小化关键网络的延迟。 • 使芯片尽量密集。

第8章ASIC布局布线

2020年4月22日星期三

实际中ASIC的布局和布线过程,可分为布图阶段 、布局阶段、布线阶段。布图规划阶段的输入来自系统 划分和设计输入的输出——网表。布图规划是在布局之 前,但我们将它们放在一起讨论。布局阶段的Байду номын сангаас出将给 布线工具提供指导。

在布图规划开始时我们有一个网表,它描述了电路 模块,模块内的逻辑单元及其它们的连接。举例来说, 下图1显示了一个Viterbi译码器,它由一组标准单元构 成,单元旁边尚没有布线空间。我们可以把标准单元想 象成为墙上的砖块,需要做的就是留下互连,即石灰浆 空间(我们称这些空间为通道),并安排各个单元。下 图2显示了这样一个已完成的墙面——在布图规划和布 局阶段都结束后。到现在我们还没有做任何布线——它 将留到以后进行——我们所完成的是对逻辑单元的布局 ,希望能够使总互连长度达到最小。

下图所示,显示了互连延迟和门延迟随特征尺寸减 少而变化的曲线,但却以不同的比率显示。这是因为最 小宽度的互连电容将趋向于极限2pFcm-1而门延迟却继 续下降。布图规则使我们能够通过估计互连的长度来预 测其延迟。

cadence工具介绍

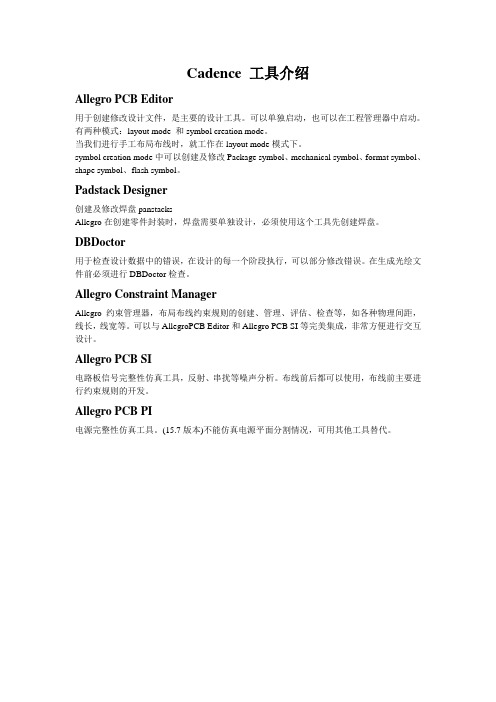

Cadence 工具介绍

Allegro PCB Editor

用于创建修改设计文件,是主要的设计工具。

可以单独启动,也可以在工程管理器中启动。

有两种模式:layout mode 和symbol creation mode。

当我们进行手工布局布线时,就工作在layout mode模式下。

symbol creation mode中可以创建及修改Package symbol、mechanical symbol、format symbol、shape symbol、flash symbol。

Padstack Designer

创建及修改焊盘panstacks

Allegro在创建零件封装时,焊盘需要单独设计,必须使用这个工具先创建焊盘。

DBDoctor

用于检查设计数据中的错误,在设计的每一个阶段执行,可以部分修改错误。

在生成光绘文件前必须进行DBDoctor检查。

Allegro Constraint Manager

Allegro约束管理器,布局布线约束规则的创建、管理、评估、检查等,如各种物理间距,线长,线宽等。

可以与AllegroPCB Editor和Allegro PCB SI等完美集成,非常方便进行交互设计。

Allegro PCB SI

电路板信号完整性仿真工具,反射、串扰等噪声分析。

布线前后都可以使用,布线前主要进行约束规则的开发。

Allegro PCB PI

电源完整性仿真工具。

(15.7版本)不能仿真电源平面分割情况,可用其他工具替代。

工具之间的关系。

Cadence后端实验系列15-布局布线-SoCEncouter

SOC Encounter 布局/布线 流程

IO,电源和地的布置

指定平面布置图 平面布置图

电源的规划

电源布线

布线

输入文件

• 逻辑和时序库:TLF或.lib • 物理库:库交换格式(.LEF) • 门级网表:*.v • 时序约束:*.sdc • IO assignment file:*.io

SOC Encounter采用层次化设计功能将芯片分割成

多个小块,以便单独进行设计,再重新进行组装。SOC Encounter首先读入RTL或门级网表,并快速构建可准确代 表最终芯片(包括时序、布线、芯片大小,功耗和信号完整 性)的芯片“虚拟原型”。通过使用物理虚拟原型功能,设 计师可以快速验证物理可行性并在逻辑上进行必要更改。

布局布线设计流程

1、登录服务器,进入终端,输入:encounter ,进入soc encounter

这里输入命令: encounter,就可以启 用soc encounter软件

用户界面

2、调入门级网表和库

网表文件:bin/accu_synth.v

约束文件:bin/accu.sdc

时序库: hjtc18_ff.lib hjtc18_ss.lib hjtc18_tt.lib

——Cell-Based IC Physical Design and Verification-SOC Encounter

Thank you!

cadence15encouter20110110outlinesocencounter简介socencounter布局布线流程演示socencountersocencounter是cadence数字集成电路设计平台的一个集成的后端工具功能相当强大可以从综合一直做到生成gdsii文件

Cadence软件包含工具及功能介绍

Cadence软件介绍Cadence 是一个大型的EDA 软件,它几乎可以完成电子设计的方方面面,包括ASIC 设计、FPGA 设计和PCB 板设计。

Cadence 在仿真、电路图设计、自动布局布线、版图设计及验证等方面有着绝对的优势。

Cadence 包含的工具较多几乎包括了EDA 设计的方方面面。

Cadence 是一个大型的EDA 软件,它几乎可以完成电子设计的方方面面,包括ASIC 设计、FPGA 设计和PCB 板设计。

Cadence 在仿真、电路图设计、自动布局布线、版图设计及验证等方面有着绝对的优势。

Cadence 包含的工具较多几乎包括了EDA 设计的方方面面。

下面主要介绍其产品线的范围。

1、板级电路设计系统。

包括原理图输入、生成、模拟数字/混合电路仿真,fpga设计,pcb编辑和自动布局布线mcm电路设计、高速pcb版图的设计仿真等等。

包括:A、Concept HDL原理图设计输入工具, 有for NT和for Unix的产品。

B、Check Plus HDL原理图设计规则检查工具。

(NT & Unix)D、Allegro Expert专家级PCB版图编辑工具(NT & Unix)E、SPECTRA Expert AutoRouter 专家级pcb自动布线工具F、SigNoise信噪分析工具G、EMControl 电磁兼容性检查工具H、Synplify FPGA / CPLD综合工具I、HDL Analyst HDL分析器J、Advanced Package Designer先进的MCM封装设计工具2、Alta系统级无线设计这部分包括:A、SPW (Cierto Signal Processing Work System)信号处理系统。

可以说,spw包括了matlab的很多功能,连demo都有点象。

它是面向电子系统的模块化设计、仿真和实现的环境。

它的通常的应用领域包括无线和有线载波通信、多媒体和网络设备。

CADENCEPCB设计布局与布线

CADENCEPCB设计布局与布线CADENCEPCB设计工具是电子工程师在进行PCB电路板设计时经常使用的软件。

其强大的功能使得设计师可以进行布局和布线,确保电路板的性能和可靠性。

下面将详细介绍CADENCEPCB设计的布局和布线过程。

首先是布局过程。

布局是指在PCB上放置电子元器件和确定它们之间的物理布置。

布局的目标是优化电路板的性能、减小电磁干扰并提供良好的散热。

以下是CADENCEPCB设计中的布局步骤:1.确定布局约束:首先,设计师需要根据电路的要求和特定的应用环境,确定布局的约束条件,如电源分配、信号完整性、热管理等。

这些约束条件将指导接下来的布局和布线过程。

2.放置电子元器件:根据电路图和设计要求,将电子元器件在PCB上进行合理的放置。

重要的因素包括元器件之间的物理距离,信号和电源线的长度和走向,以及避免冲突和干扰的布局。

3.优化布局:在放置元器件之后,设计师需要优化布局,以确保信号完整性。

这包括优化电源和地平面的布置,减小信号线的长度和交叉,并提供良好的散热条件等。

4.电源和地平面设计:在布局过程中,需要合理设计电源和地平面,以提供足够的电源稳定性和地电流供应。

这需要将电源和地线走线得当,并采用合适的电容和电感等元件进行滤波和终端处理。

接下来是布线过程。

布线是指设计师将电子元器件之间的连线进行优化和优化,以确保信号的完整性、最小化电磁干扰并满足设计约束条件。

以下是CADENCEPCB设计中的布线步骤:1.设计路由规则:在进行布线之前,设计师需要制定一个路由规则,包括最小线宽和线间距、阻抗控制、信号类型和电源线与地线的关系等。

这些规则将指导后续的布线过程。

2.自动布线:CADENCEPCB设计工具提供了自动布线工具,可以根据预先设定的规则和优化目标,自动生成布线方案。

设计师可以根据需要进行调整和优化。

3.手动布线:对于一些复杂的板线、高速信号或特殊需求,手动布线是必要的。

对于这些情况,设计师需要手动布线,根据设计约束和优化目标,确定线路的走向和走线方式,并避免冲突和干扰。

Cadence软件介绍

Cadence软件介绍Cadence 就是一个大型的EDA 软件,它几乎可以完成电子设计的方方面面,包括ASIC 设计、FPGA 设计与PCB 板设计。

Cadence 在仿真、电路图设计、自动布局布线、版图设计及验证等方面有着绝对的优势。

Cadence 包含的工具较多几乎包括了EDA 设计的方方面面。

下面主要介绍其产品线的范围。

1、板级电路设计系统包括原理图输入、生成、模拟数字/混合电路仿真,fpga设计,pcb编辑与自动布局布线mcm电路设计、高速pcb版图的设计仿真等等。

包括:A、Concept HDL原理图设计输入工具, 有for NT与for Unix的产品。

B、Check Plus HDL原理图设计规则检查工具。

(NT & Unix)D、Allegro Expert专家级PCB版图编辑工具(NT & Unix)E、SPECTRA Expert AutoRouter 专家级pcb自动布线工具F、SigNoise信噪分析工具G、EMControl 电磁兼容性检查工具H、Synplify FPGA / CPLD综合工具I、HDL Analyst HDL分析器J、Advanced Package Designer先进的MCM封装设计工具2、Alta系统级无线设计这部分包括:A、SPW (Cierto Signal Processing Work System)信号处理系统。

可以说,spw包括了matlab的很多功能,连demo都有点象。

它就是面向电子系统的模块化设计、仿真与实现的环境。

它的通常的应用领域包括无线与有线载波通信、多媒体与网络设备。

在进行算法设计、滤波器设计、c Code生成、软/硬件结构联合设计与硬件综合的理想环境。

它里面非常有意思的就就是信号计算器。

B、HDS (Hardware Design System)硬件系统设计系统它现在就是SPW的集成组件之一。

包括仿真、库与分析扩展部分。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

本节将使用综合工具(Design Compiler 对一个 8位全加器逻辑综合,并产生一个门级网表;利用该网表使用自动布局布线工具(Silicon Ensemble 生成一个全加器的版图。

首先输入 8位全加器 verilog 代码:

module adder8(Cout,S,A,Cin;

output Cout;

output [7:0]S;

input [7:0]A;

input [7:0]B;

input Cin;

reg [8:0]SUM;

reg [7:0]S;

reg Cout;

wire [7:0]A,B;

always @(Aor B or Cin

begin

SUM [8:0]=A+B+Cin;

S =SUM [7:0];

Cout =SUM [8];

end

endmodule

打开综合工具 DC (psyn_gui&

File->Read..

读入代码

File->Setup..设置 3

个相关工艺库将带红色 *号的 3

个库设置如下图 Design->CompileDesign.. 编译

Schematic->NewDesign Schematic View..

可以看到综合后的顶层结构通过双击 C1模块还可以看到全加器的门级结构

为了后面自动布局布线的需要, 这里我们要将这个综合结果保存为 adder8_nl.v 门级网表。

在 psyn_gui-xg-t>

后输入如下命令

下面进行自动布局布线 (一下有路径出现的地方要特别注意打开 Silicon Ensemble (sedsm

&

File->Import->LEF… 导入库的转换格式

注意此文件的路径!

File->Import->Verilog… 导入工艺库(此库为 verilog 描述的标准单元,包含各种延时信息

这里去掉后面的!

继续 File->Import->Verilog… 导入网表 adder8_nl.v

(此处要先删掉第一个工艺库这里要加上顶层模块名 adder8

Floorplan->InitializeFloorplan…

准备工作完成开始布局布线

点击 Variables 将里面的 PLAN.LOWERLEFT.ORIGIN 由 FALSE 改为 TURE

Edit ->Add ->Row… Area 的区域可以直接点击 Area 并在图上拖拽,并使其大小与芯

片核一致

File->Saveas… 保存为 fplan

Route->PlanPower… 设置电源环在 Plan Power 窗口中点击 Add

Rings…

Place->Ios…

放置输入输出

Place->Cells…

放置单元

Place->FillerCells->AddCells…

Route->RoutePower->FollowPins… 添加管脚(金属线宽设为 1.8 Route->Wroute…

布线

View->DisplayOptions… 检查管脚名设置 Pin 为 ON

File->Export->DEF… 命名为

adder8_wrouted.def

打开 icfb &

再导入 DEF

文件之前要确保你有如下图中的一些库文件

File->Import->DEF…

Enter “ tutorial ” for Library Name, “ adder8” for Cell Name, and “ autoRouted ”

for View Name.

打开 View 中的

autoRouted

Design->Save..

Tool->Layout..将提取图转换为版图,这里需要改变几个参数 Edit->Search..点击Add Criteria

然后做如下图的几个改动

Apply Replace All

Design->Save

As..

现在就可以打开 layout 了

DRC… 熟悉吧! !。