CADENCE仿真步骤

cadenceic基础仿真经典实用

• 选择分析模式:

•cadence ic 基础仿真

• 电路中有两个电压源,一个用作VDD,另一个用作信号输入 Vin

V in

•cadence ic 基础仿真

• 输出的选择

•cadence ic 基础仿真

• 分析一阶共源放大器获得的波形图 • 波形图显示了当Vin 从0->2V 时输出的变化

•cadence ic 基础仿真

• 下图为以温度为变量进行直流分析时候的波形图

•cadence ic 基础仿真

带隙基准的温度参考

•cadence ic 基础仿真

•cadence ic 基础仿真

•cadence ic 基础仿真

•cadence ic 基础仿真

实例5 一阶放大器

共源的一阶放大器

• 下图显示了为仿真产生的输出日志文件 •

•cadence ic 基础仿真

• 产生的波形如下所示:

•cadence ic 基础仿真

• 可以通过设定坐标轴来获得电流—电压曲线 • 按以下方式进行: Axis-> X Axis

•cadence ic 基础仿真

• 按下图所示,将X轴设定为二极管上的电压 降

•cadence ic 基础仿真

• 在改变了X轴之后,波形应如下图所示:

•cadence ic 基础仿真

• 由于我们只对二极管的伏安特性曲线感兴趣,因此我们可以只选择流 经二极管的电流与其两端压降。新的曲线如下图所示:

•cadence ic 基础仿真

实例2 双极型晶体管的伏安特性曲线

• 首先为双极型晶体管电路新建一个cell view • 利用原理图编辑所需要的仿真电路

然后单击ESC。 • 可以得到如下图所示的一族伏安特性曲线

cadenceic教程schematic及其仿真

cadenceic教程schematic及其仿真第一章. Cadence cdsSPICE的使用说明Cadence cdsSPICE 也是众多使用SPICE内核的电路模拟软件之一。

因此他在使用上会有部分同我们平时所用到的PSPICE相同。

这里我将侧重讲一下它的一些特殊用法。

§ 1-1 进入Cadence软件包一.在工作站上使用在命令行中(提示符后,如:ZUEDA22>)键入以下命令icfb&↙(回车键),其中& 表示后台工作。

Icfb调出Cadence软件。

出现的主窗口如图1-1-1所示:图 1-1-1Candence主窗口二.在PC机上使用1)将PC机的颜色属性改为256色(这一步必须);2)打开Exceed软件,一般选用xstart软件,以下是使用步骤:start method选择REXEC(TCP-IP),Programm选择Xwindow。

Host选择10.13.71.32 或10.13.71.33。

host type选择sun。

并点击后面的按钮,在弹出菜单中选择command tool。

确认选择完毕后,点击run!3)在提示符ZDASIC22> 下键入:setenv DISPLAY 本机ip:0.0(回车)4)在命令行中(提示符后,如:ZUEDA22>)键入以下命令icfb&↙(回车键)即进入cadence中。

出现的主窗口如图1-1-1所示。

以上是使用xstart登陆cadance的方法。

在使用其他软件登陆cadance时,可能在登录前要修改文件.cshrc,方法如下:在提示符下输入如下命令:vi .cshrc↙ (进入全屏幕编辑程序vi)将光标移至setevn DISPLAY ZDASIC22:0.0 处,将“ZDASIC22”改为PC机的IP,其它不变(重新回到服务器上运行时,还需按原样改回)。

改完后存盘退出。

然后输入如下命令:source .cshrc↙ (重新载入该文件)以下介绍一下全屏幕编辑程序vi的一些使用方法:vi使用了两种状态,一是指令态(Command Mode),另一是插入态(Insert Mode)。

CAdence16.6PSpice1,使用自带例程进行第一个仿真

CAdence16.6PSpice1,使⽤⾃带例程进⾏第⼀个仿真1、建⽴原理图选择如下

2、新建⼀个⼯程,如下:

3、上图点击OK,进⼊界⾯,界⾯有下拉框,以放⼤器为例

4

5、发现⼯程⾥边⾃带如下:

6、点击1处,弹出2的参数会话框

7、点击第⼀张图,开始运⾏

8、弹出新的,运⾏结果如下:

在7界⾯更改了参数以后,只需要在8的界⾯点击运⾏就能看到新的波形了

9、可以在红圈位置直接删除不想看到的,点击选中,delete

10、点击1,在2位置添加想看到的曲线

例如看功率如下

11、如何看功率最⼤值,打击1,2处选择函数,3处选中要看的

得到结果如下

12、点击如下按钮,让此界⾯永远处于最上,之后让界⾯像第⼆张图这样

13、我们此时可以移动原理图的探针,我们会发现,波形跟着实时改变

14、⽣成报告。

window--copy to clipboard,之后在word⾥边可以直接粘贴。

15、通过点击如下按钮,能看到直流静态⼯作点、直流静态电流,功耗。

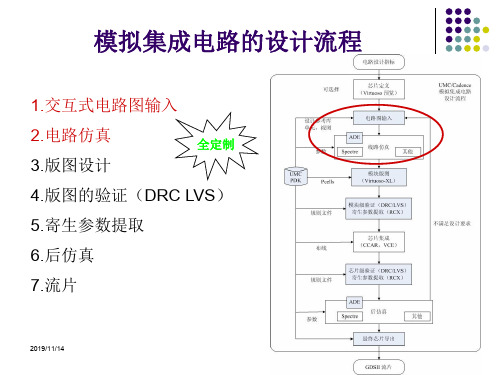

CADENCE仿真流程

CADENCE仿真流程1.设计准备在进行仿真之前,需要准备好设计的原理图和布局图。

原理图是电路的逻辑结构图,布局图是电路的物理结构图。

此外,还需要准备好电路的模型、方程和参数等。

2.确定仿真类型根据设计需求,确定仿真类型,包括DC仿真、AC仿真、时域仿真和优化仿真等。

DC仿真用于分析直流电路参数,AC仿真用于分析交流电路参数,而时域仿真则用于分析电路的时间响应。

3.设置仿真参数根据仿真类型,设置仿真参数。

例如,在DC仿真中,需要设置电压和电流源的数值;在AC仿真中,需要设置信号源的频率和幅度;在时域仿真中,需要设置仿真的时间步长和仿真时间等。

4.模型库选择根据设计需求,选择合适的元件模型进行仿真。

CADENCE提供了大量的元件模型,如晶体管、二极管、电感、电容等。

5.确定分析类型根据仿真目标,确定分析类型,例如传输功能分析、噪声分析、频率响应分析等。

6.仿真运行在仿真运行之前,需要对电路进行布局和连线。

使用CADENCE提供的工具对电路进行布局和连线,并生成物理设计。

7.仿真结果分析仿真运行后,CADENCE会生成仿真结果。

利用CADENCE提供的分析工具对仿真结果进行分析,观察电路的性能指标。

8.优化和修改根据仿真结果,对电路进行优化和修改。

根据需要,可以调整电路的拓扑结构、参数和模型等,以改进电路的性能。

9.再次仿真和验证根据修改后的电路,再次进行仿真和验证,以确认电路的性能指标是否得到改善。

最后需要注意的是,CADENCE仿真流程并不是一成不变的,根据具体的设计需求和仿真目标,流程可能会有所调整和修改。

此外,CADENCE还提供了许多其他的工具和功能,如电路板设计、封装设计、时序分析等,可以根据需要进行使用。

CADENCE仿真步骤

CADENCE仿真步骤

Cadence是一款电路仿真软件,它可以帮助设计师创建、分析和仿真

电子电路。

本文将介绍Cadence仿真的步骤。

1.准备仿真结构:第一步是准备仿真结构。

我们需要编写表示电路的Verilog或VHDL代码,然后将它们编译到Cadence Integrated Circuit (IC) Design软件中。

这会生成许多文件,包括netlist和verilog等文件,这些文件将用于仿真。

2.定义仿真输入输出信号:接下来,我们需要定义仿真的输入信号和

输出信号。

输入信号可以是电压、电流、时间和其他可测量的变量。

我们

需要定义输入信号的模拟和数字值,以及输出信号的模拟和数字值。

3.定义参数:参数是仿真中用于定义仿真设计的变量,这些变量可以

是仿真中电路的物理参数,如电阻、电容、时延、输入电压等,也可以是

算法参数,如积分步长等。

4.运行仿真:在所有参数和信号都设置完成后,我们可以运行仿真。

在运行仿真之前,可以使用自动参数检查来检查参数是否正确。

然后,使

用“开始仿真”命令即可启动仿真进程。

5.结果分析:在仿真结束后,我们可以使用结果分析器来查看输出信

号的模拟和数字值,以及仿真中电路的其他特性,如暂态分析、稳态分析、功率分析等。

以上就是Cadence仿真步骤。

CadenceallegroPI仿真

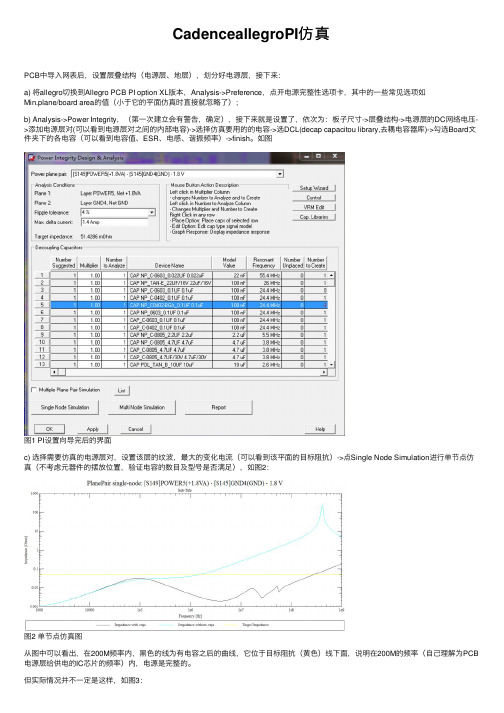

CadenceallegroPI仿真PCB中导⼊⽹表后,设置层叠结构(电源层、地层),划分好电源层,接下来:a) 将allegro切换到Allegro PCB PI option XL版本,Analysis->Preference,点开电源完整性选项卡,其中的⼀些常见选项如Min.plane/board area的值(⼩于它的平⾯仿真时直接就忽略了);b) Analysis->Power Integrity,(第⼀次建⽴会有警告,确定),接下来就是设置了,依次为:板⼦尺⼨->层叠结构->电源层的DC⽹络电压->添加电源层对(可以看到电源层对之间的内部电容)->选择仿真要⽤的的电容->选DCL(decap capacitou library,去耦电容器库)->勾选Board⽂件夹下的各电容(可以看到电容值、ESR、电感、谐振频率)->finish。

如图图1 PI设置向导完后的界⾯c) 选择需要仿真的电源层对,设置该层的纹波,最⼤的变化电流(可以看到该平⾯的⽬标阻抗)->点Single Node Simulation进⾏单节点仿真(不考虑元器件的摆放位置,验证电容的数⽬及型号是否满⾜),如图2:图2 单节点仿真图从图中可以看出,在200M频率内,⿊⾊的线为有电容之后的曲线,它位于⽬标阻抗(黄⾊)线下⾯,说明在200M的频率(⾃⼰理解为PCB 电源层给供电的IC芯⽚的频率)内,电源是完整的。

但实际情况并不⼀定是这样,如图3:图3 在单节点仿真中加实际情况如红⾊的曲线,则应为电源平⾯选⼀个电容的谐振频率为fa的电容,再次仿真之后,会得到有两个峰值的曲线,再加谐振频率等于,峰值对应的横坐标(谐振频率)的电容值即可,依次这样进⾏,直到整条曲线在要求的频率范围之内,位于⽬标谐振频率曲线下⾯。

(在调的时候,不⼀定是⾮得改原理图中电容的⼤⼩,也可适当增加原理图中滤波电容的数量)如蓝⾊曲线,相对于红⾊曲线,其谐振频率不到1M,⽅法同上,不过选这样的电容,电容值都⽐较⼤,如100uF。

cadence运放仿真-35页PPT文档资料

其它有关的菜单项(1)

Tools/Parametric Analysis

它提供了一种很重要的分析方法——参量分析的方法, 也即参量扫描。可以对温度,用户自定义的变量variables 进行扫描,从而找出最合适的值。

2019/11/14

其它有关的菜单项(2)

Outputs/To be plotted/selected on schematic

2019/11/14

Calculator的使用

Calculator是 一个重要的数 据处理工具, 可以用来仿真 电源抑制比, 相位裕度,共

模抑制比

2019/11/14

其它有关的菜单项(3)

Results菜单

2019/11/14

模拟结果的显示以及处理

在模拟有了结果之后, 如果设定的output有 plot属性的话,系统 会自动调出waveform 窗口,并显示outputs 的波形,如左图

Sweep Variable: Frequency Sweep Range :1 Hz~100M Hz 仿真完成后,点击 Result -> Direct Plot -> AC Gain&Phase 查看运放的幅频特性和相频特性

2019/11/14

仿真结果

该运放直流增益为80.9dB,单位增益带宽为82M Hz, 相位裕度为67.32deg。

2019/11/14

Analog Design Simulation菜单介绍

Session菜单

Schematic Window Save State Load State Options Reset Quit

回到电路图

2019/11/14

Cadence仿真流程

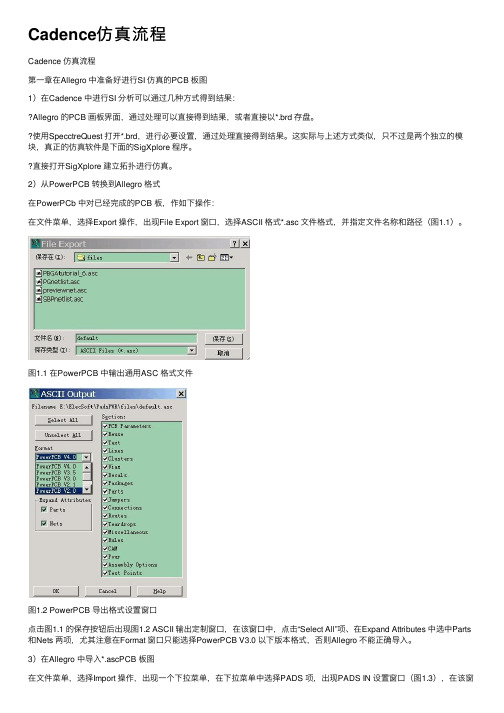

Cadence仿真流程Cadence 仿真流程第⼀章在Allegro 中准备好进⾏SI 仿真的PCB 板图1)在Cadence 中进⾏SI 分析可以通过⼏种⽅式得到结果:Allegro 的PCB 画板界⾯,通过处理可以直接得到结果,或者直接以*.brd 存盘。

使⽤SpecctreQuest 打开*.brd,进⾏必要设置,通过处理直接得到结果。

这实际与上述⽅式类似,只不过是两个独⽴的模块,真正的仿真软件是下⾯的SigXplore 程序。

直接打开SigXplore 建⽴拓扑进⾏仿真。

2)从PowerPCB 转换到Allegro 格式在PowerPCb 中对已经完成的PCB 板,作如下操作:在⽂件菜单,选择Export 操作,出现File Export 窗⼝,选择ASCII 格式*.asc ⽂件格式,并指定⽂件名称和路径(图1.1)。

图1.1 在PowerPCB 中输出通⽤ASC 格式⽂件图1.2 PowerPCB 导出格式设置窗⼝点击图1.1 的保存按钮后出现图1.2 ASCII 输出定制窗⼝,在该窗⼝中,点击“Select All”项、在Expand Attributes 中选中Parts 和Nets 两项,尤其注意在Format 窗⼝只能选择PowerPCB V3.0 以下版本格式,否则Allegro 不能正确导⼊。

3)在Allegro 中导⼊*.ascPCB 板图在⽂件菜单,选择Import 操作,出现⼀个下拉菜单,在下拉菜单中选择PADS 项,出现PADS IN 设置窗⼝(图1.3),在该窗⼝中需要设置3 个必要参数:图1.3 转换阿三次⽂件参数设置窗⼝i. 在的⼀栏那填⼊源asc ⽂件的⽬录ii. 在第⼆栏指定转换必须的pads_in.ini ⽂件所在⽬录(也可将此⽂件拷⼊⼯作⽬录中,此例)iii. 指定转换后的⽂件存放⽬录然后运⾏“Run”,将在指定的⽬录中⽣成转换成功的.brd ⽂件。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Cadence SPECCTRAQuest 仿真步骤[摘要]本文介绍了Cadence SPECCTRAQuest在高速数字电路的PCB设计中采用的基于信号完整性分析的设计方法的全过程。

从信号完整性仿真前的环境参数的设置,到对所有的高速数字信号赋予PCB板级的信号传输模型,再到通过对信号完整性的计算分析找到设计的解空间,这就是高速数字电路PCB板级设计的基础。

[关键词]板级电路仿真I/O Buffer Information Specification(IBIS)1 引言电路板级仿真对于今天大多数的PCB板级设计而言已不再是一种选择而是必然之路。

在相当长的一段时间,由于PCB仿真软件使用复杂、缺乏必需的仿真模型、PCB仿真软件成本偏高等原因导致仿真在电路板级设计中没有得到普及。

随着集成电路的工作速度不断提高,电路的复杂性不断增加之后,多层板和高密度电路板的出现等等都对PCB板级设计提出了更新更高的要求。

尤其是半导体技术的飞速发展,数字器件复杂度越来越高,门电路的规模达到成千上万甚至上百万,现在一个芯片可以完成过去整个电路板的功能,从而使相同的PCB上可以容纳更多的功能。

PCB已不仅仅是支撑电子元器件的平台,而变成了一个高性能的系统结构。

这样,信号完整性在PCB板级设计中成为了一个必须考虑的一个问题。

传统的PCB板的设计依次经过电路设计、版图设计、PCB制作等工序,而PCB的性能只有通过一系列仪器测试电路板原型来评定。

如果不能满足性能的要求,上述的过程就需要经过多次的重复,尤其是有些问题往往很难将其量化,反复多次就不可避免。

这些在当前激烈的市场竞争面前,无论是设计时间、设计的成本还是设计的复杂程度上都无法满足要求。

在现在的PCB板级设计中采用电路板级仿真已经成为必然。

基于信号完整性的PCB仿真设计就是根据完整的仿真模型通过对信号完整性的计算分析得出设计的解空间,然后在此基础上完成PCB设计,最后对设计进行验证是否满足预计的信号完整性要求。

如果不能满足要求就需要修改版图设计。

与传统的PCB板的设计比较既缩短了设计周期,又降低了设计成本。

同时,随着软件业的高速发展,涌现出了越来越多操作更简便、功能更多、成本更低的EDA软件。

越来越完备的仿真模型也得以提供。

所有这些都为PCB设计中广泛的采用电路设计板级仿真提供了充分条件。

下面就Cadence SPECCTRAQuest这一高速电路板级设计仿真工具采用IBIS模型详细介绍进行板级仿真设计的全过程。

2 仿真前环境设置使用Cadence SPECCTRAQuest进行高速电路设计的仿真,不同的设计者根据各自的需要可以灵活的利用这个EDA工具进行仿真设计。

当然,在进行一个完整的PCB板设计前仿真时,按照一定步骤规地完成仿真设计,将会为你的仿真工作带来极大的方便。

可以减少整个仿真工作的工作量、可以减少整个仿真工作中出现错误的可能性、可以留下一个完整的有价值的文档,同时也能养成良好的仿真工作习惯,为今后高效的完成高速电路的仿真设计打下基础。

首先,我们知道Cadence公司的EDA软件可以运行在WindowsNT环境下和UNIX环境下,除非特别说明,本文所述都是在WindowsNT环境下。

SPECCTRAQuest是Cadence EDA工具中有关高速电路设计的一个模块。

在进行网络拓扑结构提取和信号分析之前,一些前期的准备工作必须正确完成。

★PCB板外型边框(Outline)根据实际结构设置PCB板边框。

★PCB板叠层(Stackup)主要确定PCB板布线层数以及层叠(stack-up)方式,会直接影响到印制线的布线和阻抗。

根据芯片管脚数、芯片密度、网表密度等方面来考虑。

然后根据实际情况确定叠层参数,可以选用各个PCB制板公司推荐的叠层参数。

关键是要选取合适的布线阻抗。

在Cadence中打开Setup Advisor进入Edit Stack-up对话框,如图1,进行编辑。

★导入网表(Netlist)★器件预布局(Placement)将其中的关键器件进行合理的布局,主要涉及相对距离、抗干扰、散热、高频电路与低频电路、数字电路与模拟电路等方面。

★PCB板布线分区(Rooms)主要用来区分高频电路与低频电路、数字电路与模拟电路以及相对独立的电路。

元器件的布局以及电源和地线的处理将直接影响到电路性能和电磁兼容性能。

★PCB板禁止布线区划分(Keepouts)根据PCB制板工艺的要求确定禁止布线区。

图1 Stack-up编辑框在完成上述工作以后,还要对将要进行仿真设计的PCB板做如下设置:●设置PCB板直流电源网络对于含有多种电压值电源供电的PCB板,正确的设置尤显重要。

在Cadence中打开Setup Advisor进入Identify DC Nets对话框,如图2,进行编辑。

图2 设置直流电源网络●设置器件类型一般器件类型在原理图库中已经指定并带入PCB图中,但仍然需要对器件类型进行确认,以防不正确的设置。

电阻、电阻排、电容、电感、晶体管、保险丝、二极管等都要设置成DISCRETE。

●为所有IC和独立元器件附仿真模型所有在仿真设计中需要模型的器件的仿真模型在原理图库中都应该正确指定,对于电阻、电容这些独立元器件需要在原理图中正确指定VALUE属性,SPECCTRAQuest可以自动为它们分配ESpice模型。

首先,打开Signal Library Brower对话框,若已有规的完整DML模型库,我们可以直接将需要的模型库加入到工作库中。

若只有IBIS模型,则需要按Translate->后选择ibis2signoise将IBIS模型转换成DML模型。

如图3。

图3 仿真模型库设置框然后打开Signal Model Assignment对话框,Auto Setup将自动分配模型给每个已经指定模型的器件。

如图4。

也可以按Find Model为器件手工分配模型,或按Create Model 编辑生成一个模型,这需要有足够的建模经验。

模型分配好后运行Signal Audit会有一个详细的报告,需要仔细的检查。

图4 仿真模型分配窗设置正确的管脚类型和器件类型一样,所有器件管脚类型在原理图中已经指定,但仍需确认。

连接器、独立元器件的管脚类型应为UNSPEC。

在图4窗口中点击RefDesPins栏后可以检查每个器件的每个管脚类型。

3 仿真步骤1、拓扑的抽取在模型添加完成后,即可进入信号线的仿真阶段。

从Allegro或SPECCTRAQUEST中都可以进入Constraint Manager,Allegro的路径是Setup-》Electrical Constraint Spreadsheet,SPECCTRAQUEST中的进入路径是Constraints-》Electrical Constraint Spreadsheet。

Constrain Manager是Cadence的约束管理器,所有连线的拓扑抽取以及对网络赋拓扑都是在这儿进行的。

打开界面,如同图5所示:图5 Constraint Manager 界面从左边分类栏看,分成两类,Electrical Constraint Set类是中所有已经输入到该管理器的电气约束约定,Net类是电路中所有的网络。

第一次打开时,第一类是空的。

对Net类,打开下面的任何一分类,都可以抽取拓扑。

在Net栏点击Signal Integrity、Timing、Routing的任何一个,右边就会将本板的全部网络显示出来,如图6所示。

各个网络按字母排列,其中前面有“+”号的表示是总线或Xnet。

右击所选网络选择SigXplorer,就将拓扑抽取出来并进入SQ signal explorer expert 界面图7,所有网络的前仿真是在这个界面中进行的。

图6 抽取网络拓扑图7 Signal Explorer 界面2、参数设定因为对各个器件及阻容器件的模型已经在全部指定,所以抽取出来的拓扑上面的各IO 都有相应的IO模型,对那些没有指定的模型,Cadence会赋给它缺省的模型。

Cadence抽出的拓扑结构是根据各元器件的相对位置并考虑到布线方便抽取的,其中互连线的距离是它计算的曼哈顿距离(即Δx+Δy)。

仿真的主要目的就是根据仿真的结果优化网络的拓扑结构,用来约束PCB布线,使布线按照最优结果方向进行。

SQ Signal Explorer Expert界面除了菜单与工具栏以外分为两个部分,即上面的拓扑示意图与下面的参数、测量选择以及结果、控制的标签窗口。

在下面的Parameters标签窗口中的白色区域是可以编辑的,而灰色区域是无法编辑的,CIRCUIT是整个参数的总标题,下面的tlineDelayMode栏可以选择是用时间还是用长度表示传输线的延时(若用长度表示,则缺省的单位是mm,若用时间表示,则缺省的单位是ns,其中传输线的缺省传输速度是140mm每ns);userRevision表示目前的拓扑版本(第一次一般是1.0,以后修改拓扑时可以将此处的版本提高,这样以后在Constraint Manage里不用重新赋拓扑,只要升级拓扑即可)。

点击开单板名称后(本例中即ODTA),下面就列出本拓扑的各个元件(包括器件、阻容、电源、传输线),可以编辑各个元件的特性;对器件,可以选择对应管脚的IO BUFFER模型,但一般不推荐去更改它的模型,因为已经赋给器件整体模型了,相应的IO Buffer的模型也就确定了。

对阻容器件,可以更改它们的阻容值;对电源,可以更改电源值;对传输线,可以更改以下几项:impedance,即传输线的交流阻抗,可以根据叠层情况在适当围更改它;propDelay,即传输线的延时来表示的长度;traceGeometry,传输线的类型,即是微带线或带状线,由于在前仿真中传输线是用一个集中式的无损耗模型来表示的,所以这边选择微带线或带状线的关系并不大;velocity,传输线的信号传输速度,这边一般不去改变它,用它的缺省值,即5567.72mil/ns,约14cm/ns。

为了得到更大围的仿真结果,扩大参数的选择围,我们一般对阻容器件的阻值、传输线的阻抗、传输线的长度选择多个值进行扫描。

在各个元件的参数设定后,即可在拓扑上加激励进行仿真。

首先是加激励源,点击模型上面、位号下面的Tristate,出现如图8所示的窗口进行选择:图8 激励源设置框在Cadence中共有7种激励:Pulse:脉冲方波,就是时钟源性质的波形,如果选择Pulse,整个界面中的其他选项是灰的,不允许再选;Rise:表示一个上升沿;Fall:表示一个下降沿;Custom:表示一种可以自定义的波形激励,这是最常用的波形,在这种形式下,首先在Frequency中输入信号的频率,在Pattern中输入波形的形状。