cadence仿真工具介绍

cadenceic基础仿真经典实用

• 选择分析模式:

•cadence ic 基础仿真

• 电路中有两个电压源,一个用作VDD,另一个用作信号输入 Vin

V in

•cadence ic 基础仿真

• 输出的选择

•cadence ic 基础仿真

• 分析一阶共源放大器获得的波形图 • 波形图显示了当Vin 从0->2V 时输出的变化

•cadence ic 基础仿真

• 下图为以温度为变量进行直流分析时候的波形图

•cadence ic 基础仿真

带隙基准的温度参考

•cadence ic 基础仿真

•cadence ic 基础仿真

•cadence ic 基础仿真

•cadence ic 基础仿真

实例5 一阶放大器

共源的一阶放大器

• 下图显示了为仿真产生的输出日志文件 •

•cadence ic 基础仿真

• 产生的波形如下所示:

•cadence ic 基础仿真

• 可以通过设定坐标轴来获得电流—电压曲线 • 按以下方式进行: Axis-> X Axis

•cadence ic 基础仿真

• 按下图所示,将X轴设定为二极管上的电压 降

•cadence ic 基础仿真

• 在改变了X轴之后,波形应如下图所示:

•cadence ic 基础仿真

• 由于我们只对二极管的伏安特性曲线感兴趣,因此我们可以只选择流 经二极管的电流与其两端压降。新的曲线如下图所示:

•cadence ic 基础仿真

实例2 双极型晶体管的伏安特性曲线

• 首先为双极型晶体管电路新建一个cell view • 利用原理图编辑所需要的仿真电路

然后单击ESC。 • 可以得到如下图所示的一族伏安特性曲线

(完整word版)cadence软件介绍

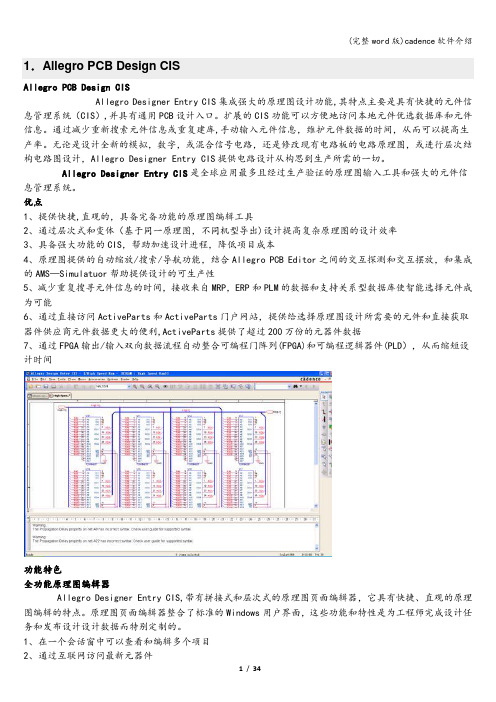

1.Allegro PCB Design CISAllegro PCB Design CISAllegro Designer Entry CIS集成强大的原理图设计功能,其特点主要是具有快捷的元件信息管理系统(CIS),并具有通用PCB设计入口。

扩展的CIS功能可以方便地访问本地元件优选数据库和元件信息。

通过减少重新搜索元件信息或重复建库,手动输入元件信息,维护元件数据的时间,从而可以提高生产率。

无论是设计全新的模拟,数字,或混合信号电路,还是修改现有电路板的电路原理图,或进行层次结构电路图设计,Allegro Designer Entry CIS提供电路设计从构思到生产所需的一切。

Allegro Designer Entry CIS是全球应用最多且经过生产验证的原理图输入工具和强大的元件信息管理系统。

优点1、提供快捷,直观的,具备完备功能的原理图编辑工具2、通过层次式和变体(基于同一原理图,不同机型导出)设计提高复杂原理图的设计效率3、具备强大功能的CIS,帮助加速设计进程,降低项目成本4、原理图提供的自动缩放/搜索/导航功能,结合Allegro PCB Editor之间的交互探测和交互摆放,和集成的AMS—Simulatuor帮助提供设计的可生产性5、减少重复搜寻元件信息的时间,接收来自MRP,ERP和PLM的数据和支持关系型数据库使智能选择元件成为可能6、通过直接访问ActiveParts和ActiveParts门户网站,提供给选择原理图设计所需要的元件和直接获取器件供应商元件数据更大的便利,ActiveParts提供了超过200万份的元器件数据7、通过FPGA输出/输入双向数据流程自动整合可编程门阵列(FPGA)和可编程逻辑器件(PLD),从而缩短设计时间功能特色全功能原理图编辑器Allegro Designer Entry CIS,带有拼接式和层次式的原理图页面编辑器,它具有快捷、直观的原理图编辑的特点。

cadence工具介绍

标签:cadence工具介绍cadence工具介绍主要是cadence的常用工具:(一)System & Logic Design & Verification 1、SPW:系统仿真工具,与matlab相似,但是比其专业,用于系统建模,常用于通信系统2、Incisive:就是大家最常用的nc_verilog, nc_sim, nc_lauch,以及ABV,TBV的集合,仿真和验证功能很强大(二)Synthesis & Place & Route 1、BuildGates:与DC同期推出的综合工具,但是在国内基本上没有什么市场,偶尔有几家公司用2、RTL Complil er:继BuildGates之后的一个综合工具,号称时序,面积和功耗都优于DC,但是仍然无法取代人们耳熟能详的DC 3、Silicon Ensemble & PKS: 硅谷早期做物理设计的工程师,几乎都用它。

是第一个布局布线工具4、First Encount er & SoC Encounter: 继SE以后的很好的P&R工具,但是盗版太少,所以也只有大公司能用且都用,但是目前astro在国内有赶超之意5、Cetlic :噪声分析工具,权威6、Fire&Ice: 分布参数提取工具,国内很多人用synopsys的StarRC 7、VoltageStrom:静态功耗和动态功耗分析的很不错的工具,与s 的Power Complier相同。

8、SingnalStrom:时序分析工具,唯一一个能建库的工具9、nanoroute : 很强大的布线器喔,但是不是一般人能用的到的。

我也是在cadence实习的时候爽过的,比astro快十倍不止。

(三)custom IC Design 1、Virtoso:版图编辑工具,没有人不知道吧,太常用了,现在还有一个公司的laker 2、diva, dracula, assura: 物理验证工具,用的比较普遍,但是calibre是标准,很多公司都是用其中的一个和calibre同时验证,我好可怜,现在只能用herculus (四)数模混合信号设计这部分太多了,但是一个ADE的环境基本上都能包括,不细说了,打字都打累了(五)PCB A llego最为典型了,很多大公司都用的。

cadence ac仿真原理

一、概述在电子设计领域中,cadence ac仿真是一个非常重要的工具,它能够帮助工程师们验证电路的性能,优化设计方案,提高产品的可靠性和稳定性。

本文将介绍cadence ac仿真的原理及其应用。

二、cadence ac仿真概述cadence ac仿真是一种基于交流电源(AC)信号的电路仿真技术。

它能够模拟电路在不同频率下的响应特性,包括电压、电流、相位等参数。

通过cadence ac仿真,工程师可以分析电路的稳定性、频率响应、相位裕度等重要指标,从而优化电路设计。

三、cadence ac仿真原理cadence ac仿真的原理主要基于两个方面:信号源和电路模型。

1. 信号源在cadence ac仿真中,信号源通常是一个交流电源,它能够产生不同频率和幅值的正弦波信号。

通过改变信号源的频率和幅值,工程师可以模拟不同工作条件下电路的响应特性。

2. 电路模型电路模型是cadence ac仿真的核心部分,它对电路中的元件进行建模,包括电阻、电容、电感等。

在仿真过程中,cadence会根据电路模型和信号源的输入,计算出电路在不同频率下的响应,包括电压、电流、相位等参数。

四、cadence ac仿真应用1. 频率响应分析通过cadence ac仿真,工程师可以分析电路在不同频率下的响应特性,包括增益、相位、带宽等参数。

这些参数对于电路的稳定性和性能至关重要,通过仿真分析,工程师可以优化电路设计,提高产品的性能。

2. 稳定性分析cadence ac仿真还可以帮助工程师分析电路的稳定性。

在回路不稳定的情况下,电路可能会产生不稳定的波形和振荡,严重影响产品的可靠性和稳定性。

通过仿真分析,工程师可以及早发现并解决稳定性问题,保证产品的可靠性。

3. 相位裕度分析相位裕度是评价电路稳定性的重要指标,它描述了电路在闭环条件下的相位裕度和裕度裕度。

通过cadence ac仿真,工程师可以分析电路的相位裕度,及时发现并解决相位裕度不足的问题,确保电路的稳定性和可靠性。

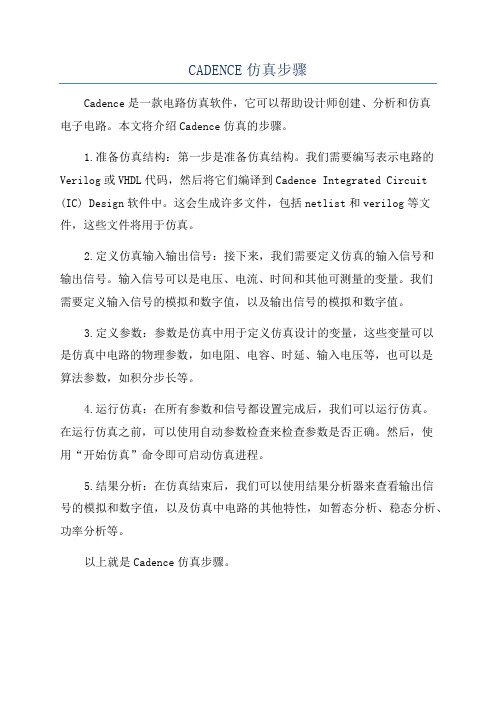

CADENCE仿真步骤

CADENCE仿真步骤

Cadence是一款电路仿真软件,它可以帮助设计师创建、分析和仿真

电子电路。

本文将介绍Cadence仿真的步骤。

1.准备仿真结构:第一步是准备仿真结构。

我们需要编写表示电路的Verilog或VHDL代码,然后将它们编译到Cadence Integrated Circuit (IC) Design软件中。

这会生成许多文件,包括netlist和verilog等文件,这些文件将用于仿真。

2.定义仿真输入输出信号:接下来,我们需要定义仿真的输入信号和

输出信号。

输入信号可以是电压、电流、时间和其他可测量的变量。

我们

需要定义输入信号的模拟和数字值,以及输出信号的模拟和数字值。

3.定义参数:参数是仿真中用于定义仿真设计的变量,这些变量可以

是仿真中电路的物理参数,如电阻、电容、时延、输入电压等,也可以是

算法参数,如积分步长等。

4.运行仿真:在所有参数和信号都设置完成后,我们可以运行仿真。

在运行仿真之前,可以使用自动参数检查来检查参数是否正确。

然后,使

用“开始仿真”命令即可启动仿真进程。

5.结果分析:在仿真结束后,我们可以使用结果分析器来查看输出信

号的模拟和数字值,以及仿真中电路的其他特性,如暂态分析、稳态分析、功率分析等。

以上就是Cadence仿真步骤。

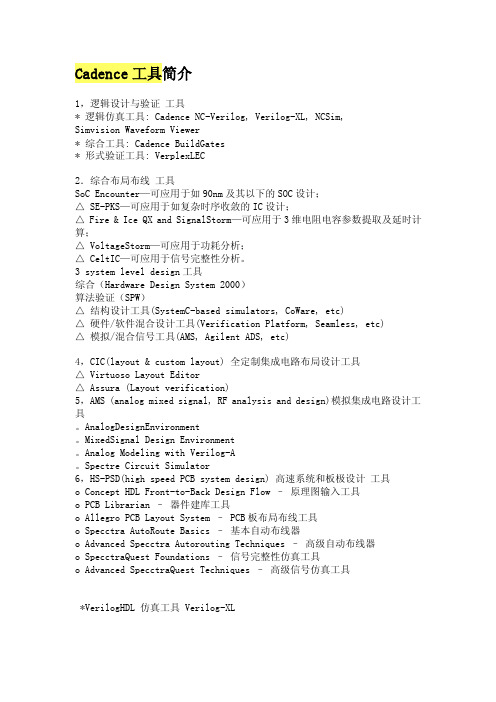

Cadence工具简介

Cadence工具简介1,逻辑设计与验证工具* 逻辑仿真工具: Cadence NC-Verilog, Verilog-XL, NCSim,Simvision Waveform Viewer* 综合工具: Cadence BuildGates* 形式验证工具: VerplexLEC2.综合布局布线工具SoC Encounter—可应用于如90nm及其以下的SOC设计;△ SE-PKS—可应用于如复杂时序收敛的IC设计;△ Fire & Ice QX and SignalStorm—可应用于3维电阻电容参数提取及延时计算;△ VoltageStorm—可应用于功耗分析;△ CeltIC—可应用于信号完整性分析。

3 system level design工具综合(Hardware Design System 2000)算法验证(SPW)△ 结构设计工具(SystemC-based simulators, CoWare, etc)△ 硬件/软件混合设计工具(Verification Platform, Seamless, etc)△ 模拟/混合信号工具(AMS, Agilent ADS, etc)4,CIC(layout & custom layout) 全定制集成电路布局设计工具△ Virtuoso Layout Editor△ Assura (Layout verification)5,AMS (analog mixed signal, RF analysis and design)模拟集成电路设计工具。

AnalogDesignEnvironment。

MixedSignal Design Environment。

Analog Modeling with Verilog-A。

Spectre Circuit Simulator6,HS-PSD(high speed PCB system design) 高速系统和板极设计工具o Concept HDL Front-to-Back Design Flow –原理图输入工具o PCB Librarian –器件建库工具o Allegro PCB Layout System – PCB板布局布线工具o Specctra AutoRoute Basics –基本自动布线器o Advanced Specctra Autorouting Techniques –高级自动布线器o SpecctraQuest Foundations –信号完整性仿真工具o Advanced SpecctraQuest Techniques –高级信号仿真工具*VerilogHDL 仿真工具 Verilog-XL*电路设计工具 Composer电路模拟工具 Analog Artist*版图设计工具 Virtuoso Layout Editor版图验证工具 Dracula 和 Diva*自动布局布线工具 Preview 和 Silicon Ensembleform:Mr Bond coms-chip expert设计任务 EDA工具功能仿真和测试 a. Cadence, NC_simb. Mentor ModelSim (调试性能比较突出)c. Synopsys VCS/VSSd. Novas Debussy (仅用于调试)逻辑综合 a. Synopsys, DCb. Cadence, BuildGatesc. Mentor, LeonardoDFT a. Mentor, DFTAdvisorb. Mentor, Fastscanc. Mentor, TestKompressd. Mentor, DFTInsighte. Mentor, MBISTArchitectf. Mentor, LBISTArchitectg. Mentor, BSDArchitecth. Mentor, Flextesti. Synopsys, DFT Complierj. Synopsys, Tetra MAXk. Synopsys, BSD Complier布局,时钟树综合和自动布线a. Cadence, Design Plannerb. Cadence, CT-Genc. Cadence, PKSd. Cadence, Silicon Ensemblee. Synopsys, Chip Architectf. Synopsys, Floorplan Managerg. Synopsys, Physical Complier & Apolloh. Synopsys, FlexRoute网表提取及RC参数提取物理验证a. Mentor, xCalibreb. Cadence, Assure RCXc. Synopsys, Star-RCXTd. Mentor, Calibree. Synopsys, Herculef. Cadence, Assure延时计算与静态时序分析a. Synopsys, Prime Timeb. Cadence, Pearlc. Mentor, SST Velocity形式验证 a. Mentor, FormalProb. Synopsys, Formalityc. Cadence, FormalCheck功能优化与分析 a. Synopsys, Power Compilerb. Synopsys, PowerMill-ACEHDLQA a. TransEDA, Verification Navigatorb. Synopsys, LEDAFPGA开发 a. Mentor, FPGAdvantageb. XILINX, ISEc. Altera, QuartusIISoC开发 a. Mentor, Seamless CVEb. Cadence, SPWc. Synopsys, Co-Centric版图设计工具 a. Cadence, Virtuosob. Mentor, IC-Stationc. 思源科技, Laker电路级仿真 a. Mentor, ELDOb. Mentor, ADMSc. Cadence, Spectre, Spectre RFd. Cadence, AMSe. Synopsys, Star-Hspice以下只是个人和本公司的评价,不一定十分全面,仅供参考。

cadence原理图仿真

cadence原理图仿真首先,我们来了解一下cadence原理图仿真的基本原理。

在进行原理图仿真时,我们需要将电路设计转换为一个数学模型,然后利用计算机软件对这个模型进行求解,得到电路的各种参数和性能指标。

这个数学模型通常是由电路的基本元件和它们之间的连接关系构成的,通过建立节点方程和元件特性方程,可以得到一个包含了电路各种参数的数学方程组。

然后利用数值计算方法对这个方程组进行求解,就可以得到电路的各种性能指标,比如电压、电流、功率等。

在cadence原理图仿真中,我们通常会使用一些常见的仿真工具,比如SPICE仿真器。

SPICE是一种通用的电路仿真工具,它可以对各种类型的电路进行仿真,包括模拟电路、混合信号电路和射频电路等。

通过建立电路的原理图,并在仿真器中设置各种参数和仿真条件,就可以对电路进行仿真分析,得到电路的各种性能指标。

在进行cadence原理图仿真时,我们需要注意一些关键的仿真参数和设置。

首先是仿真的时间步长和仿真的时间范围,这两个参数会直接影响到仿真的精度和速度。

通常情况下,我们需要根据电路的特性和仿真的要求来合理地设置这两个参数,以保证仿真结果的准确性。

另外,还需要注意仿真的激励信号和仿真的分析类型,比如直流分析、交流分析、脉冲分析等,这些参数会直接影响到仿真的结果和分析的内容。

除了基本的仿真参数设置,我们还需要注意一些特殊情况下的仿真技巧。

比如在进行混合信号电路的仿真时,需要考虑模拟部分和数字部分之间的接口和耦合关系,以保证整个系统的稳定性和正确性。

另外,在进行射频电路的仿真时,需要考虑传输线的特性和电磁场的影响,以保证仿真结果的准确性和可靠性。

总的来说,cadence原理图仿真是电子设计中非常重要的一环,它可以帮助工程师们验证电路设计的正确性和稳定性,提前发现潜在的问题,从而节省时间和成本。

通过合理地设置仿真参数和注意一些特殊情况下的仿真技巧,可以得到准确可靠的仿真结果,为电路设计和调试提供有力的支持。

cadence相关软件介绍.

公司概述Cadence是全球电子设计自动化(EDA领先企业,从事软件与硬件设计工具、芯片知识产权与设计服务,目前正致力于EDA产业的转型。

Cadence把此次转型构想命名为EDA360,因为它将包含设计过程中的所有方面,并关注最终产品的可盈利性。

这种应用驱动型方法,能在创建、集成与优化电子设计方面帮助我们的客户以更低的成本和更高的质量完成硅芯片、片上系统设备、以及完整的系统实现。

Cadence Design System, Inc.公司成立于1988年,总部位于美国加州圣荷塞,其设计中心、研发中心和销售部门分布于世界各地。

CADENCE中国1992年Cadence 公司进入中国大陆市场,迄今已拥有大量的集成电路 (IC 及系统设计客户群体。

在过去的二十年里,Cadence公司在中国不断发展壮大,建立了北京、上海、深圳分公司以及北京研发中心、上海研发中心,并于2008年将亚太总部设立在上海,Cadence中国现拥有员工400余人。

北京研发中心和上海研发中心主要承担美国公司总部EDA软件研发任务,力争提供给用户更加完美的设计工具和全流程服务。

Cadence在中国拥有强大的技术支持团队,提供从系统软硬件仿真验证、数字前端和后端及低功耗设计、数模混合RF 前端仿真与DFM以及后端物理验证、SiP封装以及PCB设计等技术支持。

我们的销售方案中还包括提供专业设计服务,VCAD团队为用户提供高质量、有效的设计和外包服务。

把世界顶尖的产品技术和服务融入中国,成为中国电子行业最亲密合作伙伴,和中国电子高科技产业共同腾飞是Cadence 在中国的坚定信念。

市场与趋势Cadence服务于产值达2万亿美元的全球电子市场,其中包括产值超过3000亿美元的半导体市场。

我们的主要垂直市场领域包括:有线与无线通讯;工业、医疗与汽车电子;计算机与消费电子,比如多媒体和个人娱乐设备。

这些领域占全球电子设备营收和半导体营收的90%以上。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

6.改名(rename):>mv A B (文件或目录改名) 7.删除: >rm fileA (删除文件,可以有多个文件名) >rm –r dirA (删除目录,可以有多个目录名) 8.编辑文件:>vi fileA (文件不存在时,自动创建新文件) 编辑命令:I(插入), o(下插入行), O(上插入行), Esc键(退出), x(删除字符), dd(删除行), h l k j或方向键(左右上下移动) 非编辑状态时,按Shift+:,文件尾出现“:”,此时可以 保存文件(w )和退出vi状态(q)。

1.创建目录: >mkdir dirname 2.改变工作目录:>cd dirname (到下级目录) > cd .. (到上级目录) 3.列出当前工作目录:>pwd 4.列文件清单:>ls dirA (可以有多个目录名,没有目录名时为当前目录。可以 加命令选项 -l or -a or -la) 5.复制(copy):>cp fileA fileB (文件复制) >cp fileA fileB dirA (复制文件到目录) >cp -r dirA dirB (复制目录)

打开工作窗口(terminal): 按mouse右键,点击open terminal

COPYRIGHT FOR ZHOUQN

关机:

在terminal中敲命令halt, 回车

重开机:

在terminal中敲命令reboot, 回车

COPYRIGHT FOR ZHOUQN

• LINUX操作系统常用命令简介

COPYRIGHT FOR ZHOUQN

• Cadence icfb EDA工具介绍

library、cell 和 view 1. Cadence icfb工具启动

登陆 创建工作目录:>mkdir work 进入工作目录:>cd work 启动icfb工具: >icfb&

出现CIW窗口

COPYRIGHT FOR ZHOUQN

COPYRIGHT FOR ZHOUQN

(11)Chech and Save

(12)Save

(5)放大、缩小 (6)Stretch拉动(保持连接) (7)copy (8)删除

从分类菜单中可以看 到命令的快捷键和许 多其它命令

(9)undo (10)属性、参数修改

COPYRIGHT FOR ZHOUQN

Cadence 仿真工具使用介绍

COPYRIGHT FOR ZHOUQN

• 物理版图设计

W

1.4 模拟集 成电路设计 步骤

W/L ratios

M3

设计构思 确定设计

电路设计

与设计指标比较 设计 模拟 与设计指标比较

– 根据工艺版图 L 设计规则设计 • 电路测试 电路或系 模拟集成 器件、器件之 统说明 电路设计 – 电路制备后 间的互联 – 对电路功能 电源和时钟线 的分布 和性能参数 – 的测试验证 与外部的连接

COPYRIGHT FOR ZHOUQN

• Linux操作系统:在pc机上,安装 (1) 虚拟机 (2) linux 操作系统 (3) 在linux操作系统中安装IC设计软件

COPYRIGHT FOR ZHOUQN

启动与登陆: (1) 虚拟机登陆

COPYRIGHT FOR ZHOUQN

• (2) 启动linux----点击start this virtual machine

COPYRIGHT FOR ZHOUQN

Pin names 总线命名方式 总线名放置方式 Pin 的旋转和镜像

(2)Add Pin 调用端口Pin

COPYRIGHT FOR ZHOUQN

连线名称

连线名称的相 关属性

(3)Add Wire连线 (narrow or wide)

连线规则 连线粗细

(4) Wire Name 连线命名

+ Vin

版图设计

M4

`

M6 Vout

M1

物理版图设计 C1 M2

`

版图验证

Cout Vb M4 M7

寄生参数提取 芯片制造 测试和验证

DC Currents

芯片实现

Topology

测试与产品开发

产品

COPYRIGHT FOR ZHOUQN

工具使用基本介绍

• 集成电路设计基本工作环境

EDA软件:Cadence 、Synopsys、Mentor等 • 资源库:生产商工艺相关文件、单元库等 • 用户数据:电路、版图、仿真文件等 • 硬件:工作站、 PC机 以下介绍在linux操作系统环境下的有关过程

• 2. Library 的创建

CIW窗口ToolsNewLibrary

COPYRIGHT FOR ZHOUQN

CIW窗口ToolsNewLibrary

COPYRIGHT FOR ZHOUQw

• 原理图 (schematic)-ComposerSchematic • 版图 (layout)--Virtouso

COPYRIGHT FOR ZHOUQN

原理图编辑 1.原理图编辑窗口结构

分类编辑 命令菜单

常用快捷命 令菜单

COPYRIGHT FOR ZHOUQN

浏览器 Library Name(option)

Cell View

阵列(行数、列数) 旋转、X镜像、Y镜像 Variable(如果有)

(1)Instance 调用库单元(Cellview)

COPYRIGHT FOR ZHOUQN

(3) 用户登录 注意:linux与windows切换用Ctrl + Alt键

COPYRIGHT FOR ZHOUQN

(3) 用户登录----输入用户名

COPYRIGHT FOR ZHOUQN

(3) 用户登录----输入用户名密码

COPYRIGHT FOR ZHOUQN

• 仿真环境设置

COPYRIGHT FOR ZHOUQN

• 仿真环境设置

COPYRIGHT FOR ZHOUQN

COPYRIGHT FOR ZHOUQN