Cadence IC设计教程

cadence教程-IC设计工具原理共页课件 (一)

cadence教程-IC设计工具原理共页课件 (一) CADENCE教程-IC设计工具原理共页课件作为一名IC设计工程师,必须要掌握各种IC设计工具。

Cadence是业内最受欢迎的EDA(电子设计自动化)软件之一,广泛应用于IC和系统级芯片设计。

这篇文章将介绍Cadence教程——IC设计工具原理共页课件,帮助初学者更好地了解这款软件。

一、课程内容该课程共分为六个部分,从IC设计的基础知识开始,逐步深入讲解Cadence软件的使用和原理。

1. IC设计的基础知识该部分主要介绍集成电路的概念、IC设计的基本流程、ASIC和FPGA的区别等内容,帮助学习者更好地了解IC设计的基本知识。

2. Cadence软件的安装和配置该部分教授如何安装、配置Cadence软件,学习者将了解如何正确设置工作目录、环境变量等,以便进行后续的IC设计工作。

3. Cadence软件的基本流程该部分主要介绍Cadence软件的基本使用流程,包括创建项目、编辑电路图、绘制版图、进行仿真等,重要的是学习者将学会如何创建一个完整的设计流程。

4. Cadence软件的高级应用该部分讲解Cadence软件的高级应用,包括使用脚本自动化设计、使用Verilog语言、进行DC分析、进行静态时序分析等内容,让学习者掌握Cadence软件更加深入的应用。

5. Cadence软件的Debug该部分介绍如何使用Cadence软件进行Debug,掌握Debug技巧,帮助学习者快速找到设计中的问题,并进行修复。

6. 基于Cadence软件的实际设计案例该部分介绍基于Cadence软件的实际设计案例,包括ADC设计、FPGA 设计等,帮助学习者更好地理解设计流程,并将所学知识应用到实践中。

通过以上六个部分,这个Cadence课程全面系统的讲解了IC设计软件工具的使用和原理共页,让学习者更好地了解Cadence软件和IC设计的概念和方法。

二、课程特点1.操作实战:一步步教大家如何使用Cadence软件,操作更为透彻,方便学生理解。

集成电路版图设计cadence设计流程

集成电路版图设计cadence设计流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor.I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!集成电路版图设计的Cadence设计流程详解集成电路(IC)版图设计是半导体行业中至关重要的环节,它直接影响到芯片的性能、功耗和可靠性。

CADENCE全定制IC设计流程

CADENCE全定制IC设计流程CADENCE是一种广泛应用于集成电路(IC)设计的软件工具。

它提供了完整的设计流程和工具,用于设计、验证和制造IC芯片。

在基于CADENCE的全定制IC设计流程中,在IC设计的每个阶段都使用到了CADENCE工具套件,包括电路和物理设计工具、模拟和数字仿真工具、布图工具以及物理验证工具等。

下面是使用CADENCE进行全定制IC设计的一般流程:1.设计需求分析:根据所需的功能和性能需求,进行设计需求分析。

这包括确定电路拓扑结构、电路规范和性能指标等。

2. 电路设计:使用CADENCE中的Schematic设计工具,绘制电路原理图。

根据设计需求,选择合适的电子元件并进行电路布线。

使用CADENCE的仿真工具,验证电路的功能和性能。

3.物理设计:将电路原理图转换为布局图。

使用CADENCE的布局工具,在设计规范的限制下进行器件布局和连线布线。

这包括选择合适的器件大小和排列方式,以优化电路性能和功耗。

4.物理验证:使用CADENCE的物理验证工具,对电路布局进行验证。

这包括电路的电性能分析、功耗分析、时序等效验证以及电磁兼容性分析等。

根据验证结果进行布局优化和改进。

5.交互测试:将设计与其他模块和子系统进行集成测试。

使用CADENCE的模拟工具和数字仿真工具,对整个系统进行功能验证和性能评估。

7.物理制造:通过CADENCE的布局生成工具,生成用于物理制造的设计数据库文件。

这包括物理制造规则检查、填充、光刻掩膜生成等。

8.物理验证:使用CADENCE的物理验证工具,对物理制造的设计进行验证。

这包括工艺模拟、功耗分析、封装和信号完整性分析等。

9.物理制造:将设计数据库文件发送给制造厂商进行实际制造。

这包括掩膜制造、芯片加工、封装和测试等。

10.性能评估:对实际制造的芯片进行性能评估和测试。

使用CADENCE的集成测试工具,进行功能测试、速度测试和功耗测试等。

11.系统集成:将IC芯片集成到目标系统中,并进行系统级测试和验证。

cadence教程IC设计工具原理课件

21

EDA概述

CADENCE

• EDA应用于三方面: 印制电路板的设计(PCB) 可编程数字系统设计(CPLD、 FPGA、SOPC) IC设计(ASIC, Soc)

26

EDA概述

CADENCE

• EDA主要供应商:

VHDL仿真 行为综合 逻辑综合 可测性设计 低功耗设计 布局布线

后仿真

Cadence Vantage Synopsys Synopsys Alta Synopsys Compass Mentor Graphics Synopsys Sunrise Compass Synopsys Epic Cadence Avant! Mentor Graphics Synopsys Cadence Compass IKOS Vantage

(4)物理版图设计和验证工具(Cadence公司的Virtuoso Layout Editor,Synopsys公司的ComsSE ,Tanner公司的 L-edit)

(5)模拟电路编辑与仿真(Synopsys公司的HSpice , Cadence公司的Spectre Simulator ,Tanner公司的S-edit)

第一章 IC设计基础

CADENCE

• 集成电路设计就是根据电路功能和性能 的要求,在正确选择系统配置、电路形 式、器件结构、工艺方案和设计规则的 情况下,尽量减小芯片面积,降低设计 成本,缩短设计周期以保全全局优化, 设计出满足要求的集成电路。其最终的 输出是掩模版图,通过制版和工艺流片 得到所需的集成电路。

• 缺点:会有一定比例的后续工序无法适应软核IP设计, 从而造成一定程度的软核IP修正,在性能上有较大的 不可预知性。

CADENCE全定制IC设计流程

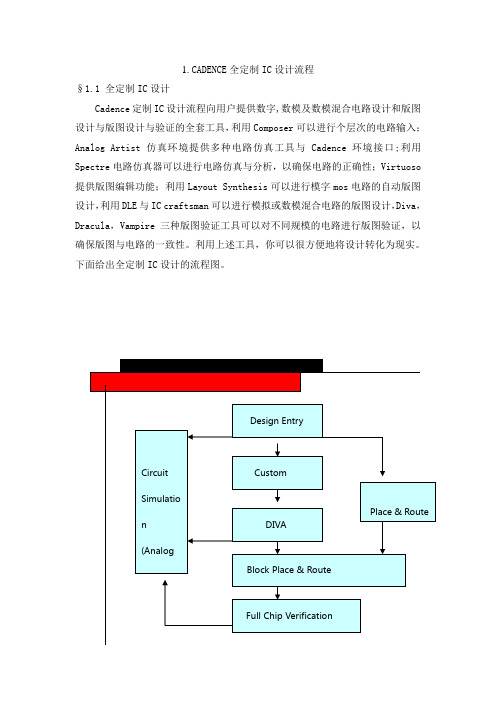

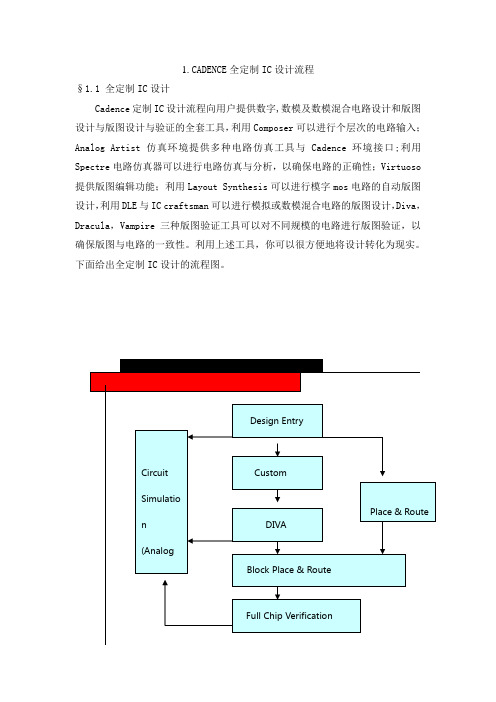

1. CADENCE全定制IC设计流程§1.1 全定制IC设计Cadence定制IC设计流程向用户提供数字,数模及数模混合电路设计和版图设计与版图设计与验证的全套工具,利用Composer可以进行个层次的电路输入;Analog Artist仿真环境提供多种电路仿真工具与Cadence环境接口;利用Spectre电路仿真器可以进行电路仿真与分析,以确保电路的正确性;Virtuoso 提供版图编辑功能;利用Layout Synthesis可以进行模字mos电路的自动版图设计,利用DLE与IC craftsman可以进行模拟或数模混合电路的版图设计,Diva,Dracula,Vampire三种版图验证工具可以对不同规模的电路进行版图验证,以确保版图与电路的一致性。

利用上述工具,你可以很方便地将设计转化为现实。

下面给出全定制IC设计的流程图。

2.Cadence cdsSPICE的使用说明Cadence cdsSPICE 也是众多使用SPICE内核的电路模拟软件之一。

因此他在使用上会有部分同我们平时所用到的PSPICE相同。

这里我将侧重讲一下它的一些特殊用法。

§ 2-1 进入Cadence软件包一.在工作站上使用在命令行中(提示符后,如:ZUEDA22>)键入以下命令icfb&↙(回车键),其中& 表示后台工作。

Icfb调出Cadence 软件。

出现的主窗口如图2-1-1所示:图 2-1-1Candence主窗口二.在PC机上使用1)将PC机的颜色属性改为256色(这一步必须);2)打开Exceed软件,一般选用xstart软件,以下是使用步骤:start method选择REXEC(TCP-IP),Programm选择Xwindow。

Host选择10.13.71.32 或10.13.71.33。

host type选择sun。

并点击后面的按钮,在弹出菜单中选择command tool。

(完整版)CADENCE全定制IC设计流程

1. CADENCE全定制IC设计流程§1.1 全定制IC设计Cadence定制IC设计流程向用户提供数字,数模及数模混合电路设计和版图设计与版图设计与验证的全套工具,利用Composer可以进行个层次的电路输入;Analog Artist仿真环境提供多种电路仿真工具与Cadence环境接口;利用Spectre电路仿真器可以进行电路仿真与分析,以确保电路的正确性;Virtuoso 提供版图编辑功能;利用Layout Synthesis可以进行模字mos电路的自动版图设计,利用DLE与IC craftsman可以进行模拟或数模混合电路的版图设计,Diva,Dracula,Vampire三种版图验证工具可以对不同规模的电路进行版图验证,以确保版图与电路的一致性。

利用上述工具,你可以很方便地将设计转化为现实。

下面给出全定制IC设计的流程图。

2.Cadence cdsSPICE 的使用说明Cadence cdsSPICE 也是众多使用SPICE 内核的电路模拟软件之一。

因此他在使用上会有部分同我们平时所用到的PSPICE 相同。

这里我将侧重讲一下它的一些特殊用法。

§ 2-1 进入Cadence 软件包一.在工作站上使用在命令行中(提示符后,如:ZUEDA22>)键入以下命令icfb&↙(回车键),其中& 表示后台工作。

Icfb 调出Cadence 软件。

出现的主窗口如图2-1-1所示:图 2-1-1Candence 主窗口二.在PC 机上使用1)将PC 机的颜色属性改为256色(这一步必须);2)打开Exceed 软件,一般选用xstart 软件,以下是使用步骤:start method 选择REXEC (TCP-IP ) ,Programm 选择Xwindow 。

Host 选择10.13.71.32 或10.13.71.33。

host type 选择sun 。

Cadence IC Design

第1章Cadence IC 5.1.41 的基本设置本章是Cadence IC 5.1.41 是设计的简明入门教程,目的是让读者在刚接触该软件的时候对它的基本功能有一个总体的了解。

本章主要内容如下:[1] 启动Cadence IC 前的准备;[2] Command Interpreter Window (CIW, 命令行窗口);[3] Library Manager 设计库管理器;[4] Virtuoso® Schematic Editor 电路图编辑器简介;[5] Virtuoso® Analog Design Environment (ADE) 简介。

1.1 启动前的准备要在Unix/Linux 使用Cadence IC 5.1.41 工具应当保证以下的条件:[1] 保证Cadence IC 5.1.41 已经由管理员正确地安装在电脑上;并且软件授权密钥已经设置完成。

[2] 在Shell 中设置了正确的环境变量。

必须将Cadence IC 的安装路径加入Shell 环境变量,Cadence IC 5.1.41 才能正常运行。

以Cshell 为例,Cadence IC 被安装在了/tools/cadence/ic5141,则需要在~/.cshrc 文件中加入这样的路径配置语句:setenv ic50 /tools/cadence/ic5141set LD_LIBRARY_PATH=($ic50/tools/lib $ic50/tools/dfII/lib $ic50/tools/tcltk/ tcl8.0/lib $LD_LIBRARY_PATH)set path = ($ic50/tools/bin $ic50/tools/dfII/bin $ic50/tools/dracula/bin $path)也可以把路径的设置写在一个单独的配置文件中。

例如,将上面的配置写在配置文件/env/cadence_5141 中,则可以在~/.cshrc 中加入一行source /env/cadence_51411.1.1 启动配置文件:.cdsinit.cdsinit 文件是在Cadence IC 中启动时运行的SKILL 脚本文件。

CadenceIC设计基础教程.pdf

第1章 Cadence IC 5.1.41的基本设置本章是Cadence IC 5.1.41是设计的简明入门教程,目的是让读者在刚接触该软件的时候对它的基本功能有一个总体的了解。

本章主要内容如下:[1] 启动Cadence IC前的准备;[2] Command Interpreter Window (CIW, 命令行窗口);[3] Library Manager 设计库管理器;[4] Virtuoso® Schematic Editor电路图编辑器简介;[5] Virtuoso® Analog Design Environment (ADE) 简介。

1.1启动前的准备要在Unix/Linux使用Cadence IC 5.1.41工具应当保证以下的条件:[1] 保证Cadence IC 5.1.41已经由管理员正确地安装在电脑上;并且软件授权密钥已经设置完成。

[2] 在Shell中设置了正确的环境变量。

必须将Cadence IC的安装路径加入Shell环境变量,Cadence IC 5.1.41才能正常运行。

以Cshell 为例,Cadence IC被安装在了/tools/cadence/ic5141,则需要在~/.cshrc文件中加入这样的路径配置语句:setenv ic50 /tools/cadence/ic5141set LD_LIBRARY_PATH=($ic50/tools/lib $ic50/tools/dfII/lib $ic50/tools/tcltk/ tcl8.0/lib $LD_LIBRARY_PATH)set path = ($ic50/tools/bin $ic50/tools/dfII/bin $ic50/tools/dracula/bin $path)也可以把路径的设置写在一个单独的配置文件中。

例如,将上面的配置写在配置文件/env/cadence_5141中,则可以在~/.cshrc中加入一行source /env/cadence_51411.1.1启动配置文件:.cdsinit.cdsinit文件是在Cadence IC中启动时运行的SKILL脚本文件。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验一、Virtuoso Schematic Editor实验目的:掌握电原理图(schematic)设计输入方法。

边学边做[1]启动IC Design 软件:开机后运行Exceed进入服务器SOLARIS登录界面,输入用户名和密码(由系统管理员提供);点击一下cpu disk菜单项上方的三角箭头,点击This Host出现Terminal窗口,(或点击Console 出现Console窗口);cp /eva01/cdsmgr/ training_IC_data/SchemEd.tar . (提醒:最后是个小点,稍等)tar vxf SchemEd.tar (稍等)cd adelabic5icfb &(或icms &,你知道后缀&的作用吗?在UNIX命令后加&表示后台运行)若出现“What’s New”窗口,关掉它。

出现“icfb-log:/…”窗口(CIW:Command Interpreter Window)了吗?[2]建立新库、新单元以及新视图(view):在CIW中,File->New->Library,在弹出的“New Library”窗口,Name栏中:mylib选中右下方:* Don’t need techfileOK查看CIW窗口:Tools->Library Manager,在Library中应有mylib,单击它。

在Library Manager 窗口,File->New->Cellview,在弹出的“Create New File”窗口Cell Name栏中,nand2Tool栏中,选Composer-SchematicOK[3]添加元件(实例instance)在弹出的“Virtuoso Schematic Editing:…”窗口中,左边为工具栏,选instance图标(或i)单击“Add instance”窗口Library栏最右侧Browser,弹出“Library Browser-…”窗口,Library选analogLib,Cell选nmos4, View选symbol鼠标回到“Add instance”窗口,Model name栏:trnmos, width: 3.0u , Length: 0.5u,Hide 在“Virtuoso Schematic Editing:…”窗口, 鼠标左键单击一次,间隔一定距离再单击一次,这样就增加了2个nmos4元件,ESC(试一试:先选中一个元件,再q,查看/改变属性)。

仿照上述方法,增加pmos4元件。

在“Add instance”窗口,Model name栏:trpmos,width: 2.0u , Length: 0.5u;放置2个pmos4,ESC。

(试一试热键f,[,]的功能)[4]添加管脚(PIN)选“Virtuoso Schematic Editing:…”窗口左边工具栏中的Pin图标(或p)在“Add Pin”窗口中,Pin Names:INA INB,Direction选input, Usage选schematic,Hide 在“Virtuoso Schematic Editing:…”窗口, 鼠标左键单击一次,间隔一定距离再单击一次,放置2个输入PIN,p,在“Add Pin”窗口中,Pin Names:OUT,Direction选output, Usage选schematic,在“Virtuoso Schematic Editing:…”窗口放置输出PIN,[5]添加电源和地:i (或单击instance工具图标)弹出“Add instance”窗口,Browse,Library选analogLib,Cell栏:vdd, View选symbol在“Virtuoso Schematic Editing:…”窗口放置vdd,回到“Add instance”窗口,Browse,Cell栏:gnd, 在“Virtuoso Schematic Editing:…”窗口放置gnd,ESC , Cancel掉“Add instance”窗口。

[6]摆放元件并加网线:参照下图放好元件(symbol):(移动用m键,删除用Delete键,取消命令用ESC键)选“Virtuoso Schematic Editing:…”窗口左边工具栏中的Wire(narrow),连好网线,ESC[7]保存文件:“Virtuoso Schematic Editing:…”窗口左上角Check and Save工具。

DIY(Do It Yourself)在mylib库中建立amplifier单元(Cell)如下图所示。

图中所有单元来自analoglib库,参数如下表:Cell Name 属性propertiesQ0,Q1:Model Name=trnpnnpn Forpnp ForQ2,Q3,Q4:Model Name=trpnppmos4 For M1: Model Name=trpmos, Length=8u, Width=iPar(“l”)*16nmos4 For M2,M5: Model Name=trnmos, Length=10u, Width=100upmos4 For M3: Model Name=trpmos, Length=iPar(“w”)/16, Width=128ures Resistance=2.5Kcap Capacitance=CAP (设计变量)vdd, vss 注意 vss是负电源,不是gndPIN管脚:输入管脚: iref, inm, inp, 输出管脚: outWire Name vdd! , gnode注意:你画的schematic电路中,双极晶体管Q和FET管M的下标编号可能与上图不同,可用q查看/改变属性,另外可能使用m (移动),r(旋转),f(全屏),先m再shift + r (左右翻转),先m再 Ctrl + r (上下翻转)等命令。

ESC(终止操作)标注线网名:用Wire Name工具(或l)将M1与M3的衬底连线、M2与M5的栅极连线分别标注为vdd!和gnode。

如发生了错误删除,用“Virtuoso Schematic Editing:…”窗口左边中间的undo工具(或u),注意:只能恢复前一个被删除的对象。

最后check and save.层次化设计——symbol生成[1]symbol生成进入“Virtuoso Schematic Editing:mylib nand2 schematic”窗口。

Design -> Create Cellview->From Cellview在Cellview From Cellview窗口,From View Name栏为:schematic,Tool / Data Type栏为Composer-Symbol。

OK在“Symbol Generation Options”窗口,单击Load/Save按纽,OK出现“Virtuoso Schematic Editing:mylib nand2symbol”窗口,Design->Check and Save改变symbol形状:用m命令将Symbol的上边界位置和INA管脚向上移动一网格,得到下图:用m命令将3个cdsParam(n)移到方框外面的下方,将cdsName()移到方框外面上方,将字符OUT移到方框外面右方,删除内部绿色方框。

参照下图,单击菜单Add -> Shape -> Circle,加个小圆圈,Add -> Shape -> Arc,加个圆弧(先确定上下2点,如出现angle not allowed不必紧张,稍微移动鼠标试一试,你会发现如何画弧),用m将左边的红色外框右移(缩短原symbol外框),2个PIN以及连线(INA和INB)同样右移,用Line工具画出缺少的3边。

上述步骤中,均使用ESC取消操作命令。

画好后,Design -> Check and Save[2]创建amplifier的symbol:仿照前述步骤,得到如下symbol:提示:在“Symbol Generation Options”窗口,将iref 管脚(Pin)设置为Bottom Pin。

然后删除cdsParam(3), r旋转pin名iref,(选做)删除红色外框,选择Selection Box工具,在“Add Selection Box”中,Automatic添加Text:Add -> Note -> Note Text,在“Add Note Text”窗口的Note Text文本框中:Amp 将鼠标移至“Virtuoso Symbol Editing:mylib amplifier symbol”窗口,在你希望的位置单击,回到“Add Note Text”窗口,Cancel。

Save。

(如果你无法画斜线,鼠标右键点击1、2次就可切换成功)结果如下图所示:实验结果查验:1.申请教员或助教查验你做的实验结果。

2.Close 所有窗口。

注意:你所画的部分电路,以后在spectre仿真实验时会用到。

因此不要删除!Cadence IC设计实验实验二、 Spectre Simulation实验目的:掌握电路特性仿真方法进入Cadence系统:cd adelabic5icfb &实验内容与步骤:一、nand2电路仿真[1]、创建激励信号电路模块:在CIW窗口(icfb-Log:/…):Tools->Library Manager,弹出Library Manager 窗口,在Library中应有mylib,点击它。

File->New->Cellview,在弹出的“Create New File”窗口Cell Name栏中,testnand2Tool栏中,选Composer-Schematic, OK在“Virtuoso Schematic Editing:…”窗口中,按下图加入单元(Instance)、Pin并连线。

点击Check and Save图中所有单元来自analoglib库symbol,参数如下:Cell Name CDF Parametervpulse V0: V olt 1:0, V olt2:3, Delay:10n, Rise:500p,Fall:500p,width:10n,Period:20n vpulse V1: V olt 1:0, V olt2:3, Delay:15n, Rise:500p,Fall:500p,width:20n,Period:40nDCvotlage:3,Number of noise:0 (前面所有电源此项均为0)V2:vdc Forcap For C0: Capacitance: 100fvdd,gndPin管脚:Name: INA INB OUT, Direction: inputoutput[2]、编写仿真文件1.设置仿真环境。