cadence原理图设计实例教程

Cadence原理图库的制作及使用(二)

Cadence原理图库的制作及使用(二)在上一节中,我们讲述了一种原理图库的制作方法:使用封装编辑器创建封装,然后生成符号。

在本节内容当中,我们将要讲述另外一种制作方法:先创建符号,然后由符号得到封装。

本节将要讲述另外一种方法:从符号得出封装。

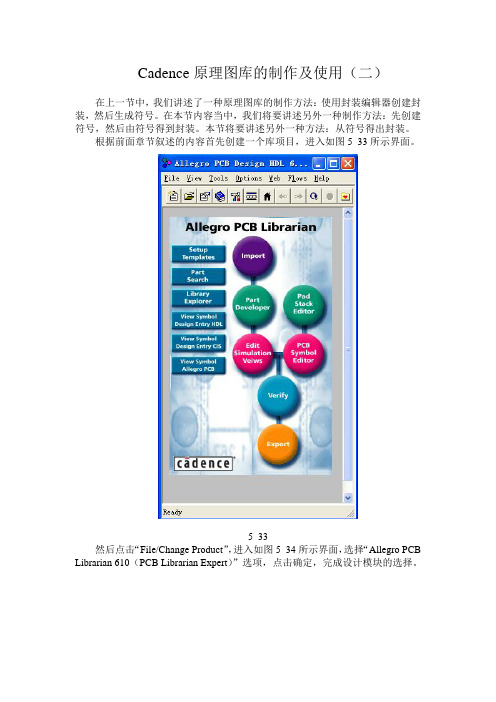

根据前面章节叙述的内容首先创建一个库项目,进入如图5_33所示界面。

5_33然后点击“File/Change Product”,进入如图5_34所示界面,选择“Allegro PCB Librarian 610(PCB Librarian Expert)”选项,点击确定,完成设计模块的选择。

5_34单击图5_33中“Part Developer”,进入库设计软件界面,如图5_35所示。

5_35选择File菜单中的New/Cell选项,出现如图5_36所示对话框。

5_36有些元件有多个相同的功能组,需要创建单个功能组的符号和整个元件的符号以方便原理图设计,满足设计的不同需求。

创建符号的方法如下:1、输入sizeable管脚并通过符号编辑器创建符号;2、创建封装;3、创建必要的通道;4、通过拷贝sym_1来创建sym_2;5、确定sym_2的SIZE属性并添加HAS_FIXED_SIZE 属性。

在“Cell”对应的空白栏处输入元件库的名称,自己可以随意写,但是最好用和芯片信息相关的名字,比如可以用元件型号命名,例如要制作74HC04的原理图元件库,在空白栏处输入74HC04,单击确定,出现如图5_37所示界面。

5_37选择左边项目栏中的symbols选项,右键点击弹出如图5_38所示界面。

5_38选择弹出菜单中的“New”选项,左键点击之后界面如图5_39所示。

5_39在右边界面当中选择“symbol pins”选项卡,界面如图5_40所示。

5_40左键点击“Pins”选项卡,弹出如图5_41 所示菜单。

选择“Add”选项,打开如图5_42所示界面。

5_415_42在该例子中,我们选择【Sizeable】单选框,74HC04芯片有一个输入管脚A,一个输出管脚Y,共有六个slots。

Cadence--原理图的设计2

线进行连接,则需要在A图纸和B图纸上分别放置两 个“页面连接器”,而且两个图纸上的页面连接器 的名称应该完全一致,这样才能表示它们之间的连 接关系。

层次式电路原理图设计

现代电路设计往往采用“由顶而下”的设计方法

(其实不仅仅是电路设计,程序设计、结构设计等, 也常常采用“由顶而下”的方法),层次式原理图 就适应了这种设计思想。

Cadence—原理图设计2

原理图的类型

平坦式电路原理图设计

层次式电路原理图设计

平坦式电路原理图设计

平坦式电路原理图,就相当于把一张大的原理图切

割成若干份,而每张图纸就是切割后的小图,同时 各个图纸之间是通过“页面连接器”相互连接的。 放置页面连接器时,首先点击

比如在A图纸的电路与B图纸的电路之间,有两条连

在层次式电路原理主图中,反映各个 子图之间的连接关系;子图反映内部具体的电路。

我们的设计最好采用先设计主图,并由主图中的子

图块生成子图,再绘制子图电路。这样的设计方法 是典型的“由顶而下”的设计方法。

绘制子图块,点击

绘制子图的对话框

课堂作业

1、完成一个平坦式原理图

2、完成一个层次式原理图

检查调试至无错

在这之后,我们应该绘制该子图所对应的具体电路,

在此过程中,接口的位置也可以根据需要进行移动。

创建完成后项目管理器和信息输出可以看见主图、

子图以及接口的信息。

模块一

模块二

模块三

在绘制了所有子图的电路之后,按照以前的步骤,

还需要进行DRC校验、元件重新编号、元件封装的 设置、生成网络表等工作。

在主图上画出了子图块之后,还要给它填上接口,添

加接口的方法是,首先点击子图块,使其处于被选中 的状态,然后点击 图标。

第二章Cadence的原理图设计

第二章 Cadence的原理图设计2.1Design Entry CIS软件概述Cadence软件系统有两套电路原理图的设计工具,一套是Design Entry HDL,另一套就是我们马上要开始学习的Design Entry CIS。

其中Design Entry HDL 是Cadence公司原本的原理图设计软件,可以用于芯片电路和板级电路的设计,其长处在于可以把芯片的电路原理图和板级电路原理图结合在一起,进行综合设计;而Design Entry CIS主要用于常规的板级电路设计,Design Entry CIS原本是OrCAD公司的产品,OrCAD公司后来被Cadence公司收购,于是Design Entry CIS也就成了Cadence公司的另一套电路原理图设计软件。

Design Entry CIS原理图设计软件的特点是直观、易学、易用,在业界有很高的知名度,利用Design Entry CIS原理图设计软件可以进行简单的(只有单张图纸构成的)电路原理图设计,也可以进行(由多张图纸拼接而成的)平坦式电路原理图设计,还可以进行(多张图纸按一定层次关系构成的)层次式电路原理图设计。

在本章中,我们首先学习简单的电路原理图设计,然后再学习较为复杂的平坦式和层次式电路原理图设计。

我们将围绕一块非常简单的STC系列单片机下载电路板,学习简单电路原理图的设计,同时在此过程中,还将学习到USB转UART串行口、STC系列单片机下载电路等方面的知识。

接着,我们将围绕一块ARM-7核心实验板,进行平坦式和层次式电路原理图的设计,而该核心板是配套于ARM-7实验箱。

在此过程中我们还将学习到嵌入式技术等方面的知识。

2.2初识Design Entry CIS一.启动Design Entry CIS我们在电脑上点击“开始→所有程序→Cadence SPB 16.2→Design Entry CIS”,如下图所示:图2-1 启动Design Entry CIS这时将弹出如下对话框:图2-2 选择工作内容在这里我们选择“OrCAD Capture CIS”一项,点击“OK”按钮后,就实际启动了Design Entry CIS,出现如下界面:图2-3 OrCAD Capture CIS软件界面与大多数软件一样,OrCAD Capture CIS软件也是以项目方式管理我们的设计文件的。

(完整版)OrCADCaptureCIS(Cadence原理图绘制)

(完整版)OrCADCaptureCIS(Cadence原理图绘制)OrCAD Capture CIS(Cadence原理图绘制)1.新建原理图 (2)1,打开软件 (2)2,设置标题栏 (2)3,创建⼯程⽂件 (4)4,设置颜⾊ (4)2.制作原理库 (6)1,创建元件库 (6)2,修改元件库位置,新建原理图封库 (6)3,原理封装库的操作 (7)3.绘制原理图 (9)1.加⼊元件库,放置元件 (9)2.原理图的操作 (10)3. browse命令的使⽤技巧 (12)4.元件的替换与更新 (13)4.导出⽹表 (14)1.原理图器件序号修改 (14)2.原理图规则检查 (15)3.显⽰DRC错误信息 (16)4.创建⽹表 (17)5.⽣成元件清单(.BOM) (18)设计⽬的:创建如图RS232转换RS422原理图1.新建原理图1,打开软件2,设置标题栏Options-------DesignTemplate创建完原理图⼯程后,也可以修改标题栏Options--------Schematic Page Properties3,创建⼯程⽂件File------New------Projet4,设置颜⾊Options--------Preferences2.制作原理库1,创建元件库File-------New----Library2,修改元件库位置,新建原理图封库点击如图位置⿏标右击,点击Save As另存为。

New Part新建⼀个封装库。

3,原理封装库的操作Place------Pin 放置管脚选中管脚,按住键盘Ctrl同时⿏标拖动器件完成管脚的复制选中管脚⿏标右击Edit Properties 编辑选中管脚信息,如下图Place------Rectangle 放置矩形Place------line 放置线Place------Text 放置⽂字Place------ellipse 放置椭圆Options-----Part Properties 原理封装库属性Options-----Package Properties 原理封装库信息View------- Package 显⽰这个封装库的所有部分快捷键I-----放⼤O----缩⼩Delete-------删除最终根据操作完成MAX3221ECAE原理图库的编辑3.绘制原理图1.加⼊元件库,放置元件1.打开原理图⼯程,打开原理图2.Place-------Part(快捷键P)添加封装注:软件⾃带库路径,如下图所⽰常⽤到的电容电阻库2.原理图的操作1.快捷键I-----放⼤O----缩⼩Delete-------删除W-------放置⾛线R----旋转⽅向按住Alt键拖动器件可以切断⽹络连接Edit-----Mirror-----Horizontally ⽔平⽅向镜像Edit-----Mirror------ vertically垂直⽅向镜像Edit-----Mirror---------Both整体镜像Edit-----Properties显⽰修改PCB封装信息2.选中器件,按住键盘Ctrl同时⿏标拖动器件完成器件的复制3.放置⾛线 1.⿏标左键双击终⽌布线2.画线时按住键盘Shift 任意⾓度⾛线4.放置电源5.放置地6.放置空⽹络7.放置节点8.相同原理图放置⽹络连接(快捷键N)9. 放置总线10. 总线⼊⼝(F4连续放置总线⼊⼝⽹络等⾃动递增)11. 不同原理图页⾯的⽹络连接12. 放置⽂字13.Options--------Preferences3. browse命令的使⽤技巧1.选中.dsn⽂件如图2.Edit----Browse-----Parts显⽰修改器件信息Edit----Browse-----Nets显⽰修改⽹络信息Edit----Browse-----DRC markers显⽰DRC错误信息Edit----Browse-----off-page connectors显⽰不同原理图页⾯的⽹络连接4.元件的替换与更新1.选中打开原理图⼯程中Design cache,如图⿏标右击Cleanup Cache清除原理图中不存在的元件封装库2.⿏标右击Design cache下所需要更新替换的封装库Replace Cache-------替换元件封装库,如图所⽰Update Cache--------更新封装库最终经过以上操作完成如图所⽰原理图绘制4.导出⽹表注:导⽹表之前的注意事项:1.原理图器件序号修改2.原理图规则检查3.PCB封装库是否正确⽆误,属性是否正确4.⽹络管脚顺序是否准确5.如果建⽴⽹络表时出现错误,查看“Sessions log”中错误信息1.原理图器件序号修改1.选中.dsn⽂件如图2.Tools-------Annotate第⼀步:清除所有器件序号第⼆步:重新增加器件序号2.原理图规则检查Tools-----Design Rules Check3.显⽰DRC错误信息Edit----Browse-----DRC markers4.创建⽹表Tools------Create Netlist如果建⽴⽹络表时出现错误,查看“Sessions.log与netlist.log”中错误信息5.⽣成元件清单(.BOM) 注:⽣成清单前请先创建⽹表1,先选中如图.dsn⽂件2,Tools---------Bill of Materials按照公司规范进⾏元件清单处理:10KMCSY清单.xlsx。

CADENCE 培训(原理图设计一)

CONCEPT-HDL原理图设计一.创建新项目1.用Project Manager建立Project*注意:在这里最好新建一个自己的设计目录并将所用库拷到本目录下,如果用默认的目录和库,很容易将目录结构搞乱。

记住一定要编辑cds.lib文件在Project Manager工具栏中选择File->New,将出现一个建立Project的对话框,按着提示新建了一个cpm文件并建立起了一个Lib:Cell:View:File结构的目录层次。

其中Lib、Cell和View分别表示一组目录。

在实际使用中发现,认识并理解这个结构,对学习这套工具的使用很有帮助。

下图显示了一个典型的Lib:Cell:View目录结构:由上图可以看出Lib目录是一个库目录,该目录下包含了所有的Cells。

每个Cell目录下存放了一个设计(这里的设计是指PCB或芯片的设计,因此PCB中使用的芯片也被认为是一个设计而存在Cell目录下)的所有数据。

这些数据又被分类归入各个VIEW。

比如,UAS项目中交换板的Cell目录是SPB,在SPB下有schematic,symbol,package和physical等view目录。

每个View目录下包含了一个设计的某一方面的数据。

比如,原理图数据都被存放在sch_n VIEW(n表示原理图的版本号)。

而Layout数据则被放physical下。

<project_name>.cpm当新工程的Wizard提示你给出新工程的名字后,你提供的工程名将被小写和加重,这个文件被用作工程文件名(后缀为*.cpm),这个工程文件包含了设计名称和库搜索列表(设计列表和零件列表)。

cds.lib一个库被添加到搜索列表里之前,他首先必须被定义在cds.lib文件里,因此每一个在搜索列表里的库必须有一个都必须有一个相应的条目在cds.lib里。

每个在cds.lib里的库有两个特征:名称和物理位置。

New Project Wizard会自动添加一个设计库进入工程文件,cds.lib文件辉映射库名到库位置。

Cadence-实例教程--唐明

Hierarchy-Editor

config

2.7Cell 的管理

Cell 的删除、复制、重命名与Library相似

3.绘制原理图

3.绘制原理图

使用 Cadence 软件进行绘图操作时,应注 意掌握其软件设计思想。无论在原理图设 计、符号设计还是版图设计,都有一个“操 作模式”的概念。

Cadence 软件适合“批量式”操作 切换操作的方法有两种,一是“Esc”键退回

1.2环境设置

1 .cshrc 文件设置

.cshrc文件中指定 Cadence 软件和 licence 文件所在的路径

2 .cdsenv 文件设置

.cdsenv 文件包含了 Cadence 软件的一些初始设置,该文件用 SKILL 语言写,Cadence 可直接执行

3 .cdsinit 文件设置 4 cds.lib 文件设置 库文件定义 5 工艺文件(technology file)

1.4添加工艺库

2.库文件的管理

2.库文件的管理

CIW>Tools> Library Manager 可以在Library Manager中已存在的Cell View

库(library):特定工艺相关的单元集合 单元(cell):构成系统或芯片模块的设计对象 视图(view):单元的一种预定义类型的表示 CIW:命令解释窗口 属性(attributes):预定义的名称-值对的集合 搜索路径(search path):指向当前工作目录和

3.6旋转和翻转元件

按键m>选中元件>按键F3>设置 Rotate—旋转,Sideways—左右翻转,

Upside Down—上下翻转 放置元件

3.7放大缩小

Cadence教程(D422)

规定:本实验教材中红色为键入命令或字符,兰色为菜单项,紫色为键盘功能键;“单击”指鼠标左键按下一次。

实验一、Virtuoso Schematic Editor实验目的:掌握电原理图(schematic)设计输入方法.[1]启动IC Design 软件:首先,登陆Linux,在username文件夹中建立一个你命名的文件夹,然后在Terminal 窗口中进入这个文件夹,在该文件夹目录下输入:icfb&,(这样,你在cadence 中做的一切工作都会自动保存在这个文件夹中,如果直接icfb&的话,会导致你的工作成果,例如:电路图、仿真结果等,会在/home中保存,影响其他人的使用)[2]建立新库、新单元以及新视图(view):首先,输入icfb&后,出现下图窗口在图中CIW窗口中依次打开:Tools-〉Library Manager,出现下图窗口:在图中窗口中依次打开:File-〉New—>Library,出现下图窗口:输入Library Name:test,然后点OK。

(注意下面的保存路径就是你第一步建立的文件夹)出现下一个窗口:选中Attach to an existing techfile,然后OK.出现下一个窗口:选中右下方Technology Library:chrt35dg_SiGe,然后OK.下面我们来画一个nand2电路。

选中左侧的test,在Library Manager 窗口,File->New-〉Cellview,如下图:在弹出的“Create New File”窗口Cell Name栏中,nand2 Tool栏中,选Composer—SchematicOK,如下图[3]添加元件(实例instance)在弹出的“Virtuos o Schematic Editing:…”窗口中,左边为工具栏,选instance 图标(或i)单击“Add instance”窗口Library栏最右侧Browser,弹出“Library Browser-…”窗口,Library选chrt35dg_SiGe,Cell选nmos_3p3, View选symbol鼠标回到“Add instance”窗口,Model name栏:nmos_3p3,width(Total Width): 3.0u , Length:0。

cadence原理图设计实例教程

器件放置

• 也可以按下步骤放置uA741:

➢ 执行P1ace/Part命令 ➢ 在 Part中输“ *741* ” , ➢ 点击Part Search, ➢ 点击Begin Search, ➢ 在Library 库中寻找到

uA741/opamp.olb ➢ 单击“OK” ➢ 执行前面的步骤,单击

“OK”,放置器件,断开放 置

放置电容符号

➢ 执行P1ace/Part命令 ➢ 在 “Libraries”列表框中选

择“ANALOG” ➢ 在 “Part”列表框中选择

“ C” ➢ 单击“OK” ➢ 将电阻C移至合适位置,

(按键盘中的R键,器件旋 转)按鼠标左键放置 ➢ 按ESC键(或鼠标右键点 end mode)结束绘制元器

器件封装调用

在Link Footprint to Component 栏内点OK,对于没有 定义的管脚封装图,出现MAXECO提示说明,确定

器件封装调用

在Link Footprint to Component 栏内点OK,对于没有定义的管脚封 装图, 点Link existing footprint to component来查找连接封装。

Place net name

放置分页图纸间的接口

原理图绘制

(二) 原理图绘制

以声控开关为例(电源是直流12V,负载为发光二极管)见下 图:

放置集成块运放uA741

• 执行P1ace/Part命令 • 在 “Libraries”列表

框中选择“OPAMP” 库 • 在 “Part”列表框中 选择“uA741” • 单击“OK” • 将集成块移至合适位 置,按鼠标左键 • 按ESC键或鼠标右键点 end mode以结束绘 制元器件状态

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

仿真波形测量

➢ 执行Plot/Label/Mark命令,显示该波形顶峰标尺坐标

仿真波形测量

➢ 第一位置坐标为顶峰处时间数值 ➢ 第二位置坐标为顶峰处电压数值

仿真波形测量

➢ 执行Trace/Cursor/Trough命令, Plot/Label/Mark命令,测量该波形谷底坐标

仿真波形测量

声音信号触发后灯亮保持时间的测量: 执行Trace/Cursor/Display命令,使测量坐标处于显示状态

仿真波形测量

➢ 点击分析窗口左下角“V(U2:OUTPUT)”, 再点击该波形在声音 触发下,由低电平变成高平处的位置,执行Plot/Label/Mark,读 出该处的时间为795us,同样测量出该信号由高电平变成低电平 处的时间为11.321ms,两者相减约10.526ms。

3、电路原理图编辑

实验仿真

开始绘制电路图 :进入Schematic窗口,则在窗口右边 会出现下图的工具栏:

放置总线引出管脚

放置端口

指示管脚不连接

Place junction

放置阶层

放置阶层引脚

添பைடு நூலகம்文字

Place part

Place Bus

Place GND

绘制无电气性质符号

Place wire

Place power

印制版设计

2、启动OrCAD/ Layout

选择“开始”→“程序”→“OrCAD Release 9.1”→“Layout”

印制版设计

3、 启动File>New命令或按钮 4、 指定所要启用的板框档(*.tpl)或技术档(*.tch),查找范 围Orcad/Layout/Data 如下图,查找DEFAULT文件,打开

按ESC键,以结束 仪器探头放置

电路图的仿真

电路图的仿真

4、运行仿真程序 执行PSpice/Run命令 屏幕上出现PSpice仿真分析窗口

电路图的仿真

仿真结果图

仿真波形测量

5、波形测量 执行Trace/Cursor/Display命令

仿真波形测量

仿真波形测量

➢ 点击分析窗口左下角“V(U1:OUT)” ➢ 执行Trace/Cursor/Peak命令,测量标尺定位于该波形

Place net name

放置分页图纸间的接口

原理图绘制

(二) 原理图绘制

以声控开关为例(电源是直流12V,负载为发光二极管)见下图:

放置集成块运放uA741

➢ 执行P1ace/Part命令 ➢ 在 “Libraries”列表框

中选择“OPAMP”库 ➢ 在 “Part”列表框中选

择“uA741” ➢ 单击“OK”

“ C” ➢ 单击“OK” ➢ 将电阻C移至合适位置,

(按键盘中的R键,器件旋 转)按鼠标左键放置

➢ 按ESC键(或鼠标右键点 end mode)结束绘制元器

放置二极管符号

➢ 执行P1ace/Part命令 ➢ 在 “Libraries”列表框中选

择“diode”库 ➢ 在 “Part”列表框中选择

在Create a New Project Using复选 框中选择Analog or Mixed-Signal Circuit 单击“OK”

实验仿真

出现”Create PSpice Project”对话窗口 选择”Create a blank proj”,然后点“OK”. 建立一个空项目。

实验仿真

“ R”,单击“OK” ➢ 将电阻R移至合适位置,

(按键盘中的R键,器件 旋转)按鼠标左键放置

➢ 按ESC键(或鼠标右键 点end mode)结束绘制 元器件状态

放置电容符号

➢ 执行P1ace/Part命令 ➢ 在 “Libraries”列表框中选

择“ANALOG” ➢ 在 “Part”列表框中选择

放置的器件如下图

元器件间的电连接

➢ 器件的移动:对准器件,点击鼠标左键,按住左键, 拖动鼠标到适合的位置。

➢ 器件的翻转,点中器件,按键盘上的“R”,或单击鼠 标的右键,点“Rotate”命令。

➢ 器件的删除,点中器件,按键盘上的删除键Delete ➢ 执行P1ace/Wire命令

将光标移至互连线的起始位置处,点击鼠标左键 移动鼠标,在互连线终点,单击鼠标左键进行连接 单击鼠标右键,选择End Wire子命令,结束互连线绘 制

放置地符号

➢ 执行P1ace/Ground命令 ➢ 在 “Libraries”列表框中

选择“SOURCE” ➢ 在 “Symbol”列表框中选

择“ 0/SOURCE” ➢ 单击“OK” ➢ 将地符号0 地移至合适位

置,按鼠标左键

➢ 按ESC键或鼠标右键点 end mode以结束绘制元 器件状态

原理图绘制

“ VDC” ➢ 单击“OK” ➢ 将直流源VDC移至合适

位置,按鼠标左键

➢ 按ESC键(或鼠标右键 点end mode)结束绘制 元器件状态

放置激励源符号

➢ 执行P1ace/Part命令 ➢ 在 “Libraries”列表框中

选择“SOURCE” ➢ 在 “Part”列表框中选择

“ VSIN”,或 “VPULSE”, 或“VPWL” ➢ 单击“OK” ➢ 将激励源移至合适位置, 按鼠标左键 ➢ 按ESC键或鼠标右键点 end mode以结束绘制元

印制版设计

(四)电路印制版电路版PCB板设计

一、快速穿越 Layout Plus

1. 生成Netlist 在Capture中的专案

管理视窗下(点File/项目名), 点击Tools>Creat Netlist…

印制版设计

生成Netlist

在Create Netlist 菜单栏下选Layout按下图选择,确定

Analog or Mixed-signal Circuit 本工程以后将进行数/模混合仿真 PC Board Wizard 本工程以后将用来进行印刷版图设计

Programmable Logic Wizard

本工程以后将用于可编程器件的设计(在 9.2版本已经不支持) Schematic 本工程只进行原理图设计

电路系统

计算机辅助设 计

准确、高效地设计电路

电子设计方法的发展

(1)传统的设计方法

焊接电路图—测试—修改电路—反复—确定—绘制印 制板图(绘图工具)—制作印制板(工艺流程)

“ D1N4002”,单击“OK” ➢ 将该二极管移至合适位置,

(按键盘中的R键,器件旋 转)按鼠标左键放置

➢ 按ESC键(或鼠标右键点 end mode)结束绘制元器 件状态

放置直流电源符号

➢ 执行P1ace/Part命令 ➢ 在 “Libraries”列表框中

选择“SOURCE” ➢ 在 “Part”列表框中选择

印制版设计

5、指定所要载入的纲路表档案(*.MNL), 点击生成的网络表文件,打开

印制版设计

6、生成电路板档案(*.max),在Save File As 菜单栏 内点保存

印制版设计

7、给你的器件查找并定义封装

Layout调入Netlist时,会自动运行AutoECO,检测Layout的 Library中是否有器件的封装,如果没有,您可以通过Link existing footprint to component来查找连接封装。如下所示:

器件封装调用

以这样的方式,直到把所有没有定义的管脚封装图在Link Footprint to Component 栏,点Link existing footprint to component查找出来

印制版设计

二、零件布局

调入网络表后,零件将随着纲路档案的载入而散布在 编辑区里,紧接着,依下列步骤进行自动零件布置: 1. 定义板框。首先切换到Global Layer层(按0键), 然后按钮,进入放置物件状态,再以画框的方式,直 接在编辑区里画板框。 2、 板框定义完成后,启动Auto>Place>Board命令, 程式即迅速布置零件。见下图

实验仿真

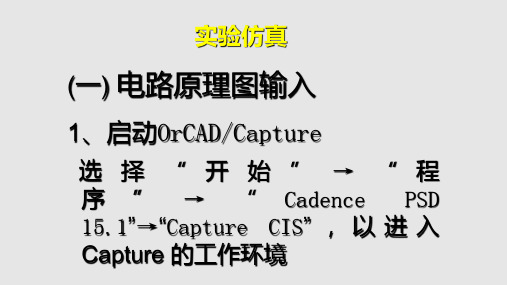

(一) 电路原理图输入

1、启动OrCAD/Capture

选择“开始”→“程 序 ” → “ Cadence PSD 15.1”→“Capture CIS” , 以 进 入 Capture 的工作环境

实验仿真

2、创建新项目

在菜单栏中选择file>new>Project

实验仿真

Name:键入项目名称,如 swth Location:点 Browse选择项目名 保存的路径,如 F:\mydesign Create a New Project Using: 工程项目后续处理功能选择:

印制版设计

印制版设计 三、自动布线

零件布置完成后,只要启动Auto>Autoroute>Board 命令,即可进行自动布线。

印制版设计

(四)、输出

Layout Plus的打印可分为校对用的打印印及精细的输出, 校对用的打印是将各板层重叠在一起打印输出,当我们要 进行叠印时,则File>Print/Plot启动命令,然后在随即出现 的对话盒中,选择打印选项,再按ok钮即可打印。 如果要进行精细的打印或分板层输出的话,则启动 Options> Post Process命令,然后在随即出现的表格中, 选择所要打印的板层,再点击鼠标右键,在弹出菜单中选 取其中的Plot to Print Manager命令,即可打印您选中的 板层。

➢ 将集成块移至合适位置, 按鼠标左键

➢ 按ESC键或鼠标右键点 end mode以结束绘制 元器件状态

器件放置

➢ 也可以按下步骤放置uA741:

➢ 执行P1ace/Part命令 ➢ 在 Part中输“ *741* ” , ➢ 点击Part Search, ➢ 点击Begin Search, ➢ 在Library 库中寻找到