PCB LAYOUT 布线设计注意要点

PCB布线设计的注意事项

PCB布线设计的注意事项在进行PCB(Printed Circuit Board)布线设计时,需要注意一些重要的事项,以确保电路板的性能和稳定性。

下面将列举一些在进行PCB布线设计时需要注意的要点。

首先,我们需要考虑信号线的路径和长度。

信号线应尽量避免直角折线,因为直角折线会导致信号的反射和干扰,影响电路的稳定性。

而且,信号线的长度也要尽量短,以减少信号传输时的延迟和失真。

要保持信号线的匹配阻抗,可以通过控制信号线的宽度和距离来实现。

其次,要合理安排电源和地线的布线。

电源线和地线应尽量平行布线,以减少相互干扰。

另外,电源和地线的布线也要尽量靠近负载器件,以减小电压降和电磁干扰。

要为不同的模拟和数字电路分开布线,以避免互相干扰。

在进行地线布线时,要尽量减少地线回流路径的长度,从而降低地线回流时的电感。

此外,在进行PCB布线设计时,还需要注意保持电路板的散热性能。

可以根据电路板上的热源分布,合理安排散热器件和通风孔的位置,在布线设计中留出足够的散热空间。

同时,要尽量避免散热器件和信号线之间的靠近,以减少散热器件对信号线的干扰。

另外,在PCB布线设计中,还要考虑EMI(Electromagnetic Interference)和ESD(Electrostatic Discharge)的问题。

为了防止电路板受到外部干扰或电击,可以采用屏蔽罩和防静电措施,同时在布线设计时留出足够的防护空间。

同时,还要注意采用合适的阻抗匹配技术,减少信号回返路径上的高频电磁干扰。

最后,PCB布线设计还需要考虑板上元件的布局。

元件的相互位置关系会影响电路的整体性能,因此在设计时要合理安排元件的位置和连接方式,以降低电路的复杂度和成本。

同时,还要考虑到布线的可维护性和排布的合理性,方便后续的检修和维护工作。

总之,PCB布线设计是电路设计中非常重要的一个环节,合理的布线设计可以提高电路的性能和稳定性,减少电磁干扰和信号失真。

通过遵循上述注意事项,可以有效提高PCB布线设计的质量和效率,确保电路板的可靠性和稳定性。

初学PCB Layout注意事项

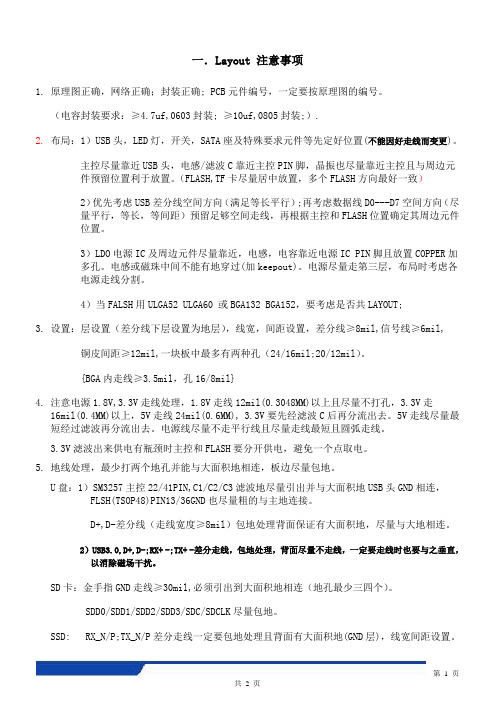

一.Layout 注意事项1.原理图正确,网络正确;封装正确; PCB元件编号,一定要按原理图的编号。

(电容封装要求:≥4.7uf,0603封装; ≥10uf,0805封装;).2.布局:1)USB头,LED灯,开关,SATA座及特殊要求元件等先定好位置(不能因好走线而变更)。

主控尽量靠近USB头,电感/滤波C靠近主控PIN脚,晶振也尽量靠近主控且与周边元件预留位置利于放置。

(FLASH,TF卡尽量居中放置,多个FLASH方向最好一致)2)优先考虑USB差分线空间方向(满足等长平行);再考虑数据线D0---D7空间方向(尽量平行,等长,等间距)预留足够空间走线,再根据主控和FLASH位置确定其周边元件位置。

3)LDO电源IC及周边元件尽量靠近,电感,电容靠近电源IC PIN脚且放置COPPER加多孔。

电感或磁珠中间不能有地穿过(加keepout)。

电源尽量走第三层,布局时考虑各电源走线分割。

4)当FALSH用ULGA52 ULGA60 或BGA132 BGA152,要考虑是否共LAYOUT;3.设置:层设置(差分线下层设置为地层),线宽,间距设置,差分线≥8mil,信号线≥6mil,铜皮间距≥12mi l,一块板中最多有两种孔(24/16mil;20/12mil)。

{BGA内走线≥3.5mil,孔16/8mil}4.注意电源1.8V,3.3V走线处理,1.8V走线12mil(0.3048MM)以上且尽量不打孔,3.3V走16mil(0.4MM)以上,5V走线24mil(0.6MM), 3.3V要先经滤波C后再分流出去。

5V走线尽量最短经过滤波再分流出去。

电源线尽量不走平行线且尽量走线最短且圆弧走线。

3.3V滤波出来供电有瓶颈时主控和FLASH要分开供电,避免一个点取电。

5.地线处理,最少打两个地孔并能与大面积地相连,板边尽量包地。

U盘:1)SM3257主控22/41PIN,C1/C2/C3滤波地尽量引出并与大面积地USB头GND相连,FLSH(TSOP48)PIN13/36GND也尽量粗的与主地连接。

PCB layout布线注意的问题

在PCB设计中,布线是完成产品设计的重要步骤,可以说前面的准备工作都是为它而做的,在整个PCB中,以布线的设计过程限定最高,技巧最细、工作量最大。

PCB布线有单面布线、双面布线及多层布线。

布线的方式也有两种:自动布线及交互式布线,在自动布线之前,可以用交互式预先对要求比较严格的线进行布线,输入端与输出端的边线应避免相邻平行,以免产生反射干扰。

必要时应加地线隔离,两相邻层的布线要互相垂直,平行容易产生寄生耦合。

自动布线的布通率,依赖于良好的布局,布线规则可以预先设定,包括走线的弯曲次数、导通孔的数目、步进的数目等。

一般先进行探索式布经线,快速地把短线连通,然后进行迷宫式布线,先把要布的连线进行全局的布线路径优化,它可以根据需要断开已布的线。

并试着重新再布线,以改进总体效果。

对目前高密度的PCB设计已感觉到贯通孔不太适应了,它浪费了许多宝贵的布线通道,为解决这一矛盾,出现了盲孔和埋孔技术,它不仅完成了导通孔的作用,还省出许多布线通道使布线过程完成得更加方便,更加流畅,更为完善,PCB 板的设计过程是一个复杂而又简单的过程,要想很好地掌握它,还需广大电子工程设计人员去自已体会,才能得到其中的真谛。

1. 电源、地线的处理既使在整个PCB板中的布线完成得都很好,但由于电源、地线的考虑不周到而引起的干扰,会使产品的性能下降,有时甚至影响到产品的成功率。

所以对电、地线的布线要认真对待,把电、地线所产生的噪音干扰降到最低限度,以保证产品的质量。

对每个从事电子产品设计的工程人员来说都明白地线与电源线之间噪音所产生的原因,现只对降低式抑制噪音作以表述:众所周知的是在电源、地线之间加上去耦电容。

尽量加宽电源、地线宽度,最好是地线比电源线宽,它们的关系是:地线>电源线>信号线,通常信号线宽为:0.2~0.3mm,最经细宽度可达0.05~0.07mm,电源线为1.2~2.5 mm对数字电路的PCB可用宽的地导线组成一个回路, 即构成一个地网来使用(模拟电路的地不能这样使用) 用大面积铜层作地线用,在印制板上把没被用上的地方都与地相连接作为地线用。

在手机PCB Layout中布线要注意哪些事项

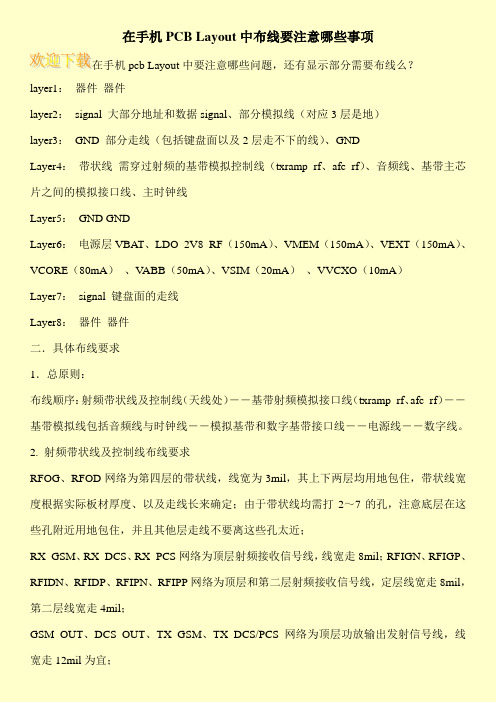

在手机PCB Layout中布线要注意哪些事项在手机pcb Layout中要注意哪些问题,还有显示部分需要布线么?layer1:器件器件layer2:signal 大部分地址和数据signal、部分模拟线(对应3层是地)layer3:GND 部分走线(包括键盘面以及2层走不下的线)、GNDLayer4:带状线需穿过射频的基带模拟控制线(txramp_rf、afc_rf)、音频线、基带主芯片之间的模拟接口线、主时钟线Layer5:GND GNDLayer6:电源层VBAT、LDO_2V8_RF(150mA)、VMEM(150mA)、VEXT(150mA)、VCORE(80mA)、V ABB(50mA)、VSIM(20mA)、VVCXO(10mA)Layer7:signal 键盘面的走线Layer8:器件器件二.具体布线要求1.总原则:布线顺序:射频带状线及控制线(天线处)――基带射频模拟接口线(txramp_rf、afc_rf)――基带模拟线包括音频线与时钟线――模拟基带和数字基带接口线――电源线――数字线。

2. 射频带状线及控制线布线要求RFOG、RFOD网络为第四层的带状线,线宽为3mil,其上下两层均用地包住,带状线宽度根据实际板材厚度、以及走线长来确定;由于带状线均需打2~7的孔,注意底层在这些孔附近用地包住,并且其他层走线不要离这些孔太近;RX_GSM、RX_DCS、RX_PCS网络为顶层射频接收信号线,线宽走8mil;RFIGN、RFIGP、RFIDN、RFIDP、RFIPN、RFIPP网络为顶层和第二层射频接收信号线,定层线宽走8mil,第二层线宽走4mil;GSM_OUT、DCS_OUT、TX_GSM、TX_DCS/PCS网络为顶层功放输出发射信号线,线宽走12mil为宜;。

PCB布线的技巧及注意事项

PCB布线的技巧及注意事项布线技巧:1.确定电路结构:在布线之前,需要先确定电路结构。

将电路分成模拟、数字和电源部分,然后分别布线。

这样可以减少干扰和交叉耦合。

2.分区布线:将电路分成不同的区域进行布线,每个区域都有自己的电源和地线。

这可以减少干扰和噪声,提高信号完整性。

3.高频和低频信号分离:将高频和低频信号分开布线,避免相互干扰。

可以通过设立地板隔离和电源隔离来降低电磁干扰。

4.绕规则:维持布线规则,如保持电流回路的闭合、尽量避免导线交叉、保持电线夹角90度等。

这样可以减少丢失信号和干扰。

5.简化布线:简化布线路径,尽量缩短导线长度。

短导线可以减少信号传输延迟,并提高电路稳定性。

6.差分线布线:对于高速信号和差分信号,应该采用差分线布线。

差分线布线可以减少信号的传输损耗和干扰。

7.用地平面:在PCB设计中,应该用地平面层绕过整个电路板。

地平面可以提供一个低阻抗回路,减少对地回路电流的干扰。

8.参考层对称布线:如果PCB板有多层,应该选择参考层对称布线。

参考层对称布线可以减少干扰,并提高信号完整性。

注意事项:1.信号/电源分离:要避免信号线与电源线共享同一层,以减少互相干扰。

2.减小射频干扰:布线时要特别注意射频信号传输的地方,采取屏蔽措施,如避免长线路、使用高频宽接地等。

3.避免过长接口线:如果接口线过长,则信号传输时间会增加,可能导致原始信号失真。

4.避免过短导线:过短的导线也可能引发一些问题,如噪声、串扰等。

通常导线长度至少应该为信号上升时间的三分之一5.接地技巧:为了减少地回路的电流噪声,应该尽量缩短接地回路路径,并通过增加地线来提高接地效果。

6.隔离高压部分:对于高压电路,应该采取隔离措施,避免对其他电路产生干扰和损坏。

7.注重信号完整性:对于高速和差分信号,应该特别注重信号完整性。

可以采用阻抗匹配和差分线布线等技术来提高信号传输的稳定性。

总结起来,PCB布线需要遵循一些基本原则,如简化布线、分区布线、差分线布线等,同时需要注意电源和信号的分离、射频干扰的减小等问题。

pcb布局布线技巧及原则

PCB布局布线技巧及原则1. 引言PCB(Printed Circuit Board)布局布线是电子产品设计中至关重要的一步。

良好的布局布线能够确保电路的可靠性、性能和EMI (Electromagnetic Interference)抗干扰能力。

本文将介绍一些常见的PCB布局布线技巧及原则,帮助读者更好地进行电路设计和布线。

2. PCB布局技巧2.1 分区布局在设计复杂的电路板时,将电路板分为几个功能区域进行布局是一个很好的策略。

例如,将微处理器、模拟电路和电源电路分开布局。

这可以降低信号干扰,并更好地管理电源分配和地平面。

2.2 复用层对于多层PCB设计,可以使用复用层的技术来提高布局效率。

复用层是指多个分区共享同一个地平面或电源平面。

这样做可以减少电路板的层数,提高信号完整性和EMI性能。

2.3 阻抗控制在高速设计中,阻抗控制是非常重要的。

通过合理设计走线宽度、间距和层间距,可以实现所需的阻抗匹配。

使用阻抗控制工具进行模拟和仿真分析,以确保信号完整性。

2.4 时钟信号布局时钟信号在高速电子系统中非常关键。

为了降低时钟抖动和噪声,应优先布置时钟信号线。

时钟信号线应尽量短、直接,并与其他信号线保持一定的距离以减少干扰。

2.5 地平面和电源分布良好的地平面和电源分布可以大大改善电路性能和抗干扰能力。

地平面应尽量连续、整齐,并尽可能地覆盖整个PCB区域。

电源分布应合理,避免共享电流,以减少电源波动。

3. PCB布线原则3.1 追求最短和最直接的路径布线时应尽量追求最短和最直接的路径,以降低传输延迟和信号损失。

避免走线过长或弯曲,特别是对于高速信号和时钟信号。

3.2 避免平行和交叉在布线过程中,应尽量避免平行和交叉走线。

平行走线容易引起串扰干扰,而交叉走线则易引起交互耦合。

合理规划走线,尽量平行走线和交叉垂直走线。

3.3 差分信号布线对于高速差分信号,应采用差分布线技术。

差分信号的两条传输线上的信号互为补码,可以大大减小对外部干扰的敏感度。

PCB板布局布线基本规则

PCB板布局布线基本规则PCB(Printed Circuit Board,印刷电路板)布局布线是电子产品设计中非常重要的一步,它决定了电路板的性能和可靠性。

下面将介绍一些PCB板布局布线的基本规则。

1.尽量规划好电路板的整体布局。

合理的整体布局可以降低电磁干扰和噪声,提高信号的可靠性。

布局过程中,需要考虑各个电路模块的电源分布、信号线的走向和电路板边缘的保留空间等因素。

2.尽量减少信号线的长度。

信号线过长会引起信号衰减、时钟偏差和串扰等问题。

因此,应尽量减少长距离信号线的使用,并将不同功能模块的信号线放在靠近彼此的位置,以缩短线路长度。

3.引脚布局要合理。

电路板上的引脚布局应遵循一定的规则,如相同功能的引脚应该靠近彼此,避免交叉连接;高频信号线和低频信号线应分开布局,以防止互相干扰;输入和输出信号一般不要使用同一个引脚。

4.电源和地线的布局要合理。

电源和地线是电路工作的基础,其布局质量直接影响整体性能。

应尽量减少电源和地线的长度,避免共享电源或地线的引脚。

此外,电源和地线的宽度也要足够,以满足电流的要求。

5.差分线路应尽量成对布线。

差分信号线路通常由两根线组成,它们相互平行,保持相同的长度和间距。

这种布线方式可以减小干扰并提高抗干扰能力。

6.避免使用尖锐的角度和过窄的宽度。

锐角和过窄的线路会增加信号的传输损耗,并增加线路的阻抗。

在布局和布线过程中,应尽量避免生成锐角,选择合适的宽度。

7.需要进行地线屏蔽的信号要有相应的地线屏蔽层。

一些对干扰非常敏感的信号线,如高频信号线和时钟信号线,需要有地线屏蔽层进行保护,防止外界干扰。

8.PCB板的散热设计。

在布局布线过程中,需要考虑板上发热器件的散热问题。

可以尽量将发热器件靠近PCB板的边缘,以方便散热或使用附加的散热设计。

9.电路板边缘的保留空间。

为了使电路板在安装时能够与其他组件或设备连接,需要在板的边缘预留一定的空间。

这个空间通常被称为边际空间,用于放置连接器、插座等。

PCBLAYOUT设计规范

PCBLAYOUT设计规范PCB(Printed Circuit Board)是电子产品的核心组件之一,决定了电路设计的可靠性和性能。

良好的PCB布局设计可以降低电路噪声、提高信号完整性,并且方便后续的组装和维修。

以下是PCB布局设计的一些规范和建议:1.尺寸和形状规范:根据具体应用需求确定PCB板的尺寸和形状。

在选择尺寸时要考虑电路的复杂性和器件的布局。

广泛使用的尺寸为贴片型器件的长度加上两倍的元件间距。

2.组件布局规范:将元件分为功能模块,并合理安排它们的位置,以降低电路的互相干扰。

尽量将高频、噪声源放置在一起,并且与敏感信号的路径保持一定的距离。

3.走线规范:为了提高信号完整性,收集和地线走线应尽量平行运行。

重点信号线应保持足够的间距。

避免过于细长的路径和尖锐的弯曲,以减少信号反射和耦合。

4.功率平面和地面规范:为了提供稳定的供电和减少噪声,设计时需要规划功率平面和地面。

功率平面应该贴近电源引脚,且尽量大且连续。

地面应尽量覆盖整个PCB板,且与其他层相连。

5.元件引脚排布规范:元件引脚的排布应该尽量规整,方便焊接和组装。

相同类型的引脚应按照相同的方向排列。

供电和地线引脚应靠近一起,以减少线路长度和电磁干扰。

6.保持合理的间距:线与线、线与元件之间应保持合适的间距,以避免突然放电和相互干扰。

7.考虑热设计:对于功耗较大的元件,应考虑散热设计。

可以使用散热器或合理的布局来进行热扩散。

8.通过规范:为了提高布局的可维护性,设置适当的通过或测试点。

这有助于后续的调试和维修。

9.引入尽可能多的阻尼电容:引入阻尼电容可以帮助减少电源线噪声和抑制瞬态响应。

10.使用模块化设计:基于较小的模块进行设计,有助于封装、修改和重用。

这样可以提高开发效率和产品可维护性。

总之,良好的PCB布局设计对电路性能的稳定性和可靠性至关重要。

通过遵循上述规范和建议,可以降低电磁干扰、提高信号完整性,并且简化后续的组装和维护工作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Resonator

Non-critical

Low current drive circuit

3. For some very sensitive analog circuit, keep its power supply separated from other digital circuit/noisy circuit will be very important

Page � 5

电源布局的树状结构

Never let high current / noisy power supply connect to and pass through low current / sensitive power supply.

Sensitive low current

Microcontroller 1. Reset circuit shall be placed very close to microcontroller, no other current pass through reset power supply 2. Resonator GND should only connect to microcontroller Analog circuit Reset

General purpose logic circuit Connector High current drive circuit

Noisy High current

Analog circuit Critical

Page � 6

Power supply

芯片电源的去耦电容

去耦电容应该和芯片的电源 /地保持最小电气回路长度

Some part, such as tact switch, is very sensitive to PCB flatness, shall be place close to supporting structure. PCB flatness could change over time.

Need some space around connector for finger to plug/unplug connector

数码管、板边等

受力敏感型器件,如按键、液晶、晶振、较大的芯片或单方向本体长度较长且对板子变形敏感的器件

等

Page � 3

Heavy part screw Stanchion PCB

Heavy part (such as transformer) shall be placed close to mounting screw or some other structure which can provide supporting

�

�

�

�

�

�

Page � 2

整体布局中的机械应力考虑

在布板的时候应该充分考虑生产、安装、运输、使用、维护过程中可能受到的应力 ,并采取适当的措施。器件包括但不限于:

重型元器件,如变压器、散热器等

在生产、安装、维修、使用过程中需要较大受力的器件 ,如接插件及带有接插件的

器件,线束等

在生产、安装、维修、使用过程中可能受力的器件 ,如高度较高的电解电容、蜂鸣器、

Vcc GND Bulk cap decoupling cap

Solution C (good): Each IC has its bypass cap very close to it with short return loop. This is good for pure logic circuit, which don’t have high peak current on DC bus.

√

VCC GND

DC supply storage cap

Filter cap for sensitive circuit

×

VCC GND Sensitive circuit (Micro, sensor…) Noisy circuit (Relay drive, motor drive…)

Sensitive circuit (Micro, sensor…)

Solution A (good): Each IC has its bypass cap very close to it with short return loop. A bulk cap may need if high peak current present on DC bus on followed IC/circuit.

(1) High current / “noisy” GND trace (such as GND path on the relay drive circuit, DC fan drive) must be directly connected to DC power supply output, or before main microprocessor capacitor bank used charge storage and filtering. (2) High current / noisy GND traces should not connect to GND trace behind main capacitor bank used for charge storage and filtering for sensitive circuits (like microprocessor core).

Solution B (good): Each IC has its bypass cap very close to it with short return loop. A bulk cap is placed at the joint point of different circuits. It will be helpful to insulate coupling between two/multiple its.

Storage cap for sensitive circuit

Noisy circuit (Relay drive, motor drive…)

Noisy VCC/GND

Clean VCC/GND

Page � 9

Noise

晶振、陶振电路

该电路及其敏感,并且会导致较为严重后果,一定要谨慎

Microprocessor Clock:

If not, PCB could be damaged during shipping, assembly or normal operation. Since component has more movement rather than it is placed close to mounting support structure, components is much easy fall out.

Gap increased due to PCB flatness change, but not too much Gap increased due to PCB flatness change, out of limit

Force

Some part is not heavy, but may introduce high push/pull force during assembly, such as connector, also shall be placed close to supporting structure

LAYOUT 设计提示

低速小功率电路,单面/双面板

团队的协作

LAYOUT 是团队合作的成果 谁是设计者

�

硬件工程师及其设计审核者应该对原理图的正确 性负责。要保证提供给 LAYOUT专员的图纸是正 确有效的。 LAYOUT专员对通用型工艺性负责。 应保证 LAYOUT符合相应的生产工艺要求 ,互相 硬件工程师和LAYOUT专员应该密切配合 专员应该密切配合, 发现问题,共同解决问题。 应该始终保持设计的严谨性。 应该通过分析计算 将问题尽量在做板之前解决掉,尽量减少对样板 的依赖。应建立健全设计规范,并有效执行规范。 减少随机性设计失误。提高设计质量的一致性。 。两 应保证原理图和 LAYOUT的一致性和同步性 的一致性和同步性。 者应使用相同的软件, LAYOUT必须基于源自于 原理图的网络表。一般应保证跳线两端的网络一 致。 关键性的LAYOUT设计要求应该在原理图或原理 图附件上明确标示, 以便保证相关要求能够在后 续的设计变更中依旧得到执行,并成为关键 LAYOUT检查的条款。 应设置合理的规则器,并充分利用软件的规则器 进行自动检查,严格消除不合格项。