TI锂电池均衡电路开发板电路图bq76PL536EVM-3

BQ76PL536EVM-3;中文规格书,Datasheet资料

User's GuideSLUU437B–October2010–Revised May2011bq76PL536EVM Quick Start Guide1ScopeThis document covers the initial connection and installation of the Texas Instruments bq76PL536Evaluation Module(EVM),supplied in kit form including the EVM board,the Aardvark USB-SPI adapter, and connectors to make cells-to-EVM connection.It is not meant as a comprehensive guide to using the '536integrated circuit and its'features.See the device data sheet for details(SLUSA08).2Software Installation2.1PC Requirements1.Pentium1.66GHz(Core™2or better recommended)2.Windows-XP™SP2(software has not been tested with Windows Vista™/Win7)™2.0or later,with updates4.Available USB powered-port(hub OK if wall adapter used)2.2Installing the Aardvark DriverCAUTIONThe Aardvark driver must be installed before attaching the adapter for the firsttime.The Aardvark driver should be installed prior to installing the TI supplied bq76PL536Evaluation software.From the CD-ROM,run the file"/Tools/Aardvark/Drivers/TotalPhaseUSB-v2.xx.exe"to install the drivers.If prompted to do so,plug in the Aardvark to an available USB port using the supplied cable.The port must be a powered-port,typically directly from a e of a USB non-powered hub may not provide sufficient operating current for the Aardvark or EVM to operate correctly.2.3Installing the bq76PL536Evaluation SoftwareFrom the CD-ROM,run the file"/Software/bq76PL536Evaluation Software x_x_x.msi"to install,where the "x_x_x"is replaced by the current build number.Installation is automatic.This installs the GUI(Graphical User Interface)software for Windows.As new versions are released,they may be installed over theexisting version.Windows-XP,Windows Vista are trademarks of Microsoft Corporation.All other trademarks are the property of their respective owners.EVM Assembly and Configuration 3EVM Assembly and Configuration3.1Configure the Isolated Communications Interface3.1.15V vs3.3V SelectionIn the ISO-COMMS section of the PCB,there are two jumpers.JP5selects5V or3.3V I/O operationacross the isolation boundary.The Aardvark adapter supplied with the EVM uses3.3V logic,but is5Vtolerant.JP5should be configured for3.3V operation with the supplied Aardvark interface adapter,although either position will work correctly.For connection to a user supplied microcontroller,select the appropriate voltage.3.1.2Use USB Power from AardvarkJP1selects power from the USB connection through the Aardvark when installed in the“USB”position. 3.2Configure the EVM board3.2.1Use with CellsRemove jumpers JP1-18(18)located near the black battery connectors P1-P3to reduce the current draw of the board.It is OK to leave the jumpers in place;they connect a1K precision resistor between each adjacent pair of cell inputs and are supplied to use the EVM with power supplies in place of cells(see the Use with~12-26VDC Power Supply).Connect cells to the supplied mating connectors with screw terminals BEFORE plugging the connector into the EVM at P1,the large black connector on the left edge of the board.The most negative cellconnects to the most bottom of the black connector(P1).The bottom-most pin of the battery connector is the most negative connection to the board from thebattery stack.This is the negative end of cell1.The next pin up the connector is the positive end of cell1 (and the negative end of cell2).The connections proceed in this fashion up the connector to pin7,which is the most positive voltage from the battery stack connected to each IC.Pin7of P1(P1.7)is connected to P2.1on the board.The same is true of P2.7and P3.1.P3.7is connected to the top of the PCB(most positive voltage),while P1.1is connected to the bottom of the PCB(most negative voltage).The battery connections should be made secure,a loose connection may result in device destruction.Ideally,the cells are connected to one another by secure means such as welding,and only tap points are brought over to the EVM from each cell-to-cell interconnection.Although the device is immune to the effects of a random connection sequence,the ideal connectionsequence is from pin P1.1to pin3.7in order.TI recommends that users unfamiliar with the EVM and/or li-ion cells begin by using power supplies as outlined in the next section. EVM Assembly and Configuration 3.2.2Use with~12-26VDC Power SupplyImportant:Install jumpers JP1-18(18)located near the black battery connectors P1-P3before connecting power supplies.These jumpers connect a precision0.1%resistor divider network between cellconnections.Connect an appropriate power supply capable of supplying12-26VDC to connector P1,then plug P1into the EVM connector.Any voltage which meets the IC requirements will work,18-24V is typical of mostsix-cell systems.Plug additional supplies into P2and P3.The supplies must be isolated from each other and from earth ground to avoid unintentional short circuits.A separate supply is required for each IC (each cell-connection plug).The supply negative connection is made to pin1of the mating connector,the pin that will connect to the bottom-most pin of the mating connector.The positive connection is made to pin7,the top-most on the connector.It is not necessary to connect to the intermediate pins due to the resistive divider on the EVM which was enabled when JP1-18were installedCAUTIONDo not remove any of the jumpers JP1-18while using the EVM in thisconfiguration.Lethal DC voltages may be present for these configurations.Contact with these voltages may result in serious injury or eappropriate safety precautions.(+)and (–)outputsmust remain isolatedfrom earth ground.EVM Assembly and ConfigurationFigure 1.Correct Connection of Three ~20V Power Supplies to EVMFigure 2.Alternate Connection for Single 54V SupplyEVM Assembly and Configuration Figure 3.Incorrect Connections,Base IC Not PoweredFigure 4.Incorrect Connections,Insufficient V BAT Per ICFigure 5.Incorrect Connections,Top IC Not Powered,IC1,2Insufficient V BATConnecting the EVM 3.3Non-Critical Hardware Testing or Firmware Development3.3.1Stacking EVMsFor casual testing,one or two devices may be powered(in order from negative to positive)in lieu ofpowering all3devices.Due to poor termination of the unpowered devices in this configuration,detailed testing or critical hardware evaluations should not be undertaken.Any odd behavior or unexpected fault conditions should be ignored until verified with the EVM correctly powered by three isolated supplies4Connecting the EVM4.1Connection OrderFigure6.Bq76pl536EVM-3(a)Configure the EVM jumpers per Section3.1.(b)Connect the EVM to the Power Supplies or cells,turn on the supplies at~12to24V is recommended.The Absolute Maximum voltage per IC is36V and should not be exceeded,30V is the recommendedmaximum continuous voltage.(c)Connect the USB cable to the Aardvark and your PC.(d)Connect the Aardvark ribbon cable to the10pin header on the EVM boardThe Aardvark adapter should be connected last during power-up,and disconnected first whenpowering down.If not using the wall adapter to supply power,it must be after starting the Windowsapplication to avoid a turn-on issue with the Aardvark adapter.Many laptop computers power off theirUSB ports when they go into sleep,standby,or hibernate modes.If the device the Aardvark isconnected to remains powered when this happens,the Aardvark may suffer permanent damage.(e)Start the WinGUI User Interface software supplied with the EVM and installed earlier4.2Connection NotesThe ISO-COMMS section of the EVM board isolates the EVM side voltages completely from the PC side.It isolates all power,ground,and signal lines to the EVM.Caution must still be carefully taken when using the EVM as part of a stack,where lethal voltages may be present.The galvanic isolation provided by the ISO-COMMS section does not eliminate the need for safe handling procedures,proper High-Voltageequipment and protective clothing.Proper safety procedures should always be followed. Evaluation Software Details Because the ISO-COMMS circuit section fully isolates the PC,Aardvark,and wall adapter from the EVM “battery”side,the Aardvark is insensitive to the powering of the EVM,which receives its’power from the battery cells or power supply used for evaluation.The grounds(VSS)are fully isolated;please keep this in mind when using an oscilloscope or meter.Do not inadvertently connect the EVM VSS to the PC/Aardvark VSS by connecting two probe grounds orotherwise forming a ground loop through external wiring,including the building wiring.4.3Quick CheckThe first step in communicating with the bq76PL536is to set a unique address for each device in thestack.This is required even if you are only using a single device.This occurs automatically when theEvaluation software is first started.To do this manually,select COMMAND|AUTO ADDRESS(shortcut key CTRL+A).This will cause the software to interrogate the stack of‘536devices,find all availabledevices,and assign each a unique address beginning with address0x01.Address0x00is reserved for un-addressed devices.After addressing is complete,you should see the number of devices found and the total combined voltage of all cells being monitoring displayed in the STACK HEIGHT and V STACK windows.5Evaluation Software Details5.1Main ScreenThe main screen is divided into4major areas,plus the menu and status bars.The software is referred to as the“Windows Graphical User Interface”,or abbreviated to WinGUI.VBRIC K The voltage measured by the bq76PL536between the BATx and VSS pinsVCELLn the voltage measured between the pair of pins VCn–VCn-1(i.e.VCELL2=VC2-VC1).ADDR displays the address of the device being monitored in the measurement result area.LOG DEVICE Checking this box will add the contents of the device at this address to the log file.TSn The voltage measured between the TSn+and TSn-inputs,converted by the WinGUIto temperature based on the characteristics of the thermistor used in the EVM design.The EVM and WinGUI are configured to measure this voltage as a ratio of REG50,which removes any offset or gain errors introduced by drift in the REG50output.VIEW AS...Shows the ratio of the measured input voltage to REG50as a percentage.Evaluation Software Details Updates the displayed measurements for this device.The conversion is started bysending the register command CONVERT[CONV]=1,or hardware by toggling the CONV pin if the HW IO CONTROL box is checked.5.1.1Volatile RAM Configuration Registers–The lower half of this area displays the volatile configuration registers shown as bit fields,see thebq76PL536data sheet for details on programming these registers.These registers display green for logic 0,and orange for logic1.The two states may be toggled between by left-clicking on the bitThe STATUS,COV_FAULT,and CUV_FAULT bits are either white(logic0)or red(logic1)for asserted.In most cases,the asserted state indicates an error condition sensed by the bq76PL536.To clear a fault,first remove the physical condition causing the fault,then click on the ALERT or FAULT bit to reset the state of the bit.This writes a1to the bit,followed by a0,which is the device’s method for clearing the asserted bit state back to logic0.5.1.2Group-3Protected Registers–The device is provided with many configuration options set by bits contained in a special set of registers protected against accidental writing.These RAM registers are initialized from OTP(One-TimeProgrammable)EPROM cells.The device is shipped with these EPROM locations un-programmed(blank).The Windows GUI interface hides the un-programmed nature of the device by setting defaults in the registers cells when the Evaluation software starts(this can be defeated by setting the TOOLS|OPTIONS defaults).The last settings are also automatically saved by the GUI and restored on next use.These features are provided for ease of use,and are implemented solely in the ers areresponsible for programming OTP bits in parts correctly during manufacturing for correct operationin-circuit.Some Group-3registers are shown as registers at the bottom of the left side of the screen,the others in the top right section of the screen as listboxes and registers5.1.3Quick AccessThe Quick Access register(s)provide R/W access to any location in the part.They are named arbitrarily in the GUI‘X’,‘Y’,and‘Z’–there are no XYZ registers in the part.Some registers,such as the MASTER register require multi-byte writes to“unlock”the target register for writing.To accomplish this,program the X register address/data with the first unlock key,the Y register with the second unlock key,and finally the Z register with the target address and data.Then use the“write all”button to send all three address/data bytes in the correct order and timing to accomplish the multi-byte write.(This is done automatically when using the Protected Registers window.)5.1.4LED Status IndicatorsAt the top right of the user interface screen are8status indicator"LED's".These provide a quick view of the status of the devices,and the interface,cable connections,etc.Green normally indicates a logic0condition,and red a logic one condition.Gray indicates undefined. Evaluation Software Details ALERT A condition has been sensed that is causing the ALERT hardware pin to be asserted.This is also indicated by the ALERT bit being set(red)in the[DEVICE]STATUS register.Thesource of the ALERT condition is indicated in the ALERT register just below the STATUSregister.FAULT Similar to the ALERT indicator,this LED indicates the FAULT bit,and FAULT hardware pin are asserted.The source is indicated in the FAULT register,just below the ALERTregister.LAST CRC The last CRC received by the GUI was incorrect for the contents of the packet.Thisusually indicates a communications error caused by improper connection,excessivecabling,etc.The cause of the communications error should be corrected beforecontinuing.LOG Green if a log file is being written to.Logging is useful to capture information about cell or interface behavior over long periods of timeSTACK At least one device was found during auto-addressing or rebuild addresses.This indicates that the bottom device in the stack was found,is powered,not in POR,and the ribboncable from the Aardvark to the EVM is connected correctly.This verifies the cabling andconnection all the way to the IC.INTERFACE The Aardvark USB-SPI interface adapter was successfully found and communicated with.This verifies the cabling and driver to the adapter.5.1.5Global RegistersDEVICE The Address of the device currently being communicated with.Change to accessdifferent devices in the stack.“BROADCAST”mode also available to send a singlecommand to all devices in the stack.(In BROADCAST mode,no data is shown–theinterface can only display data from one device at a time.STACK HT.The number of devices found during the last AUTO-ADDRESS orREBUILD-ADDRESS cycle.POLL Check or un-check this box to turn polling on or off.Note that many menu items areunavailable during polling–turn polling off to access them.RATE This list box allows choosing a polling rate between100ms and60s.The LEDilluminates green each time the GUI polls the device eful as a heartbeatindicator when polling or logging is active.A setting“Fast”is also available.In thisposition,the WinGUI will poll as fast as possible,with only Windows OS slowing itdown.On most systems,this results in a poll every10-20ms,but your results may varydepending on the speed of your CPU and other tasks that are running.LOG STACK Enables or disables data logging.Logging is to a file in comma-separated-values(.csv) format.Set up logging in the LOG|SETUP menu.Logging may also be started/stopped under the LOG menu.Data is captured each poll,set by the polling interval inTOOLS|INTERFACE.VIEW PLOT Check this box to view a dynamic plot of data collected during polling.See PLOTTING for further information on configuring the plotter.Evaluation Software Details HW I/O Check this box to force the Evaluation software to use the hardware pins CONV andDRDY to initiate,and monitor ADC conversion cycles,instead of sending commands tothe CONVERT_CTRL[CONV]register bit.Similarly,it is monitoring the FAULT andALERT hardware pin states to determine a FAULT and/or ALERT condition beingpresent.Note that in HW I/O mode,the REFRESH button toggles the hardware CONVline,but the user may optionally use the CONVERT_CTRL[CONV]bit to force softwareinitiated conversions by clicking on the bit.5.2AddressingThe first step in communicating with thebq76PL536is to set a unique address for eachdevice in the stack.This is required even if you areonly using a single device.On the menu,selectCOMMAND|AUTO ADDRESS(shortcut key CTRL+A).This will cause the software to interrogate thestack of'536devices,find all available devices,andassign each a unique address beginning withaddress0x01.Address0x00is reserved forun-addressed devices.After addressing is complete,the number ofdevices found and the total combined voltage of allcells being monitoring are displayed in the STACKHEIGHT and V STACK windows.In this example,2bq76PL536devices are connected togethermonitoring12cells of about3.3V each.The screen automatically refreshes each time something changes.Addressing the device will cause all displayed values and registers to update.The user hould see all cell voltages displayed,along withregisters showing FAULT and ALERT status,DEVICE STATUS,etc.5.3Menus and Commands5.3.1File MenuThis menu provides a way to save complex registersettings between sessions.The settings are savedto a file on the local disk,selected using a dialogbox that appears when the Load or Save commandis selected.Multiple files,with different settings maybe saved under different file names.Saved registersettings are then re-loaded from the saved file.Allregisters–volatile and shadow–are saved orloaded,except the ADC measurementsAnother useful command available in this menu allows copying the current measurement data(VCn,VBRICK,and TS1,TS2,in that order)to the clipboard,and subsequent copying to a document orspreadsheet.measurements.It will also create Eprom programmable image for Bq76PL536OTP EPROM Programmer分销商库存信息: TIBQ76PL536EVM-3。

锂电池保护与均衡

单节锂电池的保护与均衡

下面是单节锂电池的保护和均衡线路

保护线路

上图为单节锂电池的过充电压和过放电压保护线路部分

1.过放电压保护

正常放电过程中,锂电池保护IC(IC1)的PIN 1 输出电压为电池电压,当电池电压低于设定的过放电压保护点的时候,PIN 1输出为0,此时将使Q2导通,再使Q3导通。

从而使Signal 2 信号为0,并发送信号关断门口MOSFET,达到保护作用。

2.过充电压保护

正常充电过程中,锂电池保护IC(IC1)的PIN 3 输出电压为电池电压,当电池电压高于设定的过充电压保护点的时候,PIN 3 输出为0,此时将使Q1导通,再使Q4导通。

从而使Signal 1 信号为0,并发送信号关断门口MOSFET,达到保护作用。

均衡线路

上图为单节锂电池的均衡线路部分

均衡只有在充电过程中才会有。

(如想在放电过程中加入均衡,需加入CPU控制)

正常充电过程中,当电池电压到达设定的均衡电压点的时候,A点的电压将为2.5V,导致TL431导通。

TL431导通后,将使Q2、Q3(功率晶体管)导通。

当Q2导通后,由于有充电信号Signal 1 在,将有电压送进来,使B点电压抬升;而Q2导通前,由于B点电压被嵌死,故Signal 1 信号不会对此有影响。

B点电压抬升后,Q4导通,Signal 2 信号回送给充电器,要求关机,充电就会结束。

注:B点电压必须在每颗电池电压均达到均衡电压点的时候,才会被抬升,否则只要有一节电池还没开始均衡,B点电压就会始终被嵌死。

锂电池充电电路图(DOC)

锂电池充电电路图2009-03-08 18:26锂电池是继镍镉、镍氢电池之后,可充电电池家族中的佼佼者.锂离子电池以其优良的特性,被广泛应用于: 手机、摄录像机、笔记本电脑、无绳电话、电动工具、遥控或电动玩具、照相机等便携式电子设备中。

一、锂电池与镍镉、镍氢可充电池:锂离子电池的负极为石墨晶体,正极通常为二氧化锂。

充电时锂离子由正极向负极运动而嵌入石墨层中。

放电时,锂离子从石墨晶体内负极表面脱离移向正极。

所以,在该电池充放电过程中锂总是以锂离子形态出现,而不是以金属锂的形态出现。

因而这种电池叫做锂离子电池,简称锂电池。

锂电池具有:体积小、容量大、重量轻、无污染、单节电压高、自放电率低、电池循环次数多等优点,但价格较贵。

镍镉电池因容量低,自放电严重,且对环境有污染,正逐步被淘汰。

镍氢电池具有较高的性能价格比,且不污染环境,但单体电压只有1.2V,因而在使用范围上受到限制。

二、锂电池的特点:1、具有更高的重量能量比、体积能量比;2、电压高,单节锂电池电压为3.6V,等于3只镍镉或镍氢充电电池的串联电压;3、自放电小可长时间存放,这是该电池最突出的优越性;4、无记忆效应。

锂电池不存在镍镉电池的所谓记忆效应,所以锂电池充电前无需放电;5、寿命长。

正常工作条件下,锂电池充/放电循环次数远大于500次;6、可以快速充电。

锂电池通常可以采用0.5~1倍容量的电流充电,使充电时间缩短至1~2小时;7、可以随意并联使用;8、由于电池中不含镉、铅、汞等重金属元素,对环境无污染,是当代最先进的绿色电池;9、成本高。

与其它可充电池相比,锂电池价格较贵。

三、锂电池的内部结构:锂电池通常有两种外型:圆柱型和长方型。

电池内部采用螺旋绕制结构,用一种非常精细而渗透性很强的聚乙烯薄膜隔离材料在正、负极间间隔而成。

正极包括由锂和二氧化钴组成的锂离子收集极及由铝薄膜组成的电流收集极。

负极由片状碳材料组成的锂离子收集极和铜薄膜组成的电流收集极组成。

锂电池充放电管理芯片,IC整套组合电路图

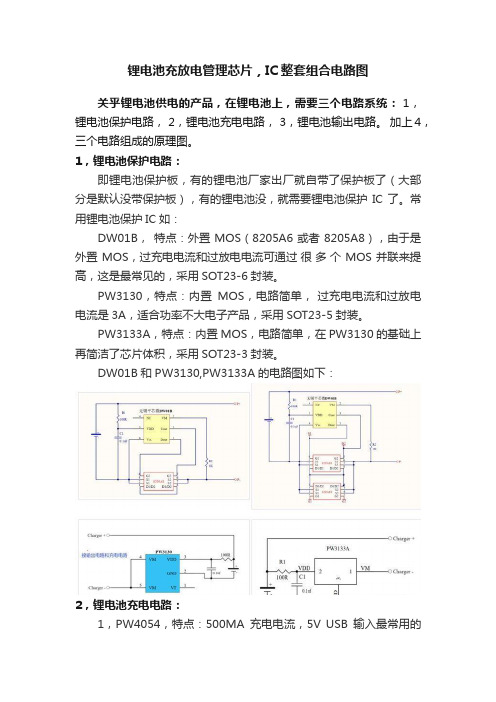

锂电池充放电管理芯片,IC整套组合电路图关乎锂电池供电的产品,在锂电池上,需要三个电路系统: 1,锂电池保护电路, 2,锂电池充电电路, 3,锂电池输出电路。

加上4,三个电路组成的原理图。

1,锂电池保护电路:即锂电池保护板,有的锂电池厂家出厂就自带了保护板了(大部分是默认没带保护板),有的锂电池没,就需要锂电池保护IC了。

常用锂电池保护IC如:DW01B,特点:外置MOS(8205A6或者8205A8),由于是外置MOS,过充电电流和过放电电流可通过很多个MOS并联来提高,这是最常见的,采用SOT23-6封装。

PW3130,特点:内置MOS,电路简单,过充电电流和过放电电流是3A,适合功率不大电子产品,采用SOT23-5封装。

PW3133A,特点:内置MOS,电路简单,在PW3130的基础上再简洁了芯片体积,采用SOT23-3封装。

DW01B和PW3130,PW3133A的电路图如下:2,锂电池充电电路:1,PW4054,特点:500MA充电电流,5V USB输入最常用的充电IC,采用SOT23-5封装;2,PW4056,特点:1A充电电流, 5V USB输入也是属于常用的充电IC,采用SOP8封装;3,PW4203,特点:5V,9V,12V,15V兼容高低压输入的锂电池充电IC,采用SOP8封装。

(注:产品很多,不能一一罗列,太多了,自行再添加)3,锂电池输出电路:1,锂电池自身供电电压是3V-4.2V之间,锂电池直接供电,电路就是直接接供电。

2,锂电池升压输出电路:PW5100,锂电池升压5V输出,输出电流在600MA,外围最简单;PW5300,锂电池升压4.5V~10V,输出功率6W(6W/电压=电流)PW5328B,锂电池升压4.5V ~20V。

(注:产品很多,不能一一罗列,太多了,自行再添加)3,锂电池降压输出电路:PW6566,LDO,输出3V,2.8V,2.5V,1.8V,1.5V,1.2V,电流最大250MA。

基于BQ76PL536的锂电池管理系统

基于BQ76PL536的锂电池管理系统去年电动汽车项目在国资委吵得火热,我们便计划开发一款关于电动汽车用的BMS。

经过多方考察,我们做了如下的方案。

二、BMS方案结合国内锂电池现状以及一些国内主流的BMS做法,BMS采用外部主动均衡技术来实现。

BMS主要有三个部分组成:1、模拟前端(AFE)部分模拟前端主要实现电池组的串联,单组电池电压的采集,单组电池温度采集,单组电池过压欠压报警,主回路电流监控(包括放电和充电)。

2、主动均衡部分主动均衡部分主要通过超级电容对过压的单组电池进行电量泄放,对欠压的单组电池进行电量补充。

防止过充和过放对锂电池本身造成伤害,也避免了因发热造成的火花、燃烧甚至爆炸。

3、主控部分主控制器负责信号的收集与整理、均衡策略调整以、控制各个均衡电路工作、以及与充电机和汽车管理系统进行通信。

BMS系统框图如图2。

三、BMS具体实施1、模拟前端(AFE)部分AFE部分主要芯片使用TI的BQ76PL536A,主要负责单组电池电压的采集,单组电池温度采集,单组电池过压欠压报警。

BQ76PL536A 可以最多实现32组串联完全满足电动汽车需求。

BQ76PL536A利用差分输入方式,实现对单组电池进行电压采样并通过SPI总线将各个电池组的电压信息以及报警信息传送到主控单元,完成AFE的工作。

其具体电路如图3所示。

AFE另一部分用来实现主回路的电流采样,通过监测主回路的电流对电池组、充电机、汽车动力驱动电路进行保护。

当电流大小超过设定值主控单元通过CAN总线通知充电机和汽车管理系统进而可以切断电源对汽车电源系统起到保护作用。

采样电阻使用锰铜丝绕制,信号经过精密仪表用放大器(AD8230)隔离放大再到AD采集器(AD7170),AD采集器通过SPI总线将电流信息传输给主控单元。

或者用隔离放大器直接将信号传输到主控芯片,利用主控芯片集成的AD进行测量。

隔离放大器价格偏高,基本在20美金以上,所以暂不考虑。

锂电池组均衡电路制作

锂电池组均衡电路制作

锂电池组均衡电路是一种通过监测锂电池组中每个单体电池的电压,并根据电压差异自动调整电池充放电状态的电路。

以下是一些简单的制作锂电池组均衡电路的方法:

使用集成均衡器:可以使用市售的集成均衡电路芯片,例如ATtiny13A、BQ77PL157等,这些芯片具有自带保护和均衡功能,可以直接连接到锂电池组上。

DIY均衡器:可以通过购买均衡电路模块并通过串联连接来实现均衡功能。

在DIY设计时,需要根据实际的锂电池组情况(如电压、容量、数量等)选择合适的模块进行组装,通常还需要一定的电子基础知识和使用工具,因此需要谨慎操作。

自制均衡器:可以自己设计和制作均衡电路,电路板设计和焊接需要一定的电子技能。

首先需要确定所需的均衡器电路类型和参数,选择合适的元器件进行组装和连接,最后进行测试和验证。

在使用锂电池组均衡电路时,需要注意保证各单元电池的连接正确、均衡电路的稳定性和可靠性,以及保证锂电池组的安全使用。

均衡电路原理

均衡电路原理成组锂电池串联充电时,应保证每节电池均衡充电,否则使用过程中会影响整组电池的性能和寿命。

常用的均衡充电技术有恒定分流电阻均衡充电、通断分流电阻均衡充电、平均电池电压均衡充电、开关电容均衡充电、降压型变换器均衡充电、电感均衡充电等。

而现有的单节锂电池保护芯片均不含均衡充电控制功能;多节锂电池保护芯片均衡充电控制功能需要外接CPU,通过和保护芯片的串行通讯(如I2C总线)来实现,加大了保护电路的复杂程度和设计难度、降低了系统的效率和可靠性、增加了功耗。

本文针对动力锂电池成组使用,各节锂电池均要求充电过电压、放电欠电压、过流、短路的保护,充电过程中要实现整组电池均衡充电的问题,设计了采用单节锂电池保护芯片对任意串联数的成组锂电池进行保护的含均衡充电功能的电池组保护板。

锂电池组保护板均衡充电基本工作原理采用单节锂电池保护芯片设计的具备均衡充电能力的锂电池组保护板示意图如图1所示。

其中:1为单节锂离子电池;2为充电过电压分流放电支路电阻;3为分流放电支路控制用开关器件;4为过流检测保护电阻;5为省略的锂电池保护芯片及电路连接部分;6为单节锂电池保护芯片(一般包括充电控制引脚CO,放电控制引脚DO,放电过电流及短路检测引脚VM,电池正端VDD,电池负端VSS等);7为充电过电压保护信号经光耦隔离后形成并联关系驱动主电路中充电控制用MOS管栅极;8为放电欠电压、过流、短路保护信号经光耦隔离后形成串联关系驱动主电路中放电控制用MOS管栅极;9为充电控制开关器件;10为放电控制开关器件;11为控制电路;12为主电路;13为分流放电支路。

单节锂电池保护芯片数目依据锂电池组电池数目确定,串联使用,分别对所对应单节锂电池的充放电、过流、短路状态进行保护。

该系统在充电保护的同时,通过保护芯片控制分流放电支路开关器件的通断实现均衡充电。

图1 具备均衡充电能力的锂电池组保护板示意图当锂电池组充电时,外接电源正负极分别接电池组正负极BAT+和BAT-两端,充电电流流经电池组正极BAT+、电池组中单节锂电池1~N、放电控制开关器件、充电控制开关器件、电池组负极BAT-,电流流向如图2所示。

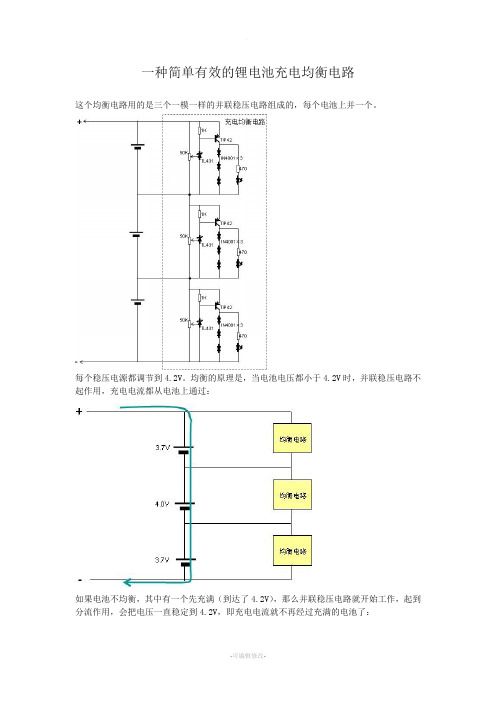

一种简单有效的锂电池充电均衡电路

如果电池不均衡,其中有一个先充满(到达了4.2V),那么并联稳压电路就开始工作,起到分流作用,会把电压一直稳定到4.2V,即充电电流就不再经过充满的电池了:

原理就这么简单,再看看并联稳压电路的原理。下面是单个的电路,TL431是基准电压,通过调节可变电阻,把电压调节到4.2V。

下面是单个的电路tl431通过调节可变电阻把电压调节到如果电池两端小于42vtl431不吸收电流即下面的lbo所以ic0充电电流就还是通过电如果电池两端到达42vtl431开始吸收电流lb0充电电流即lc通过三极管就不通过电池了即不再给电池充电了

一种简单有效的锂电池充电均衡电路

这个均衡电路用的是三个一模一样的并联稳压电路组成的,每个电池上并一个。

最右边的发光二极管有指示作用,灯亮,表示电压已经达到4.2V,即这个均衡电路对应的电池已经充满电了。

实际做好的电路板:

电路调试也比较简单,就是先不接电池,均衡电路直接接恒流电源(如果电源不支持恒流,可以串一个电阻,慢慢的把电源电压调上来)。然后一个一个调节可变电阻,让每个均衡电路的两端都是4.20V.

如果电池两端小于4.2V,TL431不吸收电流,即下面的Ib=0,所以Ic=0,三级管关闭,充电电流就还是通过电池。

如果电池两端到达4.2V,TL431开始吸收电流,Ib>0,充电电流(即Ic)通过三极管,就不通过电池了,即不再给电池充电了。

另外说明一下,这个电路中的三个串联的二极管IN4001,是起分压作用的,可以减少散耗在三极管TIP42上的功率。如果不接这三个二极管IN4001,那么三极管TIP42上散耗的功率P=4.2V×充电电流,加上之后,P=(4.2V-3×0.7V)×充了4.20V。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

*4

*4

R87 R88 1K 1K RES0603 RES0603 1-SDI_N 1-CS_N

1-VSS

1-SPI-MOSI 1-SPI-SCLK 1-SPI-SS 1-VSS

B

SCLK_N

ALERT_N

FAULT_N

CONV_N

DRDY_N

SD0_N

SDI_N

CS_N

P1 39502-1007_7-POS TP2

3

2-CELL4

CELL4

1 2 3 4 ISO/COMMS 5 VSIG FAULT ALERT DRDY 6 7 8 9 10

VSIG FAULT ALERT DRDY CONV GND MOSI MISO CS SCLK

4

2-CELL3

CELL3

5

2-CELL2

CELL2

6

2-CELL1

CELL1

ALERT_S

FAULT_S

CONV_S

DRDY_S

SCLK_S

SD0_S

SDI_S

1-FAULT_S

1-SDO_S

1-CONV_S

1-DRDY_S

#5 - THESE CAPACITORS ARE USED IN DESIGNS THAT HAVE HIGH NOISE LEVELS WHEN STACKING IC'S. USE 22pF - 100pF CAPS AS NEEDED

4

3

2 INDIVIDUAL GROUND PLANES ARE NECESSARY FOR PROPER NOISE REJECTION AND STABILITY OF THESE CIRCUITS

LTR

1

REVISION RECORD ECO NO: APPROVED: DATE:

#4

P10 2 4 6 8 10 10P/DIL

3-VBAT [1,4]

3-VBAT [1,4]

D

#5 - THESE CAPACITORS ARE USED IN DESIGNS THAT HAVE HIGH NOISE LEVELS WHEN STACKING IC'S. USE 22pF - 100pF CAPS AS NEEDED (33pF 50V 0603 NPO 10% ARE THE DEFAULT CAPACITORS)

1 JP6 2P/SIP JP5 2P/SIP JP4 2P/SIP JP3 2P/SIP JP2 2P/SIP JP1 2P/SIP R80 1K 0.1% RES0805 R72 1K 0.1% RES0805 R65 1K 0.1% RES0805 R54 1K 0.1% RES0805 R50 1K 0.1% RES0805 R44 1K 0.1% RES0805

6

1-CELL1

CELL1 SPI-SCLK

7 TP1

1-CELL0

CELL0

SPI-SS

J5- PART NUMBER CUI INC. PJ-102A 2.1MM PCB MOUNT JACK

FIDUCIAL_MARK TPA FIDUCIAL_MARK TPB FIDUCIAL_MARK TPC

1-VSS

1-ALERT_S

2

1-CELL5

3

1-CELL4

DNP

1-VSS

CELL4

DRDY CONV

EXTERNAL POWER 5VDC @200mA

X3 X4

4

1-CELL3

CELL3

5

1-CELL2

CELL2

SPI-MISO SPI-MOSI

1-SPI-MISO 1-SPI-MOSI 1-SPI-SCLK 1-SPI-SS

1-CELL6

CELL6 CELL5

*4 - LOCATE THESE RESISTORS CLOSE TO THE MOST SOUTH IC

BQ76PL536_CIRCUIT1 SHEET-2

GPIO FAULT ALERT

1-GPIO 1-FAULT 1-ALERT 1-DRDY/TX 1-CONV/RX

3-VBAT VBAT 3-CELL6 CELL6

SDI_N

CS_N

3-CS_N

SHUNT, ECON, TIN, BLACK MOLEX part number# 90059-0007 Distributor - Digikey

CELL 18 + CELL 17 + CELL 16 + CELL 15 + CELL 14 + CELL 13 + CELL 13 -

NORTH

DNP

1 3 5 7 9

CAUTION HIGH VOLTAGE

NOTE: The ground reference per circuit block is unique The most negative connection of CELL0 is the ground reference for each chip.

DO NOT connect ground references from different chips Only the ground reference CELL0 of circuit 1 is safe to connect non-isolated test equipment grounds. D

P5 10P/DIL 1 3 5 7 9

SCL SDA MISO SCLK CS

GND 5VDC 5VDC MOSI GND

2 4 6 8 10

B

1-VSS

*4

1-ALERT_N 1-FAULT_N 1-CONV_N 1-DRDY_N R85 1K RES0603

*4

R86 1K RES0603 1-SCLK_N 1-SDO_N

1 JP12 2P/SIP JP11 2P/SIP JP10 2P/SIP JP9 2P/SIP JP8 2P/SIP JP7 2P/SIP R131 1K 0.1% RES0805 R128 1K 0.1% RES0805 R121 1K 0.1% RES0805 R119 1K 0.1% RES0805 R116 1K 0.1% RES0805 R112 1K 0.1% RES0805

2-ALERT_S

2-FAULT_S

2-SCLK_S

2-SDO_S

R90 DNP RES0603 R89 0R0 RES0603 2-VSS

CONV SHEET-5 1-FAULT 1-ALERT 2-VSS C54 0.0033uf 50V CAP0603 1-DRDY/TX 1-CONV/RX 1-SPI-MISO USB-5VDC I2C-SCL I2C-SDA SPI-MISO SPI-SCLK SPI-SS SPI-MOSI AGND AGND

#5

C123 DNP CAP0603

3-FAULT_N

3-SCLK_N

ALERT_N

CONV_N

DRDY_N

3-ALERT_N

3-CONV_N

3-DRDY_N

FAULT_N

SCLK_N

SDO_N

3-SDO_N

3-SDI_N

P3 39502-1007_7-POS TP6 1 JP18 2P/SIP JP17 2P/SIP JP16 2P/SIP JP15 2P/SIP JP14 2P/SIP JP13 2P/SIP R180 1K 0.1% RES0805 R177 1K 0.1% RES0805 R171 1K 0.1% RES0805 R166 1K 0.1% RES0805 R163 1K 0.1% RES0805 R155 1K 0.1% RES0805

ALERT_S CONV_S FAULT_S DRDY_S SCLK_S SDO_S SDI_S CS_S 3-CS_S

R152 0R0 RES0603

R149 DNP RES0603

3-CONV_S

3-DRDY_S

3-ALERT_S

3-FAULT_S

3-SCLK_S

3-SDO_S

C89 0.0033uf 50V CAP0603

R150 0R0 RES0603 3-VSS

3-SDI_S

GROUND PLANE OF CIRCUIT 3 GROUND PLANE OF CIRCUIT 2 *2

R145 1K RES0603

*1

*1

*1

*1

R159 1K RES0603

R156 R157 R158 1K 1K 1K RES0603 RES0603 RES0603

P2 39502-1007_7-POS TP4

R147 R148 1K 1K RES0603 RES0603 2-SDI_N 2-CS_N

C

ALERT_N

FAULT_N

CONV_N

DRDY_N

SCLK_N

2-VBAT

CELL 12 + CELL 11 + CELL 10 + CELL 9 + CELL 8 + CELL 7 + CELL 7 -

2

3-CELL5

CELL5

3

3-CELL4

CELL4 BQ76PL536_CIRCUIT3 SHEET-4

4

3-CELL3

CELL3

5

3-CELL2

CELL2

6

3-CELL1

CELL1

7 TP5

3-CELL0

CELL0

*1 - LOCATE THESE RESISTORS CLOSE TO THE MOST NORTH IC