《数字电路与数字逻辑》练习题

数字逻辑与逻辑设计模拟卷及答案

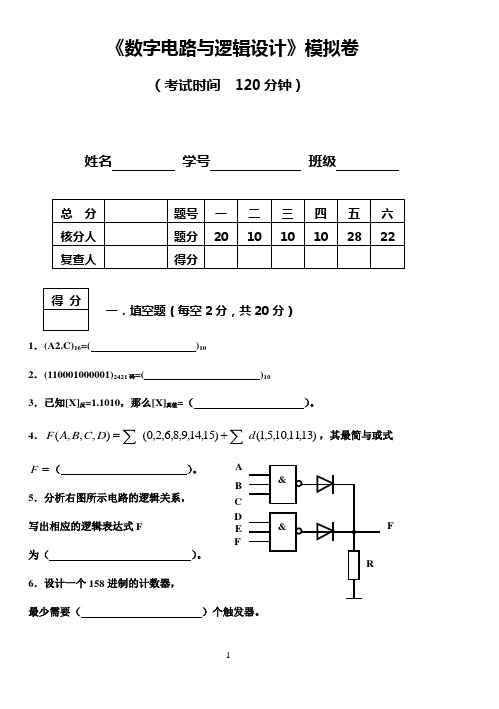

《数字电路与逻辑设计》模拟卷(考试时间 120分钟)姓名 学号 班级一.填空题(每空2分,共20分)1.(A2.C)16=( )102.(110001000001)2421码=( )103.已知[X]反=1.1010,那么[X]真值=( )。

4.)13,11,10,5,1()15,14,9,8,6,2,0(),,,(d D C B A F ∑∑+=,其最简与或式=F ( )。

5.分析右图所示电路的逻辑关系, 写出相应的逻辑表达式F为()。

6.设计一个158进制的计数器,最少需要( )个触发器。

7.当用D 触发器实现T ’触发器功能时,则D 端应接( )端。

8.模为2n 的扭环形计数器,其无用状态数为( )。

A B CD E FF9.如下图所示逻辑部件,其中各方框中采用模N 的计数器作N 次分频器,则Z 输出的频率是( )。

10.时序逻辑电路使用时钟脉冲CP 上升沿更新状态的边沿触发器,已知CP 及输入X 的波形如下图所示,则X 的取值(从左向右)是( )。

二.单项选择题(每小题1分,共10分)1.与二进制0101等值的余3码是( )。

(1)1010 (2)1000 (3)0001 (4)0011 2.二进制数011001的典型格雷码是( )。

(1)011011 (2)101101 (3)010111 (4)010101 3.表达式F=AB 可用来表示( )。

(1)A<B (2)A>B (3)A>B (4)A<B4.如将TTL “与非”门仅作为“非”门使用,则多余输入端应做( )处理。

(1)全部挂高 (2)其中一个接地 (3)全部接地 (4)部分接地 5.标准与或式是由( )构成的逻辑表达式。

(1)与项相或 (2)最小项相或 (3)最大项相与 (4)或项相与 6. 如图所示由两个”与非”门构成的基本触发器,欲使该触发器保持现态,则该触发器输入信号应为( )。

(1)S=R=0 (2)S=R=1 (3)S=1 R=0 (4)S=0 R=17.n 位二进制译码器与门阵列中,共有( )个二极管。

数字电路与逻辑设计习题及参考答案

数字电路与逻辑设计习题及参考答案一、选择题1. 以下表达式中符合逻辑运算法则的是 D 。

·C=C 2 +1=10 <1 +1=12. 一位十六进制数可以用 C 位二进制数来表示。

A . 1 B . 2 C . 4 D . 163. 当逻辑函数有n 个变量时,共有 D 个变量取值组合?A. nB. 2nC. n 2D. 2n 4. 逻辑函数的表示方法中具有唯一性的是 A 。

A .真值表 B.表达式 C.逻辑图 D.状态图5. 在一个8位的存储单元中,能够存储的最大无符号整数是 D 。

A .(256)10 B .(127)10 C .(128)10 D .(255)106.逻辑函数F=B A A ⊕⊕)( = A 。

C.B A ⊕D. B A ⊕ 7.求一个逻辑函数F 的对偶式,不可将F 中的 B 。

A .“·”换成“+”,“+”换成“·” B.原变量换成反变量,反变量换成原变量 C.变量不变D.常数中“0”换成“1”,“1”换成“0” 8.A+BC= C 。

A .A+B +C C.(A+B )(A+C ) +C9.在何种输入情况下,“与非”运算的结果是逻辑0。

DA .全部输入是0 B.任一输入是0 C.仅一输入是0 D.全部输入是1 10.在何种输入情况下,“或非”运算的结果是逻辑1。

AA .全部输入是0 B.全部输入是1 C.任一输入为0,其他输入为1 D.任一输入为111.十进制数25用8421BCD 码表示为 B 。

101 010112.不与十进制数()10等值的数或代码为 C 。

A .(0101 8421BCD B .16 C .2 D .813.以下参数不是矩形脉冲信号的参数 D 。

A.周期 B.占空比 C.脉宽 D.扫描期 14.与八进制数8等值的数为: BA. 2B.16C. )16D. 215. 常用的BCD码有 D 。

A.奇偶校验码B.格雷码码 D.余三码16.下列式子中,不正确的是(B)+A=A B.A A1⊕=⊕=A ⊕=A17.下列选项中,______是TTLOC门的逻辑符号。

《数字逻辑电路》试题及参考答案

《数字逻辑电路》在线作业参考资料一、单选题1. 一位8421BCD计数器,至少需要(B)个触发器A 3B 4C 5D 102. 在(A)的情况下,函数运算的结果是逻辑“1”A全部输入是“0” B任一输入是“0” C任一输入是“1” D全部输入是“1”3. 表示两个相邻脉冲重复出现的时间间隔的参数叫(A )A.脉冲周期B.脉冲宽度C.脉冲前沿D.脉冲后沿4. 只能读出不能写入,但信息可永久保存的存储器是(A)A.ROMB.RAMC.RPROMD.PROM5. 在(D)的情况下,函数Y=AB运算的结果不是逻辑“0”。

A全部输入是“0”B任一输入是“0”C任一输入是“1”D全部输入是“1”6. 下列哪些信号一定不属于数字信号(A)A.正弦波信号B.时钟脉冲信号C.音频信号D.视频图像信号7. 在(B)的情况下,函数Y=/(AB)运算的结果不是逻辑“0”。

A全部输入是“0”B任一输入是“0”C任一输入是“1”D全部输入是“1”8. 符合六变量m5的相邻最小项,有下列(C )说法成立A. 共有5 个相邻最小项B. m0、m4、m7、m13是它的相邻项C. 共有6 个相邻最小项D. m4、m21、m13、m38是它的相邻项9. 下列器件中,属于时序部件的是(A)A.计数器B.译码器C.加法器D.多路选择器10. 在n变量的逻辑函数F中,有(C )A. 若mi为1,则Mi也为1B. 若F所有mi为0,则F为1C. 若F所有Mi为1,则F为1D. F的任一最小项标记为mni( i = 1~2n )11. 半加器的逻辑功能是(A)A. 两个同位的二进制数相加B. 两个二进制数相加C. 两个同位的二进制数及来自低位的进位三者相加D. 两个二进制数的和的一半12. 1路—4路数据分配器有(A)A.一个数据输入端,两个选择控制端,四个数据输出端B.四个数据输入端,两个选择控制端,一个数据输出端C.一个数据输入端,一个选择控制端,四个数据输出端D.四个数据输入端,一个选择控制端,一个数据输出端13. 全部的最小项之和恒为(B)A.0B.1C.0或1D.非0非114. 对于四变量逻辑函数,最小项有(D)个A.0B.1C.4D.1615. 逻辑表达式A+BC=( C )A. ABB. A+CC. (A+B)(A+C)D. B+C16.在(A)的情况下,函数运算的结果不是逻辑“1”A全部输入是“0” B 任一输入是“0”C任一输入是“1” D全部输入是“1”17. 十进制数25用8421BCD码表示为(B )。

[东北师范大学]《数字电路与数字逻辑》20春在线作业1-4

![[东北师范大学]《数字电路与数字逻辑》20春在线作业1-4](https://img.taocdn.com/s3/m/bfc252b6453610661fd9f47c.png)

【奥鹏】-[东北师范大学]数字电路与数字逻辑20春在线作业1 试卷总分:100 得分:100第1题,组合逻辑电路的输出和()的状态有关。

A、输出B、输入C、输入和输出正确答案:B第2题,逻辑代数由逻辑变量集、逻辑常量及其()构成.A、逻辑运算B、程序C、符号D、伪代码正确答案:A第3题,将十六进制数E3.14B转换为二进制数是:()A、10011110.001011100010B、11000111.010*********C、11100011.000101001011D、11101010.110010110101正确答案:C第4题,ispEXPERT设计输入不可采用()A、原理图B、硬件描述语言C、功能模拟D、混合输入正确答案:C第5题,555定时器不可以组成( )A、多谐振荡器B、单稳态触发器C、施密特触发器D、JK触发器正确答案:D第6题,组合电路()。

A、可能出现竞争冒险B、一定出现竞争冒险C、状态改变时,可能出现竞争冒险正确答案:C第7题,电路具有两个稳定状态,在无外来触发信号作用时,电路将()。

A、自动变化B、保持原状态不变C、不确定正确答案:B第8题,PLSI器件的实现功能的核心部分是()A、通用逻辑块(GLB)B、总体布线池(GRP)C、输出布线池(ORP)D、输入输出单元正确答案:A第9题,描述小规模时序逻辑电路的有效的方法是()A、方程法B、状态表/状态转换表C、状态图/状态转换图D、时序图方法正确答案:A第10题,组合电路是由()。

A、门电路构成B、触发器构成C、A和B正确答案:A第11题,下列关于GAL说法正确的是()A、与阵列可编程B、或阵列可编程C、或阵列固定D、与阵列可固定正确答案:A,C第12题,PLS2000与3000系列中基本逻辑单元与PLS1000系列不同之处是()A、全局时钟结构B、I/O单元C、输出使能结构D、输出布线池结构正确答案:A,B,C,D第13题,最常用的两种整形电路是()。

《数字电路与数字逻辑》练习题答案

《数字电路与数字逻辑》练习题一答案一、 填空 1、75 3.375 2、11110103、(17A )H >(376.125)D >(67)O >(11000)B4. 40,3.31255. 0.1101B ,0.61O ,0.DH11111110.01B ,376.4O ,FE .4H6. +1111101,01111101,01111101,01111101 —101010,1101010,1010101,10101107.))()((C A D C B A +++ ))()((C A D C B A +++ 8.0 19.101011.1 2B.8 10.n2 1 11、81,3.62512、11111110.01, 11111110.01, 11111110.01, 11111110.01 13、(27A )H >(76.125)D >(67)O >(10110)B14、Q n , 1 15、9, 8 16、4 17、(3FFF)H18、B A A+B AB+C 19、32进制20. 56,2.812521. 100101B ,45O ,25H101.0101B ,5.24O ,5.5H22. +1111100,01111100,01111100,01111100—11101,111101,100010,10001123.A B ,A,AB + AC ,A+B C24.(4E.4)16=(1001110.01)2=(116.2)8=(1111000.00100101)842125、(10011001)余3码(1010101)格雷码26.10101 11010 1101127、输入原来状态28、(A+C)(B+C)29、10,830、T触发器31、随机存取存储器RAM 只读存储器ROM32、833、CABC+AB+ABC34、C++A+BB35,6.562536.110011,63,33;101.0101,5.24,5.537.+1101000,01101000,01101000,01101000;-100111,1100111,1011000,101100138.A B,A,A + B ,A +BC二、单项选择题:三1.2.(1))BA或C+D+++CADBD(BCABD(2)B=异或操作AF⊕3.分析以下电路,说明电路功能。

东师《数字电路与数字逻辑16秋在线作业2

B.提高D/A转换速度

C.提高D/A转换速度

D.增加可靠性

正确答案:

10.触发器可以记忆()位二值信号。

A. 1

B. 2

C. 4

D. 8

正确答案:

数字电路与数字逻辑16秋在线作业2

二、多选题(共10道试题,共30分。)

1.下列哪些属于用卡诺图化简逻辑函数时的步骤:()。

A.将逻辑式化为标准“与或”式

A.错误

B.正确

正确答案:

4.逻辑函数Y=A + B+ C+B已是最简与或表达式。

A.错误

B.正确

正确答案:

5.占空比的公式为:q = t w / T,则周期T越大占空比q越小。

A.错误

B.正确

正确答案:

6.若两个函数具有不同的真值表,则两个逻辑函数必然不相等。

A.错误

B.正确

正确答案:

7. RAM能随时读出RAM中所存的内容,又能随时将新的内容写入RAM中

二、多选题(共10道试题,共30分。)

1. RAM的典型结构由哪几部分组成()

A.地址译码

B.存储矩阵

C.读出电路

D.读/写控制

正确答案:

2. 555定时器电路可以应用于哪些方面()

A.自动控制

B.定时

C.仿声

D.防盗报警

正确答案:

3.最大项具有下列性质:()。

A.在输入变量的任何取值下必有一个最大项,而且仅有一个最大项的值为0。

A.错误

B.正确

正确答案:

14.主从JK触发器,边沿JK触发器和同步JK触发器的逻辑功能完全相同

A.错误

B.正确

数字电路与数字逻辑4时序逻辑电路习题解答

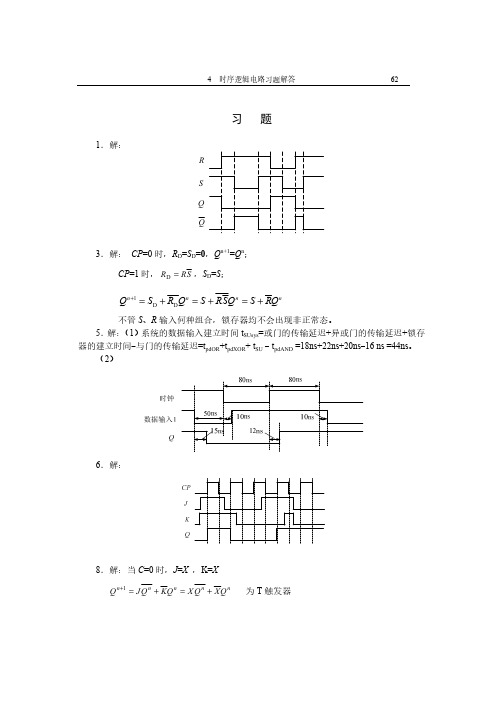

4 62习 题1.解:QQRS3.解: CP =0时,R D =S D =0,Q n+1=Q n ; CP =1时,S R R =D ,S D =S ;1D D n n n n Q S R Q S RSQ S RQ +=+=+=+不管S 、R 输入何种组合,锁存器均不会出现非正常态。

5.解:(1)系统的数据输入建立时间t SUsys =或门的传输延迟+异或门的传输延迟+锁存器的建立时间-与门的传输延迟=t pdOR +t pdXOR + t SU - t pdAND =18ns+22ns+20ns -16 ns =44ns 。

(2)4 63当C =1时, J =X X K = X Q K Q J Q n n n =+=+1 为D 触发器9. 解:当EN =0 ,Q n+1=Q n ;当EN =1,Q n+1=D ,则D EN Q EN Q n n ⋅+⋅=+11,令D EN Q EN D n ⋅+⋅=1即可。

10.解:根据电路波形,它是一个单发脉冲发生器,A 可以为随机信号,每一个A 信号的下降沿后;Q 1端输出一个脉宽周期的脉冲。

12.解:(1)(2)4 6415. 解:X =0时,计至9时置0000:03Q Q LD =,D 3D 2D 1D 0=0000X =1时,计至4时置1011:23Q Q LD =,D 3D 2D 1D 0=10112303Q Q X Q Q X LD +=,D 2=0,D 3=D 1=D 0=X16.解:当片1计数到1001时,置数信号LD 为低电平,这时,再来一个CP 脉冲,下一个状态就进入0000。

应该等到片0和片1的状态同时为1001时,片1的下一个状态才能进入0000。

改进后电路为:对改进后电路的仿真结果:17.解:4 6518.解:19. 解:从图所示电路图可知,S 1S 0=01,根据表4.8-3所示的74LS194功能表,电路处于右移功能。

右移数据输入端的逻辑表达式为:32IR Q Q D =。

数字逻辑与数字电路习题【有答案】

《数字逻辑与数字电路》习题案例(计算机科学与技术专业)2011年7月计算机与信息学院计算机科学技术系一、选择题1.十进制数33的余3码为 。

A. B. C. D.2.二进制小数-0.0110的补码表示为 。

A .0.1010B .1.1001C .1.0110D .1.10103.两输入与非门输出为0时,输入应满足 。

A .两个同时为1B .两个同时为0C .两个互为相反D .两个中至少有一个为04.某4变量卡诺图中有9个“0”方格7个“1”方格,则相应的标准与或表达式中共有多少个与项 ?A . 9B .7C .16D .不能确定5. 下列逻辑函数中,与A F =相等的是 。

)(A 11⊕=A F )(B A F =2⊙1 )(C 13⋅=A F )(D 04+=A F6. 设计一个6进制的同步计数器,需要 个触发器。

)(A 3 )(B 4 )(C 5 )(D 67. 下列电路中,属于时序逻辑电路的是 。

)(A 编码器 )(B 半加器 )(C 寄存器 )(D 译码器8. 列电路中,实现逻辑功能n n Q Q =+1的是 。

)(A )(B9. 的输出端可直接相连,实现线与逻辑功能。

)(A 与非门 )(B 一般TTL 门)(C 集电极开路OC 门 )(D 一般CMOS 门10.以下代码中为无权码的为 。

A . 8421BCD 码B . 5421BCD 码C . 余三码D . 格雷码11.以下代码中为恒权码的为 。

A .8421BCD 码B . 5421BCD 码C . 余三码D . 格雷码12.一位十六进制数可以用 位二进制数来表示。

A . 1B . 2C . 4D . 16CP QCP QCPQ 0 CP13.十进制数25用8421BCD码表示为。

A.10 101B.0010 0101C.D.1010114.在一个8位的存储单元中,能够存储的最大无符号整数是。

A.(256)10B.(127)10C.(FF)16D.(255)1015.与十进制数(53.5)10等值的数或代码为。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《数字电路与数字逻辑》练习题一、填空1将下列二进制数转为十进制数(1001011) B = ( )D( 11 . 011 ) B =()D2•将下列有符号的十进制数转换成相应的二进制数真值、原码、反码和补码成最简与或式的形式AB AC BC =(其反函数F 是 _____________________________ 。

8 .当i = j 时,同一逻辑函数的最小项m j m j(+122)=( )真值=( 原码)反码=(补码3. 把下列4个不同数制的数(376.125) D 、(110000)B 、(17A) H 、(67) 0(按从大到小的次)>()>()。

将下列各式变换4. 将下列二进制数转为十进制数 (101000) B =(D5. 将下列十进制数转为二进制数, (0. 8125)=( H(254 . 25)=(H6. 将下列有符号的十进制数转换成相应的二进制数真值、 =( )真值=( =( )反码=(=( )真值=( =( )=((+125)(—42)7.逻辑函数 (11 . 0101 ) B八进制数和十六进制数 B =(原码、反码和补码) ) ) ) 原码 补码 原码 补码F = AB CD AC 的对偶函数F ■是两个最大项M j + M j = ___________ 。

9.(43.5)10= (_______ )2= (________ )16。

10. ___________________________________________ n个输入端的二进制译码器,共有_______________________________________________ 输出端,对于每一组输入代码,将有__________ 输出端具有有效电平。

11.将下列二进制数转为十进制数(1010001)B = ()D (11. 101)B = ()D12.将下列有符号的十进制数转换成相应的二进制数真值、原码、反码和补码(+254.25 )=()真值=()原码=()反码=()补码13.把下列4个不同数制的数(76.125)D、(27A)H、(10110)B、(67)0按从大到小的次序排列()>()>()>()。

14.对于D触发器,欲使Qn+仁Qn输入D=(),对于T触发器,欲使Qn+仁Qn输入T= ()15.一个512*8位的ROM芯片,地址线为()条,数据线为()条。

16.对32个地址进行译码,需要()片74138译码器。

17.存储器起始地址为全0, 256K*32的存储系统的最高地址为()。

18.将下列各式变换成最简与或式的形式()()()19•五级触发器的进位模数最大为()进制。

20.十进制数(78.25 )10转换成十六进制数是(),转换成二进制数是(),转换成八进制数是(),转换成8421BCD码为()。

21.将二进制1100110转换成余3码为(),转换成格雷码为()。

22.设真值X= —0101,则X的原码为(),反码为(),补码为()。

23.卡诺图是()的一种特殊形式。

利用卡诺图法花剑逻辑函数比()法更容易得到简化的逻辑函数表达式。

24.函数L=AC+BC勺对偶式为:()。

25.一个1024*16位的ROM芯片,地址线为()位,数据线为()位。

26.对于JK触发器,若J=K,可完成()触发器的逻辑功能。

27.组合逻辑电路中部包含存储信号的()元件,它一般是由各种()组合而成的。

28.对64个地址进行译码,需要()片74138译码器。

29.AB+AC化成最小项的形式为()。

30.将变换成或非的形式为()。

31.数制转换(6.3125)10=()2(1101.1101)2=()1032.将下列有符号的十进制数转换成相应的二进制数真值、原码、反码和补码(+11/32)=( ) 真值=() 原码=( ) 反码=() 补码(-15/64)=( ) 真值=() 原码=( ) 反码=() 补码33.把下列3个数(76.125)D、(27A)H、(67)0按从大到小的次序排列( )>( )>( )34.已知二进制数1100101,将其转换成格雷码为( ) 。

35.已知格雷码编码为1100101,将其转换成二进制数为( ) 。

26•将下列二进制数转为十进制数(101001) B = ( ) D (110. 1001) B = ( ) D 36.将下列十进制数转为二进制数,八进制数和十六进制数(51) = ( ) B = ( ) O = ( ) H (5. 3125) = ( ) B = ( ) O = ( ) H 37.将下列有符号的十进制数转换成相应的二进制数真值、原码、反码和补码(+104)=( )真值=( )原码=( )反码=( )补码(—39)=( )真值=( )原码=( )反码=( )补码38.将下列各式变换成最简与或式的形式A +B =A + AB =A + AB =(A + B ) (A + C )=二、选择题1..001)等值的十六进制数学是()。

(A)337.2 (B)637.2 (C)1467.1 (D)c37.42.是8421BCD码的是( )(A)1010 (B)0101 (C)1100 (D)11113.和二进制码1100对应的格雷码是( )(A)0011 (B)1100 (C)1010 (D)01014.如右图,电路实现的逻辑功能F=()(A)AB (B)0 (C)A+B (D)15.TTL电路中,高电平V H的标称值是( )(A)0.3V (B)2.4V (C)3.6V (D)5V6.和逻辑式A ABC相等的式子是()(A)ABC (B)1+BC (C)A (D) A BC7.若干个具有三态输出的电路输出端接到一点工作时,必须保证( )(A)任何时候最多只能有一个电路处于三态,其余应处于工作态。

(B)任何时候最多只能有一个电路处于工作态,其余应处于三态。

(C)任何时候至少要有两个或三个以上电路处于工作态。

(D)以上说法都不正确。

8. A+B+C+ A+A B=( )(A)A (B) A (C) 1 (D)A+B+C9.下列等式不成立的是( )(C) AB+AC+BC=AB+BC (A) A AB = A B (B)(A+B)(A+C)=A+BC(D) AB AB AB AB =110. F(A,B, C) = m(0,1,2,3,4,5,6),则F=()(A)ABC (B)A+B+C (C) A B C (D) ABC三、简答1 •写岀函数尸的反函数歹,并将戸化为最简与或式; F = AB+C + AB(8分) 2、(1)化简下面的式子(6分)(2)分析此组合逻辑电路的逻辑功能(7分)3、分析以下电路,说明电路功能。

(10分)4.分析以下电路,说明电路功能。

(10分)四、化简题1•将逻辑函数F = BCD AB - ABCD BC转化为最小项表达式2•卡诺图法化简逻辑函数F(A, B,C,D)二ABCD ABCD ACD AD。

3.将图示波形作用在维持阻塞JK触发器上,试画出触发器Q端的工作波形(设初态Q"二0 )。

CP五、组合逻辑设计题1. 3-8译码器的各输入端的连接情况及第六脚输—形如下图所示_Q _________ 1试画出输出Y 0, 丫"丫3,丫4,丫5引脚的波形。

(10分)。

2.在举重比赛中,有甲、乙、丙三位裁判,其中甲为主裁判,当两位或两位以上裁判(其中必须包括甲裁判在内)认为运动员上举合格,才可发出合格信号,试用3-8译码器和逻辑门设计上述要求的组合逻辑电路。

(10分)3•设计一个组合逻辑电路,其功能是将8-4-2-1 BCD码转换成余3码,门电路不限。

画出真值表并写出相应的逻辑表达式即可。

(注:余3 码=BCD 码+ 0011) (12 分)4.设计一个四位格雷码变二进制数的转换电路,推出相应的逻辑表达式即可(12分)5.(6分)用74LS151 (8选一数据选择器)实现三人表决电路(即三人表决一件事,按照少数服从多数的原则)。

6.设计一个组合电路,用来判断输入的四位8421BCD码A,B,C,D当其值大于或等于5时,输出为1,反之输出为0。

写出逻辑表达式即可六、组合电路分析题1.已知逻辑电路如下图所示,分析该电路的功能2、分析下图组合逻辑电路功能。

(10分)3.已知电路如图所示。

(其中,触发器为上升沿触发的边沿型D触发器。

)(1 )写出状态方程;(2 )画出电路的状态转换图(3)根据状态转换图,说出电路的逻辑功能,检查电路能否自启动。

(18分)4 .试分析如下电路,写出 F 的表达式。

(10分)5 •分析下图,写出 F 的表达式。

(15分)6.下图中设初态Q D Q C Q B Q A "000,试分析该电路。

(15分)《数字电路与数字逻辑》练习题一、填空题1. (11.001) 2=()16=()10 (-1101) 2=( )原码=()补码(75)10=()8421BCD ()余3码2.触发器有 个触发器。

个稳态,存储8位二进制信息要3. 米利型时序电路输出信号与 和有关,没有输入变量的时序电路又称—型电路。

4. 如果某计数器中的触发器不是同时翻转,这种计数器称为 ____________ 计数器,n进制计数器中的n 表示计数器的 ______________ ,最大计数值是 _____________ 。

5. A/D 转换的基本步骤是 ________ 、 __________ 、 __________ 、 ___________ 四个步骤。

6. 半导体存储器从存,取功能上可以分为 _____________ 和 ____________ 。

二、单项选择题1 .在下列()输入情况下,与非运算的结果等于逻辑0。

①全部输入0 ②仅有一端输入0 ③全部输入1④ 仅有一端输入12.下列器件中,属于组合逻辑电路的是()①计数器和全加器 ②寄存器和比较器 ③计数器和寄存器 ④全加器和比较器 3 .一个8421BCD 码计数器,至少需要( )个触发器①3②4③5④104.一个16选一数据选择器,其地址输入端有( )个①1②2③45. 不符合常用逻辑关系的说法是( ①有0出0,全1出1③有1出1,全0出0 6. 将JK 触发器转换成D 触发器,其转换电路中的虚线框处应是(① 与非门 ② 异或门 ③ 连接线④8)。

②有0出1,全1出0 ④有0出0,有1出1④非门三、判断题1.一个逻辑函数的对偶式只是将逻辑函数中的原变量换成反变量,反变量换成原变量。

一|2 •卡诺图方格中1所对应的最小项之和组成原函数。

3. 维持阻塞D 触发器克服了空翻。

4 •双向移位寄存器电路中没有组合逻辑电路。