采样保持电路设计研究

采样保持电路

一、采样保持电路结构的选择常见的采样保持结构有以下两种:图1、电荷传输型采样保持电路图2、电容翻转型采样保持电路图3、图1,图2所用的时钟信号工作原理:一、电荷传输型采样保持电路首先Φ1、Φ1’为高电平,采样电容CS 对输入信号进行采样,然后Φ1’比Φ1提前0.4ns 进入下降沿,此时x 点为高阻状态,故当Φ1变为低电平,即ks1开关关断时,x 点不再导通,即抑制了开关ks1的电荷注入效应。

当Φ2为高电平的时候,Φ1、Φ1’此时为低电平,电路进入保持状体。

CS 上的差分电荷就传到了Cf 上,此时差分输出电压即为差分输入电压(CS=Cf )。

二、电容翻转型采样保持电路首先Φ1、Φ1’为高电平,采样电容CS 对输入信号进行采样,然后Φ1’比Φ1提前0.4ns 进入下降沿,此时x 点为高阻状态,故当Φ1变为低电平,即ks1开关关断时,x 点不再导通,即抑制了开关ks1的电荷注入效应。

当Φ2为高定平时,采样电容C 的左端接放大器的输出端,因为输出共模电平等于输入共模电平,所以采样保持电路的输出等于采样保持电路的输入。

对两种结构进行对比。

1、 所需放大器的带宽。

为简化分析我们将其简化为单极点系统,则放大器的传输函数为:()1A A S sω=+ (1)式中:A 表示低频增益,0ω为3dB 带宽。

将放大器接成闭环后,其闭环传输函数为:00/(1/)/(1)()1/(1)11/A s A fA Ac S Af s fA s ωωω++==++++ (2) 其中f 为反馈系数。

则该闭环系统的时间常数为: τ=01/fA ω= 1/n f ω (3) 其中n ω为运放的单位增益带宽对于单位阶跃输入信号,闭环系统输出阶跃响应为: Vout (t )= /1(1)()t e u t f-τ- (4)同样我们要求输出的误差必须小于1/2LSB ,得/t e -τ<112N + (5)从(3)、(5)我们可得11ln 2N n pft ω+>(6) 其中p t 为信号建立时间,大约为3/8T 。

一种高精度、低功耗采样保持电路的设计

目录1 引言 02 采样保持电路基本理论分析及主要设计考虑1基本采样保持电路的分析1采样保持电路的性能指标1采样保持电路结构分析及选择1采样保持的基本结构1电荷重分配式采样保持电路2电容翻转式采样保持电路33 采样保持电路的设计与实现4采样保持电路的整体结构4采样保持运算放大器的设计6运算放大器的性能参数6几种运放的结构比较7采样保持放大器的设计与仿真7偏置电路的设计10开关电容的选取11采样开关的设计12MOS开关简介 12MOS开关非理想因素的分析12栅压自举开关12时钟产生电路的设计13采样保持电路总体仿真164 采样保持模块版图实现17版图设计基本原则17采样保持电路版图实现18整体设计布局18元器件版图设计18各个模块的版图设计19整体版图设计215总结22谢辞错误!未定义书签。

参考文献23附录1 241 引言近几年微电子技术发展十分迅速,数字信号技术已经十分广泛,在生产生活中变得越来越重要,很多模拟电路在数字领域也变得能够实现[1]。

模数转换器(ADC)是数字信号和模拟信号的接口,已近成为各种数字系统中必不可少的一个模块,它对整个数字系统有着十分巨大的作用。

模数转换电路的发展趋势是高分辨率、高转换速率、低功耗方向发展;采样保持电路,它与模数转换器有着相同的发展方向。

低电压、高速、高精度的采样保持电路一直是一个设计难点,也是一个研究热点。

研究主要从采样模式和保持模式两方面进行,采样模式包括栅压自举开关电路,MOS 管电荷注入效应,时钟馈通效应,开关导通电阻的非线性和噪声;保持模式主要对运放的建立过程的研究。

本设计讨论的就是模数转换器的一个最前端的模块——采样保持电路。

采样保持电路(sample hold devices)简称S/H,它是用在模拟/数字转换系统中的一种电路[2]。

作用是采集模拟输入电压在某一时刻的瞬时值,并在模数转换器进行转换期间保持输出电压不变,以供模数转换。

模数转换需要一定时间,在转换过程中,如果送给ADC的模拟量发生变化,则不能保证精度。

基于0.18μm CMOS工艺的高速以及高精度采样保持电路设计的开题报告

基于0.18μm CMOS工艺的高速以及高精度采样保

持电路设计的开题报告

1.背景

在现代电子系统中,采样保持(Sample and Hold)电路是一个基本的电路模块。

采样保持电路通常用于信号的模拟-数字转换器(ADC)输入阶段,其作用是将模拟信号转换成数字信号。

采样保持电路可以在采样时将模拟信号锁定在特定的时间点并保持其电平,然后将信号电平转换成数字信号,以进一步进行数字信号处理。

采样保持电路的性能对于ADC转换器的整体性能至关重要。

因此,设计高速以及高精度采样保持电路是电子工程领域的一个重要研究课题。

2.研究内容

本项目基于0.18μm CMOS工艺,旨在设计高速以及高精度采样保持电路。

研究内容主要包括以下方面:

(1)研究不同类型采样保持电路的原理和特点,分析其优缺点。

(2)设计基于CMOS工艺的高速采样保持电路。

采用低阻抗传输门和复合输送栅(Composite Transconductance Amplifier)构建的电路,以提高采样速度。

(3)设计基于CMOS工艺的高精度采样保持电路。

采用带负反馈的Sample and Hold电路来提供更高的采样保持精度。

(4)在HSpice仿真平台上对设计的电路进行仿真和验证,分析优化效果。

3.研究意义

设计高速以及高精度采样保持电路,对提高ADC转换器的性能、减小系统误差具有重要的意义。

本项目将通过研究不同类型采样保持电路

的特点并设计高速以及高精度采样保持电路,为ADC转换器的进一步发展提供技术支持。

adc采样控制电路设计实验总结

ADC采样控制电路设计实验总结

本次实验主要是设计一个ADC采样控制电路,通过该电路可以实现对模拟信号的采样和控制。

在实验过程中,我学到了很多关于ADC采样控制电路的知识和技巧。

首先,我了解了ADC的工作原理。

ADC是将模拟信号转换为数字信号的一种电路。

它通常由一个采样保持电路、一个量化器和一个编码器组成。

采样保持电路用于在特定的时刻对模拟信号进行采样,并将其保持在一个稳定的状态。

量化器将采样到的信号转换为离散的数字值,而编码器则将数字值转换为二进制码。

其次,我学习了如何设计和实现一个ADC采样控制电路。

在实验中,我使用了一个运算放大器和一个多路选择器来实现采样保持电路。

运算放大器用于放大输入信号,并将其输出连接到多路选择器的输入端。

多路选择器根据控制信号选择不同的输入信号,并将其输出连接到量化器和编码器。

在实验中,我还学习了如何选择合适的元件和参数来实现ADC采样控制电路。

例如,我需要选择一个合适的运算放大器来放大输入信号,并选择一个合适的多路选择器来实现采样保持功能。

此外,我还需要选择合适的量化器和编码器来实现数字信号的转换和输出。

最后,我进行了实验验证,并对实验结果进行了分析和总结。

通过实验,我发现ADC采样控制电路可以准确地对模拟信号进行采样和控制,并将采样到的信号转换为数字信号。

同时,我也发现了一些实验中的问题和不足之处,例如电路的稳定性和精度等方面还需要进一步改进和优化。

一种用于流水线ADC采样保持电路的设计

Ke r s:s mp e h l ic i;f l - fe e c tu t r y wo d a l — o d cr u t ul di r n e sr c u e;g t —o tg o tta pe wic y f a e v la e b o srp d s th

MH , h i a  ̄ q ec f1MH ,h up t i a sui s redn m crne( F R)o 7 . B o e z tes n l eu n yo g z teo t g l p r u- e y a i a g S D u sn o f f 3 4 d .P w r

为 1 H , 0M z 输入信号频率为 1MH 时 , 出信号无杂散动态范 围( F R) 7 . B 功耗 约为 2 w。 z 输 S D 为 34d , 0m

关键 词 : 采样保持 电路 ; 全差分结构 ; 自举开关 栅压

中图分类 号 : N 3 T 42

文 献标识 码 : A

L e g,HU IF n ANG hih n ,L N i S ze I We

( e aoao KyL brtyo coe co i It rt i ut, uh uU i rt,F zo 50 2, hn r fMi —l t nc ne ae Cr i F zo nv sy uhu3 00 C i r er g d c s ei a)

文章 编号 :0 5— 4 0 2 1 ) 2— 1 0— 4 1 0 9 9 (0 0 0 0 7 0

EEA CC :1 0 20

一

种 用 于 流 水 线 A C采 样 保 持 电路 的 设 计 D

0.13um CMOS流水线型ADC采样保持电路设计的开题报告

0.13um CMOS流水线型ADC采样保持电路设计的开题报告摘要:本文详细阐述0.13um CMOS流水线型ADC采样保持电路的设计过程。

首先,对该电路的原理和常见设计方案进行了介绍,并分析了其主要优点和不足之处。

接着,我们设计了一种基于CMOS技术的电路方案,并对其进行了仿真和性能测试。

最终,通过实验结果,证明了该设计方案的可行性和优越性。

关键词:ADC、流水线、采样保持、CMOS1. 研究背景与意义ADC(模数转换器)是将模拟信号转换为数字信号的重要设备,广泛应用于通信、电力、环境监测等领域。

在现代高速数字通信中,高速、高精度的ADC已经成为必不可少的部分。

流水线型ADC是各类ADC中性能最好、速度最快、成本最低的一种。

它具有较高的采样速度和较低的噪声性能,被广泛应用于高速数字通信系统中。

采样保持电路是流水线型ADC中的一个重要组成部分,其主要功能是在ADC采样过程中对输入信号进行采样和保持。

因此,设计一种高性能、低功耗、基于CMOS技术的流水线型ADC采样保持电路,具有重要的现实意义。

2. 研究内容2.1 流水线型ADC原理及常见设计方案流水线型ADC采用逐级转换的方式,将模拟信号经过多个级别的转换,最终转换为数字信号。

其基本结构如下图所示:[image]常见的流水线型ADC采样保持电路有:单级采样保持电路、多级采样保持电路和分立滞后电容采样保持电路等。

这些电路各有优缺点,根据实际需求进行选择。

2.2 电路设计本设计采用多级采样保持电路的方案,其主要组成部分有精密采样电容、自适应开关电容和运放等。

2.3 仿真及性能测试通过电路仿真和性能测试,对设计方案进行验证和评估,分析其优点和不足之处。

3. 研究成果本研究设计了一种基于CMOS技术的流水线型ADC采样保持电路方案,并通过电路仿真和性能测试,验证了其可行性和优越性。

该方案具有以下优点:(1)采样精度高,大大提高了ADC的分辨率和信噪比。

采样保持电路设计与制作

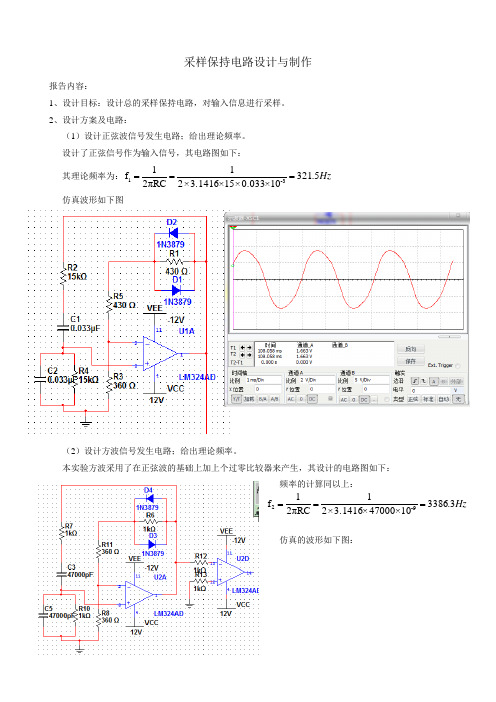

采样保持电路设计与制作报告内容:1、设计目标:设计总的采样保持电路,对输入信息进行采样。

2、设计方案及电路:(1)设计正弦波信号发生电路;给出理论频率。

设计了正弦信号作为输入信号,其电路图如下: 其理论频率为:Hz 5.32110×0.033×15×3.1416×21πRC 21f 3-1=== 仿真波形如下图(2)设计方波信号发生电路;给出理论频率。

本实验方波采用了在正弦波的基础上加上个过零比较器来产生,其设计的电路图如下:频率的计算同以上:Hz 3.338610×47000×3.1416×21πRC 21f 9-2===仿真的波形如下图:(3)设计总的采样保持电路。

总的采样保持电路如下,仿真的波形如上:(S开关所用的CD4051芯片在仿真中用场效应管代替)另外需提供:示波器1台、直流电源±12V。

4、制作采样保持电路的实物照片5、制作结果:给出示波器显示的结果(照片)和频率; 正弦波:实验所得到的正弦波频率Hz 67.359f ’1=(理论计算Hz 5.321f 1=) 方波频率Hz 86.3301f ’2=(理论计算Hz 3.3386f 2=) 实验产生的误差可能是:电阻和电容的数值与理论值存在差距;导线连接时接触问题等;方波:采样保持及方波:6、心得体会。

本次实验总的进程比较顺利,没有损坏任何实验器件,这主要是得益于模拟软件的仿真。

首先在模拟软件上设置正弦波和方波,通过调整不同的阻值和电容值来实现对电路频率的控制,模拟出比较理想的波形之后,再进行实物的连接,这样既能方便的调整电路,大大减少实验时间,又能最大程度的避免实验时对器件的损坏。

通过本次实验,我认识到一个小小的道理:做实验时一定要细心,仔细连接和检查电路,才能顺利地取得成功,欲速则不达!。

采样保持电路

一、采样保持电路的引入在A/D转换期间,为了使输入信号不变,保持在开始转换时的值,通常要采用一个采样保持电路。

对于MCS-96单片机的A/D转换器,启动转换实际上是把采样开关接通,进行采样,过一段时间后,开关断开,采样电路进入保持模式,才是A/D真正开始转换二、采样保持电路的原理A/D转换需要一定时间,在转换过程中,如果送给ADC的模拟量发生变化,则不能保证精度。

为此,在ADC前加入采样保持电路,如图下所示。

采样保持电路有两种工作状态:采样状态和保持状态。

1、采样状态:控制开关K闭合,输出跟随输入变化。

2、保持状态:控制开关K断开,由保持电容C维持该电路的输出不变。

运算放大器A2:典型的跟随器接法。

输入阻抗:高阻。

保持状态(K分)下Ch放电小,保持电压不变。

输出阻抗:小。

采样保持电路的负载能力大。

运算放大器A1:K闭合时为跟随器。

(不关心K断开的情况)。

输入阻抗:高阻。

对输入信号的负载能力要求小。

输出阻抗:小。

采样状态时,Ch上的电压快速跟随输入变化。

控制开关K:由接口电路控制。

三、采样采样脉冲的频率由下图可知,采样脉冲的频率fs(fs=1/Ts)越高,采样越密,采样值越多,采样信号的包络线越接近输入信号的波形.假设输入信号的最高频率为fm,则根据采样定理知:当采样频率fs>2fm时,采样信号可正确反映输入信号。

通常对直流或缓变低频信号进行采样时可不用采样保持电路。

三、加入S/H后模/数转换控制过程加入S/H后,整个模/数转换过程如下图所示。

1、CPU经接口电路使K闭合(启动采样)。

2、CPU经接口电路使K断开(保持)。

(*)3、CPU向ADC发出启动转换信号(转换或称量化)。

(*)4、查询A/D转换完成否,或使用中断方式。

5、读取转换后的数字。

6、在实际硬件设计中,一般第②、③步设计为用一条指令完成。

四、多路转换模拟开关1、原理由于计算机在任一时刻只能接收一路模拟量信号的采集输入,当有多路模拟量信号时需通过模拟转换开关,按一定顺序选取其中一路进行采集。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

北京工业大学

硕士学位论文

采样保持电路设计研究

姓名:王龙伟

申请学位级别:硕士

专业:微电子学与固体电子学指导教师:董利民

20090501

第3章采样保持电路模块

3.3.3改进的开关电容采样保持电路

Razavi单位增益采样保持电路给出了一个简单有效的方式达到提高输入阻抗,提高精度的目的,但是由于采样保持电路的输出在每个周期都需要复位到参考电平,这要求运放有较大的摆率【4卜451,另外,该电路的输出误差与运算放大器的增益成简单的反比关系。

如图3.14,所示,我们考虑运放的输入寄生电容为Cin,并在采样模式转变到放大模式时计算电路的输出电压值,另外运放增益有线,所以在放大模式下,Vx不等于零,在Cin上的电荷为CinVx,在结点X上的电荷守恒要求电荷CinVx来自电容Ch,使Ch上的电荷增加到CinVx+ChVO。

所以,

‰一(G%+巳比)

G

矿一‰%—1=%

(3-29)

因此,k蕊Vo堋1一石l(鲁+1)】

4、C^

(3—30)可以看出,即使速度的要求不高,输入电容必须尽量小,增加增益Av可以减小误差,但通常高增益是以大的宽长比输入器件为代价的,因此选择器件尺寸需要同时考虑到增益和输入寄生电容。

可见,Razavi采样保持电路要求运放有较高的增益和较大的摆率。

图3—15给出了针对此问题的改进方案,加入了存储电容,在①l相位时,通过电容CO预测输出电压值,而不是复位,这样系统对运算放大器建立时间的要求会大大降低,降低了对运放带宽和摆率的要求【46.521。

图3.14S/I-I的精度计算

Fig.3-14AccuracycalculationofS/H

如图3.15,在时钟①l相位时,输入电压采集在电容cl上,同时输出电压保持在电容c0上。

C2的作用是预测系统的输出电压,C2=CI+CO。

在02相位时,采样电容跨接在运算放大器两端,保持采样电压值,然后根据输出电压的大。