两非门振荡器说明

逻辑笔电路的工作原理(三款简单的逻辑笔电路原理图详解)

逻辑笔电路的工作原理(三款简单的逻辑笔电路原理图详解)逻辑笔是是采用不同颜色的指示灯为表示数字电平的高低的仪器·它是测量数字电路一种较简便的工具·使用逻辑笔可快速测量出数字电路中有故障的芯片·逻辑笔上一般有二三只信号指示灯,红灯一般表示高电平,绿灯一般表示低电平·黄灯表示所测信号为脉冲信号。

本文主要介绍了三款逻辑笔电路的工作原理,具体的跟随小编一起来了解一下。

逻辑笔电路的工作原理(一)廉价而可靠的逻辑笔电路工作原理数字电路中,有三种逻辑状态:“1”(高电平)、“0”(低电平)和“悬空”(高阻态),这就是通常说的三态逻辑。

逻辑笔就是通过发光二极管或数码管显示出被测点的逻辑状态,是数字电路制作、维修和测试不可缺少的工具。

电路原理如下图所示。

图中U1和U2是两个四——二与非门电路,即图1中的U1A~U1D、U2A~U2D。

电路主要由电源极性保护、测试探头、逻辑变换、脉冲展宽及逻辑显示五部分组成。

图中,保险丝F1和D5是电源极性保护电路,当电源接反时,F1熔断并切断电源以保护电路不被烧坏。

P1为测试探头,用于输入测试点的逻辑信号;U1A、U1B、U2A、T1、U1D、U1C等构成逻辑变换电路;U2A、U2B、C1、R6及U1C、U2C、C2、R7构成两个脉冲展宽电路;LED1为低电平显示,LED2是高电平显示。

当P1探得低电平时,即P1=0,那么经过以下逻辑变换后,由于U侣的4脚输入为高电平,此时U侣的6脚的输出就取决于U1B的5脚的输入,致使U侣的6脚输出逻辑暂不能确定。

同理,U1C的8脚输出逻辑也暂不能确定。

由于U2C的两个输入端通过电阻R7接地,所以U2C的输入逻辑为低电平,输出为高电平。

即U1B的5脚和U1C的10脚输入端逻辑状态是高电平。

同样,U2A-2的脚也为高电平输入。

因此,U1B-6=0、U1C-8=0,则继续上述逻辑变换为:U1B-6=0→U2A-1=0→。

CD4060

(一)秒时钟信号的产生1.振荡器1) 晶体振荡器晶体振荡器电路给数字钟提供一个频率稳定准确的32768Hz的方波信号,可保证数字钟的走时准确及稳定。

晶体振荡器是构成数字式时钟的核心,它保证了时钟的走时准确及稳定。

数字钟的精度主要取决于时间标准信号的频率及其稳定度。

晶体具有较高的频率稳定性及准确性,从而保证了输出频率的稳定和准确因此,一般采用石英晶体振荡器经过分频得到这一信号。

2) 振荡电路如图2所示电路通过CMOS非门构成的输出为方波的数字式晶体振荡电路。

这个电路中,CMOS非门U1与晶体、电容和电阻构成晶体振荡器电路,U2实现整形功能,将振荡器输出的近似于正弦波的波形转换为较理想的方波。

输出反馈电阻R1为非门提供偏置,使电路工作于放大区域,即非门的功能近似于一个高增益的反相放大器。

电容C1、C2与晶体构成一个谐振型网络,完成对振荡频率的控制功能,同时提供了一个180度相移,从而和非门构成一个正反馈网络,实现了振荡器的功能。

晶体XTAL的频率选为32768Hz。

该元件专为数字钟电路而设计,其频率较低,有利于减少分频器级数。

图2 晶体振荡电路框图2.分频器电路1) 分频器通常,数字钟的晶体振荡器输出频率较高,为了得到1Hz的秒信号输入,需要对振荡器的输出信号进行分频.时间标准信号的频率很高,要得到秒脉冲,需要分频电路。

分频器实际上也就是计数器,为此电路输送一秒脉冲。

2) 分频器电路电路通常实现分频器的电路是计数器电路,一般采用多级2进制计数器来实现.例如,将32768Hz的振荡信号分频为1HZ的分频倍数为32768(),即实现该分频功能的计数器相当于15级2进制计数器. 这里用一个14级2进制计数器和一个1级2进制计数器。

本次设计是运用了CD4060分频器进行分频,分频电路可提供512HZ和1024HZ的频率,在经CD4027分频器进行一分频,为此电路输送一秒脉冲。

本设计中采用CD4060来构成14级分频电路。

与或非门电路

2. 固定频率TTL振荡器

2.3.4 门电路构成控制门

◆ 与门控制电路

可应用在什么地方?

◆ 或门控制电路

2.3.4 门电路组成单稳态触发器 ◆ 什么是单稳态触发器

单稳态触发器具有两个开关状态:一个是稳定状 态,另一个是非稳定状态,也称为暂态。

1. 微分型单稳态触发器逻辑电路

L L L L L L L L L L 4 1 2 3 1 2 3 1 2 3

3) 满足以上逻辑关系的产品分类电路,如下图所示:

2.3.3 门电路组成数字信号源

◆ 概 述 数字信号源可由产生脉冲波形的振荡电路构成。在数字电 路的应用中,它可提供连续的且具有一定频率(周期)的脉冲 信号。可作为微型计算机、单片机等数字电路的时钟信号源。 可应用在哪些地方? ◆ 实 例

2.4.2 其他常用TTL门电路

1. 集电极开路门电路(OC门) ◆ 问题的提出 2. 三态门 3. 驱动电路 在实际应用中,有时要将n 个门电路的输 出端连接在一起,称为“线与”。 试分析:当其中一个F2输出为低电平,另一 个F1输出为高电平时会出现什么状况?

i

F1

F2

图2.37 i 过大一方面会使与非门F2的输出低电平状态受到破坏(使 L2=1);另一方面会使与非门F1的T3管烧坏。所以,实际应用 中这种接法是不允许的。 ◆ 问题的解决 集电极开路的TTL门电路,又称“OC门”

2.2.1 TTL系列门电路

◆ TTL(晶体管—晶体管逻辑)门电路只制成单片集成电路。 输入级由多发射极晶体管构成,输出级由推挽电路(功率输出 电路)构成。标准TTL与非门如下图所示。 ◆ 标准TTL与非门 ◆ 电路工作原理

1. 电路组成 2. 逻辑关系 3. 分析负载情况

脉冲波形产生与变换电路(课件)

2

矩形脉冲波形的主要参数

图6.1.2 矩形脉冲波形的主要特征参数

3

主要参数

六个特征参数定义: ①脉冲周期 T:周期性脉冲序列中,两个相邻脉冲 出现的时间间隔。 ②脉冲幅值Um :脉冲信号的最大变化幅值。 ③占空比D :脉冲信号的正脉冲宽度与脉冲周期的 比值,即 D=tW / T 。 ④脉冲宽度 tW :从脉冲波形上升沿的 0.5Um 到下降 沿的 0.5Um所需的时间。 ⑤上升时间tr:脉冲波形由0.1Um上升到0.9Um所 需的时间。 ⑥下降时间tf:脉冲波形由0.9Um下降到0.1Um所需 的时间。

4

6.2 单稳态触发器

特点: ①有一个稳态和一个暂稳态 ②在外界触发信号作用下,能从稳态→暂稳态 ,维持一段时间后自动返回稳态 ③暂稳态维持的时间长短取决于电路内部参数 单稳态触发器的暂稳态通常都由RC电路的充放电 过程来维持。按电路中决定暂态时间的电路连接形式 不同,单稳态触发器可分为积分型和微分型两种,如 图6.2.1、6.2.5所示。

41

随着充电过程的进行,电容电压逐渐升高, 因此uI也逐渐增大。一旦uI 达到非门G1的阈值 电压UTH,多谐振荡器必将发生如下正反馈过 程:

这一正反馈过程促使G1瞬间导通、G2瞬间截止,可

得uO1 =UOL, uO =UOH。该状态被定义为第二暂稳

态。

42

②第二暂稳态自动翻转至第一暂稳态

当多谐振荡器进入第二暂稳态的瞬间,电路输

其中,74121的电路符号如图。

14

图6.2.10 集成单稳态触发器的两种工作波形

15

图6.2.12 集成单稳态触发器74121 的外部元件连接方法 (a)使用外接电阻Rext 且采用下降沿触发 (b)使用内部电 阻Rint 且采用上升沿触发

74系列芯片简介——功能与描述

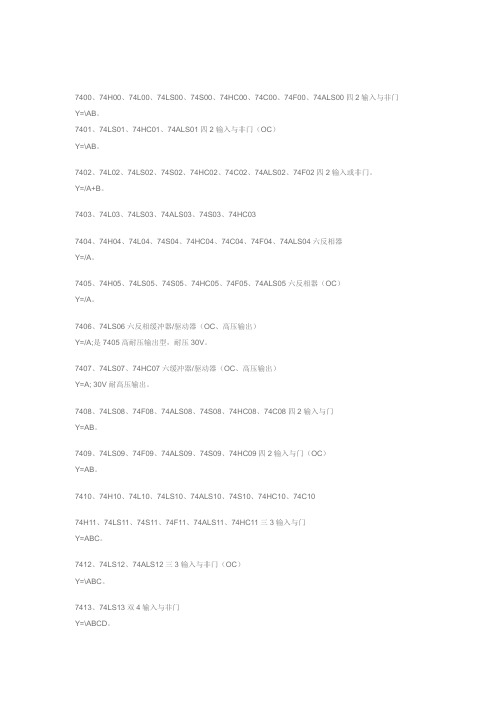

7400、74H00、74L00、74LS00、74S00、74HC00、74C00、74F00、74ALS00四2输入与非门Y=\AB。

7401、74LS01、74HC01、74ALS01四2输入与非门(OC)Y=\AB。

7402、74L02、74LS02、74S02、74HC02、74C02、74ALS02、74F02四2输入或非门。

Y=/A+B。

7403、74L03、74LS03、74ALS03、74S03、74HC037404、74H04、74L04、74S04、74HC04、74C04、74F04、74ALS04六反相器Y=/A。

7405、74H05、74LS05、74S05、74HC05、74F05、74ALS05六反相器(OC)Y=/A。

7406、74LS06六反相缓冲器/驱动器(OC、高压输出)Y=/A;是7405高耐压输出型,耐压30V。

7407、74LS07、74HC07六缓冲器/驱动器(OC、高压输出)Y=A; 30V耐高压输出。

7408、74LS08、74F08、74ALS08、74S08、74HC08、74C08四2输入与门Y=AB。

7409、74LS09、74F09、74ALS09、74S09、74HC09四2输入与门(OC)Y=AB。

7410、74H10、74L10、74LS10、74ALS10、74S10、74HC10、74C1074H11、74LS11、74S11、74F11、74ALS11、74HC11三3输入与门Y=ABC。

7412、74LS12、74ALS12三3输入与非门(OC)Y=\ABC。

7413、74LS13双4输入与非门Y=\ABCD。

7414、74LS14、74HC14、74C1474H15、74LS15、74ALS15、74S15三3输入与门(OC)Y=ABC。

7416、74LS16六反相缓冲器/驱动器Y=/A;7417、74LS17六缓冲器/驱动器(OC、高压输出)Y=A;15V耐压输出。

CD4069逻辑功能及引脚介绍

CD4069逻辑功能及引脚如图2a所示,其中非门F1、F2和外接电阻R2、R3、电容C4构成多谐振荡器,产生约3Hz的脉冲方波,供给CD4017作计数脉冲和CD40174作移位脉冲。

R3、C4为振荡定时元件,调节这两个元件可改变振荡信号频率,从而控制彩灯色彩的流动速度,以呈现各种不同的视觉效果。

另外,CD4069的非门3还用作CD40174复位信号的倒相器。

CD4069为CMOS数字集成电路,是一种高输入阻抗器件,容易受外界干扰造成逻辑混乱或出现感应静电而击穿场效应管的栅极。

虽然器件内部输入端设置了保护电路,但它们吸收瞬变能量有限,过大的瞬变信号和过高的静电电压将使保护电路失去作用,因此,CD4069中未使用的非门F4、F5、F6的输入端{9}、{11}、{13}脚均接到Vss接地端,以作保护。

CD4069多谐振荡器输出端{4}脚送出的脉冲串,一路直接送入CD4017的计数脉冲输入端{14}脚。

CD4017为十进制计数/时序分配器,用于产生CD4066模拟开关切换的控制信号。

其引脚功能如图2b所示。

Cr为复位端,当Cr端输入高电平时、计数器置零态。

CD4017具有自动启动功能,即在电路进入无效状态时,在计数脉冲作用下,最多经过两个时钟周期就能回到正常循环圈中,因此本控制器的CD4017未设置加电复位电路。

Co为进位输出端,当计数满10个时钟脉冲时输出一个正脉冲。

CD4017有CL和EN两个计数输入端,CL端为脉冲上升沿触发端,若计数脉冲从CL端输入,则EN端应接低电平;EN端为脉冲下降沿触发端,若计数脉冲从EN端输入,则CL端应接高电平,否则禁止输入计数脉冲。

取自CD4069的计数脉冲从其CL端{14}脚输入,故EN端{13}脚接地。

Y0~Y9为计数器的十个输出端,输出端送出的脉冲方波通过隔离二极管VD3~VD12连接成两路控制信号,加到模拟开关CD4066。

当第一个计数脉冲到来时,CD4017内电路翻转,{3}脚Y0呈高电平,经二极管VD5加到CD4066{12}脚。

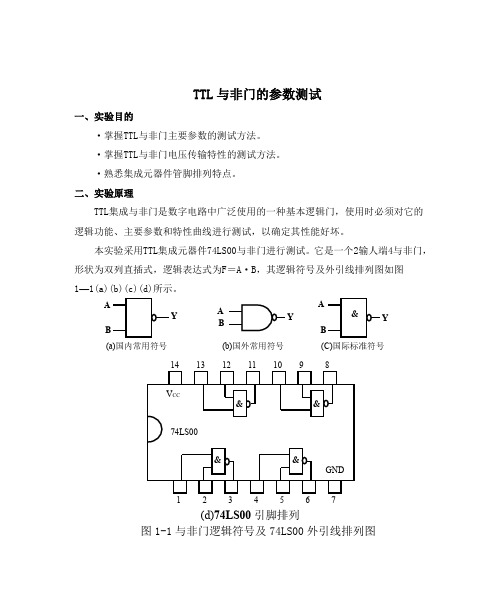

TTL与非门参数测试

2.根据实验数据画出传输特性曲线,试在曲线上标出VOH、VOL、VON、VOFF,计算VNH和VNL。

六、思考题

1.TTL电路多余的输入端应如何处理?为什么?

与非门多余的输入端:①悬空;②接高电平;③与一个有效端接在一起。或非门多余的输入端①接地②与一个有效端接在一起。其原则是无效输入端不能影响输入和输出之间的逻辑关系。

表一

带负载

开路

VOH(V)

VOL(V)

VOH(V)

VOL(V)

3.59

0.296

4.04

0.08

(2)测量输入开门电平VON和关门电平VOFF

表二

VOH(V)

VOFF(V)

VOL(V)

VON(V)

3.59

1.14

0.296

1.92

(3)测量低电平输入电流IIL和高电平输入电流IIH;

表三

IIL(mA)

(4)输入开门电平VON和关门电平VOFF

VON是指与非门输出端接额定负载时,使输出处于低电平状态时所允许的最小输入电压。换句话说,为了使与非门处于导通状态,输入电平必须大于VON。

VOFF是指使与非门输出处于高电平状态所允许的最大输人电压。

(5)扇出系数N0

N0是说明输出端负载能力的一项参数,它表示驱动同类型门电路的数目。N0的大小主要受输出低电平时,输出端允许灌人的最大电流的限制,如灌人负载电流超出该数值,输出低电平将显著抬高,造成下一级逻辑电路的错误动作。

V0(V)

1.60

1.70

1.80

1.90

2.00

2.5

3.0

3.5

4.0

4.5

5.0

V0(V)

数字电路及其应用

当今时代,数字电路已广泛地应用于各个领域。

本报将在“电路与制作”栏里,刊登系列文章介绍数字电路的基本知识和应用实例。

在介绍基本知识时,我们将以集成数字电路为主,该电路又分TTL和CMOS两种类型,这里又以CMOS集成数字电路为主,因它功耗低、工作电压范围宽、扇出能力强和售价低等,很适合电子爱好者选用。

介绍应用时,以实用为主,特别介绍一些家电产品和娱乐产品中的数字电路。

这样可使刚入门的电子爱好者尽快学会和使用数字电路。

一、基本逻辑电路1.数字电路的特点在电子设备中,通常把电路分为模拟电路和数字电路两类,前者涉及模拟信号,即连续变化的物理量,例如在24小时内某室内温度的变化量;后者涉及数字信号,即断续变化的物理量,如图1所示。

当把图1的开关K快速通、断时,在电阻R上就产生一连串的脉冲(电压),这就是数字信号。

人们把用来传输、控制或变换数字信号的电子电路称为数字电路。

数字电路工作时通常只有两种状态:高电位(又称高电平)或低电位(又称低电平)。

通常把高电位用代码“1”表示,称为逻辑“1”;低电位用代码“0”表示,称为逻辑“0”(按正逻辑定义的)。

注意:有关产品手册中常用“H”代表“1”、“L”代表“0”。

实际的数字电路中,到底要求多高或多低的电位才能表示“1”或“0”,这要由具体的数字电路来定。

例如一些TTL 数字电路的输出电压等于或小于0.2V,均可认为是逻辑“0”,等于或者大于3V,均可认为是逻辑“1”(即电路技术指标)。

CMOS数字电路的逻辑“0”或“1”的电位值是与工作电压有关的。

讨论数字电路问题时,也常用代码“0”和“1”表示某些器件工作时的两种状态,例如开关断开代表“0”状态、接通代表“1”状态。

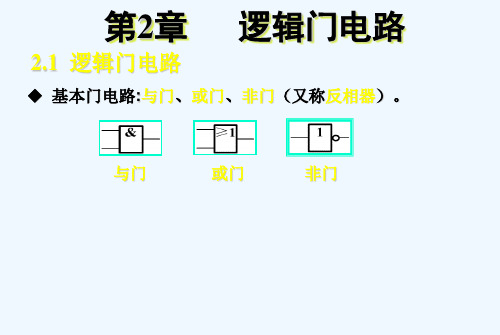

2.三种基本逻辑电路数字电路中的基本电路是与门、或门和非门(反相器)。

与门和或门电路的基本形式有两个或两个以上的输入端、一个输出端。

因输入和输出可以各自为“0”或“1”状态,具有判定的功能,所以把它们称为基本逻辑电路。