layout(匹配)

layout-提高篇

■

■

详细的整体布局的考虑因素来自■模块的放臵应该与信号的流向一致 ,每个模块一定按照 确定好的引脚位臵引出自己的连线

■

保证主信号信道简单通畅,连线尽量短、少拐弯、等长

不同模块的电源、地分开,以防干扰 ,电源线的寄生电 阻尽可能减小,避免各模块的电源电压不一致。 尽可能把电容、电阻和大管子放在侧旁,利于提高电路 的抗干扰能力。

这种瞬态脉冲可能的产生原因是瞬时电源中断等,它可能会 使引脚电位高于vdd或低于vss,容易发生 latchup。因此 对于电路中有连接到电源或地的MOS管,周围需要加保护环。

■

■

容易发生latchup的地方:任何不与power supply、substrate

相连的引脚都可能。所以精度要求高时,要查看是否有引脚 引线既不连power supply,也不连substrate,凡是和这样的 引线相连的源区、漏区都要接保护环。

●

关于寄生电容

避免时钟线与信号线的重叠

●

●

●

●

●

两条信号线应该避免长距离平行,信号线之间交叉对彼此 的影响比二者平行要小; 输入信号线和输出信号线应该避免交叉; 对于易受干扰的信号线,在两侧加地线保护; 模拟电路的数字部分,需要严格隔离开。

信号连线对称的图例

保护环

避免闩锁效应:最常见的Latchup诱因是电源、地的瞬态脉冲,

layout的金属线尤其是电源线、地线

根据电路在最坏情况下的电流值来决定金属线的宽度以 及接触孔的排列方式和数目,以避免电迁移。

电迁移效应:所谓电迁移效应是指当传输电流过大时,电子碰 撞金属原子,导致原子移位而使金属断线。 在接触孔周围,电流比较集中,电迁移效应更加容易发生。

calibredrc和lvs验证总结

v2lvs能够把verilog网表和相对应的spice库、verilog子库转成Calibre LVS用

RULECHECK CT_11 ................ TOTAL Result Count = 0

RULECHECK CT_12 ................ TOTAL Result Count = 0

RULECHECK M1_1 ................. TOTAL Result Count = 0

(1)Calibre是一个“Edge-Based”Tool,默认错误的显示是边

(2)DRC 检查的结果有are、Opposite。

(3)常用的几条检查规则,具体可阅读Calibre的手册

(a)Internal(内边对内边)用来检查 Width、Overlap;

RULECHECK M1_6 ................. TOTAL Result Count = 3

RULECHECK M2_1 ................. TOTAL Result Count = 0

RULECHECK M2_2 ................. TOTAL Result Count = 0

Merge if space is less than

NW_2b

0 0 2 Jan 2 20:10:47 2004

Rule File Pathname:

Minimum space between two NW with different potential is

NW_3

……

Rule File Pathname:

RULECHECK PD_M1 ................ TOTAL Result Count = 0

版图LAYOUT布局经验总结94条

layout布局经验总结布局前的准备:1 查看捕捉点设置是否正确.08工艺为0.1,06工艺为0.05,05工艺为0.025.2 Cell名称不能以数字开头.否则无法做DRACULA检查.3 布局前考虑好出PIN的方向和位置4 布局前分析电路,完成同一功能的MOS管画在一起5 对两层金属走向预先订好。

一个图中栅的走向尽量一致,不要有横有竖。

6 对pin分类,vdd,vddx注意不要混淆,不同电位(衬底接不同电压)的n井分开.混合信号的电路尤其注意这点.7 在正确的路径下(一般是进到~/opus)打开icfb.8 更改cell时查看路径,一定要在正确的library下更改,以防copy过来的cell是在其他的library下,被改错.9 将不同电位的N井找出来.布局时注意:10 更改原理图后一定记得check and save11 完成每个cell后要归原点12 DEVICE的个数是否和原理图一至(有并联的管子时注意);各DEVICE的尺寸是否和原理图一至。

一般在拿到原理图之后,会对布局有大概的规划,先画DEVICE,(DIVECE 之间不必用最小间距,根据经验考虑连线空间留出空隙)再连线。

画DEVICE后从EXTRACTED中看参数检验对错。

对每个device器件的各端从什么方向,什么位置与其他物体连线必须先有考虑(与经验及floorplan的水平有关).13 如果一个cell调用其它cell,被调用的cell的vssx,vddx,vssb,vddb如果没有和外层cell连起来,要打上PIN,否则通不过diva检查.尽量在布局低层cell时就连起来。

14 尽量用最上层金属接出PIN。

15 接出去的线拉到cell边缘,布局时记得留出走线空间.16 金属连线不宜过长;17 电容一般最后画,在空档处拼凑。

18 小尺寸的mos管孔可以少打一点.19 LABEL标识元件时不要用y0层,mapfile不认。

layout布局经验总结

布局前的准备:1 查看捕捉点设置是否正确.08工艺为0.1,06工艺为0.05,05工艺为0.025.2 Cell名称不能以数字开头.否则无法做DRACULA检查.3 布局前考虑好出PIN的方向和位置4 布局前分析电路,完成同一功能的MOS管画在一起5 对两层金属走向预先订好。

一个图中栅的走向尽量一致,不要有横有竖。

6 对pin分类,vdd,vddx注意不要混淆,不同电位(衬底接不同电压)的n井分开.混合信号的电路尤其注意这点.7 在正确的路径下(一般是进到~/opus)打开icfb.8 更改cell时查看路径,一定要在正确的library下更改,以防copy过来的cell是在其他的library下,被改错.9 将不同电位的N井找出来.布局时注意:10 更改原理图后一定记得check and save11 完成每个cell后要归原点12 DEVICE的个数是否和原理图一至(有并联的管子时注意);各DEVICE的尺寸是否和原理图一至。

一般在拿到原理图之后,会对布局有大概的规划,先画DEVICE,(DIVECE之间不必用最小间距,根据经验考虑连线空间[转帖]layout布局经验总结[ICISEE论坛]/bbs/dispbbs.asp?BoardID=36&id=1012(第1/8 页)2006-7-17 16:01:33[转帖]layout布局经验总结[ICISEE论坛]留出空隙)再连线。

画DEVICE后从EXTRACTED中看参数检验对错。

对每个device器件的各端从什么方向,什么位置与其他物体连线必须先有考虑(与经验及floorplan的水平有关).13 如果一个cell调用其它cell,被调用的cell的vssx,vddx,vssb,vddb如果没有和外层cell连起来,要打上PIN,否则通不过diva检查.尽量在布局低层cell时就连起来。

14 尽量用最上层金属接出PIN。

15 接出去的线拉到cell边缘,布局时记得留出走线空间.16 金属连线不宜过长;17 电容一般最后画,在空档处拼凑。

高速电路板LAYOUT及匹配设计技术

High-Speed Board Design Techniques

INTRODUCTION

The most important factor in the design of many systems today is speed. 66-MHz thru 200-MHz processors are common; 233 and 266-MHz processors are becoming readily available. The demand for high speed results from: a) the requirement that systems perform complex tasks in a time frame considered comfortable by humans; and b) the ability of component manufacturers to produce high-speed devices. An example of a) is the large amount of information that must be processed to perform even the most rudimentary computer animation. Currently, Programmable Array Logic (PAL®) devices are available with propagation delays of 4.5 ns, and complex PLDs such as MACH® have propagation delays of 5 ns. While this might seem fast, it is not the propagation delay that creates the potential for problems, but rather the fast edge rates needed to obtain the fast propagation delays. In the future, much faster devices will become available, with correspondingly faster edge rates. Designing high-speed systems requires not only fast components, but also intelligent and careful design. The analog aspect of the devices is as important as the digital. In high-speed systems, noise generation is a prime concern. The high frequencies can radiate and cause interference. The corresponding fast edge rates can result in ringing, reflections, and crosstalk. If unchecked, this noise can seriously degrade system performance. This application note presents an overview of the design of high-speed systems using a PC-board layout. It covers:

电路版图设计与规则(参考模板)

第三章集成电路版图设计每一个电路都可以做的很完美,对应的版图也可以画的很艺术,需要的是耐心和细心,当然这需要知识,至少我这么认为。

3.1认识设计规则(design rule)什么是设计规则?根据实际工艺水平(包括光刻精度、刻蚀能力、对准容差等)和成品率要求,给出的一组同一工艺层及不同工艺层之间几何尺寸的限制,主要包括线宽、间距、覆盖、露头、凹口、面积等规则,分别给出它们的最小值,以防止掩膜图形的断裂、连接和一些不良物理效应的出现。

芯片上每个器件以及互连线都占有有限的面积。

它们的几何图形形状由电路设计者来确定。

(从图形如何精确地光刻到芯片上出发,可以确定一些对几何图形的最小尺寸限制规则,这些规则被称为设计规则)制定设计规则的目的:使芯片尺寸在尽可能小的前提下,避免线条宽度的偏差和不同层版套准偏差可能带来的问题,尽可能地提高电路制备的成品率。

设计规则中的主要内容:Design Rule通常包括相同层和不同层之间的下列规定:最小线宽 Minimum Width最小间距 Minimum Spacing最小延伸 Minimum Extension最小包围 Minimum Enclosure 最小覆盖 Minimum Overlay集成电路版图设计规则通常由集成电路生产线给出,版图设计者必须严格遵守!!!3.2模拟集成电路版图设计中遵从的法则3.2.1电容的匹配对于IC layout工程师来说正确地构造电容能够达到其它任何集成元件所不能达到的匹配程度。

下面是一些IC版图设计中电容匹配的重要规则。

1)遵循三个匹配原则:它们应该具有相同方向、相同的电容类型以及尽可能的靠近。

这些规则能够有效的减少工艺误差以确保模拟器件的功能。

2)使用单位电容来构造需要匹配的电容,所有需要匹配的电容都应该使用这些单位电容来组成,并且这些电容应该被并联,而不是串联。

3)使用正方块电容,并且四个角最好能够切成45度角。

周长变化是导致不匹配的最主要的随机因素,周长和面积的比值越小,就越容易达到高精度的匹配。

Calibre经典教程和看LVS的错误报告的方式

看calibre lvs 错误报告的方式1.Report开头部份的Warning和Error信息(因为显现Warning和Error的情形很多,那个地址要紧举一些常见的例子):Error部份:只要report的开头部份有Error信息显现,lvs就确信没有运行成功。

Error一样由lvs命令文件或netlist 文件中的参数概念引发,这时需要修改lvs文件或netlist。

Error信息都很直观,比较容易查出产生Error的地址。

o Example1 (参见文件“”) :在””的2191和2192行挪用到了两个标准单元”INLX1”和”LOGICOL”,可是netlist中找不到对这两个标准单元的描述。

那个错误需要检查netlist,添加上对这些标准单元的描述部份。

通常标准单元的netlist由foundry提供,是一个单独的cdl或spice文件;Example1:LVS Netlist Compiler - Errors and Warnings for ""-------------------------------------------------------------Error: No matching ".SUBCKT" statement for "INLX1" at line 2191 in file ""Error: No matching ".SUBCKT" statement for "LOGIC0L" at line 2192 in file ""Warning部份:warning可不能阻碍lvs的运行,可是常常会致使结果的不正确。

很一些warning 能够忽略掉,这些常常是netlist中或lvs命令文件中一些多余部份引发的,例如下面的Example2_1和Example2_2;很多warning是不能忽略的,最多见的是short和soft connect,例如下面的Example3, Example4_1, Example4_2;o Example2_1 (参见文件“”) :那个warning是因为calibre不认netlist中的参数”*.MEGA” ,这时需要在netlist 中注释掉那个参数。

LAYOUT规范

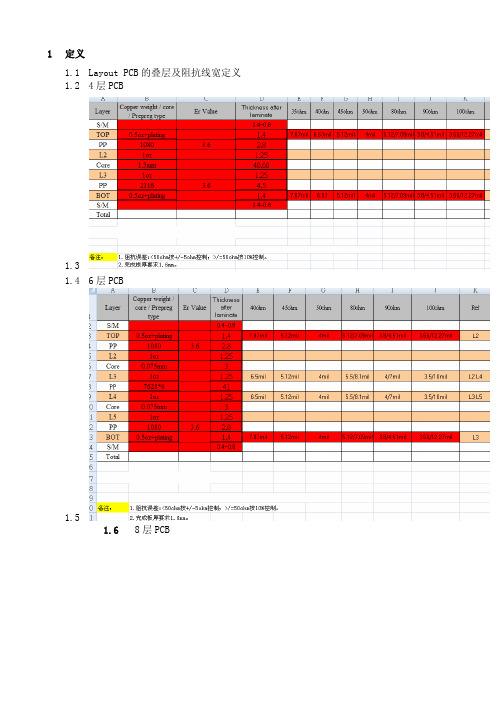

1定义1.1Layout PCB的叠层及阻抗线宽定义1.24层PCB1.31.46层PCB1.51.68层PCB1.7.2要求2.1设计流程:2.1.1 评审通过后的原理图2.1.2 网表2.1.3 PCB 架构(外形尺寸,螺丝孔,定位孔及禁布区)2.1.4 如有增加新器件,需提供新的封装资料(PCB FOOTPRINT)2.1.5 根据单板结构图或对应的标准板框, 创建PCB设计文件2.1.6 布局及布线2.1.7 工艺设计要求2.1.8 设计评审2.2元件的布局:2.2.1创建网络表2.2.1.1 网络表是原理图与PCB的接口文件,PCB设计人员应根据所用的原理图和PCB设计工具的特性,选用正确的网络表格式,创建符合要求的网络表。

2.2.1.2 创建网络表的过程中,应根据原理图设计工具的特性,积极协助原理图设计者排除错误。

保证网络表的正确性和完整性。

2.2.1.3 确定器件的封装(PCB FOOTPRINT).2.2.1.4 创建PCB板 根据单板结构图或对应的标准板框, 创建PCB设计文件;注意正确选定单板坐标原点的位置,原点的设置原则:单板右边和下边的延长线交汇点。

板框四周倒圆角,倒角半径5mm。

特殊情况参考结构设计要求。

2.2.2 布局前设置2.2.2.1 根据结构图设置板框尺寸,按结构要素布置安装孔、接插件等需要定位的器件,并给这些器件赋予不可移动属性。

按工艺设计规范的要求进行尺寸标注。

2.2.2.2 根据结构图和生产加工时所须的夹持边设置印制板的禁止布线区、禁止布局区域。

根据某些元件的特殊要求,设置禁止布线区。

2.2.2.3 综合考虑PCB性能和加工的效率选择加工流程。

加工工艺的优选顺序为:元件面单面贴装——元件面贴、插混装(元件面插装焊接面贴装一次波峰成型)——双面贴装——元件面贴插混装、焊接面贴装。

2.3 布局规则2.3.1遵照“先大后小,先难后易”的布置原则,即重要的单元电路、核心元器件应当优先布局.2.3.2 布局中应参考原理框图,根据单板的主信号流向规律安排主要元器件.2.3.3 布局应尽量满足以下要求:总的连线尽可能短,关键信号线最短;高电压、大电流信号与小电流,低电压的弱信号完全分开;模拟信号与数字信号分开;高频信号与低频信号分开;高频元器件的间隔要充分.2.3.4 相同结构电路部分,尽可能采用“对称式”标准布局;2.3.5 按照均匀分布、重心平衡、版面美观的标准优化布局;2.3.6 器件布局栅格的设置,一般IC器件布局时,格点应为50 mil,小型表面安装器件,如表面贴装元件布局时,格点设置应不少于10mil。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

亚芯 微 电 子 有 限 公 司

Asian Microelectronics Co.,Ltd.

5.dummy器件的详细讲述: 如果周边环境不同,会使工艺中的刻蚀率不同,比如:线宽大, 刻蚀率大,刻蚀的快。刻蚀的快慢会影响线电阻等电学参数。 例子: 尺寸较大的管子被拆成小管子并联时, 尺寸较大的管子被拆成小管子并联时,要在两端的小管的栅旁 加上dummy gate,这样可以保证比较精确的电流匹配。 加上dummy gate,这样可以保证比较精确的电流匹配。 而且这种dummy gate的宽度可以比实际的栅宽小。 而且这种dummy gate的宽度可以比实际的栅宽小。 的宽度可以比实际的栅宽小 各个小管子的gate 最好用metal联起来,如果用poly metal联起来 poly连会引起刻蚀 各个小管子的gate 最好用metal联起来,如果用poly连会引起刻蚀 率的偏差。 率的偏差。 详细图例如下: 详细图例如下:

亚芯 微 电 子 有 限 公 司

Asian Microelectronics Co.,Ltd.

详细的整体布局的考虑因素

a.模块的放置应该与信号的流向一致 ,每个模块一定按照确定好 模块的放置应该与信号的流向一致 的引脚位置引出自己的连线 b.保证主信号信道简单通畅,连线尽量短、少拐弯、等长 连线尽量短、 连线尽量短 少拐弯、 c.不同模块的电源、地分开,以防干扰 ,电源线的寄生电阻尽可 不同模块的电源、 不同模块的电源 地分开, 能减小,避免各模块的电源电压不一致。 d.尽可能把电容、电阻和大管子放在侧旁,利于提高电路的抗干 尽可能把电容、 尽可能把电容 电阻和大管子放在侧旁, 能力。 扰能力。

亚芯 微 电 子 有 限 公 司

Asian Microelectronics Co.,Ltd.

Art of Layout

亚芯 微 电 子 有 限 公 司

Asian Microelectronics Co.,Ltd.

主要工作注意事项

一.画之前的准备工作 二.与circuit designer沟通 三.layout的金属线尤其是电源线、地线 四.保护环 五.衬底噪声 六.管子的匹配精度 七.一般性注意事项 八.有待解决的问题

亚芯 微 电 子 有 限 公 司

Asian Microelectronics Co.,Ltd.

4. N管的周围应该加吸收少子电子的N型保护环(ntap),ntap环接 管的周围应该加吸收少子电子的N型保护环(ntap),ntap环接 ),ntap vdd; 管的周围应该加吸收少子空穴的P型保护环(ptap), vdd;P管的周围应该加吸收少子空穴的P型保护环(ptap), ptap环接gnd。双环对少子的吸收效果比单环好。下图是一个N管 环接gnd ptap环接gnd。双环对少子的吸收效果比单环好 保护环的例子。

亚芯 微 电 子 有 限 公 司

Asian Microelectronics Co.,Ltd.

.信号连线对称的图例

亚芯 微 电 子 有 限 公 司

Asian Microelectronics Co.,Ltd.

ห้องสมุดไป่ตู้

关于寄生电容 a.避免时钟线与信号线的重叠 避免时钟线与信号线的重叠 b.两条信号线应该避免长距离平行,信号线之间交叉对彼此的影 两条信号线应该避免长距离平行, 两条信号线应该避免长距离平行 响比二者平行要小; 响比二者平行要小; c.输入信号线和输出信号线应该避免交叉 输入信号线和输出信号线应该避免交叉; c.输入信号线和输出信号线应该避免交叉; d.对于易受干扰的信号线 在两侧加地线保护; 对于易受干扰的信号线, d.对于易受干扰的信号线,在两侧加地线保护; e.模拟电路的数字部分 需要严格隔离开。 模拟电路的数字部分, e.模拟电路的数字部分,需要严格隔离开。

亚芯 微 电 子 有 限 公 司

Asian Microelectronics Co.,Ltd.

三.layout的金属线尤其是电源线、地线

1.根据电路在最坏情况下的电流值来决定金属线的宽度以及接触孔 根据电路在最坏情况下的电流值来决定金属线的宽度以及接触孔 的排列方式和数目,以避免电迁移。 的排列方式和数目,以避免电迁移 电迁移效应:所谓电迁移效应是指当传输电流过大时,电子 碰撞金属原子,导致原子移位而使金属断线。 在接触孔周围,电流比较集中,电迁移效应更加容易发生。 在接触孔周围,电流比较集中,电迁移效应更加容易发生 2. 避免天线效应 天线效应——长金属线(面积较大的金属线)在刻蚀的时候, 会吸引大量的电荷(因为工艺中刻蚀金属是在强场中进行的), 这时如果该金属直接与管子栅(相当于有栅电容)相连的话,可 能会在栅极形成高电压会影响栅极氧化层的质量,降低电路的可 靠性和寿命。

亚芯 微 电 子 有 限 公 司

Asian Microelectronics Co.,Ltd.

一.Layout之前的准备工作

1.先估算芯片面积: 先分别计算各个电路模块的面积,然后再加上模块之间走 线以及端口引出等的面积,即得到总的芯片面积。 2.Top-Down设计流程: 先根据电路规模对版图进行整体布局,芯片的整体布局包 括主要单元的形状大小以及位置安排 形状大小以及位置安排,电源和地的布局, 形状大小以及位置安排 输入输出引脚的放置等,统计整体芯片的引脚个数 包 引脚个数,包 引脚个数 括测试点也要确定好,严格确定每个模块的引脚属性 引脚属性、 括测试点也要确定好 引脚属性 位置 。

亚芯 微 电 子 有 限 公 司

Asian Microelectronics Co.,Ltd.

3.衬底可靠电位的连接: a.尽量把衬底与电源的接触穿孔(substrate contact)的位置和该位置 尽量把衬底与电源的接触穿孔( contact) 尽量把衬底与电源的接触穿孔 的管子的衬底注入极( injector)的距离缩小,距离越近越好, 的管子的衬底注入极(substrate injector)的距离缩小,距离越近越好 因为这种距离的大小对衬底电位偏差影响非常大。 b.把衬底接触孔的数量增多,尽量多打孔 把衬底接触孔的数量增多, 把衬底接触孔的数量增多 尽量多打孔,保证衬底与电源的接 触电阻较小。

3.芯片金属线存在寄生电阻和寄生电容效应 寄生电阻会使电压产生漂移,导致额外噪声的产生; 寄生电容耦合会使信号之间互相干扰。 关于寄生电阻: a.镜像电流源内部的晶体管在版图上应该放在一起 ,然后通过 镜像电流源内部的晶体管在版图上应该放在一起 连线引到各个需要供电的模块 。 b.加粗金属线 加粗金属线 c.存在对称关系的信号的连线也应该保持对称,使得信号线的寄 存在对称关系的信号的连线也应该保持对称, 存在对称关系的信号的连线也应该保持对称 生电阻保持相等 。

亚芯 微 电 子 有 限 公 司

Asian Microelectronics Co.,Ltd.

四.保护环

1.避免闩锁效应:最常见的Latchup诱因是电源、地的瞬态脉冲,这种 电源、地的瞬态脉冲 电源 瞬态脉冲可能的产生原因是瞬时电源中断等,它可能会使引脚电 位高于vdd或低于vss,容易发生latchup。因此对于电路中有连接到 电源或地的MOS管,周围需要加保护环。 2.容易发生latchup的地方:任何不与power supply、substrate相连的引 脚都可能。所以精度要求高时,要查看是否有引脚引线既不连 power supply,也不连substrate,凡是和这样的引线相连的源区、漏区 都要接保护环。 3.保护环要起到有效的作用就应该使保护环宽度较宽、电阻较低, 保护环要起到有效的作用就应该使保护环宽度较宽、 保护环要起到有效的作用就应该使保护环宽度较宽 电阻较低, 而且用深扩散材料。 而且用深扩散材料

亚芯 微 电 子 有 限 公 司

Asian Microelectronics Co.,Ltd.

.

亚芯 微 电 子 有 限 公 司

Asian Microelectronics Co.,Ltd.

6.主要单元电路的匹配:差分对的管子位置和连线长短都要对称,能合为 分对的管子位置和连线长短都要对称, 分对的管子位置和连线长短都要对称 一条线的连线就要合;差分对主要使V 匹配,而电流镜主要使I 匹配。 一条线的连线就要合;差分对主要使VGS匹配,而电流镜主要使ID匹配 7. MOS匹配的几点注意: a. contact孔、metal走线不要放在有源区内 ,如果metal一定要跨过有源区 contact孔 metal走线不要放在有源区内 如果metal一定要跨过有源区 如果metal 的话,就应该加入dummy 走线。 的话,就应该加入dummy 走线。 b.最好把匹配管子放在远离深扩散边缘的地方,至少要两倍结深。N最好把匹配管子放在远离深扩散边缘的地方,至少要两倍结深。 最好把匹配管子放在远离深扩散边缘的地方 well属于深扩散 PMOS也要放在阱内距离阱边较远处 属于深扩散, 也要放在阱内距离阱边较远处。 well属于深扩散,PMOS也要放在阱内距离阱边较远处。 c.尽量使用NMOS管来作匹配管 因为NMOS PMOS更易达到匹配 尽量使用NMOS管来作匹配管, NMOS比 c.尽量使用NMOS管来作匹配管,因为NMOS比PMOS更易达到匹配 。 d.为避免由gradient引起的mismatch,采用conmmon-centroid layout同心结 为避免由gradient引起的mismatch conmmonlayout同心结 为避免由gradient引起的mismatch,采用conmmon 差分对可用cross pairs结构 结构。 构,且尽量紧密 ,差分对可用cross-coupled pairs结构。 差分对可用crosse.匹配器件要远离功率器件摆放,功耗大于50mw的就属于功率器件。 匹配器件要远离功率器件摆放, 匹配器件要远离功率器件摆放

亚芯 微 电 子 有 限 公 司

Asian Microelectronics Co.,Ltd.

二.与circuit designer沟通