89C51 CPU核及片上系统设计

89c51芯片资料

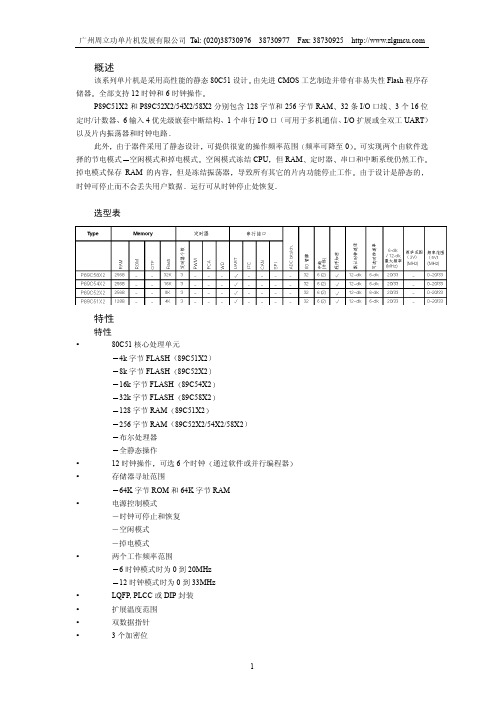

概述该系列单片机是采用高性能的静态80C51设计由先进CMOS工艺制造并带有非易失性Flash程序存储器全部支持12时钟和6时钟操作P89C51X2和P89C52X2/54X2/58X2分别包含128字节和256字节RAM32条I/O口线3个16位定时/计数器6输入4优先级嵌套中断结构1个串行I/O口可用于多机通信I/O扩展或全双工UART以及片内振荡器和时钟电路此外由于器件采用了静态设计可提供很宽的操作频率范围频率可降至0可实现两个由软件选择的节电模式空闲模式和掉电模式空闲模式冻结CPU但RAM定时器串口和中断系统仍然工作掉电模式保存RAM的内容但是冻结振荡器导致所有其它的片内功能停止工作由于设计是静态的时钟可停止而不会丢失用户数据运行可从时钟停止处恢复选型表特性特性y 80C51核心处理单元4k字节FLASH89C51X28k字节FLASH89C52X216k字节FLASH89C54X232k字节FLASH89C58X2128字节RAM89C51X2256字节RAM89C52X2/54X2/58X2布尔处理器全静态操作y 12时钟操作可选6个时钟通过软件或并行编程器y 存储器寻址范围64K字节ROM和64K字节RAMy 电源控制模式―时钟可停止和恢复―空闲模式―掉电模式y 两个工作频率范围6时钟模式时为0到20MHz12时钟模式时为0到33MHzy LQFP, PLCC或DIP封装y 扩展温度范围y 双数据指针y 3个加密位y 4个中断优先级y 6个中断源y 4个8位I/O口y 全双工增强型UART―帧数据错误检测―自动地址识别y 3个16位定时/计数器T0T1标准80C51和增加的T2捕获和比较y 可编程时钟输出y 异步端口复位y 低EMI (禁止ALE以及6时钟模式)y 掉电模式可通过外部中断唤醒订购信息P89C51X24K字节FLASH类型编号封装温度范围()P89C51X2BA PLCC44 0~+70P89C51X2BN DIP40 0~+70P89C51X2BBD LQFP44 0~+70P89C51X2FA PLCC44 -40~+85 P89C52X28K字节FLASH类型编号封装温度范围()P89C52X2BA PLCC44 0~+70P89C52X2BN DIP40 0~+70P89C52X2BBD LQFP44 0~+70P89C52X2FA PLCC44 -40~+85 P89C52X2FN DIP40 -40~+85 P89C52X2FBD LQFP44 -40~+85 P89C54X216K字节FLASH类型编号封装温度范围()P89C54X2BA PLCC44 0~+70P89C54X2BN DIP40 0~+70P89C54X2BBD LQFP44 0~+70P89C54X2FA PLCC44 -40~+85 P89C58X232K字节FLASH类型编号封装温度范围()P89C58X2BA PLCC44 0~+70P89C58X2BN DIP40 0~+70P89C58X2BBD LQFP44 0~+70P89C58X2FA PLCC44 -40~+85B=07040+85下表所示为操作模式电源电压以及最大外部时钟频率之间的关系操作模式电源电压最大时钟频率6-clock 5V10% 20MHz 12-clock 5V10% 33MHz框图1逻辑符号PLCC和CLCC封装及管脚功能DIP 封装及管脚功能 LQFP 封装及管脚功能管脚描述 管脚号名称 DIP LCC QFP 类型 名称和功能Vss 20 22 16I地 Vcc 40 44 38 I电源提供掉电空闲正常工作电压P0.0-0.739-32 43-36 37-30 I/O P0口 P0口是开漏双向口可以写为1使其状态为悬浮用作高阻输入P0也可以在访问外部程序存储器时作地址的低字节在访问外部数据存储器时作数据总线此时通过内部强上拉输出1P1.0-1.7 1-8 1 22-92 340-44 1-3I/O P1口 P1口是带内部上拉的双向I/O 口向P1口写入1时P1口被内部上拉为高电平可用作输入口当作为输入脚时被外部拉低的P1口会因为内部上拉而输出电流(见DC 电气特性)P1口第2功能T2(P1.0) 定时/计数器2的外部计数输入/时钟输出(见可编程输出)T2EX(P1.1)定时/计数器2重装载/捕捉/方向控制P2.0-2.7 21-28 24-31 18-25 I/O P2口 P2口是带内部上拉的双向I/O 口向P2口写入1时P2口被内部上拉为高电平可用作输入口当作为输入脚时被外部拉低的P2口会因为内部上拉而输出电流(见DC 电气特性)在访问外部程序存储器和外部数据时分别作为地址高位字节和16位地址(MOVX @DPTR)此时通过内部强上拉传送1当使用8位寻址方式(MOV@Ri)访问外部数据存储器时,P2口发送P2特殊功能寄存器的内容P3口P3口被内部上拉为高电平可用作输入口输入脚时口会因为内部上拉而输出电电气特性)串行输入口INT0(P3.2)INT1(P3.3)WR(P3.6)当晶振在运行中期高电平即可复位内部有扩散电阻连接到VssVcc输出脉冲锁存地在正常情况下ALE输出信号恒定为并可用作外部时钟或定时注意每次访问外部数据时一个ALE可以通过置位ALE只能在执行程序存储使能当执行外部程序存储器代码时个机器周期被激活两次在访问外部数据存储器时访问内部程序存储器时外部寻址使能在访问整个外部程序存储器时如果EA将执行内部程序除非程序计数器包含大于片内FLASH的地址该引脚在(Vpp)如果保密位已编程在复位时由内部锁存反相振荡放大器输入和内部时钟发生电路输入反相振荡放大器输出注: 为了避免上电时的”latch-up”效应任意管脚Vpp除外上的电压任何时候都不能高于Vcc+0.5V低于Vss-0.5V表1 P89C51X2/52X2/54X2/58X2 特殊功能寄存器双字节指针高字节*号的#80C51修改而来或新增加的表示保留位1复位值由复位源确定存储器的内容存储单先进的沟道氧化工艺和低内部电场的结合使擦除和编程操作特性y 可编程加密位y 每字节最少10000次擦除/编程周期 y 数据最少可保存10年y 从一般销售商处可获得编程支持振荡器特性XTAL1和XTAL2为输入和输出可分别作为一个反相放大器的输入和输出此管脚可配置为使用内部振荡器要使用外部时钟源驱动器件时XTAL2可以不连接而由XTAL1驱动外部时钟信号无占空比的要求因为时钟通过触发器二分频输入到内部时钟电路但高低电平的最长和最短时间必须符合手册的规定时钟控制寄存器CKCON该器件提供通过一个SFR 位CKCON 的X2位和一个Flash 位保密块中的FX2控制选择6时钟/12时钟模式当X2置0时12时钟模式有效该位置1时系统切换到6时钟模式由于该功能是通过SFR 位实现的因此可以随时访问并修改需要注意的是将X2从0改为1将导致用户代码以两倍的速度执行因为所有的系统时间间隔都变成原来的1/2从6时钟模式变为12时钟模式会将运行代码的速度降低为1/2Flash 时钟控制位FX2可通过并行编程器编程取代X2位实现6时钟模式见表2表2FX2时钟模式位只能通过并行编程器设置X2位CKCON.0CPU 时钟模式擦除 0 12时钟模式默认擦除 1 6时钟模式 编程 X 6时钟模式可编程时钟输出可从P1.0编程输出50%占空比的时钟信号P1.0除了作为常规I/O 口外还有两个可选功能它可编程为1用于定时/计数器2的外部时钟输入2使用16MHz操作频率时12时钟模式下输出50%占空比的61Hz~4MHz时钟信号6时钟模式时为122Hz~8MHz要将定时/计数器2配置为时钟发生器C/T2(T2CON.1)必须清零而T2MOD中的T20E位必须置位要启动定时器2还必须将TR2(T2CON.2)置位时钟输出频率由振荡器频率和定时器2捕获寄存器的重新装入值确定公式如下振荡器频率n65536RCAP2H,RCAP2L此处n = 166时钟模式或3212时钟模式RCAP2H,RCAP2L RCAP2H和RCAP2L的内容作为一个16位无符号整数在时钟输出模式中定时器2的翻转将不会产生中断这和它作为波特率发生器时相似定时器2可同时作为波特率发生器和时钟发生器但需要注意的是波特率和时钟输出频率相同复位在振荡器工作时将RST脚保持至少两个机器周期高电平12时钟模式为24个振荡器周期6时钟模式为12振荡器周期可实现复位为了保证上电复位的可靠RST保持高电平的时间至少为振荡器启动时间通常为几个毫秒再加上两个机器周期复位后振荡器以12时钟模式运行当已通过并行编程器设置为6时钟模式时除外低功耗模式时钟停止模式静态设计使时钟频率可以降至0MHz(停止)当振荡器停振时RAM和SFR的值保持不变该模式允许逐步应用并可将时钟频率降至任意值以实现系统功耗的降低如要实现最低功耗则建议使用掉电模式空闲模式空闲模式见表3中CPU进入睡眠状态但片内的外围电路仍然保持工作状态正常操作模式的最后一条指令执行进入空闲模式空闲模式下CPU内容片内RAM和所有SFR保持原来的值任何被使能的中断此时程序从中断服务程序处恢复并继续执行或硬件复位与上电复位使用相同的方式启动处理器均可终止空闲模式掉电模式为了进一步降低功耗通过软件可实现掉电模式(见表3)该模式中振荡器停振并且在最后一条指令执行进入掉电模式降到2.0V时片内RAM和SFR保持原值在退出掉电模式之前Vcc必须升至规定的最低操作电压硬件复位或外部中断均可结束掉电模式硬件复位使所有的SFR重新设置但不改变片内RAM的值外部中断允许SFR和片内RAM都保持原值WUPD AUXR1.3从掉电唤醒使能或禁止通过外部中断唤醒掉电WUPD0禁止WUPD=1使能要正确退出掉电模式在Vcc恢复到正常操作电压范围之后复位或外部中断开始执行并且要保持足够长的时间 ( 通常小于10ms )以使振荡器重新启动并稳定下来使用外部中断退出掉电模式时INT0和INT1必须使能且配置为电平触发将管脚电平拉低使振荡器重新启动退出掉电模式后将管脚恢复为高电平一旦中断被响应RETI之后所执行的是进入掉电模式指令的后一条指令表3 空闲模式和掉电模式时外部管脚的状态器件在内部复位之前从停止处恢复程序正常运行时间为这段时间内片内硬件禁止对内部RAM但对当Idle模式被复位所中为了消除可能产生的误写操作应用模式指令后的指令不应执行写I/O口或写外部存储器操作进入件将ALE保持低电平模式时口处于悬浮状态持工作状态器件处于该模式时可用仿真器或测试CPU驱动电路执行正常复位时恢复正常操作定时器0和1的操作定时器0和1定时和计数功能由特殊功能寄存器TMOD的控制位C/T进行选择这两个定时/计数器有4种操作模式通过TMOD的M1和M0选择两个定时/计数器的模式01和2都相同模式3不同如下所述模式0将定时器设置成模式0时类似8048定时器即8 位计数器带32分频的预分频器图2所示为模式0工作方式此模式下定时器寄存器配置为13位寄存器当计数从全为1翻转为全为0时定时器中断标志位TFn置位当TRn=1同时GATE=0或INTn=1时定时器计数置位GATE时允许由外部输入INTn 控制定时器这样可实现脉宽测量TRn为TCON寄存器内的控制位图3该13位寄存器包含THn全部8个位及TLn的低5位TLn的高3位不定可将其忽略置位运行标志TRn不能清零此寄存器模式0的操作对于定时器0及定时器1都是相同的两个不同的GATE位TMOD.7和TMOD.3分别分配给定时器0及定时器1模式1模式1除了使用了THn及TLn全部16位外其它与模式0相同模式2此模式下定时器寄存器作为可自动重装的8位计数器TLn如图4所示TLn的溢出不仅置位TFn而且将THn内容重新装入TLn THn内容由软件预置重装时THn内容不变模式2的操作对于定时器0及定时器1是相同的模式3在模式3中定时器1停止计数效果与将TR1设置为0相同此模式下定时器0的TL0及TH0作为两个独立的8位计数器图5为模式3时的定时器0逻辑TL0C/T GATETR0TH0TF1此时TH0控制定时器中断可用于需要一个额外的位定时器的场合定时器时80C513个定时计数器当定时器时定时器可通过开关进入它仍可用作串行端口的波特或者应用于任何不要求中断的场合复位值2 1 0 置位时只有在计数器清零时计数器用作定时器或计数器清零则用作定时器从内部系统时钟输入置位用作计数器从脚输入定时器模式选择定时器模式无预分频器当溢出时将计数器控制位控制1控制位控制图1 定时/计数器0/1模式控制寄存器TMOD图2 定时/计数器0/1的模式013位定时/计数器InterruptTCON 地址88H 7 6 5 4 3 2 1 0 可位寻址 复位值00HTF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0位符号功能TCON.7 TF1定时器1溢出标志定时/计数器溢出时由硬件置位中断处理时由硬件清除或用软件清除TCON.6 TR1定时器1运行控制位由软件置位/清零将定时/计数器打开/关闭TCON.5 TF0定时器0溢出标志定时/计数器溢出时由硬件置位中断处理时由硬件清除或用软件清除 TCON.4 TR0定时器0运行控制位由软件置位/清零将定时/计数器打开/关闭 TCON.3 IE1 中断1边沿触发标志当检测到外部中断1边沿时由硬件置位中断处理时清零TCON.2 IT1 中断1触发类型控制位由软件置位/清零以选择外部中断以下降沿/低电平方式触发TCON.1 IE0 中断0边沿触发标志当检测到外部中断0边沿时由硬件置位中断处理时清零TCON.0 IT0 中断0触发类型控制位由软件置位/清零以选择外部中断以下降沿/低电平方式触发图3 定时器/计数器控制寄存器TCON图4 定时/计数器0/1的模式28位自动重装Interrupt通过设置特殊功能寄存器位可将其作为定时见图6定时器有三种操作模式捕获递增或递减计数和波特率发生这三种模式由T2CON 中的位进行选择见表3捕获模式 通过EXEN2设置两个选项如果定时器16位由T2CON TF2溢出标志位该位可用于产生IE 中断使能位如果EXEN21与以上描述相同即外部输入时将定时器2TL2和的当前值各自捕获到RCAP2L EXF22溢出中断地址相同定时器中断服务程序通过查询来确定引起中断的事件捕获模式如图在该模式中TL2计数器仍以的负跳变或振荡频率的1/12或6时钟模式递增递减计数器位自动重装模式中2可通过C/T2配置为定时器计数的方向是由DCEN 递减计数使能位确定的DCEN 位于T2MOD 寄存器见图8中当DCEN 0时定时器2默认为向上计数当DCEN 1时定时器2可通过T2EX 确定递增或递减计数图9显示了当DCEN 0时定时器2自动递增计数在该模式中通过设置EXEN2位进行选择如果EXEN2定时器2递增计数到0FFFFH 并在溢出后将TF2置位然后将RCAP2L 和RCAP2H 中的16位值作为重新装载值装入定时器2RCAP2L 和RCAP2H 的值是通过软件预设的如果EXEN2116位重新装载可通过溢出或T2EX 从10的负跳变实现此负跳变同时将EXF2置位如果定时器2中断被使能则当TF2或EXF2置1时产生中断在图10中DCEN 1时定时器2可递增或递减计数此模式允许T2EX 控制计数的方向当T2EX 置1时定时器2递增计数计数到0FFFFH 后溢出并置位TF2还将产生中断如果中断被使能定时InterruptInterrupt器2的溢出将使RCAP2L 和RCAP2H 中的16位值作为重新装载值放入TL2和TH2当T2EX 置零时将使定时器2递减计数当TL2和TH2计数到等于RCAP2L 和RCAP2H 时定时器产生溢出定时器2溢出置位TF2并将0FFFFH 重新装入TL2和TH2当定时器2递增/递减产生溢出时外部标志位EXF2翻转如果需要可将EXF2位作为第17位在此模式中EXF2标志不会产生中断表4 定时器2工作方式图6 定时器/计数器2T2CON 控制寄存器溢出标志定时器溢出时置位必须由软件清除当TCLK 1时TF2将不会置位外部标志当EXEN21且的负跳变产生捕获或重装时置位定时器2中断使能时EXF21从中断向量处执行中断子程序EXF2位必须用软件清零在递增式DCEN 1中EXF2不会引起中断接收时钟标志RCLK 置位时定时器的溢出脉冲作为串行口模式模式的接收时钟RCLK 0时将定时器的溢出脉冲作为接收时钟发送时钟标志TCLK 置位时定时器和的发送时钟TCLK 0时将定时器的溢出脉冲作为发送时钟外部使能标志当其置位且定时器未作为串行口时钟时允的负跳变产生捕获或重装EXEN20时T2EX 的跳变对定时无效启动停止控制位置时启动定时器计数器选择定时器20内部定时器OSC/12或OSC/61外部事件计数器下降沿触发重装标志置位EXEN21T2EX 的负跳变产生捕获清零EXEN21时定时器2溢出或的负跳变都可使定时器自动重装RCLK 1TCLK 1时该位无效且定时器强制为溢出时自动重装图7 定时器2捕获模式保留将来之用2输出使能位定时器这些位在将来8051这种情况下以后用到复位时或非有效状态时而这些位为有效状态时它的值为1从保留位读到的值是不确定的图8 定时器2模式T2MOD 控制寄存器图9 定时器2自动重装模式DCEN=0EXEN 2T imer 2InterruptEXEN 2T IME R2图10 定时器2自动重装模式DCEN=1图11 定时器2波特率发生器模式波特率发生器模式寄存器T2CON 的位TCLK 和或RCLK 见表3允许从定时器1或定时器2获得串行口发送和接收的波特率当TCLK=0时定时器1作为串行口发送波特率发生器当TCLK=1时定时器2作为串行口发送波特率发生器RCLK 对串行口接收波特率有同样的作用通过这两位串行口能得到不同的接收和发送波特率 一个通过定时器1产生另一个通过定时器2产生图11所示为定时器2工作在波特率发生器模式与自动重装模式相似当TH2溢出时波特率发生器模式使定时器2寄存器重新装载来自寄存器RCAP2H 和RCAP2L 的16位的值寄存器RCAP2H 和RCAP2LR 的值由软件预置当工作于模式1和模式3时波特率由下面给出的定时器2溢出率所决定定时器2溢出速率16定时器可配置成定时或计数方式在许多应用上定时器被设置在定时方式C/T2*=0当定时器2作为定时器时它的操作不同于波特率发生器通常定时器2作为定时器它会在每个机器周期递增1/6或1/12振荡频率当定时器2作为波特率发生器时它会在每个状态周期递增例如1/2振荡频率这样波特率公式如下模式1和模式3的波特率=(UP C OUNTING R E LOADV ALUE)T2EX PINEXEN 2RXClock TXClockT imer 1OverflowNote availability of additional external interrupt.[65536n = 166或12时钟模式RCAP2H,RCAP2L)=RCAP2H 的内容为11所示定时器作为波特率发生器仅当寄存器RCLK 和或TCLK=1定作为波特率发生器才有效溢出并不置位TF2也不产生中断这样当定时器中断不必被禁止外部使能标志被置位在中1的转换会置位EXF2T2外部标志位但并不导致TH2重装载RCAP2H RCAP2L因当定时器用作波特率发生器时如果需要可用作附加的外部中断当计时器工作在波特率发生器模式下,则不要对TH2和进行读写每隔一个状态时间或定时器在此情况下对进行读写是不准确的可对RCAP2但不要进行写否则将导致自动重装错误当对定时器进行访问时应关闭定清零表列出了常用的波特率和如何用定时器得到这些波特率表由定时器外部时钟信号由波特率为2溢出率则波特率为[n[65536(RCAP2H,RCAP2L)]]此处 n = 166时钟模式或3212时钟模式f OSC = 振荡器频率 自动重装值可由下式得到RCAP2H,RCAP2L=65536-[fosc/(n波特率)]定时器/计数器2的设置除了波特率发生器模式T2CON 不包括TR2位的设置TR2位需单独设置来启动定时器表6表7给出了T2作为定时器和计数器的设置表6 T2作为定时器T2CON模式内部控制注1外部控制注216位重装00H 08H16位捕获01H 09H波特率发生器接收和发送相同波特率34H 36H只接收24H 26H只发送14H 16H 表7 T2作为计数器TMOD模式内部控制注1外部控制注216位02H 0AH自动重装03H 0BH注1.仅当定时器溢出时进行捕获和重装2.当定时/计数器溢出并且T2EX(P1.1)发生电平负跳变时产生捕获和重装定时器2用于波特率发生器模式除外全双工增强型UART标准UART操作串口为全双工结构表示可以同时发送和接收它还具有接收缓冲在第一个字节从寄存器读出之前可以开始接收第二个字节但是如果第二个字节接收完毕时第一个字节仍未读出其中一个字节将会丢失串口的发送和接收寄存器都是通过SFR SBUF进行访问的写入SBUF的数据装入发送寄存器对SBUF 的读操作是对物理上分开的接收寄存器进行访问串口有4种操作模式模式0串行数据通过RxD进出TxD输出时钟每次发送或接收以LSB最低位作首位每次8位波特率固定为MCU时钟频率的1/12模式1TxD脚发送RxD脚接收每次数据为10位一个起始位08个数据位LSB在前及一个停止位1当接收数据时停止位存于SCON的RB8内波特率可变由定时器1溢出速率决定模式2TxD脚发送RxD脚接收每次数据为11位一个起始位08个数据位LSB在前一个可编程第9位数据及一个停止位1发送时第9个数据位SCON内TB8位可置为0或1例如将奇偶位PSW内P位移至TB8接收时第9位数据存入SCON的RB8位停止位忽略波特率可编程为MCU时钟频率的1/32或1/64由PCON内SMOD1位决定模式3TxD脚发送RxD脚接收每次数据为11位一个起始位08个数据位LSB为首位一可编程的第9位数据及一个停止位1事实上模式3除了波特率外均与模式2相同其波特率可变并由定时器1溢出率决定在上述4种模式中发送过程是以任意一条以写SBUF作为目标寄存器的指令开始的模式0时接收通过设置R1=0及REN=1初始化其它模式下如若REN=1则通过起始位初始化多机通信UART模式2及模式3有一个专门的应用领域即多机通信在这些模式时接收为9位数据第9位存入RB8接下来为停止位UART可编程为接收到停止位时仅当RB8=1时串口中断才有效可通过置位SCON内SM2位来选择这一特性下述为多机系统利用这一特性的一种方法当主机需要发送一数据块给数台从机之一时首先发送出一个地址字节对目标从机进行识别地址与数据字节通过第9位数据区别其中地址字节的第9位为1而数据字节为0SM2=1时数据字节不会使各从机产生中断而地址字节则令所有从机中断这样各从机可以检查接收到的数据判断是否被寻址被寻址的从机即可清除SM2位以准备接收随后数据内容未被寻址的从机的SM2位仍为1则不理睬随后数据继续各自工作模式0时SM2无效模式1时SM2用于检验停止位是否有效在模式1时如果SM2=1那么只有接收到有效的结束位才可产生接收中断串行端口控制寄存器SCON串行端口控制及状态寄存器即SCON如图12所示其中包括模式选择位以及发送和接收的第9位数据TB8及RB8以及串行端口中断位TI及RISCON 地址98H7 6 5 4 3 2 1 0可位寻址复位值 00H SM0/FE SM1 SM2 REN TB8 RB8 TI RI 位符号功能SCON.7 FE 帧错误位当检测到一个无效停止位时通过UART接收器设置该位但它必须由软件清零要使该位有效PCON寄存器中的SMOD0位必须置1SCON.7 SM0 和SM1定义串口操作模式要使该位有效PCON寄存器中的SMOD0必须置0SCON.6 SM1 和SM0定义串行口操作模式见下表SM0 SM1 UART模式波特率0 0 0同步移位寄存器fosc/12或fosc/6取决于时钟模式0 1 18位UART 可变1 0 29位UART fosc /64或fosc /321 1 39位UART 可变SCON.5 SM2 在模式2和3中多处理机通信使能位在模式2或3中若SM2=1且接收到的第9位数据RB8是0则RI接收中断标志不会被激活在模式1中若SM2=1且没有接收到有效的停止位则RI不会被激活在模式0中SM2必须是0SCON.4 REN 允许接收位由软件置位或清除REN=1时允许接收REN=0时禁止接收SCON.3 TB8 模式2和3中发送的第9位数据可以按需要由软件置位或清除SCON.2 RB8 模式2和3中已接收的第9位数据在模式1中或sm2=0RB8是已接收的停止位在模式0中RB8未用SCON.1 TI 发送中断标志模式0中在发送完第8位数据时由硬件置位其它模式中在发送停止位之初由硬件置位在任何模式中都必须由软件来清除TISCON. 0 RI 接收中断标志模式0中接收第8位结束时由硬件置位其它模式中在接收停止位的中间时刻由硬件置位在任何模式(SM2所述情况除外)必须由软件清除RI图12 串行控制寄存器SCON波特率操作模式0的波特率是固定的为fosc/12模式2的波特率是MCU 时钟/64或MCU 时钟/32取决于PCON 寄存器中的SMOD1位的值若SMOD1=0复位值波特率为MCU 时钟/64若SMOD1=1波特率为MCU时钟/32在80C51中模式1和模式3的波特率由定时器1的溢出速率决定使用定时器1作波特率发生器 当定时器1用作波特率发生器模式1和3中波特率由定时器1的溢出速率和SMOD1的值决定在此应用中定时器1不能用作中断定时器1可以工作在定时或计数方式和3种工作模式中任何一个在最典型应用中它用作定时器方式工作自动重装载模式TMOD 的高半字节为0010B 它的波特率值由下式给出可以定时器1的中断实现非常低的波特率将定时器配置为16位定时器TMOD 的高半字节为0001B并使用中断进行16位软件重装图13列出了几个常用的波特率以及如何从定时器1获得OS CSMOD图13 由定时器1产生的通用波特率UART 模式0串行数据由RxD 端出入TxD 输出同步移位时钟发送或接收的是8位数据低位在先其波特率固定为MCU 时钟的1/12图14是串行口模式0的功能方框简图及相关的时序图执行任何一条把SBUF 作为目的寄存器的指令时就开始发送S6P2时刻的写SBUF 信号将1装入发送移位寄存器的第9位并通知发送控制部分开始发送写SBUF 信号有效后一个完整的机器周期后SEND 端有效SEND 使能RxD P3.0端送出数据TxD P3.1输出移位时钟每个机器周期的S3S4及S5状态内移位时钟为低电平而S6S1及S2状态内为高在SEND 有效时每一机器周期的S6P2时刻发送移位寄存器的内容右移一位数据位向右移时左边添加零当数据字节最高位MSB 移到移位寄存器的输出端时其左边是装入1的第9位再左的内容均为0, 此时通知Tx 控制模块进行最后一位移位处理后禁止SEND 并置位T1, 所有这些步骤均在写入SBUF 后第10个机器周期的S1P1时进行的接收初始化条件是REN=1及R1=0下一机器周期的S6P2时RX 控制单元向接收移位寄存器写入1111 1110并在下一个时钟使RECEIVE 端有效RECEIVE 使能移位时钟转换P3.1功能移位时钟在每个机器周期的S3P1及S6P1跳变在RECEIVE 有效时每一机器周期的S6P2时刻接收移位寄存器内容向左移一位从右移位进来的值是该机器周期S5P2。

基于单片机的智能水灾报警系统的设计

我国地处季风气候区,暴雨洪水频发。

受季风气候影响,我国大部分地区夏季湿热多雨、雨热同期,不仅短历时、高强度的局地暴雨频繁发生,而且长历时、大范围的全流域降雨也时有发生,几乎每年都会发生不同程度的洪涝灾害。

因此,完善的水情监测有助于中心站实时监测各地水情,并对各种突发状况做出及时、合理的措施来防止灾害的发生和降低灾害所造成的破坏。

本次设计以AT89C51芯片为核心,辅以相关的外围电路,设计了以单片机为核心的水情监测系统。

系统由12V直流电源供电。

在硬件方面,除了单片机外,采用SDI-12总线来连接多个传感器,通过TDC40 (SDI-12 to RS232转换器)将传感器采集到的水情数据发送到单片机PO口,单片机通过FLASH存储实时数据,亦可通过PSTN, GSM、北斗卫星、海事卫星等通信信道将采集到的水情数据传输到中心站。

在软件方面,采用C语言编程。

通过对单片机程序设计实现对水情监测系统的整个水情数据的采集、存储和传输程序进行监测、判断和控制以及人机交换。

关键词: 单片机 SDI-12 数据采集水情监测C hina is located in the monsoon climate zone and torrential rain and flood often happens .Affected by this monsoon climate, most of our region is hot wet and more rain in summer .Not only for short duration, high strength local rainstorm often happens, but also rain in wide range of the valley with long duration often happens .Annually, floods disaster happens in large range of our nation with varying degrees. Therefore, Perfect hydrological monitoring can help real-time monitoring hydrological in all regions with the central station and Make timely and reasonable measures for a variety of unexpected situations to prevent disasters and reduce the damage caused by disasters.The design use the AT89C51 chip as the core, combined with the necessary peripheral circuits .We design the hydrological monitoring system with 51 MCU as a core. It consists of 12V DC power supply. On the hardware side, in addition to MCU, It uses SDI-12 bus to connect multiple sensors .Collected by TDC40(SDI-12 to RS232 converter) the water level sensor data is sent to the MCU ports PO .The MCU use FLASH to store real-time data and transport the collected water level data to the central station through communication channel, such as the PSTN, GSM, COMPASS satellite, maritime satellite and so on. On the software side, we use C language for programming. By programming on the MCU, we realize hydrological monitoring system for the entire hydrological data collection, storage and transport procedures for monitoring, to determine and control and human exchange.Key word:MCU SDI-12 data acquisition water level monitoring目录第一章绪言 (1)第二章单片机89C51简介 (2)第一节单片机的特点 (2)第二节单片机89C51介绍 (2)第三章基于单片机的水灾监测技术 (4)第一节AT89C51内部结构 (4)第二节AT89C51引脚及功能 (5)第三节时钟震荡电路设计 (7)第四节电源电路设计 (7)第四章A/D转换器TLC2543 (12)第一节TLC2543的编程要点 (12)第二节TLC2543与51系列单片机接口 (13)第三节数据采集程序设计 (14)第五章系统设计 (16)第一节系统设计思路 (16)第二节系统设计框图 (16)第三节系统硬件设计 (17)第四节系统软件设计 (17)结论 (19)致谢 (20)参考文献 (21)第一章绪言目前,国内许多水文站监测水位和降雨量仍采用人工方法。

第2章 89C51单片机硬件结构和原理

2.累加器A 使用最频繁的寄存器,可写为Acc。“A”与“Acc” 书写上 的差别,将在第3章介绍。

作用如下:

(1)ALU单元的输入数据源之一,又是ALU运算结果存放单元。 (2)数据传送大多都通过累加器A,相当于数据的中转站。为 解决“瓶颈堵塞”问题,AT89S51增加了一部分可以不经过 累加器的传送指令。

18

PSW中各个位的功能: (1)Cy(PSW.7)进位标志位

可写为C。在算术和逻辑运算时,若有进位/借位,Cy=1;

否则,Cy=0。在位处理器中,它是位累加器。 (2)Ac(PSW.6)辅助进位标志位 在BCD码运算时,用作十进位调整。即当D3位向D4位产生进 位或借位时,Ac=1;否则,Ac=0。 (3)F0(PSW.5)用户设定标志位 由用户使用的一个状态标志位,可用指令来使它置1或清0, 控制程序的流向。用户应充分利用。

端(12-21V)。

4、I/O端口P0、P1、P2和P3 准双向的含义:

当I/O口作为输入时,应先向此口锁存器写入全1, 此 时该口引脚浮空,可作高阻抗输入。

1)P0口:用作通用的I/O口;当外扩存储器及I/O接口芯片时,P0口作为低8位地址 总线及数据总线的分时复用端口。 2)P1口:用作通用的I/O口 3)P2口:用作通用的I/O口;当外扩存储器及I/O接口芯片时,P2口作为高8位地址 总线 4)P3口:用作通用的I/O口;每个引脚有第二功能

图2-6 高128字节RAM(SFR区)

1、堆栈指针SP

堆栈指针SP(8位),可指向片内RAM00H~7FH的任何单元。系统 复位后,SP指向07H的RAM单元,所以入栈的第一个数据位于08H单元。

堆栈:在片内RAM区专门开辟的一个区域,数据的存取是按“后进先

毕业设计(论文)-基于51单片机的电梯智能控制系统设计

摘要在现代电梯智能控制系统大多采用PLC智能控制,PLC具有稳定的多I/O 口输出控制,容易操作与调试,易于远程操作及监控等优点,但PLC造价高,市场上一般16点的PLC造价就至少上百元,而大多进口的西门子,欧姆龙系列就不用说了,故在小系统中,采用PLC控制不太合适。

本系统采用AT89C51进行智能控制,成本超低,但性能亦很稳定,并具有系统崩溃自锁功能,整体性能比利用PLC更优惠。

关键字:AT89C51,电机控制,24c02目录摘要 (1)目录 (2)一系统设计方案 (3)1.单片机控制系统总体框图 (3)2.电机驱动系统设计框图 (3)二元器件简介 (4)1.AT89C51的单片机简介 (4)(1)主要特性 (5)(2)管脚说明 (5)(3)振荡器特性 (8)(4)芯片擦除 (8)2.存储器24c02 (9)三电梯智能控制系统设计 (13)1.硬件电路设计 (13)(1)单片机最小系统 (13)(2)继电器控制电路的设计 (14)(3)红外检测系统 (14)(4)系统供电电源 (15)2.系统软件设计 (15)(1)软件介绍 (15)(2)程序流程图 (15)(3)程序清单 (16)四调试过程 (17)1.检测AT89C51运行否 (17)2.红外检测测试 (17)总结 (18)参考文献 (19)一系统设计方案1.单片机控制系统总体框图2.电机驱动系统设计框图二元器件简介1.AT89C51的单片机简介AT89C51是一种带4K字节闪烁可编程可擦除只读存储器(FPEROM—Falsh Programmable and Erasable Read Only Memory)的低电压,高性能CMOS8位微处理器,俗称单片机。

AT89C2051是一种带2K字节闪烁可编程可擦除只读存储器的单片机。

单片机的可擦除只读存储器可以反复擦除100次。

该器件采用ATMEL 高密度非易失存储器制造技术制造,与工业标准的MCS-51指令集和输出管脚相兼容。

AT89C51单片机的基本结构和工作原理

A T89C51单片机的主要工作特性:·内含4KB的FLASH存储器,擦写次数1000次;·内含28字节的RAM;·具有32根可编程I/O线;·具有2个16位可编程定时器;·具有6个中断源、5个中断矢量、2级优先权的中断结构;·具有1个全双工的可编程串行通信接口;·具有一个数据指针DPTR;·两种低功耗工作模式,即空闲模式和掉电模式;·具有可编程的3级程序锁定定位;AT89C51的工作电源电压为5(1±0.2)V且典型值为5V,最高工作频率为24MHz.AT89C51各部分的组成及功能:1.单片机的中央处理器(CPU)是单片机的核心,完成运算和操作控制,主要包括运算器和(1)运算器运算器主要用来实现算术、逻辑运算和位操作。

其中包括算术和逻辑运算单元ALU、累加器ACC、B寄存器、程序状态字PSW和两个暂存器等。

ALU是运算电路的核心,实质上是一个全加器,完成基本的算术和逻辑运算。

算术运算包括加、减、乘、除、增量、减量、BCD码运算;逻辑运算包括“与”、“或”、“异或”、左移位、右移位和半字节交换,以及位操作中的位置位、位复位等。

暂存器1和暂存器2是ALU的两个输入,用于暂存参与运算的数据。

ALU的输出也是两个:一个是累加器,数据经运算后,其结果又通过内部总线返回到累加器;另一个是程序状态字PSW,用于存储运算和操作结果的状态。

累加器是CPU使用最频繁的一个寄存器。

ACC既是ALU处理数据的来源,又是ALU运算结果的存放单元。

单片机与片外RAM或I/O扩展口进行数据交换必须通过ACC来进行。

B寄存器在乘法和除法指令中作为ALU的输入之一,另一个输入来自ACC。

运算结果存于AB寄存器中。

(2)控制器控制器是识别指令并根据指令性质协调计算机内各组成单元进行工作的部件,主要包括程序计数器PC、PC增量器、指令寄存器、指令译码器、定时及控制逻辑电路等,其功能是控制指令的读入、译码和执行,并对指令执行过程进行定时和逻辑控制。

密码时钟(基于51单片机的电子密码锁)

摘要随着社会的发展,人们生活水平的提高,人们对物质上的需求有了进一步的提高,平时的生活用品都要向着更方便,更人性化的方向发展。

时钟作为人们日常生活中的必备用品大家已经很习惯了,但是一个由P89C51rd2单片机控制的带有密码的时钟却可以给您的生活带来不可想象的变化。

本文就密码时钟做了详细的介绍和说明。

重点论述了以PHILIPS 8位单片机P89C51rd2为核心的软件硬件设计原理,并给出了硬件原理图和软件设计流程。

本系统划分为三个功能部分:输入部分(键盘),处理部分(P89C51rd2及驱动电路),显示部分(数码管),其中处理部分为整个系统的核心,通过P89C51rd2接收到键盘输入的信息后经过处理后调用74LS138和74LS47来驱动数码管显示相关的信息,同时本文也给出了相应软件的设计和程序代码。

以及开发调试C51程序的软件Keil的使用方法和调试过程。

该系统在实验室条件下调试成功,证明了设计思想和开发技术的正确。

关键词:密码时钟;键盘;数码管;Keil;单片机;AbstractAlong with society's development,People living standard enhancement.On people's had the further enhancement to material demand, and the usual daily necessities all must turn towards conveniently,the user friendly direction develops. The clock took in the people’s daily life necessary thing ,e verybody was already used to it.But controls by the P89C51rd2 monolithic integrated circuit has the password clock to be possible to give the change actually which your life brings cannot imagines.This article has made the detailed introduction and showing on the password clock. With emphasis elaborated take PHILIPS 8 monolithic integrated circuit P89C51rd2 as the core software hardware principle of design, and has given the hardware schematic diagram and the software design flow.This system division is three function parts: Input part (keyboard),Processing part (P89C51rd2 and actuation electric circuit),Demonstrates the part (nixietube), Processing part for overall system core. Receives the keyboard entry after P89C51rd2 the information process processing to transfer 74LS138 and 74LS47 actuates the nixietube demonstration related information, simultaneously this article has also given the corresponding software design and the procedure code. As well as the development debugs C51 the procedure the software Keil application method and debugs the process.Key words: Password clock Keyboard Nixietube Keil Monolithic integrated circuit;引言 (1)1 系统功能设计 (3)1.1 操作流程设计 (3)1.2键盘规划及编码规划,键盘功能,功能扩展 (4)2系统总体方案设计 (5)2.1工作原理 (5)2.2 开发工具 (6)2.3 系统整体原理框图 (8)3 系统单元模块设计 (9)3.1 单片机核心控制模块 (9)3.2 串口通讯模块 (13)3.3数据存储模块 (15)3.4键盘模块 (16)3.5显示模块 (17)3.6功能扩展 (22)3.7 开锁指示电路 (22)4 软件设计 (23)4.1 主程序模块 (23)5 系统实现 (23)5.1 仿真调试 (23)5.2程序下载 (28)5.3 运行结果 (29)结论 (30)致谢 (31)参考文献 (32)附录A (33)电子密码锁时钟系统软件设计引言单片机,亦称单片微电脑或单片微型计算机。

2.1 89C51单片机的内部结构

4. 数据存储器 (1) 功能: 用于存放运算的中间结果、数据暂存和缓冲、 标志位等。

(2) 编址:

FFH 52子系列才有 FFH

SFR分布在 80H-FFH

其中11个可 位寻址

的RAM区

80H 7FH 80H

普通RAM区

89C51 128字节

30H 2FH 20H 1FH 00H

位寻址区 工作寄存器区

片内RAM前32个单元是工作寄存器区(00H—1FH)

FFH 52子系列才有 的RAM区 1FH 18H 17H 10H 0FH 08H 07H 06H 05H 04H 03H 02H 01H 00H

工作寄存器区3

工作寄存器区2

工作寄存器区1

R7 R6 R5 R4 R3 R2 R1 R0

80H 7FH

2

15

1

5

2/3

32

1

5/6

3. 程序存储器 (1) 功能: 用于存放编好的程序和表格常数。 (2) 编址:

0FFFFH

外部 ROM

1000H 0FFFH 内部 ROM 0000H (EA=1) 外部 ROM (EA=0) 0000H 0FFFH

片内ROM和片外ROM取指的速度相同

0000H 0003H 000BH 0013H 001BH 0023H 002BH

51系列单片机的存储器分为数据存储器和程序存储 器,其地址空间,存取指令和控制信号各有一套。

1. 物理结构

片内程序存储器

程序存储器ROM

89C51存储器

片外程序存储器 片内数据存储器 片外数据存储器

数据存储器ROM

2. 逻辑结构

FFH 特 殊 功 能 寄 存 器 80H 7FH 通用 RAM区 位寻址区 30H 2FH 20H 1FH 0FFFH 工作寄 存器区 0000H 0000H 1000H F0H E0H D0H B8H B0H A8H A0H 98H 90H 88H 80H 特 殊 FFFFH 功 能 寄 存 器 中 位 寻 址 F移位功能;位操作。

第2章 89C51单片机的结构及原理PPT课件

2. 数据存储器

FF

80

SFR RAM

30

位寻址区

20

工作 寄存器 0-3组

FFFF RAM

外部 RAM

00

0000

12

表 2.2 寄存器与RAM 地址对照表

13

表 2.3 RAM中的位寻址区地址表

14

内部数据存储器高128单元

(特殊功能寄存器区)

程序计数器PC 累加器A 寄存器B 状态字寄存器PSW

4

2.3 89C51系列单片机的引脚功能

2.3.1 89C51系列单片机引脚功能 2.3.2 三总线结构

5

图2-3(a)89C51系列单片机的引脚 6

表2.1 P3口的第二功能表

7

2.3.2 三总线结构

图2-3(b)89C51系列单片机功能引脚分类

(总线结构图)

8

2.4 89C51系列单片机的主要组成部分

外部 ROM EA=0

0000

FF

SFR 80 RAM

30 位寻址区

20

工作 寄存器 0-3组

00

FFFF RAM

外部 RAM

0000

10

1. 程序存储器

在程序存储器中有6个单元具有特殊功能: 0000H~0002H:是所有执行程序的入口

地址,89C51复位后,CPU总是从0000H单 元开始执行程序。 0003H:外部中断0入口。 000BH:定时器0溢出中断入口。 0013H:外部中断1入口。 001BH:定时器1溢出中断入口。 0023H:串行口中断入口。

0

1

3组

18H~1FH

R0~R7

堆栈指针SP:按照先进后出、后进先出 的原则存取RAM区域。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

湖州师范学院课程设计总结报告课程名称工程项目设计训练设计题目 8051/89C51 CPU核及片上系统设计专业班级姓名指导教师报告成绩《工程项目设计训练》任务书一、设计任务8051 IP软核应用系统构建完成流水灯的设计与模式选择二、设计要求(1)了解8051/89C51单片机软核基本功能和结构,熟悉K8051单片机核信号端口功能;(2)掌握K8051单片机软核实用系统构建和软件测试方法;三、器件和设备清单四、参考设计(1) K8051单片机软核基本功能和结构与前面介绍的CPU相同,K8051单片机核也含有8位复杂指令CPU,存储器采用哈佛结构,其结构框图如图所示。

K8051的指令系统与8051/2、8031/2等完全兼容,硬件部分也基本相同,例如可接64KB外部存储器,可接256字节内部数据RAM,含两个16位定时/计数器,全双工串口,含节省功耗工作模式,中断响应结构等等。

不同之处主要有:1、K8051是以网表文件的方式存在的,只有通过编译综合,并载入FPGA中才以硬件的方式工作,而普通8051总是以硬件方式存在的;2、K8051无内部ROM和RAM,所有程序ROM和内部RAM都必须外接。

从K8051结构模块框图可见,它包含了“数据RAM端口”和“程序存储器端口”,是连接外接ROM、RAM的专用端口(此ROM和RAM都能用LPM_ROM和LPM_RAM在同一片FPGA中实现)。

然而普通8051芯片的内部RAM是在芯片内的,而外部ROM的连接必须以总线方式与其P0、P2口相接(A T89S51的ROM在芯片内,CPU核外)。

程序存储器端口ALU I/O 端口定时器/计数器UART 串行口数据RAM 端口中断控制器特殊功能寄存器K8051结构模块框图3、以软核方式存在能进行硬件修改和编辑;能对其进行仿真和嵌入式逻辑分析仪实现实时时序测试;能根据设计者的意愿将CPU 、RAM 、ROM 、硬件功能模块和接口模块等实现于同一片FPGA 中(即SOC )。

4、与普通8051不同,K8051的4个I/O 口是分开的。

例如P1口,其输入端P1I 和输出端P1O 是分开的,如果需要使用P1口的双向口功能,必须外接一些电路才能实现。

如图,K8051单片机的原理图实体图,下方是输入端,上方是输出端。

其主要端口的功能如表所示。

注意其中的双向口的表达方式。

K8051原理图实体图如图所示,单片机中的一个端口构成的双向口(P1口)电路连接方法。

图中电路调用了几个辅助元件,其中TRI是三态控制门,WIRE是普通接线,主要用于网络名转换。

K8051单片机I/O口设置成双向口的电路其中P1E是三态门控制信号,当执行从P1口的输入指令时,P1E[7..0]输出全为高电平,外部数据可以通过双向口P1[7..0]进入单片机的P1口的输入口P1I[7..0],而当执行向P1口输出的指令时,若P1口的输出口P1O[7..0]中的位为低电平,则控制信号P1E[7..0]中对应的位也为低,故信号能顺利输出P1口;但当输出信号P1O[7..0]中的位为高电平时,则控制信号P1E[7..0]中对应的位也为高电平,故这时除非P1[7..0]对应的FPGA的外部端口被上拉,否则将呈现纯高阻态。

因此,当使用单片机的双向口时须设置FPGA的端口为上拉!设置方法是,选择Assignmemts菜单中的settings项,选择左栏的Fitter Settings项,再点击右侧的More Settings按纽,在弹出的窗口(图右侧图)下栏中选择Weak PullUp Resistor,并于上方的Setting栏选择On。

注意,如果选择了Enable Bus-Hold Circuitry为ON,则不能选上拉为ON,前者是选择输出总线的最后输出为锁定。

设置FPGA的总线口输出为上拉(2)K8051单片机软核实用系统构建和软件测试K8051核在接上了ROM和RAM后就成为一个完整的8051或8052单片机了,如图是K8051核实用系统的最基本构建顶层原理图,主要由4个部件构成:K8051基本实用电路1、K8051核。

图中的CPU_Core即K8051单片机核,由VQM原码表述:CPU_Core.vqm,可以直接调用。

该元件可以与其他不同语言表述的元件一同综合与编译。

2、嵌入式锁相环PLL50。

其输入频率设置为20MHz,输出频率所在90MHz上,K8051能接受的工作时钟频率上限取决于FPGA的速度级别。

3、程序ROM,LPM_ROM。

采用ROM容量的大小也取决于FPGA所含的嵌入RAM 的大小。

图14中设置的ROM容量是4K字节,对于一般的应用足够了。

此ROM可以加载HEX格式文件作为单片机的程序代码。

HEX程序代码可以直接使用普通8051单片机程序编译器生成(设已加载了TEST1.HEX)。

4、数据RAM,LPM_RAM。

图14中设置的LPM_RAM容量是256字节。

高128字节须用间接寻址方式访问。

图中,P0I[7..0]、P1I[7..0]、P2I[7..0]、P3I[7..0]分别为P0、P1、P2、P3口的输入口;P0O[7..0]、P1O[7..0]、P2O[7..0]、P3O[7..0]分别为P0、P1、P2、P3口的输出口。

《8051/89C51 CPU核及片上系统设计》总结报告一.设计思路1.本次课程设计中,先使QuarterII设计正弦信号发生器,熟悉软件的使用。

2.设计简单的一秒钟二极管的亮灭,熟悉掌握开发板及其软件调试和引脚设定3.中和上述实验设计最终方案,实现开发板流水灯的设计,使其能够使用按键的方法实现流水灯三种模式的变化其实验思路为:按下第一个模式控制键后,8个LED数码管会从做到右一个一个亮灯,知道所有灯都亮,LED显示器会显示数字“1”:再按一下模式控制键,8个数码管会以灯0.5秒亮一次,下一个0.5秒灭,而下一个数码管同时点亮,使每个数码管都亮灭过,LED 显示器会显示数字“2”;最后再一次按模式件,8个LED数码管会分别从两边向中间亮,直到所有的灯都点亮,而LED显示器会显示数字“3”二.设计框图1.正弦信号发生器结构图2.流水灯三.模块分析流水灯:1.锁相环对锁相环进行设置:锁相环是由鉴相器(phase detector )、环路滤波器(loop filter )和压控振荡器(voltage control oscillator,VCO )组成的一种相位负反馈系统,鉴相器的输出信号v D (t) 是输入信号v i (t) 和振荡器输出信号v o (t) 的相位差,该误差电压信号通过环路滤波器滤除高频分量和噪声后,输出低频信号v C (t) 作为CO 的控制信号。

在控制电压v C (t) 作用下,VCO 输出信号v o (t) 的频率发生变化并反馈到鉴相器。

由此可知,锁相环是一传递相位的反馈系统,系统变量是相位,系统响应是对输入输出信号的相位而不是对其幅度而言。

锁相环的基本原理是,利用负反馈使输出信号频率与输入信号频率之间存在精确度相关(一般是成倍数关系),所以可以用在收发机中本振信号的产生,信号恢复,调频信号调解。

2.RAM :在Quarter中也可以直接生成相应模块,并且对其相关的引脚和频率进行设定。

设置成:3.ROM:在Quarter中也可以直接生成相应模块。

如上图所示,在设置ROM时要加载在keil软件中生成的.hex文件四.电路调试在进行电路调试前要先进行引脚设置,如下图:在设置完后进行下载测试:调试成功后的效果为:1.效果图为1秒亮灭图:2.流水灯实验,实现3种模式的变化模式一:实现灯从左到右亮灯,再从右到左亮灯模式二:实现灯从左到右亮,从右到左亮,但是每个等亮时,都有0.5秒的停顿模式三:灯从两边向中间亮起五.程序清单1.正弦信号发生器程序:Counter8:LIBRARY IEEE;--8位计数器USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY counter8 ISPORT (FIN:IN STD_LOGIC;--时钟信号CLR:IN STD_LOGIC;--清零信号DOUT:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));--计数结果END counter8;ARCHITECTURE behav OF counter8 ISSIGNAL CQI:STD_LOGIC_VECTOR(7 DOWNTO 0);BEGINPROCESS(FIN,CLR)BEGINIF CLR='1' THENCQI<=(OTHERS=>'0');--清零ELSIF FIN'EVENT AND FIN='1' THEN CQI <= CQI+1;END IF;END PROCESS;DOUT<=CQI;END behav;2.一秒亮灭程序:#include<reg51.h>#include<intrins.h>#define uint unsigned int#define uchar unsigned charsbit led=P1^0;uint i,j;void delayms(uint xms){uint i,j;for(i=xms;i>0;i--)for(j=415;j>0;j--);}void main ( ){while(1){led=~led;delayms(500);}}2.灯一秒的亮灭程序:#include<reg51.h>#include<intrins.h>#define uint unsigned int#define uchar unsigned charsbit led=P1^0;uint i,j;void delayms(uint xms){uint i,j;for(i=xms;i>0;i--)for(j=415;j>0;j--);}void main ( ){while(1){led=~led;delayms(500);}}3.流水灯程序:#include<reg51.h>#include<intrins.h>#define uint unsigned int#define uchar unsigned charsbit key1=P2^0;uchar a,b;uint i,j;uint x=0;unsigned char design[18]={0x00,0xff,0xFE,0xFD,0xFB,0xF7,0xEF,0xDF,0xBF, 0x7F,0x7F,0xBF,0xDF,0xEF,0xF7,0xFB,0xFD,0xFE};unsigned char design1[8]={0x81,0x42,0x24,0x18,0xe7,0xdb,0xbd,0x7e};void delayms(uint xms){for(i=xms;i>0;i--)for(j=415;j>0;j--);}void main ( ){P0=0;while(1){if(key1==0){delayms(5);if(key1==0){while(!key1); //按键释放检测x=x+1;P0=x;if(x >= 4)x=0;}}if(x==1){a=0x01;for(i=0;i<7;i++){P1=a;delayms(200);a=a<<1;a=a+0X01;}a=0x80;for(j=0;j<7;j++)P1=a;delayms(200);a=a>>1;a=a+0X80;} //实现流水灯来回闪烁}if(x==2){for (b=0; b<17; b++){delayms(200);P1 = design[b]; //读已定义的花样数据并写花样数据到P1口}}}if(x==3){for (b=0; b<8; b++){delayms(200);P1 = design1[b]; //读已定义的花样数据并写花样数据到P1口}}}}}六.感想此次课程设计主要是利用QuarterII,keil软件实现流水灯的多种变化,通过8051/89C51 CPU核及片上系统设计,再次熟悉了Quartus2 ,Keil软件,学习了8051/89C51单片机软核基本功能和结构,熟悉K8051单片机核信号端口功能,掌握了K8051单片机软核实用系统构建和软件测试方法等。