浙江师范大学EDA试题(11)

EDA技术EDA技术试卷(练习题库)(2023版)

EDA技术EDA技术试卷(练习题库)1、个项目的输入输出端口是定义在()。

2、描述项目具有逻辑功能的是()。

3、关键字ARCHITECTURE定义的是。

4、M AXP1USII中编译VHD1源程序时要求()。

5、1987标准的VHD1语言对大小写是()。

6、关于1987标准的VHD1语言中,标识符描述正确的是()。

7、符合1987VHD1标准的标识符是()。

8、VHD1语言中变量定义的位置是()。

9、VHD1语言中信号定义的位置是()。

10、变量是局部量可以写在()。

11、变量和信号的描述正确的是()。

12、关于VHD1数据类型,正确的是()。

13、下面数据中属于实数的是()。

14、下面数据中属于位矢量的是()。

15、可以不必声明而直接引用的数据类型是()。

16、STD_10GIG_1164中定义的高阻是字符()。

17、STD_10GIG」164中字符H定义的是()。

18、使用STD_1OG1G」164使用的数据类型时()。

19、VHD1运算符优先级的说法正确的是()。

20、如果a=1,b=0,则逻辑表达式(aANDb)OR(NOTbANDa)的值是()。

21、不属于顺序语句的是()。

22、正确给变量X赋值的语句是()。

23、EDA的中文含义是()。

24、EPF10K20TC144-4具有多少个管脚()。

25、如果a=1,b=1,则逻辑表达式(aXORb)OR(NOTbANDa)的值是()。

26、MAX+P1USII的,数据类型为std_1ogic_vector,试指出下面那个30、在一个VHD1,数据类型为integer,数据范围0to127,下面哪个赋31、下列那个流程是正确的基于EDA软件的FPGA/CP1D和变量的说法,哪一个是不正确的:()。

33、下列语句中,不属于并行语句的是:()。

34、O在EDA工具中,能将硬件描述语言转换为硬件电路的重要工具软件称为。

35、不是操作符号它只相当与作用〃target=Zb1ank〃>在VHD1的CASE语句中,条件句中的“二>”不是操作符号,它只相当与O作用。

EDA考试题目及答案

EDA考试题目及答案一、单项选择题(每题2分,共10题)1. EDA技术中,用于描述数字电路的硬件描述语言是:A. VHDLB. VerilogC. C语言D. Python答案:A2. 在VHDL中,用于定义信号的关键字是:A. variableB. constantC. signalD. type答案:C3. 下列哪个不是Verilog中的测试平台(testbench)组件?A. initial块B. always块C. moduleD. function答案:D4. 在EDA设计中,用于模拟电路行为的软件工具是:A. 仿真器B. 编译器C. 综合器D. 布局器答案:A5. 以下哪个选项不是EDA工具的主要功能?A. 电路设计B. 电路仿真C. 电路测试D. 电路维修答案:D6. 在VHDL中,用于实现组合逻辑的构造块是:A. processB. if语句C. case语句D. all of the above答案:D7. Verilog中,用于描述时序逻辑的关键字是:A. alwaysB. initialC. moduleD. assign答案:A8. 在EDA设计流程中,电路综合通常发生在哪个阶段之后?A. 电路设计B. 电路仿真C. 电路测试D. 电路验证答案:B9. 下列哪个不是VHDL中的并发语句?A. ifB. caseC. loopD. procedure答案:D10. 在Verilog中,用于描述模块间连接的关键字是:A. inputB. outputC. wireD. module答案:C二、多项选择题(每题3分,共5题)1. EDA技术可以应用于以下哪些领域?A. 集成电路设计B. 软件工程C. 电子系统设计D. 机械工程答案:A, C2. VHDL中的哪些构造可以用来描述时序逻辑?A. processB. ifC. whileD. after答案:A, D3. 在Verilog中,哪些关键字用于定义模块的端口?A. inputB. outputC. inoutD. module答案:A, B, C4. EDA工具在设计流程中可以提供哪些辅助功能?A. 设计验证B. 设计优化C. 设计转换D. 设计维护答案:A, B, C5. 在EDA设计中,哪些因素会影响电路的性能?A. 电路复杂度B. 电源电压C. 温度变化D. 材料特性答案:A, B, C, D三、简答题(每题5分,共2题)1. 描述一下在EDA设计中,为什么需要进行电路仿真?答案:在EDA设计中,电路仿真是为了在实际制造电路之前,通过软件模拟电路的行为和性能。

eda期末考试试题及答案

eda期末考试试题及答案EDA期末考试试题及答案一、选择题(每题2分,共20分)1. EDA(电子设计自动化)主要应用于以下哪个领域?A. 机械设计B. 建筑设计C. 电子电路设计D. 软件开发答案:C2. 在EDA软件中,以下哪个不是常见的设计流程?A. 原理图设计B. 电路仿真C. 手动布线D. 封装设计答案:C3. 下列哪个不是EDA工具的组成部分?A. 原理图编辑器B. PCB布局工具C. 3D建模软件D. 仿真分析工具答案:C4. 在EDA设计中,PCB指的是什么?A. 印刷电路板B. 个人计算机C. 程序控制板D. 功率控制板答案:A5. 以下哪个是EDA设计中常用的文件格式?A. .txtB. .pdfC. .schD. .jpg答案:C...(此处省略其他选择题)二、简答题(每题10分,共30分)1. 简述EDA设计流程的主要步骤。

答案:EDA设计流程通常包括原理图设计、电路仿真、PCB布局、布线、封装设计、测试与验证等步骤。

2. 解释什么是PCB布线,并说明其重要性。

答案:PCB布线是指在印刷电路板上将电子元件的引脚通过导电路径连接起来的过程。

布线的重要性在于它直接影响电路的性能、可靠性和生产成本。

3. 描述电路仿真在EDA设计中的作用。

答案:电路仿真在EDA设计中用于模拟电路在不同条件下的行为,帮助设计者预测电路的性能,优化设计,并在实际制造之前发现潜在的问题。

三、计算题(每题15分,共30分)1. 给定一个简单的RC电路,计算其时间常数τ。

答案:时间常数τ是电容C和电阻R的乘积,即τ = R * C。

2. 假设一个电路的输入信号频率为1kHz,计算其周期T。

答案:周期T是频率f的倒数,即T = 1/f = 1/1000Hz = 1ms。

四、设计题(20分)设计一个简单的放大器电路,并使用EDA工具绘制其原理图。

答案:(此处应有原理图,但无法提供图像,故省略)五、论述题(20分)论述在现代电子设计中,EDA工具的重要性及其对设计流程的影响。

eda技术实用教程期末考试题及答案

eda技术实用教程期末考试题及答案一、选择题(每题2分,共20分)1. EDA技术中,FPGA代表的是()。

A. 现场可编程逻辑阵列B. 现场可编程门阵列C. 现场可编程逻辑器件D. 现场可编程门器件答案:B2. 在EDA技术中,VHDL是一种()。

A. 硬件描述语言B. 软件描述语言C. 系统描述语言D. 网络描述语言答案:A3. 下列哪个不是EDA工具的主要功能()。

A. 逻辑综合B. 电路仿真C. 代码编译D. 布局布线答案:C4. 在VHDL中,下列哪个关键字用于定义并行语句()。

A. ifB. beginC. loopD. process答案:B5. 在EDA技术中,用于测试和验证数字电路的EDA工具是()。

A. 逻辑综合工具B. 电路仿真工具C. 布局布线工具D. 测试生成工具答案:B6. 下列哪个不是FPGA的配置方式()。

A. 在系统可编程B. 串行配置C. 并行配置D. 网络配置答案:D7. 在VHDL中,用于定义信号的关键字是()。

B. constantC. signalD. type答案:C8. 在EDA技术中,用于描述数字电路行为的模型是()。

A. 结构模型B. 数据流模型C. 行为模型D. 混合模型答案:C9. 在VHDL中,下列哪个关键字用于定义过程()。

A. procedureB. functionD. entity答案:C10. 在EDA技术中,用于优化电路性能的EDA工具是()。

A. 逻辑综合工具B. 电路仿真工具C. 布局布线工具D. 测试生成工具答案:C二、填空题(每题2分,共20分)1. EDA技术中的“EDA”代表的是______、______和______。

答案:电子设计自动化2. VHDL中的并发语句包括______、______、______和______。

答案:信号赋值、条件信号赋值、选择信号赋值、元件实例化3. 在FPGA设计中,______是用于存储配置数据的非易失性存储器。

EDA试题答案

学习使人进步1.1.1(1)什么叫EDA(P1)?EDA技术是一种以计算机为工作平台,结合计算机图形学、拓扑逻辑学、计算方法学及人工智能等多项计算机应用科学的最新成果而开发出来的一套软件工具。

1.1.2(2)EDA技术在硬件硬件方面融合了哪些技术(P1)?大规模集成电路制造技术、IC版图设计技术、ASIC (专用集成电路)测试和封装技术、FPGA和CPLD编程下载技术、自动测试技术等1.1.3(3)EDA技术在计算机辅助工程方面融合了哪些技术(P1)?计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助测试(CAT)、计算机辅助工程(CAE)技术以及多种计算机语言的设计概念。

1.1.4(4)EDA技术在现代电子学方面融合了哪些内容(P1)?如:电子线路设计理论、数字信号处理技术、嵌入式系统和计算机设计技术、数字系统建模和优化技术及微波技术等1.1.5(5)EDA技术在21世纪的突出表现有哪5个方面(P2)?●使电子设计产品以自主知识产权方式得以明确表达和确认成为可能。

●在仿真验证和设计两方面都支持标准硬件描述语言的功能强大的EDA软件不断推出。

●电子技术全方位进入EDA领域。

●EDA使得电子领域各学科的界限更加模糊,更加互为包容。

●不断推出更大规模的FPGA和CPLD。

●基于EDA工具的用于ASIC设计的标准单元已涵盖大规模电子系统及复杂IP核模块。

●软硬件IP核在电子领域得以进一步确认。

●SoC高效率低成本设计技术日益成熟。

●系统级、行为验证级硬件描述语言使复杂电子系统的设计特别是验证趋于高效和简单。

1.2.1(6)画图说明EDA技术实现目标是什么(P3)?1.3.1(7)目前常用的HDL主要有哪些?其中使用最多的是谁(P4)?VHDL;Verilog HDL;SystemVerilog ;System C 1.3.2(8)与Verilog相比VHDL有哪两方面优势?有哪三方面不足(P5)?优势:1.语法比Verilog更严谨,通过EDA工具自动语法检查,以排除许多设计中的疏忽;2.有很好的行为级描述能力和一定的系统级描述能力,而Verilog建模时,行为与系统级抽象及相关描述能力不及VHDL。

eda考试题及答案

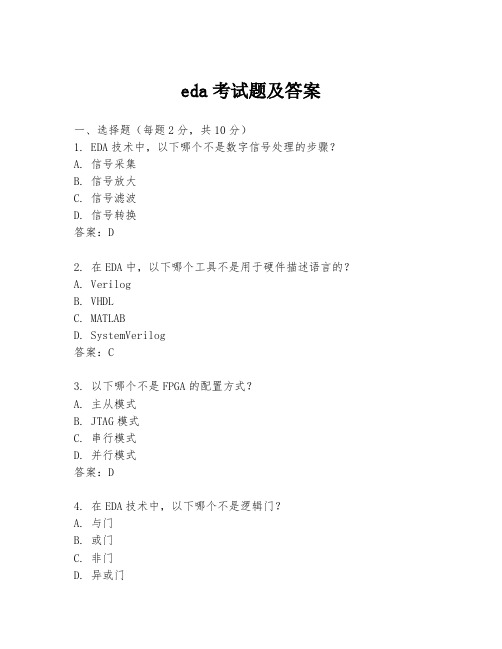

eda考试题及答案一、选择题(每题2分,共10分)1. EDA技术中,以下哪个不是数字信号处理的步骤?A. 信号采集B. 信号放大C. 信号滤波D. 信号转换答案:D2. 在EDA中,以下哪个工具不是用于硬件描述语言的?A. VerilogB. VHDLC. MATLABD. SystemVerilog答案:C3. 以下哪个不是FPGA的配置方式?A. 主从模式B. JTAG模式C. 串行模式D. 并行模式答案:D4. 在EDA技术中,以下哪个不是逻辑门?A. 与门B. 或门C. 非门D. 异或门答案:D5. 以下哪个是EDA软件中用于时序分析的工具?A. 波形仿真B. 逻辑仿真C. 时序分析器D. 功能仿真答案:C二、填空题(每题2分,共10分)1. EDA技术的核心是______,它用于设计和验证电子系统。

答案:硬件描述语言2. 在EDA设计流程中,______是将硬件描述语言转换成逻辑电路图的过程。

答案:综合3. FPGA的全称是______,它是一种可编程的逻辑器件。

答案:现场可编程门阵列4. 在EDA中,______是一种用于模拟电路行为的工具,它可以帮助设计者验证电路设计的正确性。

答案:仿真5. 在EDA中,______是一种用于优化电路布局和布线的技术,以减少电路的延迟和功耗。

答案:布局布线三、简答题(每题10分,共20分)1. 简述EDA技术在现代电子设计中的重要性。

答案:EDA技术在现代电子设计中至关重要,因为它提供了一种高效、自动化的方式来设计、模拟和验证复杂的电子系统。

通过使用EDA工具,设计师可以快速迭代设计,减少错误,缩短产品上市时间,并提高电路的性能和可靠性。

2. 描述在EDA设计流程中,仿真测试的主要目的是什么。

答案:仿真测试的主要目的是在实际硬件实现之前验证电路设计的功能正确性和性能指标。

通过仿真,设计师可以检测和修复设计中的错误,优化电路性能,并预测电路在不同工作条件下的行为,从而确保最终产品能够满足设计规格和性能要求。

EDA期末考试试卷及答案

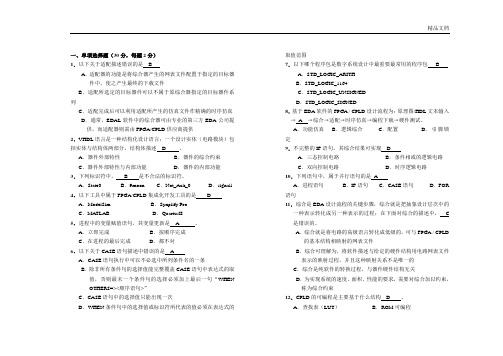

一、单项选择题(30分,每题2分)1.以下关于适配描述错误的是 BA.适配器的功能是将综合器产生的网表文件配置于指定的目标器件中,使之产生最终的下载文件B.适配所选定的目标器件可以不属于原综合器指定的目标器件系列C.适配完成后可以利用适配所产生的仿真文件作精确的时序仿真D.通常,EDAL软件中的综合器可由专业的第三方EDA公司提供,而适配器则需由FPGA/CPLD供应商提供2.VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述 D 。

A.器件外部特性B.器件的综合约束C.器件外部特性与内部功能D.器件的内部功能3.下列标识符中, B 是不合法的标识符。

A.State0 B.9moon C.Not_Ack_0 D.signall 4.以下工具中属于FPGA/CPLD集成化开发工具的是 D A.ModelSim B.Synplify ProC.MA TLAB D.QuartusII5.进程中的变量赋值语句,其变量更新是 A 。

A.立即完成B.按顺序完成C.在进程的最后完成D.都不对6.以下关于CASE语句描述中错误的是 AA.CASE语句执行中可以不必选中所列条件名的一条B.除非所有条件句的选择值能完整覆盖CASE语句中表达式的取值,否则最末一个条件句的选择必须加上最后一句“WHENOTHERS=><顺序语句>”C.CASE语句中的选择值只能出现一次D.WHEN条件句中的选择值或标识符所代表的值必须在表达式的取值范围7.以下哪个程序包是数字系统设计中最重要最常用的程序包 B A.STD_LOGIC_ARITHB.STD_LOGIC_1164C.STD_LOGIC_UNSIGNEDD.STD_LOGIC_SIGNED8.基于EDA软件的FPGA / CPLD设计流程为:原理图/HDL文本输入→ A →综合→适配→时序仿真→编程下载→硬件测试。

eda期末考试题目及答案

eda期末考试题目及答案一、选择题(每题2分,共20分)1. EDA(电子设计自动化)的主要功能是什么?A. 电路设计B. 电路仿真C. 电路测试D. 所有以上选项2. 在EDA中,HDL指的是什么?A. 高级设计语言B. 硬件描述语言C. 硬件开发语言D. 硬件描述逻辑3. 下列哪个不是EDA工具的主要组成部分?A. 原理图编辑器B. 仿真器C. 编译器D. 汇编器4. 在EDA中,FPGA代表什么?A. 现场可编程门阵列B. 固定可编程门阵列C. 功能可编程门阵列D. 快速可编程门阵列5. 以下哪个是EDA设计流程中的必要步骤?A. 原理图绘制B. 电路板布局C. 焊接D. 电路测试二、填空题(每空2分,共20分)6. 常见的EDA软件有______、______和______。

答案:Cadence, Altium Designer, Mentor Graphics7. 在EDA中,______是一种用于设计和验证数字电路的图形化编程语言。

答案:VHDL8. EDA工具可以帮助工程师进行______和______。

答案:设计优化,性能分析9. 与ASIC相比,FPGA的优点是______和______。

答案:灵活性高,开发周期短10. 在EDA设计中,布局和布线是实现______的关键步骤。

答案:电路板物理结构三、简答题(每题10分,共30分)11. 简述EDA在现代电子设计中的重要性。

答案:EDA在现代电子设计中的重要性体现在它能够提高设计效率,降低成本,缩短产品上市时间,同时提高设计的可靠性和可维护性。

12. 解释什么是仿真,并说明在EDA设计流程中仿真的作用。

答案:仿真是一种模拟实际电路在不同条件下行为的技术。

在EDA 设计流程中,仿真用于验证设计的正确性,预测电路的性能,以及发现潜在的问题,从而在实际制造之前进行必要的修改。

13. 描述FPGA与ASIC在应用上的主要区别。

答案:FPGA是一种可编程的硬件,可以在设计完成后重新配置,适用于需要快速原型开发和灵活设计调整的场景。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

浙江师范大学《EDA技术与VHDL语言》考试卷(A卷)考试类别考试使用学生学院 1专业本科考试时间分钟出卷时间 201年月日说明:考生应将全部答案都写在答题纸上,否则作无效处理。

一、填空题(根据要求在空格处填写合适语句与波形,每格2分,共20分)1. 以下为用状态机方法描述的JK触发器。

并经仿真,得到其波形,请按程序注释要求完成空格中的程序,并绘制按在图1所示输入波形时输出Q的仿真结果波形。

library IEEE;use IEEE.STD_LOGIC_1164.ALL;ENTITY JK_fsm IS --实体描述PORT ( clk, j, k, rest : IN STD_LOGIC;Q, QB : OUT STD_LOGIC );END JK_fsm;ARCHITECTURE JK_ff OF (1)IS --实体描述TYPE FSM_ST IS (s0, s1);SIGNAL states: (2); --状态机信号定义SIGNAL QT : STD_LOGIC;BEGINPROCESS( (3) ) --进程的敏感信号BEGINIF ( rest='1' ) THENstates <= S0;ELSIF( (4) ) THEN --触发器为上升沿有效CASE states ISWHEN S0 => IF ( (5) ) THEN --状态转换条件states <= S1;else states <= S0;END IF;WHEN S1 => IF ( (6) ) THEN --状态转换条件states <= S0;else states <= S1;END IF;(7) ; --状态转换条件END IF;END PROCESS;WITH (8) SELECT --根据状态信号赋值QT <= '0' when S0 ,'1' when others ;Q <= QT ;QB <= (9) ; --给输出信号赋值END JK_ff;restclkjkQ(10)图1 JK触发器的仿真图二、改错题(对操作过程中的错误进行改正,每处4分,共16分)1. 以下VHDL程序为一个具有三态输出的寄存器,存放在E:/EDAT/buffer/, 文件名为tri_register.v, 编译过程中发现几个错误提示(每一提示对应一个错误),请你指出错误原因,并加以改正。

library IEEE; --1use IEEE.STD_LOGIC_1164.ALL; --2ENTITY tri_register IS --3 PORT ( --4 clkr : IN bit; --5CE, OE : IN bit; --6DATA_IN : IN STD_LOGIC_VECTOR(7 DOWNTO 0); --7DATA_out : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); --8--DATA_exp : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) --9); --10 END tri_register; --11ARCHITECTURE rtl OF tri_register IS --12 SIGNAL DATA_t : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); --13 BEGIN --14P1: process (clkr, CE) --15 Begin --16if (CE = '0') then --17DATA_t <= "ZZZZZZZZ"; --18elsif (clkr'event and clkr='1') then --19if (OE = '0') then --20DATA_t <= "ZZZZZZZZ" ; --21Else --22DATA_t <= DATA_IN; --23end if; --24end if; --25 end if; --26end process; --27DATA_out <= DATA_t; --28 end rtl; --29提示一Error (10170): Verilog HDL syntax error at tri_register.v(1) near text ";"; expecting ".", or an identifier, or "*", or "/"提示二Error (10500): VHDL syntax error at tri_register.vhd(10) near text ")"; expecting an identifier,or "constant", or "file", or "signal", or "variable"Error (10500): VHDL syntax error at tri_register.vhd(14) near text "BEGIN"; expecting an identifier ("begin" is a reserved keyword), or "constant", or "file", or "signal", or "variable"提示三Error (10500): VHDL syntax error at tri_register.vhd(13) near text "out"; expecting an identifier ("out" is a reserved keyword), or a string literal提示四Error (10500): VHDL syntax error at tri_register.vhd(26) near text "if"; expecting "process"三、分析题(阅读所给程序,按要求回答问题,每小题12分,共36分)1. 以下为8*8点阵显示的扫描VHDL程序。

阅读程序后,回答有关问题。

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY scan_8b ISPORT( CLK : IN STD_LOGIC;COM : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);SEG : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) );END scan_8b;ARCHITECTURE art OF scan_8b ISconstant DATA0 : std_logic_vector(7 downto 0) :=x"00";constant DATA1 : std_logic_vector(7 downto 0) :=x"7E";constant DATA2 : std_logic_vector(7 downto 0) :=x"40";constant DATA3 : std_logic_vector(7 downto 0) :=x"40";constant DATA4 : std_logic_vector(7 downto 0) :=x"7E";constant DATA5 : std_logic_vector(7 downto 0) :=x"40";constant DATA6 : std_logic_vector(7 downto 0) :=x"7E";constant DATA7 : std_logic_vector(7 downto 0) :=x"00";SIGNAL CNT :STD_LOGIC_VECTOR(2 DOWNTO 0);SIGNAL segt :STD_LOGIC_VECTOR(7 DOWNTO 0);BEGINp1: PROCESS (CLK)BEGINIF CLK'EVENT AND CLK='1' THENCNT<=CNT+'1';END IF;END PROCESS p1;P2: PROCESS(CNT)BEGINCASE CNT ISWHEN "000" => segt <= DATA0; COM<="11111110";WHEN "001" => segt <= DATA1; COM<="11111101";WHEN "010" => segt <= DATA2; COM<="11111011";WHEN "011" => segt <= DATA3; COM<="11110111";WHEN "100" => segt <= DATA4; COM<="11101111"; WHEN "101" => segt <= DATA5; COM<="11011111"; WHEN "110" => segt <= DATA6; COM<="10111111"; WHEN "111" => segt <= DATA7; COM<="01111111";WHEN OTHERS=> segt <="00000000"; COM<="11111111"; END CASE;END PROCESS p2; SEG <= segt ; end art;问1) 为保证显示无明显闪烁,扫描频率应高于25Hz ,则输入时钟频率至少应取多少?问2) 如果显示与CPLD 连接如图2所示,则显示的图形是什么?问3) 进程P2中,完成了什么功能? 问4) 实验时想换一个显示图案,应该修改程序中哪部分?并写出数字6的字型和编码。