数字电路各种门路

数字逻辑门电路

数字逻辑门电路数字逻辑门电路是现代电子技术领域中重要的基础概念。

它们是通过组合逻辑来实现逻辑运算的电子元件。

本文将介绍数字逻辑门电路的基本概念、常见的逻辑门类型以及它们在计算机和电子设备中的应用。

一、基本概念数字逻辑门电路由逻辑门组成,逻辑门是指一种通过输入信号产生输出信号的电子电路。

在数字电子系统中,逻辑门能够根据输入信号的逻辑值(通常为1或0)产生相应的输出信号。

常见的逻辑门类型有与门(AND)、或门(OR)、非门(NOT)以及异或门(XOR)等。

与门(AND)是一种具有两个或多个输入端口和一个输出端口的逻辑门。

仅当所有输入端口的信号均为高电平时,输出端口才为高电平;否则,输出端口为低电平。

与门的符号通常是将输入端口以及输出端口连接的圆点和直线图形。

或门(OR)是一种具有两个或多个输入端口和一个输出端口的逻辑门。

只要有一个或多个输入端口的信号为高电平,输出端口就为高电平;只有所有输入端口的信号均为低电平时,输出端口才为低电平。

或门的符号通常是将输入端口以及输出端口连接的弧线和直线图形。

非门(NOT)是一种具有一个输入端口和一个输出端口的逻辑门。

当输入信号为高电平时,输出信号为低电平;当输入信号为低电平时,输出信号为高电平。

非门的符号通常是一个小圆圈加一个小三角形。

异或门(XOR)是一种具有两个输入端口和一个输出端口的逻辑门。

只有当输入端口的信号不全为1或不全为0时,输出端口才为高电平;否则,输出端口为低电平。

异或门的符号通常是将两个相连的弧线和直线图形。

二、常见逻辑门组合在数字电子系统中,不仅可以单独使用各种逻辑门,还可以通过多个逻辑门的组合构建出更为复杂的逻辑电路。

以下是一些常见的逻辑门组合。

1. 与非门(NAND):是将与门的输出信号输入到非门中的一种组合。

当与门的输出信号为低电平时,非门的输出信号为高电平;当与门的输出信号为高电平时,非门的输出信号为低电平。

与非门因其功能的广泛应用而变得非常重要。

基本门电路的知识点

基本门电路的知识点基本门电路是数字电子电路中最基础的部分,它们可以实现逻辑功能并处理数字信号。

本文将逐步介绍基本门电路的知识点,包括与门、或门、非门和异或门。

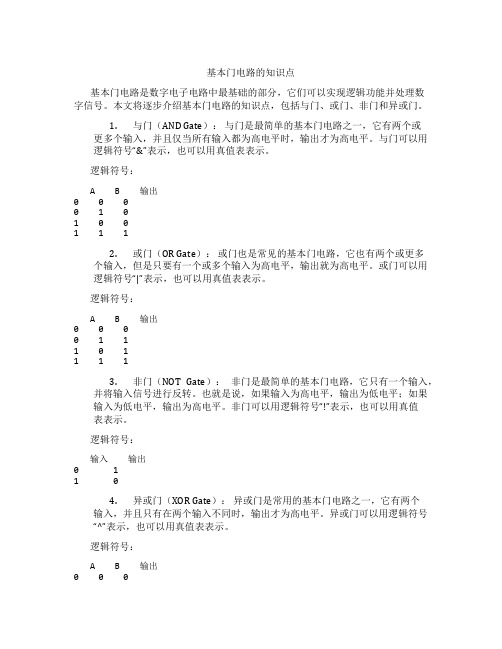

1.与门(AND Gate):与门是最简单的基本门电路之一,它有两个或更多个输入,并且仅当所有输入都为高电平时,输出才为高电平。

与门可以用逻辑符号“&”表示,也可以用真值表表示。

逻辑符号:A B 输出0 0 00 1 01 0 01 1 12.或门(OR Gate):或门也是常见的基本门电路,它也有两个或更多个输入,但是只要有一个或多个输入为高电平,输出就为高电平。

或门可以用逻辑符号“|”表示,也可以用真值表表示。

逻辑符号:A B 输出0 0 00 1 11 0 11 1 13.非门(NOT Gate):非门是最简单的基本门电路,它只有一个输入,并将输入信号进行反转。

也就是说,如果输入为高电平,输出为低电平;如果输入为低电平,输出为高电平。

非门可以用逻辑符号“!”表示,也可以用真值表表示。

逻辑符号:输入输出0 11 04.异或门(XOR Gate):异或门是常用的基本门电路之一,它有两个输入,并且只有在两个输入不同时,输出才为高电平。

异或门可以用逻辑符号“^”表示,也可以用真值表表示。

逻辑符号:A B 输出0 0 00 1 11 0 11 1 0除了以上介绍的基本门电路,还有其他一些常见的门电路,如与非门(NAND Gate)、或非门(NOR Gate)和异或非门(XNOR Gate)。

它们都是基于与门、或门、非门和异或门进行组合和连接而成的。

最后,基本门电路的知识是数字电子电路设计的基础,它们被广泛应用于计算机、通信和电子设备中。

理解基本门电路的工作原理对于深入学习和应用数字电子电路是至关重要的。

希望本文能够帮助读者对基本门电路有更清晰的认识。

数字电路的基本单元

数字电路的基本单元一、数字电路基本单元概述1. 逻辑门- 与门(AND Gate)- 逻辑功能:当所有输入为高电平(逻辑1)时,输出才为高电平;只要有一个输入为低电平(逻辑0),输出就是低电平。

其逻辑表达式为Y = A· B(对于两个输入A和B的情况)。

在电路符号上,与门有多个输入引脚和一个输出引脚,常用的电路符号是一个长方形,输入在左边,输出在右边,中间有一个“&”符号表示与逻辑。

- 或门(OR Gate)- 逻辑功能:只要有一个输入为高电平,输出就为高电平;只有当所有输入都为低电平时,输出才为低电平。

逻辑表达式为Y=A + B(对于两个输入A和B的情况)。

电路符号也是长方形,输入在左,输出在右,中间有一个“≥1”的符号表示或逻辑。

- 非门(NOT Gate)- 逻辑功能:实现输入电平的取反操作,输入为高电平则输出为低电平,输入为低电平则输出为高电平。

逻辑表达式为Y=¯A。

电路符号是一个三角形,在三角形的输入端或者输出端有一个小圆圈,表示取反操作。

- 与非门(NAND Gate)- 逻辑功能:先进行与运算,然后再对结果取反。

逻辑表达式为Y=¯A· B。

与非门的电路符号是在与门符号的基础上,在输出端加上一个小圆圈,表示取反。

- 或非门(NOR Gate)- 逻辑功能:先进行或运算,然后再取反。

逻辑表达式为Y = ¯A + B。

或非门的电路符号是在或门符号的基础上,在输出端加上一个小圆圈。

- 异或门(XOR Gate)- 逻辑功能:当两个输入电平不同时,输出为高电平;当两个输入电平相同时,输出为低电平。

逻辑表达式为Y=A⊕ B = A·¯B+¯A· B。

异或门的电路符号是一个长方形,中间有一个“=1”的符号。

- 同或门(XNOR Gate)- 逻辑功能:与异或门相反,当两个输入电平相同时,输出为高电平;当两个输入电平不同时,输出为低电平。

数字电路1-基本逻辑门电路

可编辑ppt

1

一、 脉冲信号

1. 模拟信号 电子电路中的信号

模拟信号 数字信号

模拟信号:随时间连续变化的信号

正弦波信号

t

三角波信号

t

可编辑ppt

2

处理模拟信号的电路称为模拟电路。如整流 电路、放大电路等,注重研究的是输入和输出 信号间的大小及相位关系。

在模拟电路中,晶体管三极管通常工作在放

可编辑ppt

14

集成或门电路 演示实验:(用74LS32)

或逻辑表达式: Y=A+B

记忆口诀:

“有1出1,全0为0”

可编辑ppt

15

3. “非”逻辑关系

+R

220V

AY

-

状态表

A

Y

0

1

1

0

逻辑表达式:Y = A

“非”逻辑关系是否定或相反的意思。

可编辑ppt

16

三极管“非” 门电路

1. 电路

+UCC RC 截饱止和

如: +3V

0

0 -3V

正脉冲

+3V

0

负脉冲

0

-3V

可编辑ppt

4

脉冲信号的部分参数:

0.9A

0.5A

0.1A

tp

tr

A tf

T

实际的矩形波

脉冲幅度 A 脉冲上升沿 tr

脉冲宽度 tp 脉冲周期 T

脉冲下降沿 tf

可编辑ppt

5

二、基本门电路及其组合

2.1 门电路的基本概念及分立元件基本逻辑门电路

可编辑ppt

6

1. “与”逻辑关系

数字电路-逻辑门电路

驱动门

负载门

&

&

4. IIL低电平输入电流 输入短路电流:

1 &

IIL mA

< 0.4mA

5.高电平输入电流:IIH

1 mA IIH

&

< 20μA

6.开门电平和关门电平:

与非门一输入端Vi ,其余各输入端“1”

VON: Vi由小变大,VO ↘ 到VOL时对应的Vi。 1.3V左右

VOFF:Vi由大变小,VO ↗ 到VOH时对应的Vi。 1.0V左右

第三章 逻辑门电路

前面:基本逻辑运算(逻辑门)做为黑匣子,只关心 输入、输出间的逻辑关系

本章:打开黑匣子,了解内部结构、工作原理,掌握外特性。

两大类结构逻辑门电路:TTL、CMOS

3.2 TTL逻辑门电路

3.2.1 BJT的开关特性 1、BJT的静态开关特性

iB ≈ 0 , iC ≈ 0

截止状态

-2V 0.3V

3.6V

T1

T2

0.7V

Re2 全导通,2.1V

VCC

Rc4

截止

T4

D 0.2V vO =0.2V

T3

负载

实现了:

输入高,

输出低

饱和

0.9V Rb1

vI

T1

0.2V

Rc2 T2

导通需2.1V

Re2

截止 实现了:输入低,输出高

VCC

0.7V Rc4

T4

导通

D vO ≈5V-1.4V

T3 负载 =3.6V

T2A或T2B将饱和, T3饱和,T4截止, 输出为低电平。

逻辑表达式

L A B

补充: TTL与非门的参数 (3.1.2逻辑电路的一般特性)

数电第三章门电路

§3.4 TTL门电路

数字集成电路:在一块半导体基片上制作出一个 完整的逻辑电路所需要的全部元件和连线。 使用时接:电源、输入和输出。数字集成电 路具有体积小、可靠性高、速度快、而且价 格便宜的特点。

TTL型电路:输入和输出端结构都采用了半导体晶 体管,称之为: Transistor— Transistor Logic。

输出高电平

UOH (3.4V)

u0(V)

UOH

“1”

输出低电平

u0(V)

UOL

UOL (0.3V)

1

(0.3V)

2 3 ui(V)

1 2 3 ui(V)

阈值UT=1.4V

传输特性曲线

理想的传输特性 28

1、输出高电平UOH、输出低电平UOL UOH2.4V UOL 0.4V 便认为合格。 典型值UOH=3.4V UOL 0.3V 。

uA t

uF

截止区: UBE< 死区电压, IB=0 , IC=ICEO 0 ——C、 E间相当于开关断开。

+ucc

t

4

0.3V

3.2.3MOS管的开关特 恒流区:UGS>>Uth , UDS

性: +VDD

0V ——D、S间相当于 开关闭合。

R

uI

Uo

Ui

NMO S

uO

夹断区: UGS< Uth, ID=0 ——D、S间相当于开关断开。

3.3.4 其它门电路

一、 其它门电路

其它门电路有与非门、或非门、同或门、异或门等等,比如:

二、 门电路的“封锁”和“打开”问题

A B

&

Y

C

当C=1时,Y=AB.1=AB

电子工程数字电路设计(知识点)

电子工程数字电路设计(知识点)数字电路设计是电子工程的重要内容,涉及到数字信号的处理和控制。

在电子工程领域中,数字电路是一类电路系统,用于处理和控制数字信号,并实现各种功能。

本文将介绍数字电路设计的知识点,包括逻辑门、组合逻辑电路和时序逻辑电路。

一、逻辑门逻辑门是数字电路设计的基础组成部分,用于处理和操作数字信号。

在数字电路中常见的逻辑门有与门(AND)、或门(OR)、非门(NOT)以及它们的组合形式(如与非门、或非门)。

1. 与门(AND)与门是最基本的逻辑门之一,其输出信号仅在所有输入信号均为高电平时才输出高电平。

与门的符号为“&&”。

2. 或门(OR)或门是另一个常见的逻辑门,其输出信号仅在任一输入信号为高电平时即输出高电平。

或门的符号为“||”。

3. 非门(NOT)非门是最简单的逻辑门,其输出信号与输入信号相反。

非门的符号为“!”。

二、组合逻辑电路组合逻辑电路是由逻辑门组成的电路,根据输入信号的不同组合产生不同的输出信号。

组合逻辑电路的输出仅与当前输入信号有关,而与过去的输入信号或时序无关。

1. 译码器译码器是一种常见的组合逻辑电路,用于将一组输入信号转换为对应的输出信号。

常见的译码器有二进制译码器和十进制译码器等。

2. 多路选择器多路选择器是另一种常见的组合逻辑电路,用于根据选择信号选择不同的输入信号输出。

多路选择器的输出信号与选择信号相关。

三、时序逻辑电路时序逻辑电路是由触发器和组合逻辑电路组成的电路系统,其输出信号不仅与当前输入信号相关,还与过去的输入信号和时序有关。

1. 触发器触发器是时序逻辑电路的基本组成单元,用于存储和延时信号。

常见的触发器有D触发器、JK触发器和T触发器等。

2. 计数器计数器是一种常见的时序逻辑电路,用于计数和记录输入脉冲的数量。

计数器可以分为正向计数器和逆向计数器。

四、应用场景数字电路设计在现代电子工程中具有广泛的应用。

以下是一些常见的应用场景:1. 中央处理器(CPU)中央处理器是计算机的核心部件,其中包含了大量的数字电路设计。

数字电子技术——门电路

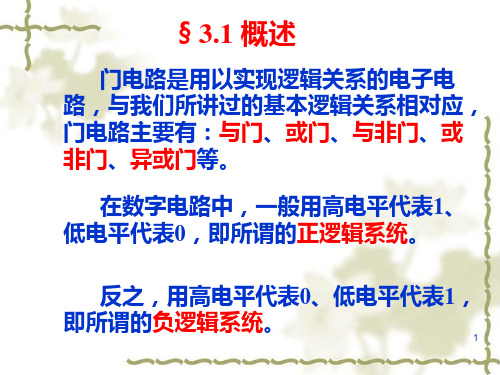

数字电子技术——门电路3.1 概述1. 门电路是用以实现逻辑关系的电子电路,与基本逻辑关系相对应。

门电路主要有:与门、或门、与非门、或非门、异或门等。

2. 高低电平高电平:数字电路中较高电平代数值的范围。

低电平:数字电路中较低电平代数值的范围。

3. 正负逻辑正逻辑:用高电平代表1、低点平代表0。

在数字电路中,一般采用正逻辑系统。

负逻辑:用高电平代表0、低点平代表1。

图14. 集成电路IC(Integrated Circuits):将元、器件制作在同一硅片上,以实现电路的某些功能。

SSI(Small-Scale Integration):£ 10个门电路。

MSI(Medium-Scale Integration):10~100个门电路。

LSI(Large-Scale Integration):1000~10000个门电路。

VLSI(Very Large-Scale Integration):³ 10000个门电路。

3.2 半导体二极管门电路图2二极管加正向电压时导通,伏安特性很陡、压降很小(硅管为0.7V,锗管为0.3V),可以近似看作是一个闭合的开关。

二极管加反向电压时截止,反向电流很小(nA级),可以近似看作是一个断开的开关。

把uD<UT=0.5V看成是硅二极管的截止条件。

图3在低速脉冲电路中,二极管开关由接通到断开,或由断开到接通所需要的转换时间通常是可以忽略的。

然而在数字电路中,二极管开关经常工作在高速通断状态。

由于PN结中存储电荷的存在,二极管开关状态的转换不能瞬间完成,需经历一个过程。

tre=ts+tf 叫做反向恢复时间。

该现象说明,二极管在输入负跳变电压作用下,开始仍然是导通的,只有经过一段反向恢复时间tre之后,才能进入截止状态。

由于tre的存在,限制了二极管的开关速度。

图4图53.3 CMOS门电路MOS门电路:以MOS管作为开关元件构成的门电路。

MOS门电路,尤其是CMOS门电路具有制造工艺简单、集成度高、抗干扰能力强、功耗低、价格便宜等优点,得到了十分迅速的发展。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

公式

1.Cmos传输门

反之,导通2.

OC门

A.B同时为高电平时,T5才导通,Y1输出低电平,Y1=(A*B)’

4. 优先编码器

S’为选通输入端,只有当s’=0时编码器正常工作,

当YS’=0时,表示电路无编码输入,但电路工作正常

当YE’=0时,表示电路有编码输入,而且电路工作正常。

5.

与上差不多P173页

6. 二进制编码器

S1,S2’,S3’为使能端

S为控制端,S=1时进行译码工作,S=0时禁止译码,输出全为1。

P175页

7.二—十进制译码器为74HC42

8.数据选择器

S1用于数据选择器的扩展9

10.

4位超进位加法器74LS283

11.

数值比较器的扩展。

13

CLK=0时Q保持;CLK=0,S=0,R=0时保持;CLK=0,S=1,R=0时Q置1;CLK=0,S=0,R=1时Q置0;CLK=0,S=1,R=1时Q不定;

SD’,RD’是置位端

12

或非门与非门

14.

15

16.边沿触发器p230页

17第六章

18.移位寄存器

双向移位寄存器74LS194A的扩展

19. 同步二进制计数器

当RD’=1.LD’=0时,电路工作在同步预置数状态,

左图主要看74LS161的芯片形状同步十六进制加/减计数器

CLKD减计数脉冲,CLKU加计数脉冲。