全差分放大器设计

全差分运算放大器设计概要

全差分运算放大器设计概要全差分运算放大器是一种常见的电子电路,它可以将输入信号的差分放大,并在输出端提供差分信号。

全差分运算放大器广泛应用于模拟与数字信号处理中,如低噪声放大器、滤波器和交叉耦合放大器等领域。

本文将介绍全差分运算放大器的设计概要,包括电路结构、设计要点和性能指标等。

[图片]该电路由两个共模反馈放大器组成,其中一个作为正放大器,另一个作为负放大器。

输入信号通过差分输入端口加到两个反馈放大器上,经过放大后,在输出端口提供差分信号。

为了保证优良的性能,必须对电路的参数进行适当的设计和调整。

首先,需要确定全差分运算放大器的增益要求。

增益是指输出信号与输入信号之间的比例关系。

在不同的应用中,增益要求可能不同。

根据增益要求,可以选择合适的放大器型号和电路拓扑结构。

其次,需要选择适当的放大器元件。

放大器元件包括晶体管、电阻、电容等。

选择合适的元件是设计成功的关键。

晶体管的选择要考虑其增益、噪声系数、带宽等指标。

电阻和电容的选择要考虑其阻值、容值、精度等因素。

然后,需要确定电路的偏置方案。

全差分运算放大器需要提供适当的偏置电压,以确保电路能够正常工作。

偏置电压的选择要考虑元件的工作状态和参数的稳定性。

常见的偏置方案包括电流镜偏置、电流源偏置等。

设计完成后,需要对电路进行性能测试和优化。

性能测试包括增益、带宽、噪声系数、非线性失真等指标的测试。

根据测试结果,可以进行相应的电路优化,以满足设计要求。

最后,需要对电路进行可靠性分析。

可靠性分析是为了确保电路在长时间工作过程中不会出现故障。

可靠性分析包括温度分析、电路重要参数的敏感度分析等。

全差分运算放大器设计的关键在于电路的结构和元件的选择。

合理的电路结构和适当的元件选择可以使电路具有较高的增益、宽带和低噪声等性能。

此外,还需要注意电路的偏置方案和可靠性分析,以确保电路的正常工作和长时间可靠性。

总之,全差分运算放大器是一种重要的电子电路,具有广泛的应用前景。

采用折叠式结构的两级全差分运算放大器的设计

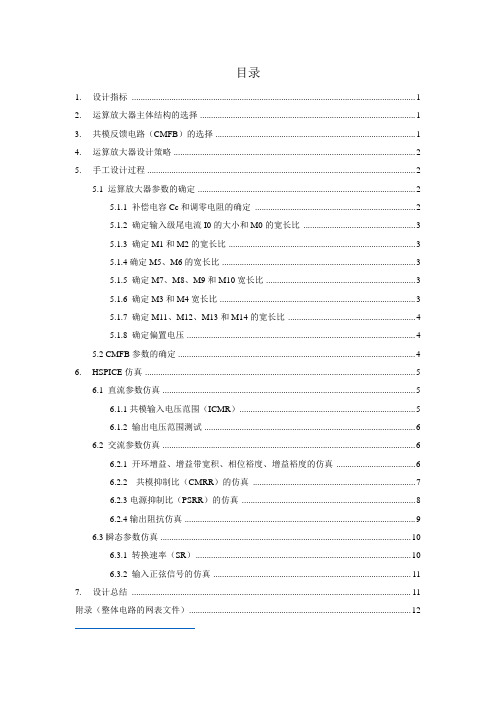

目录1. 设计指标 (1)2. 运算放大器主体结构的选择 (1)3. 共模反馈电路(CMFB)的选择 (1)4. 运算放大器设计策略 (2)5. 手工设计过程 (2)5.1 运算放大器参数的确定 (2)5.1.1 补偿电容Cc和调零电阻的确定 (2)5.1.2 确定输入级尾电流I0的大小和M0的宽长比 (3)5.1.3 确定M1和M2的宽长比 (3)5.1.4确定M5、M6的宽长比 (3)5.1.5 确定M7、M8、M9和M10宽长比 (3)5.1.6 确定M3和M4宽长比 (3)5.1.7 确定M11、M12、M13和M14的宽长比 (4)5.1.8 确定偏置电压 (4)5.2 CMFB参数的确定 (4)6. HSPICE仿真 (5)6.1 直流参数仿真 (5)6.1.1共模输入电压范围(ICMR) (5)6.1.2 输出电压范围测试 (6)6.2 交流参数仿真 (6)6.2.1 开环增益、增益带宽积、相位裕度、增益裕度的仿真 (6)6.2.2 共模抑制比(CMRR)的仿真 (7)6.2.3电源抑制比(PSRR)的仿真 (8)6.2.4输出阻抗仿真 (9)6.3瞬态参数仿真 (10)6.3.1 转换速率(SR) (10)6.3.2 输入正弦信号的仿真 (11)7. 设计总结 (11)附录(整体电路的网表文件) (12)采用折叠式结构的两级全差分运算放大器的设计1. 设计指标5000/ 2.5 2.551010/21~22v DD SS L out dias A V VV V V VGB MHz C pF SR V s V V ICMR V P mWµ>==−==>=±=−≤的范围2. 运算放大器主体结构的选择图1 折叠式共源共栅两级运算放大器运算放大器有很多种结构,按照不同的标准有不同的分类。

从电路结构来看, 有套筒式共源共栅、折叠式共源共栅、增益提高式和一般的两级运算放大器等。

全差分套筒式运算放大器设计

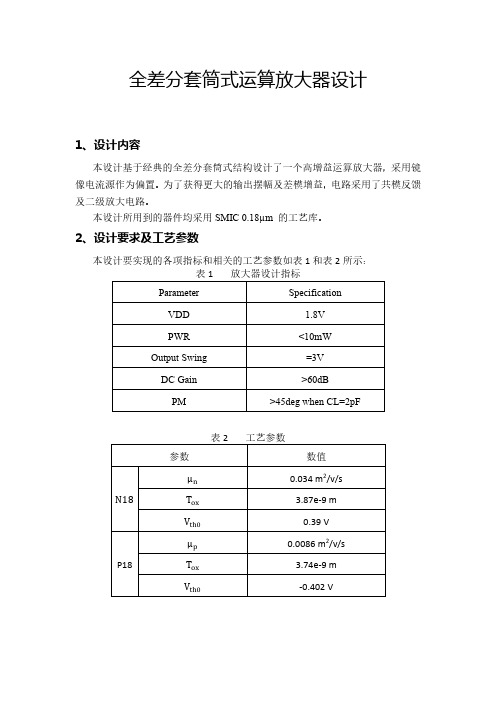

全差分套筒式运算放大器设计1、设计内容本设计基于经典的全差分套筒式结构设计了一个高增益运算放大器,采用镜像电流源作为偏置。

为了获得更大的输出摆幅及差模增益,电路采用了共模反馈及二级放大电路。

本设计所用到的器件均采用SMIC 0.18µm的工艺库。

2、设计要求及工艺参数本设计要实现的各项指标和相关的工艺参数如表1和表2所示:3、放大器设计3.1 全差分套筒式放大器拓扑结构与实际电路图1 全差分套筒式放大器拓扑结构图2 最终电路图3.2 设计过程在图1中,Mb1和M9组成的恒流源为差放提供恒流源偏置,且M1,M2完全一样,即两管子所有参数均相同。

Mb2、M7和M8构成了镜像电流源,M5、M6和M7、M8构成了共源共栅电流源,M1、M2、M3、M4构成了共源共栅结构,可以显著提高输出阻抗,提高放大倍数(把M3的输出阻抗提高至原来的(gm3 + gmb3)ro2倍。

但同时降低了输出电压摆幅。

为了提高摆幅,控制增益,在套筒式差分放大器输出端增加二级放大。

本设计中功率上限为10mW,可以给一级放大电路分配3mA的电流。

设计要求摆幅为3V,所以图1中M1、M3、M5、M9的过驱动电压之和不大于1.8-3/2=0.3V。

我们可以平均分配每个管子的过驱动电压。

根据漏电计算流公式(1)(考虑沟道长度调制效应),可以计算出每个管子的宽长比。

I D=12μn C ox WL(V GS−V TH)2(1+λV DS)(1)其中,C ox等于ε/t ox,μn和t ox可以从工艺库中查找。

4、仿真结果经过调试优化之后的仿真结果如以下各图所示:图3 增益及相位裕度从图中可以看出,本设计的低频增益达到了74.25dB,达到了预期要求。

3dB 带宽为35kHz左右,比较小,可见设计还有改进的余地。

当CL为2pF时,相位裕度:PM=180°+∠βH(ω)=180°−125.5°=54.5°电源电压为1.8V时,输出摆幅如下图所示,达到了3V。

低电压高速CMOS全差分运算放大器设计双

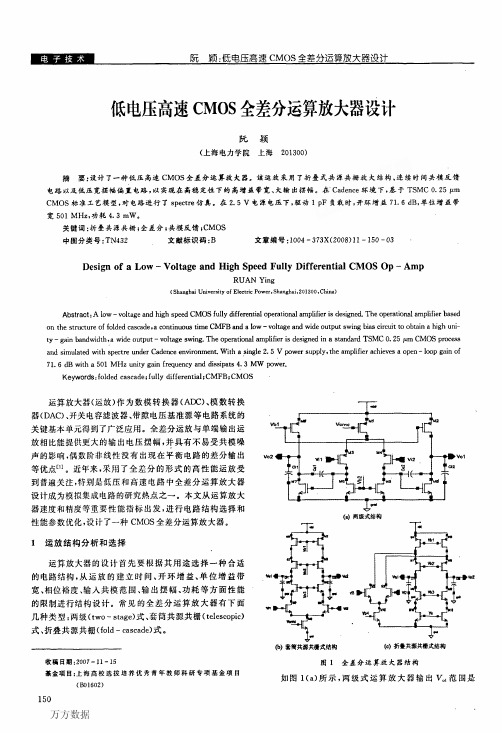

运算放大器的设计首先要根据其用途选择一种合适 的电路结构,从运放的建立时问、开环增益、单位增益带 宽、相位裕度、输入共模范围、输出摆幅、功耗等方面性能 的限制进行结构设计。常见的全差分运算放大器有下面 几种类型:两级(two—stage)式、套筒共源共栅(telescopic) 式、折叠共源共栅(fold—cascade)式。

4‘结语

本文使用TSMC公司的CM025工艺

设计并实现了一个低压高速全差分运算放

大器。采用折叠共源共栅结构,在达到较高

的带宽同时,增大了输出摆幅。连续时间共

模反馈电路以及低压宽摆幅偏置电路,实现

(1)信置电路OO半电路小信号等效模型

图3偏置电路及半电路小信号等效模型

了电路的高稳定性。该运放在2.5 V电源 电压下,’单位增益带宽可以达到501 MHz, 直流增益71.6 dB,相位裕度51。,功耗

P。《P,,更接近于原点,因此P2为折叠共源共栅运放的 主极点,P。为次极点。

要提高开环增益A。,可以采取增加M8,M9的跨导和

1 5】

沟逝长度,但将引起其源极寄生电容的增加和漏源饱和电 正减小,从而降低运放的次极点频率。同样增加M10, M11的沟道长度,会使A。增加而次极点频率减小。考虑 到M4,M5,M6,M7不在信号通路上,因此可以增加其沟 道长度球增加输出阻抗,而不降低工作速度。

△gM9(r2//rlo)r9 R。。“M7一r4+r7[1+(gM7+gM7b)^]

△gM7 r7 r4 r为MOS管的小信号输出电阻。负载电容C。远大于MOS 管各端的寄生电容,CL△cD瞰+CD曲+CD酊。。

节点1对应的极点P。:

P-=一石万勿习丽i1冠i而△一等

节点2对应的极点P。:

全差分运算放大器设计

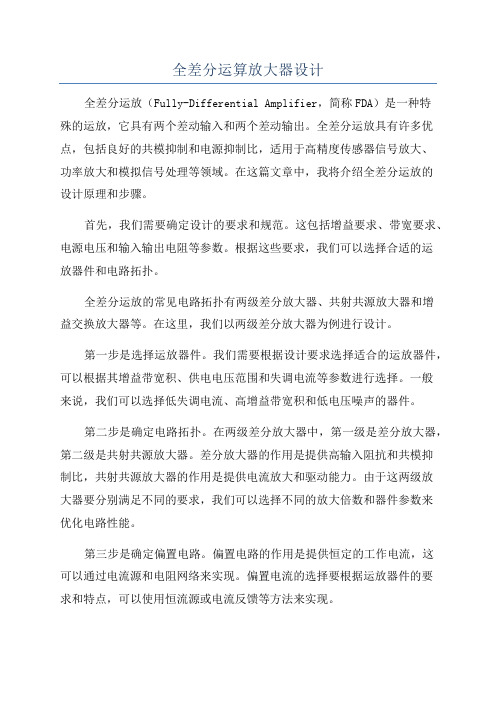

全差分运算放大器设计全差分运放(Fully-Differential Amplifier,简称FDA)是一种特殊的运放,它具有两个差动输入和两个差动输出。

全差分运放具有许多优点,包括良好的共模抑制和电源抑制比,适用于高精度传感器信号放大、功率放大和模拟信号处理等领域。

在这篇文章中,我将介绍全差分运放的设计原理和步骤。

首先,我们需要确定设计的要求和规范。

这包括增益要求、带宽要求、电源电压和输入输出电阻等参数。

根据这些要求,我们可以选择合适的运放器件和电路拓扑。

全差分运放的常见电路拓扑有两级差分放大器、共射共源放大器和增益交换放大器等。

在这里,我们以两级差分放大器为例进行设计。

第一步是选择运放器件。

我们需要根据设计要求选择适合的运放器件,可以根据其增益带宽积、供电电压范围和失调电流等参数进行选择。

一般来说,我们可以选择低失调电流、高增益带宽积和低电压噪声的器件。

第二步是确定电路拓扑。

在两级差分放大器中,第一级是差分放大器,第二级是共射共源放大器。

差分放大器的作用是提供高输入阻抗和共模抑制比,共射共源放大器的作用是提供电流放大和驱动能力。

由于这两级放大器要分别满足不同的要求,我们可以选择不同的放大倍数和器件参数来优化电路性能。

第三步是确定偏置电路。

偏置电路的作用是提供恒定的工作电流,这可以通过电流源和电阻网络来实现。

偏置电流的选择要根据运放器件的要求和特点,可以使用恒流源或电流反馈等方法来实现。

第四步是确定反馈电路。

反馈电路的作用是控制放大倍数和增益稳定性,可以使用电阻、电容或者电流源等元件来实现。

选择适当的反馈方式可以减小失调电压和非线性,提高性能。

第五步是进行电路仿真和优化。

通过电路仿真,我们可以验证设计的性能和满足要求。

优化可以通过调整电路参数和进行迭代仿真来实现,以达到设计要求。

第六步是进行电路布局和线路板设计。

在设计布局时,要注意分离放大器电路和干扰源,减少电源和信号线的串扰。

线路板设计要保证差分信号走线的对称性和阻抗匹配,以提高传输性能。

模拟集成电路设计——两级全差分高增益放大器设计_2

全差分高增益放大器的设计一、设计产品名称全差分高增益放大器二、设计目的1.掌握模拟集成电路的基本设计流程;2.掌握Cadence基本使用方法;3.学习模拟集成电路版图的设计要点;4.培养分析、解决问题的综合能力;5.掌握模拟集成电路的仿真方法;6.熟悉设计验证流程方法。

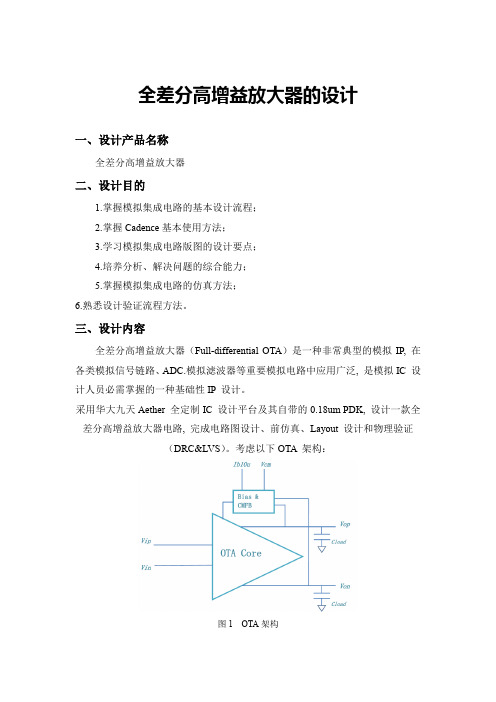

三、设计内容全差分高增益放大器(Full-differential OTA)是一种非常典型的模拟IP, 在各类模拟信号链路、ADC.模拟滤波器等重要模拟电路中应用广泛, 是模拟IC 设计人员必需掌握的一种基础性IP 设计。

采用华大九天Aether 全定制IC 设计平台及其自带的0.18um PDK, 设计一款全差分高增益放大器电路, 完成电路图设计、前仿真、Layout 设计和物理验证(DRC&LVS)。

考虑以下OTA 架构:图1 OTA架构四、电路设计思路模拟集成电路的设计分为前端与后端, 设计流程可以分为明确性能要求、选择电路结构、计算器件参数、原理图绘制、前仿真、版图绘制、DRC设计规则检查、LVS版图与电路图一致性检查、寄生参数提取及后仿真、流片测试。

本次实验使用基于华大九天Aether 全定制IC 设计平台及其自带的0.18um PDK, 实现模拟集成电路全差分高增益放大器的全流程设计与仿真。

(1)性能指标:需要验证三种PVT Corner:a) 电源电压1.8V, 温度27℃, corner 为TT;b) 电源电压1.6V, 温度80℃, corner 为SS;c) 电源电压2.0V, 温度-40℃, corner 为FF;要求各Corner 下开环技术指标(含Cload=10fF):①放大器开环DC 增益Av0≥90dB;②0dB 带宽BW0≥500MHz;③相位裕度Phase Margin≥50°。

④DC 抑制比PSRR-0≥60dB, (3*2=6 分)⑤10MHz 时抑制比PSRR-10M≥45dB。

全差分运算放大器设计

全差分运算放大器设计岳生生(200403020126)一、设计指标以上华0.6um CMOS 工艺设计一个全差分运算放大器,设计指标如下:✧直流增益:>80dB✧单位增益带宽:>50MHz✧负载电容:=5pF✧相位裕量:>60度✧增益裕量:>12dB✧差分压摆率:>200V/us✧共模电压:2.5V (VDD=5V)✧差分输入摆幅:>±4V二、运放结构选择运算放大器的结构重要有三种:(a )简单两级运放,two-stage 。

如图2所示;(b )折叠共源共栅,folded-cascode 。

如图3所示;(c )共源共栅,telescopic 。

如图1的前级所示。

本次设计的运算放大器的设计指标要求差分输出幅度为±4V ,即输出端的所有NMOS 管的,DSAT NV之和小于0.5V ,输出端的所有PMOS管的,DSAT PV之和也必须小于0.5V 。

对于单级的折叠共源共栅和直接共源共栅两种结构,都比较难达到该要求,因此我们采用两级运算放大器结构。

另外,简单的两级运放的直流增益比较小,因此我们采用共源共栅的输入级结构。

考虑到折叠共源共栅输入级结构的功耗比较大,故我们选择直接共源共栅的输入级,最后选择如图1所示的运放结构。

两级运算放大器设计必须保证运放的稳定性,我们用Miller 补偿或Cascode 补偿技术来进行零极点补偿。

三、性能指标分析1、 差分直流增益 (Adm>80db)该运算放大器存在两级:(1)、Cascode 级增大直流增益(M1-M8);(2)、共源放大器(M9-M12) 第一级增益1351113571135135753()m m m o o o o o m m m m o o o o m m g g gg gg G A R r rr r g g r r r r=-=-=-+第二级增益92291129911()m o o o m m o o gg G AR r rgg=-=-=-+整个运算放大器的增益:4135912135753911(80)10m m m m overallo o o o m m o o dB g g g gAA A g g g gr r r r ==≥++2、 差分压摆率 (>200V/us )转换速率(slew rate )是大信号输入时,电流输出的最大驱动能力。

(完整word)全差分高增益、宽带宽CMOS运算跨导放大器的设计

目录1 引言 (1)2 软件介绍 (3)3 运算放大器设计基础 (5)3.1运放的主要性能指标 (5)3.2运算放大器的基本结构 (6)3.2.1全差分运放 (6)3.2.2套筒式结构 (7)3.2.3折叠式结构 (8)4 系统总体设计 (10)4.1电路设计的整体结构 (10)4.2 主放大电路设计 (11)4.3 偏置电路的设计 (13)4.4 输出级的设计 (13)4.5 共模反馈的设计 (14)4.6 总体布局 (15)5 仿真与分析 (17)5.1运放直流与交流特性 (17)5.2噪声特性分析 (19)5.3电源抑制比 (19)5.4设计指标 (20)5.5放大器参数 (21)6 版图设计与分析 (22)6.1 L-Edit介绍 (22)6.2版图设计规则 (22)6.3基本器件版图设计 (23)6.3.1 NMOS版图设计 (23)6.3.2 电容电阻版图设计 (24)6.4版图的总体设计 (26)6.4.1主电路模块版图 (26)6.4.2偏置模块版图 (27)6.4.3输出模块版图 (27)6.4.4整体模块版图 (28)6.5 LVS版图比对 (29)7 结论 (31)谢辞 ................................................................................................... 错误!未定义书签。

参考文献 .. (32)附录1 (33)附录2 (35)1 引言集成运算放大器(Integrated Operational Amplifier)简称集成运放,是由多个CMOS管与电容电阻通过耦合方式实现提高增益的模拟集成电路[1]。

集成运放具有增益高、输入阻抗大、输出阻抗低、共模抑制比高和失调与漂移性小等优点,而且当输入电压值为零时,输出值也为零。

集成运放是构成常用集成电路系统的通用模块[2] [3]。

(p)一种高性能低功耗两级全差分运算放大器设计

收稿日期:2009202216 作者简介:翁 迪(1983—),男,硕士研究生.通信联系人:叶 凡,男,讲师,E 2mail :fanye @f .文章编号:042727104(2009)0420465205一种高性能低功耗两级全差分运算放大器设计翁 迪,范明俊,叶 凡,任俊彦(复旦大学专用集成电路与系统国家重点实验室,上海201203)摘 要:分析并设计了一种高速、高增益、低功耗的两级全差分运算放大器.该运算放大器用于高速高精度模数转换器中.运算放大器第一级采用增益自举cascode 结构获得较大的直流增益,采用2个新的全差分运算放大器替代传统的4个单端运算放大器作为增益自举结构.该放大器采用SMIC 0.18μm CMOS 工艺设计,电源电压1.8V ,直流增益125dB ,单位增益带宽300M Hz (负载3p F ),功耗6.3mW ,输出摆幅峰峰值达2V.关键词:运算放大器;增益自举;2级;全差分;高增益中图分类号:TN 492 文献标志码:A运算放大器(op amp )作为关键的模拟模块,广泛应用于开关电容滤波器、Σ2Δ调制器以及模数转换器等.在这些电路中,速度和精度两大重要因素都是由运算放大器的各种性能来决定的.例如在精度10bit 速度20M Hz 以上的高速高精度流水线模数转换器设计中,高的直流增益和大的单位增益带宽会降低运算放大器闭环工作时的增益误差和线性建立时间引起的误差,而大的输出摆幅可以有效的提高性噪比,从而可以在较小的电容负载的情况下达到较高的信噪失真比,有效地实现高速高精度和低功耗的目标;流水线模数转换器中功耗主要来自于运算放大器,所以低功耗运算放大器会使整个模数转换器功耗显著降低.一般而言,长沟道、低偏置电流、多级运算放大器可以实现高增益,然而会导致多个极点,难以达到高速大带宽的要求.共源共栅(cascode )结构的运算放大器具备频率特性好、主极点由负载电容决定、功耗最低等优点,但是输出摆幅比较小,特别在低电源电压情况下,这种缺点就更加显得突出.综合考虑,2级运算放大器可以在高增益、大输出摆幅和带宽间达到较好的平衡;高增益可以采用带增益自举的第1级实现,而带宽和速度可以在功耗允许的情况下尽量加大电流来实现.本文提出了带有增益自举结构的两级全差分运算放大器设计方案.由于这种方案目前在国内还属首次采用,所以本文对电路性能作了全面详细的分析.1 运算放大器总体结构和性能分析运算放大器应用于高性能流水线模数转换器时,运算放大器的增益要满足模数转换器中采样保持的增益误差要求和线性度要求,为达到14位精度,要求运算放大器开环直流增益大于100dB [1],而一般的2级运算放大器增益大概在80dB 左右.为了提高增益,本文提出的方案是第1级采用带有小运算放大器OPN 和O PP 增益自举的套筒式共源共栅(telescopic cascode )结构,第2级采用一般的共源放大器,电路结构如图1所示.为了保证运算放大器的稳定性,采用Miller 补偿技术进行零极点补偿,采用开关电容共模反馈以调节稳定工作点.1.1 直流增益分析该运算放大器存在2级:第1级是带增益自举的cascode 级;第2级是共源放大级.第1级增益:A 1=-G mI R OI =-g m1(R O11∥R O12),其中R O11=[1+(1+A n )g m6r o6]r o8,R O12=[1+(1第48卷 第4期2009年8月复旦学报(自然科学版)Journal of Fudan University (Natural Science )Vol.48No.4Aug.2009图1 带有增益自举的2级全差分运算放大器总体结构Fig.1 Overall structure of t he fully differential gain 2boosted two 2stage op amp+A p )g m4r o4]r o2,A n ,A p 是自举运算放大器OPN 、OPP 的直流增益,在A n ≈A p µ1的情况下,A 1≈A n [-G m (g m6r o6r o8∥g m4r o4r o2)]=A n ・A 1′,其中A 1′=-G m (g m6r o6r o8∥g m4r o4r o2)为不带增益自举的第1级的增益.第2级增益:A 2=-G mII R OII =-g m2(R 10∥R 12).总增益:A =A 1・A 2≈A n ・A 1′・A 2.(1)由上述分析可以看出,电路总的直流增益等于主电路cascode 级(m 1~m 8)、主电路输出级(m 9~m 12)和增益自举电路(OPN 或O PP )3者直流增益之积.这样设计时就可以把总增益分配到各级电路中去.每一级只要达到所指定的增益目标,总增益就能满足要求[223].1.2 单位增益带宽该运算放大器结构符合标准两级运算放大器性能分析方法[3],电路中负载电容C L ,补偿电容为C c ,主极点产生于第1级的输出端,其大小等于从m 4和m 6(或m 3,m 5)的漏端看进去的输出电阻和电容乘积的倒数:P 1=1/(R OI R OII G mII C c );次主极点位于第2级的输出端:P 2=G mII /C L ;单位增益带宽:GB m =G mI /C c ;从上面可以看出增益自举电路对整个电路的次主极点和单位增益带宽没有影响,只是会减小主极点频率.采用Miller 电容补偿会在右半平面产生一个零点:Z 0=1/(C c (1/G mII -R Z )),采用调零电阻R Z 控制零点的位置把零点从右半平面移到左半平面的次主极点P 2上,当R Z =(C c +C L )/(G mII C c )时,Z 0=1/(C c (1/G mII -R Z ))=-G mII /C L ,这样输出负载电容引起的极点就去除掉了,当然由于温度,工艺和电压等的变化会导致R Z ,C c 和C L 以及G mII 发生变化,但是在设计中,这些变量都有一定的裕度,在设计中也充分考虑,所以,也就避免了调节后的负零点位于GB W 内的现象.要满足60°相位裕度,则电路的次主极点至少要大于2.2GB m [3].即:G mII /C L >2.2G mI /C c ,若零点G mII /C L =10GB m =10G mI /C ,则C c >2.2C L G mI /G mII =0.22C L .1.3 增益自举电路与主电路的匹配传统的增益自举技术如图2所示需要额外实现4个单输入单输出的运算放大器,这样就增加了线路的复杂性、功耗和面积,同时在利用电流镜进行双端转单端输出的过程中,也消耗了运算放大器的动态幅度,不利于电路的设计和实现.这里采用2个全差分输入输出的运算放大器作为增益自举电路,由于左右两端完全对称的结构,从而可以减小相应的晶体管间由于不匹配所引入的噪声.增益自举电路主要起增加664复旦学报(自然科学版)第48卷cascode 级输出电阻的作用,因此可以将起功耗和面积尽量减小,设计时将其管子的宽长比和电流取为外部主电路的1/3左右比较合宜[2].图2 传统的增益自举技术Fig.2 Traditional gain 2boosted technology自举放大器OPN 、O PP 与主电路M 5、M 6和M 3、M 4形成闭环反馈,可以自动调整,而OPN 和OPP 输入端也有用来控制输入的共模电平.如果OPN 、O PP 速度太快,就会导致运算放大器稳定性方面问题[4].为了系统稳定,O PN 、OPP 单位增益带宽GB sub 必须满足:P 1<GB sub <P 2.(2)同时自举电路的加入有可能在GB sub 的地方产生一个极零点对(pole 2zero ),而极零点对会严重影响运算放大器建立时间,为了防止GB sub 处产生的极零点对对运算放大器闭环工作时的影响,GB sub 还必须满足:βGB <GB sub <P 2,(3)β为运算放大器闭环工作时的反馈因子,在高精度流水线模数转换器中,采样保持器采用电荷重分布形式,反馈因子为1/2,所以只要满足:1/2GB <GB sub <P 2,系统稳定性和建立时间方面要求都可以满足.增益自举小电路所选择的结构是折叠共源共栅结构如图1所示.使用这种结构主要考虑到速度和输入、输出电平的需要[5].输入级中间2个管子是用来稳定输入级尾电流源漏端电压. 偏置电路和共模反馈电路增益自举电路和主电路使用相同的偏置电压,通过折中调节最后整个电路只需要2路偏置电压,选用共[5],增大电流镜输出电阻,使输出电压更稳定并且电路结构简单,如图3所示.全差分运算放大器需要共模反馈电路确定其共模电平.共模反馈的电路多种多样,不过在这里开关电容共模反馈[5]电路相比其他电路来说具有独特的优势.首先它相对于连续时间共模反馈电路具有更高的动态范围,其次,它不会引入附加的极点且其线性度也非常好,另外,运算放大器应用在开关电容电路中无需增加额外的时钟,应用比较方便.为了保证系统能够稳定而又快速地进入工作,在第1、第2级分别采用了共模反馈.2 性能分析表1列出了带有增益自举和不带增益自举结构两级全差分运算放大器以及2个用来增益自举的辅助运算放大器OPN 、OPP 各项性能情况.可以看到,仿真结果与上述推理基本相符.带有增益自举的两级全差分运算放大器直流增益等于辅助运算放大器和没有增益自举的两级全差分运算放大器直流增益之和(都以dB 形式表示).总电路的单位增益带宽基本上与不带增益自举两级全差分运算放大器带宽相等.在辅助运算放大器OPP 、OPN 带宽满足(3)式时运算放大器建立时间20ns ,与不带增益自举时18ns 差不764 第4期翁 迪等:一种高性能低功耗两级全差分运算放大器设计图3 偏置电路和开关电容共模反馈电路Fig.3 Bias and switched 2capacitor CMFB多,当不满足(3)式只满足(2)式时运算放大器建立时间延长到39ns ,如表1中所示.可见OPP 和OPN 的带宽影响整个运算放大器建立时间比较明显.表1 运算放大器及其各子模块电路性能比较Tab.1 Op amp and other sub 2module performanceamplifierG DC /dB f B /M Hz C L /p F t set /ns φ/(°)P /μW OPN 39.5290(>321/2)19.2(<321/2)0.12.0——76.090.6 456OPP 45 251(>321/2)16.5(<321/2)0.12.0——74.389.2 375wit hout gainenhancement104.0321.0 3.01869.05470wit h gainenhancement 141.0320.0 3.0203969.06430 最后,运算放大器通过SM IC 0.18μm CMOS 工艺实现,经过流片测试,在电源电压1.8V 的情况下,增益达到125dB ,单位增益带宽300M Hz.表2详细列举了本运算放大器各项指标性能在仿真和测试后的结果比较,图4给出了用Hspice 仿真的幅频和相频特性;图5则是测试时的大信号阶跃响应.从中可以看出仿真和测试结果的总体性能差异在比较合理的范围内,而差异也主要是由于版图,寄生参数和工艺原因导致的偏差,也就是在于仿真的理想性和电路流片实现之间的差异,证明了这种运算放大器设计方案在现实应用中的可行性.并且,从流片测试结果看,总体设计也基本满足高精度低功耗电路对运算放大器的要求,而且在后期的ADC 的流片测试结果也显示该放大器设计保证了ADC 的性能.表2 运算放大器仿真、测试结果Tab.2 Simulation and testing resultsperformanceA out /V G /dB f B /M Hz t set /ns S R /(V ・μs ∃1)P /mW φ/(°)simulation214132020207 6.3469measured 212529931198 6.30—864复旦学报(自然科学版)第48卷本文提出了一种高性能低功耗的两级全差分运算放大器设计,采用0.18μm CMOS 工艺实现.利用增益自举技术,运算放大器开环增益可达到125dB ,主运算放大器为2级结构,输出摆幅在电源电压1.8V 情况下峰峰值可达到2V ,电压转换率约200V/μs.文中详细阐述了主运算放大器与辅助运算放大器之间匹配问题,在保证运算放大器其他性能不变的情况下,合理缩减辅助运算放大器的功耗,总功耗仅有6.3mW.该运算放大器被应用于低功耗14位32.5M Hz 流水线模数转换器的采样保持电路中.参考文献:[1] Yang W ,Kelly D ,Mehr I ,et al .A 32V 340mW 142b 752Msps CMOS ADC with 852dB SFDR at Nyquistinput [J ].J ournal of S oli d 2S tate Ci rcuits ,2001,36(12):193121936.[2] 柳 逊,闫 娜,吴晓铁,等.一种高性能运算放大器的设计[J ].微电子学与计算机,2005,22(6):28233.[3] Allen P E ,Holberg D R.CMOS Analog Circuit Design [M ].2版.冯 军,李智群,译.北京:电子工业出版社,2000.[4] Bult K ,G eelen G J G M.A fast 2settling CMOS op amp for SC circuits with 902dB DC gain [J ].J ournalof S oli d 2S tate Ci rcuits ,1990,25(6):137921384.[5] Lloyd J ,Lee Hae 2Seung.A CMOS op amp with fully 2differential gain 2enhancement [J ].T ransactions onCi rcuits A nd S ystems ,1994,41(3):2412243.[6] Recoules H ,Bouchakour R ,Loumeau P.A Comparative study of two SC 2CMFB networks used in fullydifferential O TA [C]∥Proceedings of 1998IEEE International Conference on Electronics ,Circuits and Systems.Portugal :IEEE Press ,1998.Design of a High 2Performance and Low 2Pow erTwo 2Stage OP AmpWE NG Di ,FAN Ming 2jun ,YE Fan ,RE N J un 2yan(A S IC &S ystem S tate Key L aboratory ,Fudan Universit y ,S hanghai 201203,China )Abstract :A high 2gain low 2power high 2speed fully differential two 2stage operational amplifier wit h a DC 2gain of 125dB and a gain 2bandwidt h of 300M Hz is analyzed and designed in a 0.18μm SMIC CMOS process.Its output swing reaches 2V and power consumption is only 6.3mW.the high DC 2gain is reached t hrough gain 2enhancement at t he first pared wit h t he traditional gain 2enhancement technology wit h four single 2ended output amplifiers ,two new fully differential amplifiers are utilized here for gain 2enhancement.The DC 2gain ,output swing and power consumption are better than t hat of t he traditional operational amplifier.K eyw ords :operational amplifier ;gain 2enhancement ;two 2stage ;fully 2differential ;high DC 2gain 964 第4期翁 迪等:一种高性能低功耗两级全差分运算放大器设计。

全差分CMOS运算放大器的设计

全差分CMOS运算放大器的设计全差分CMOS运算放大器(Fully Differential CMOS Operational Amplifier)是一种常用于模拟、混合信号和通信电路中的放大器。

全差分运算放大器结合了差分放大器和普通运算放大器的优点,具有更好的共模抑制、抗干扰能力和更高的增益。

1.设计差动放大器:差动放大器是全差分CMOS运算放大器的核心部分,其一般由两个输入差分对和一个负载电阻组成。

在设计差动放大器时,首先需要确定放大器的增益、带宽和功耗等要求。

然后,选择适当的晶体管尺寸和偏置电流来满足这些要求。

2.设计电流镜:电流镜主要用于稳定差动放大器的工作点。

常用的电流镜电路有P型电流镜和N型电流镜。

在设计电流镜时,需要考虑放大器的输入阻抗、输出阻抗和功耗。

3.设计共模反馈电路:共模反馈电路主要用于提高全差分CMOS运算放大器的共模抑制比。

在设计共模反馈电路时,需要确定合适的电压分压比例和电容值,以及选择合适的晶体管尺寸和偏置电流。

4.偏置电流源设计:5.电源设计:6.输入和输出接口设计:7.稳定性分析和优化:在设计全差分CMOS运算放大器时,还需要进行稳定性分析和优化。

常用的稳定性分析技术有迭代法、校正法和频率响应法。

稳定性优化技术有补偿电容法、极点分布法和增益调整法。

8.仿真和验证:最后,设计完成的全差分CMOS运算放大器需要进行仿真和验证。

常用的仿真和验证工具有SPICE软件、电路仿真器和实验测量仪器。

通过仿真和验证,可以评估放大器的性能和电路的可靠性。

最后,需要注意的是,在进行全差分CMOS运算放大器的设计时,应遵循设计规范和标准,如功耗规范、电压规范和噪声规范,以确保设计的可靠性和一致性。

同时,应密切关注工艺制程、温度变化等因素对电路性能的影响,并进行相应的校准和补偿。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

对于全差分放大器,一般可以得到更大的swing (由于差分信号),同时可以实现对共模干扰、噪声以及偶数阶的非线性的抑制;但其需要有两个匹配的反馈网络,以及共模反馈电路

顺便提一下,对于全差分的折叠共源共栅(folded cascode)放大器,需要注意

转换速率(正向与负向)对输入对差分对的尾电流源和cascode电流源的考虑

非主极点的位置–输入对管的drain节点(注意全差分没有镜像极点的问题..),如果考虑PMOS输入的结构,将会折叠到n管的cascode,从而减小此节点阻抗,提高此非主极点的频率;但是P输入结构亦有其问题,如直流增益和cmfb电路的速度(考虑cmfb控制的为cascode的pmos电流源)

关于共模反馈CMFB

从反馈环路来看,共模的稳定问题来源于闭环的共模增益:由于输入差分对的尾电流源的local-feedback,通常共模增益较小,导致运放无法控制其输出共模点;通过CMFB共模反馈电路,可以提高共模反馈环路的增益,以稳定共模信号。

设计CMFB需考虑补偿以减小环路的稳定时间(settling time)和提高稳定性。

从性能上,我们希望共模反馈的单位增益带宽足够大,但由于cmfb的环路相较于差模通路可能有更多高频极点,故此在一定的功耗要求下其UGB一般比较难做的高,有书中提到可以将其设计为差模UGB 的1/3

一般共模反馈的方法是控制放大器的电流源,这里如果是folded-cascode的结构,可以考虑用cmfb控制cascode的电流源而不是输入差分对的电流源—-因其在共模环路中有较少的节点–>更容易补偿等..(另一种考虑是控制尾电流源可能导致共模增益的问题)

另外,对于cmfb控制的尾电流源,常见将尾电流源分为两半,其中之一由cmfb控制,另一半接恒定偏置电流;这种结构的具体分析可见Gray书12.4.2节的内容,简单来说,single-stage的opamp中控制尾电流源的cmfb结构,其UGB主要为gmt/CL, 其中gmt为尾电流源的跨导,这里拆分尾电流源来减半cmc共模控制的部分,这样UGB减小,即缩减带宽来提升共模反馈环路的相位裕度,当然cmfb的增益相应也减小了;另外恒定偏置部分也可帮助共模电压的初始建立,减小cmfb大的扰动。

具体的,共模反馈可以分为连续时间和开关电容两类

连续时间的共模反馈

一般的问题是信号幅度的限制和共模信号干扰,具体的共模反馈的方法:

1.电阻分压resistive-divider (如下左图)

电阻和cm-sense amplifier的输入电容会引入一个极点,可以通过在电阻上并联电容的方法,引入一个左半平面零点,来减小高频极点的影响

另外一个问题,sense resistor 会load输出,减小了开环差动增益,考虑通过voltage buffer 的办法,如source follower,但其也会限制输出的差动摆幅(output swing)

关于控制尾电流源和直接inject电流的方法的比较(Gray 书)

2. 双差分对或DDA–differential difference amplifier (如下右图)

对输出的differential –swing的限制(由于直接取分输出信号到cmfb的差分对,为使其工作于饱和区,运放输出swing受限于cmfb差分对的差模输入范围)

详细的大信号分析–>输出差模对输出共模的影响

3. 深线性区的mos管transistors in triode region (主要可见Razavi书中的分析)

对输出swing的要求

较小的cmfb环路增益和带宽

关于开关电容cmfb

SC-CMFB结构,一般常用在开关电容电路中,对比连续时间的CMFB电路,他支持更大的信号摆幅,同时减小了对输出swing的限制,也没有阻性的负载效应;但需要两相非交叠时钟,同时会因非线性时钟馈通注入噪声。

开关电容cmfb一般结构可见下图,简单来说可以认为电路通过C2取得输出信号共模,并用C1给其以DC点(settle到Vcmref-Vbias的电压)。

一般的开关电容cmfb:C1应在C2大小的1/4到1/10之间(Ken Martin),但是也有其他论文谈到不同的选择方法,如:

Ojas Choksi, L. Richard Carley: Analysis of Switched-Capacitor Common-Mode Feedback Circuit, IEEE Transactions on Circuits and Systems—II: Analog and Digital Signal Processing, V ol. 50, No. 12, DEC 2003中具体关于电容大小和开关非理想性的介绍

对于SC-CMFB 的仿真, 与开关电容电路类似, 主要是pss –> pac 的方法(当然另外也有提到先做瞬态.tran 分析,再利用‘prevoppt’取settle 后op 点做ac 分析的方法);一般可以参考的是Designer’s Guide 上的‘Simulating switched-capacitor filters with SpectreRF’的这篇论文;如果主要是对差模信号的分析,也可将开关电容的共模反馈电路用连续时间的近似模型代替,如下图。