maxplus-ii安装说明[新版].ppt

MaxPlusII简易用户使用入门指南

PPT文档演模板

MaxPlusII简易用户使用入门指南

生成一个图形设计文件

•输入 LPM 符号

lpm (library parameterized megafunction) 符号的输入方法与先前符 号的输入方法相同。 在 Enter Symbol 对话框出现后,在 symbol Libraries 框中选择 “..\maxplus2\max2lib\mega_lpm” 路径。 在 Symbol Files 框中选择您需要的 lpm 符号。 双击参数框 (位于符号的右上角),输入您需要的 lpm 的参数。在 Port Status 框中选择 Unused ,可将您不需门指南

PPT文档演模板

2020/11/2

MaxPlusII简易用户使用入门指南

ES-Site 授权 及 PLS-WEB 特点

•设计输入

•项目编译

•MAX+PLUS II •MAX+PLUS II

•文本编辑器

•图形编辑器

•编译器 •网表提取器

•数据库 •建库器

•项目校验

输入 74 系列的符号

MAX+PLUS II 为实现不同的逻辑功能提供了许多符号,如:图元符 号 ,兆功能符号和宏功能符号。在图形编辑器文件中可直接使用以上 符号。74 系列符号的输入方法和上页图元输入的方法相同。 当 Enter Symbol 对话框出现后,在symbol Libraries 对话框中选 择 “..\maxplus2\max2lib\mf”路径。 在 Symbol Files 对话框中,选择您需要的 74 系列符号。

生成一个图形设计文件

输入 Altera 图元

选择工具按钮有效时,在图 形编辑器窗口的空白处单击 鼠标左键以确定输入位置, 然后选择Enter Symbol,或 双击鼠标左键。

Max+Plus II 使用说明 (一)

Max+Plus II 使用说明 (一)Max+Plus II 是一款基于计算机辅助设计 (CAD) 技术的数字逻辑电路仿真软件。

这款软件由美国英特尔公司 (Intel) 开发,可用于设计和验证数字逻辑电路,包括组合逻辑电路和时序逻辑电路。

本文将详细介绍 Max+Plus II 的使用说明,帮助用户更好地了解和应用该软件。

一、软件下载与安装Max+Plus II 可以从英特尔公司的官方网站上下载,安装过程简单,用户只需要按照安装向导逐步完成即可。

注意,该软件只能在 32 位版本的 Windows 操作系统上运行,所以用户需要确保自己的电脑系统符合要求。

二、主要功能介绍1. 逻辑设计:Max+Plus II 提供了完整的数字逻辑设计工具箱,包括位宽选择、时钟控制、计数器设计等工具,支持标准硬件描述语言VHDL 和 Verilog。

2. 仿真调试:Max+Plus II 可以进行逻辑仿真和时序仿真,模拟电路的输入输出信号,检查电路设计的正确性和可行性。

3. 器件库管理:Max+Plus II 内置了丰富的器件库,用户可以根据需要选择和添加器件,支持包括 FPGA、CPLD、RAM、ROM 等在内的多种器件类型。

4. 项目管理:Max+Plus II 支持多个项目的并行管理,用户可以轻松创建、打开、保存和关闭项目,以及在不同的项目之间进行切换操作。

三、使用步骤1. 创建项目:用户需要先创建一个新项目,然后选择适当的器件和设计语言,制定设计规范和参数,创建设计文件,并建立测试目标。

2. 设计与仿真:用户可以使用逻辑设计工具箱,将逻辑元件(例如逻辑门、寄存器、计数器等)组合起来构建数字逻辑电路,并在仿真界面中进行测试和验证。

3. 下载与调试:用户完成设计和仿真之后,可以将设计文件下载到目标设备中,然后进行实际调试和测试,以验证电路的正确性和可行性。

四、注意事项1. 在使用 Max+Plus II 进行数字逻辑电路设计时,需要遵循设计规范和标准,保证设计的正确性和可靠性。

MAX+PLUS II学习课件

设计输入 提供图形、文本和波形编辑器实现图形、AHDL、VHDL、Verilog HDL或波形的输入,也可输入网表文件。 项目编译 提供了一个完全集成的编译器(Compiler),它可直接完成从网 表提取到最后编程文件的生成,包含时序模拟、适配的标准文件。 项目校验 对设计项目的功能、时序进行仿真和时序分析,判断输入输出间 的延迟。 项目编程 将你的设计下载/配臵到你所选择的器件中去。

图形 文件

文本 文件

文本 文件

图形输入 Xilinx

MAX+PLUS II 自身产生 从其他 EDA 工具输入

1.1MAX+plus II 10.2的功能

设计输入总结图

设计文件 支持文件

MAX+PLUS II 符号编辑器

MAX+PLUS II 波形编辑器

.gdf

.wdf

.sym

MAX+PLUS II 图形编辑器

1. 2MAX+plus II 10.2的系统要求

支持的操作系统 Windows 98/Me/2000 以及 Windows xp;

安装所需空间 1Gbytes;

内存要求

可用64MB,推荐内存64MB以上。

返回目录

2013-8-9 武汉工程大学邮科院校区实验中心 11

第二章 Max+PlusII的安装向导

2013-8-9

武汉工程大学邮科院校区实验中心

29

3.2 Max+PlusII的设计流程图

设计说明书

设计输入

修改设计 编译设计文件 综合、适配与优化 定时验证,时序仿真 器件编程/配置 应用系统硬件测试

MaxPlusII使用指南

将当前设计文件设定为工程文件

注意,此路径的指示文件 始终指向当前的工程文件!

开始编译/综合工程文件---半加器

消掉此设置

为顶层设计文件--全加器的设计 另建一原理图编辑窗

设计全加器原理图

存盘!

双击此元件

打开原理 图编辑窗

将当前文件设置

成工程文件!

编译/综合前选定适配元件

消去QUARTUS设 置

使用MAX+PLUS II编译器对Altera器件设计进行编译, 并使用Altera校验工具进行器件或板级仿真。

支持与Synopsys、Viewlogic、Mentor Graphics、Cadence、Exemplar、 Data I/O、Intergraph、Minc、OrCAD等公司提供的工具接口;

选择适配器件

再选择适当的器件, 以下假设所选的器 件是EPF10K10LC84

选择器件系列

编译!

仿真测试全加器的逻辑功能

建立波形 仿真文件

选择波形编辑 器

输入测试信号

输入测试信号

全加器端口信 号

按此键

设置输入信号电平,启动仿真器

启动仿真器

时序仿真

逻辑测 试正确

建立一个新工程

每个设计都都是一个工程,都必须有一个工程名 工程名必须与设计文件名一致(相符)

原理图设计输入 文本设计输入

• 使用 VHDL、AHDL等硬件描述语言

第三方 EDA 工具

EDIF文件

• 利用开发工具FPGA-Express,或SYNPLIFY等生成

OrCAD编辑的原理图,Xilinx公司XNF格式的文件

设计输入文件

VHDL/Verilog AHDL

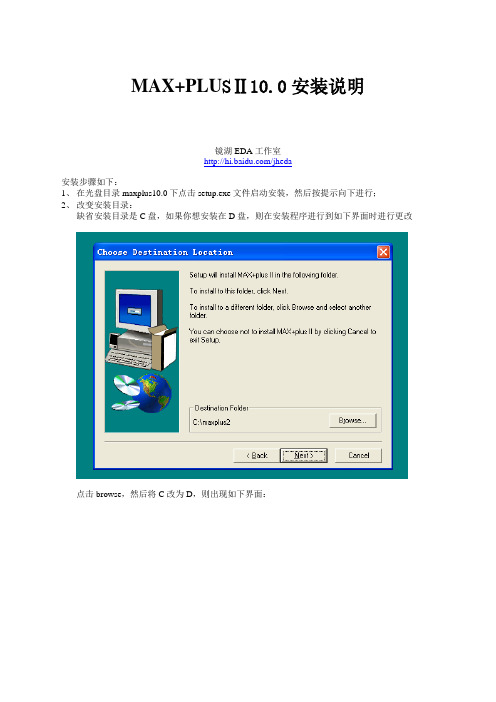

MAX+PLUSⅡ10.0安装说明

MAX+PLU SⅡ10.0安装说明

镜湖EDA工作室

/jheda

安装步骤如下:

1、在光盘目录maxplus10.0下点击setup.exe文件启动安装,然后按提示向下进行;

2、改变安装目录:

缺省安装目录是C盘,如果你想安装在D盘,则在安装程序进行到如下界面时进行更改

点击browse,然后将C改为D,则出现如下界面:

点击OK后,一直按提示进行,不要更改任何安装配置,则软件成功安装到D盘。

3、设置license文件

如果不设置license文件,则软件无法使用。

安装成功后,

1)首先将光盘目录maxplus10.0下的子目录\flexlm拷贝到你的计算机C盘;

2)打开软件:

点击【开始】-【程序】-【Altera】-【max+plusII10.0】打开软件,出现如下界面:

选【是】,则软件被打开。

3)指定license文件的路径和文件名;

点击菜单option/license setup,如下图,然后点击browse,指定license文件的路径和文件名:license文件即是C:\flexlm目录下的license.dat文件,选中后,点击OK,则license 设置成

功。

maxplusii使用说明

工程设计的构成 顶层设计

编译器可以直接读取某些顶层设计 EDIF网表文件 VHDL网表文件 Xilinx网表文件

使用图形编辑器将OrCAD编辑的原理图保存为.gdf文件 子设计 (下层模块)

EDIF格式、 VHDL文件、 OrCAD原理图和Xilinx文件 创建符号或者嵌入文件 在图形编辑器里嵌入符号或者在文本编辑器里嵌入文件

16

将当前设计文件设定为工程文件

注意,此路径的指示文件 始终指向当前的工程文件!

17

开始编译/综合工程文件---半加器

消掉此设置

18

19

为顶层设计文件--全加器的设计 另建一原理图编辑窗

20

设计全加器原理图

存盘!

双击此元件

打开原理 图编辑窗

将当前文件设置

成工程文件!

21

编译/综合前选定适配元件

1

什么是MAX+PLUS II?

一个全面集成的 CPLD 开发系统 提供与器件结构无关的开发环境 支持 所有的 Altera产品(所有器件使用一个库) 广泛满足设计需求 设计输入 综合 布局和布线 (装入) 仿真 定时分析 器件编程 提供广泛的联机帮助 支持多种平台 ( PC机和工作站 ) 支持多种 EDA软件和标准

第三方 EDA 工具 EDIF文件 利用开发工具FPGA-Express,或SYNPLIFY等生 成 OrCAD编辑的原理图,Xilinx公司XNF格式的文件

6

建立一个新工程 每个设计都都是一个工程,都必须有一个工程名 工程名必须与设计文件名一致(相符)

工程名

工程路径7Fra bibliotek89

首先建立新目录!

为设计工程建立一个新的 目录--- WORK 库

EDA工具Max_Plus

9、编译设计文件 选择 Max+Plus II | Complier, 或 File | Project | Save & Compile 或 单击水平工具条左起第12个按键 打开编译器,如图8。 单击 Start 按键后,计算机开始处理数 据。如果编译通过,会出现“ 0 errors” 和“0 warnings” 字样。 按 “确定”退出。

Байду номын сангаас

2、MAX PLUS II 安装: 安装基本过程同其它Windows应用软件安装,既 启动 Setup。 光盘上MaxPlusII V10.1安装时, 运行MaxPlusII V10.1\pc\full\ setup.exe License (软件使用授权码)设置: 在安装完基本MAX PLUS II 后,将随安装软件一 起的License.dat文件拷贝到硬盘某一目录下,启动 MAX PLUS II,选择Options|License Setup 项 在 License File or Server Name 栏输入License 的正 确路径和文件名,或通过 Browse找到License.dat,单 击 OK 按键确定。 光盘中,MaxPlusII V10.1的License.dat位于目录: MaxPlusII V10.1\补丁\ License.dat

7、保存设计的文件 选择 File | Save As 项,或者单击工 具条中保存文件按键(水平工具条左数 第三个按键),屏幕如图6。 在图6中,检查 File Name 栏应为与 工程名相同,但扩展名为 .gdf。 单击 OK 键完成设计文件的保存。

8、选择使用的CPLD芯片 选择Assign|Device项,屏幕如图7。 我们使用的CPLD是 Altera 生产的 FLEX10K 系列的 EPF10K20TI144-4,故 在Device对话框中,选: Device Family: FELX10K Devices: EPF10K20TC144-3 单击 OK 键完成芯片选择。

MAX+PLUS_II学习课件(中文)解读

2018/10/6

湖北众友科技EDA工作室

23

2.6MaxPlusII的启动

双击MAX+PLUS II10.2的图标,或从‚开始‛菜单‚程序‛中的 ‚ALTERA‛组中的‚MAX+PLUS II10.2‛运行MAX+PLUS II10.2。

2018/10/6

湖北众友科技EDA工作室

24

2.7MaxPlusII注册

MAX+PLUS II学习课件(中文版)

Max+Plus II用户 使用入门指南

EDA工作室

E-mail:Zhongyou@

2018/10/6 湖北众友科技EDA工作室 1

MAX+PLUS II学习课件目录

第一章 Max+PlusII的功能及系统要求 第二章 Max+PlusII的安装向导 第三章 Max+PlusII的设计流程 第四章 图形输入方法的设计过程 第五章 工具条和常用菜单选项说明 第六章 图形的层次化设计及BUS使用 第七章 硬件语言描述输入法 第八章 混合设计输入法 第九章 基于LPM的设计功能 第十章 应用中常见错误及处理方法

支持的器件

设计输入

常用的设计输入方法有: 通过图形编辑器,创建图形设计文件(.gdf); 通过文本编辑器,使用AHDL语言,创建文本编辑文件(.tdf); 使用VHDL语言,创建文本设计文件( .vhd);使用Verilog HDL语言,创建文本设计文件(.v)。 通过波形编辑器,创建波形设计文件(.wdf)等。

波形输入

顶层设计文件可以是 下列格式: .gdf, .tdf, .vhd, .sch, 和.edf

Synopsys, ViewLogic, Mentor Graphics,