北邮《微机原理与接口技术》期末复习题(含答案)

微机原理与接口技术考试复习题(有答案)

微机原理与接口技术考试复习题(有答案)《微型计算机原理及接口技术》试题(120分钟)一. 单项选择题(在每小题的四个备选答案中选出一个正确的1. 8086CPU芯片的外部引线中,数据线的条数为()。

A.6条B.8条C.16条D.20条2.8086CPU工作在总线请求方式时,会让出()。

A.地址总线B.数据总线C.地址和数据总线D.地址、数据和控制总线3.8086在执行OUT DX,AL指令时,AL寄存器的内容输出到()上。

A.地址总线 B.数据总线 C.存储器 D.寄存器4.8086CPU的I/O地址空间为()字节。

A.64KB B.1MB C.256B D.1024B5. 当8086CPU读I/O接口时,信号M/IO和DT/R的状态必须是()。

A.00B.01C.10D.116. 在8088CPU中, 用于寄存器间接寻址输入输出指令的寄存器是()。

A. AXB. BXC. CXD. DX7.两片8259A级联后可管理()级中断。

A.15 B.16 C.32 D.648.8086中断系统中优先级最低的的是()。

A.可屏蔽中断B.不可屏蔽中断C.单步中断D.除法出错9.CPU在执行IN AL,DX指令时,其()。

A. IO/M为高, RD为低 B. IO/M为高, WR为低C. IO/M为低, RD为低 D. IO/M为低, WR为低10. 内存从A4000H到CBFFFH,共有()A.124KB.160KC.180KD.224K11. 8088CPU中的CS寄存器是一个多少位的寄存器?()。

A.8位B.16位C.24位D.32位12.地址译码器的输出一般可为接口的()信号。

A.片选 B.数据输入 C.地址 D.控制13. 8255工作在方式0时,下面哪种说法正确()A. A、B、C三个口输入均有锁存能力B. 只有A口输入有锁存能力C. 只有C口输入有锁存能力D. A、B、C三个口输入均无锁存能力14. 实现DMA传送,需要()A.CPU通过执行指令来完成B.CPU利用中断方式来完成C.CPU利用查询方式来完成D.不需要CPU参与即可完成15.CPU在执行OUT DX,AL指令时,()寄存器的内容送到地址总线上。

微机原理与接口技术的期末试题与答案

微机原理与接口技术的期末试题与答案一、单项选择题1.下列指令正确的是[ B]A.CMP [SI],100B.CMP WORD PTR [SI],100C.CMP [SI],100hD.CMP 100h,[SI]2.下列指令正确的是[D ]A.MOV CX,ALB.MOV DS,200hC.MOV DS,CSD.MOV DS,AX3.下列指令正确的是[A ]A.POP WORD PTR [BX]B.POP BLC.POP IPD.POP CS4.下列指令正确的是[C ]A.IN DX,ALB.IN DX,AXC.IN AX,DXD.IN BX,DX5.DF=1,执行MOVSB指令后[A ]A.SI减1,DI减1B.SI加1,DI加1,CX减1C.SI减1,DI减1,CX减1D.SI加1,DI加1,CX加16.Intel 8086 I/O寻址空间为[C ]A.1MBB.1KBC.64KBD.32KB二、填空题1.二进制数10101001转换为10进制数为169 D转换为16进制数为A9 H1.在移位指令中,用于指定移位位数的操作数只用的寄存器是___CL_____。

2.内存0005CH处4个字节为D2,EF,00,F0,它是中断__17H______的入口地址存放处,它表示该中断处理程序的起始地址为_F000H___ :__EFD2H___。

解析:因为中断类型号和中断向量表中的对应物理地址由倍数4的关系,所以0005CH/4=17h,即得类型号。

3.一条指令为MOV BX,X1,其中X1的偏移地址为16 (十进制)。

在DEBUG 下,此指令会变为MOV BX,__[0010]______。

4.指令MOV AL, BYTE PTR [BX+SI]中,源操作数的寻址方式是基址变址寻址方式5.设CF=0,AX=8000H,执行ROR AX,1后,AX=_4000H___,CF=_____0_________。

微机原理与接口技术期末试题ABC三卷及答案

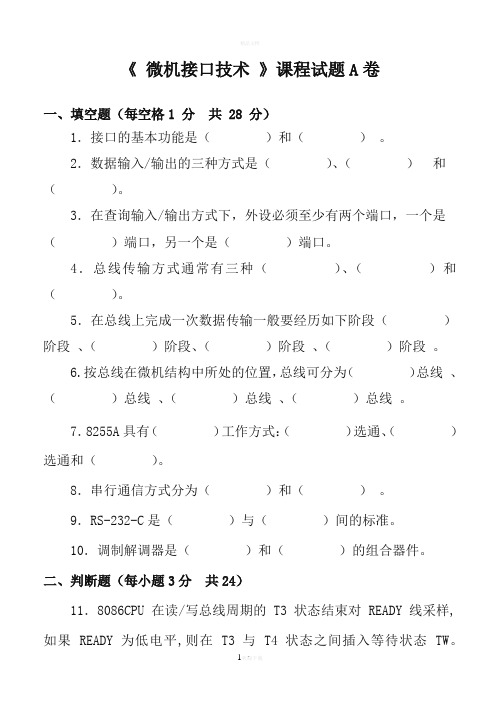

《微机接口技术》课程试题A卷一、填空题(每空格1 分共 28 分)1.接口的基本功能是()和()。

2.数据输入/输出的三种方式是()、()和()。

3.在查询输入/输出方式下,外设必须至少有两个端口,一个是()端口,另一个是()端口。

4.总线传输方式通常有三种()、()和()。

5.在总线上完成一次数据传输一般要经历如下阶段()阶段、()阶段、()阶段、()阶段。

6.按总线在微机结构中所处的位置,总线可分为()总线、()总线、()总线、()总线。

7.8255A具有()工作方式:()选通、()选通和()。

8.串行通信方式分为()和()。

9.RS-232-C是()与()间的标准。

10.调制解调器是()和()的组合器件。

二、判断题(每小题3分共24)11.8086CPU 在读/写总线周期的 T3 状态结束对 READY 线采样,如果 READY 为低电平,则在 T3 与 T4 状态之间插入等待状态 TW。

()12.在 8253 的方式控制字中,有一项计数锁存操作,其作用是暂停计数器的计数。

()13.8250 的溢出错误指示 CPU 还未取走前一个数据,接收移位寄存器又将接收到的一个新数据送至输入缓冲器。

()14.在 8088 系统(最小组态)中,执行指令”MOV [2000H],AX”需 1 个总线周期。

()15.DMA 控制器 8237A 现行字节数寄存器的值减到 0 时,终止计数。

()16.8086/8088CPU 的复位后开始执行的第一条指令的地址为FFFFH。

()17.若各中断源的优先级是一样的,则可用自动循环优先级来实现。

()18.最小模式下 8086/8088 读总线操作时序和写总线操作时序中的 DT / R 信号波形基本相同。

()三、单项选择题:(每小题 3分,共 30 分)19.8086CPU工作在总线请求方式时,会让出()。

A.地址总线 B.数据总线C.地址和数据总线 D.地址、数据和控制总线20.8086CPU的I/O地址空间为()字节。

微机原理与接口技术考试试题与答案

《微机原理与接口技术》课程期末考试试卷(A卷,考试)一、单项选择(在备选答案中选出一个正确答案,并将其填在题干后的括号。

每题 2 分,共30分)1 .某微机最大可寻址的存空间为16MB其CPU地址总线至少应有( )条。

A. 32B. 16C. 20D. 242 .用8088CPU组成的PC机数据线是( )。

A. 8 条单向线B. 16 条单向线C. 8 条双向线D. 16 条双向线3 . 微处理器系统采用存储器映像方式编址时存储单元与I/O 端口是通过( )来区分的。

A. 不同的地址编码B. 不同的读控制逻辑C. 不同的写控制逻辑D. 专用I/O 指令4 .要禁止8259A的IR0的中断请求,则其中断屏蔽操作指令字OCW应为( )。

A. 80HB. 28HC. E8HD. 01H5 . 在8086 环境下,对单片方式使用的8259A 进行初始化时,必须放置的初始化命令字为( )。

A. ICW1,ICW2,ICW3B. ICW1,ICW2,ICW4C.ICW1,ICW3,ICW4 D. ICW2,ICW3,ICW46.6166为2Kx8位的SRAM芯片,它的地址线条数为 ( )。

A. 11B. 12C. 13D. 147 . 在计算机系统中,可用于传送中断请求和中断相应信号的是( )。

A. 地址总线B. 数据总线C. 控制总线D. 都不对8 .段寄存器装入2300H,该段的最大结束地址是(A. 32FFFHB. 23000HC. 33FFFHD. 33000H9 .在进入DMA工作方式之前,DM/控制器当作CPU总线上的一个()。

A I/O设备B. I/O接口C.主处理器D.逻辑高10 .在8086宏汇编过程中不产生指令码,只用来指示汇编程序如何汇编的指令是()OA.汇编指令B .宏指令C.机器指令D .伪指令11.中断向量表占用存地址空间为()。

A. 00000H〜003FFHB. 00000H〜000FFHC. 00000H〜00100HD. FFF00H H FFFFFH12 .实现CPU与8259A之间信息交换是()。

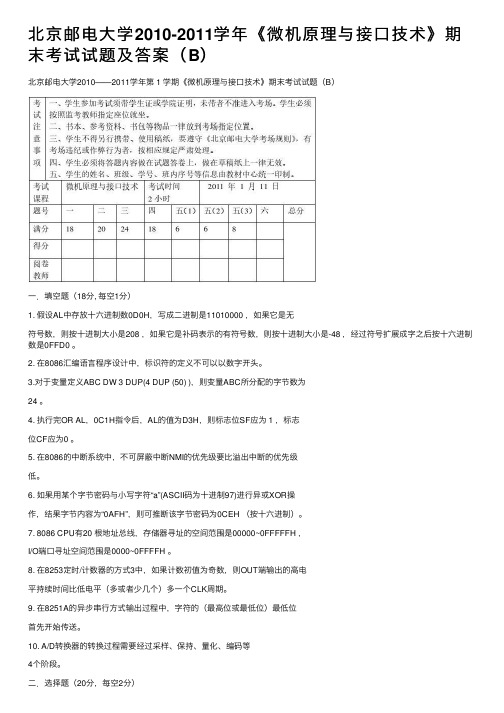

北京邮电大学2010-2011学年《微机原理与接口技术》期末考试试题及答案(B)

北京邮电⼤学2010-2011学年《微机原理与接⼝技术》期末考试试题及答案(B)北京邮电⼤学2010——2011学年第 1 学期《微机原理与接⼝技术》期末考试试题(B)⼀.填空题(18分, 每空1分)1. 假设AL中存放⼗六进制数0D0H,写成⼆进制是11010000 ,如果它是⽆符号数,则按⼗进制⼤⼩是208 ,如果它是补码表⽰的有符号数,则按⼗进制⼤⼩是-48 ,经过符号扩展成字之后按⼗六进制数是0FFD0 。

2. 在8086汇编语⾔程序设计中,标识符的定义不可以以数字开头。

3.对于变量定义ABC DW 3 DUP(4 DUP (50) ),则变量ABC所分配的字节数为24 。

4. 执⾏完OR AL,0C1H指令后,AL的值为D3H,则标志位SF应为 1 ,标志位CF应为0 。

5. 在8086的中断系统中,不可屏蔽中断NMI的优先级要⽐溢出中断的优先级低。

6. 如果⽤某个字节密码与⼩写字符“a”(ASCII码为⼗进制97)进⾏异或XOR操作,结果字节内容为“0AFH”,则可推断该字节密码为0CEH (按⼗六进制)。

7. 8086 CPU有20 根地址总线,存储器寻址的空间范围是00000~0FFFFFH ,I/O端⼝寻址空间范围是0000~0FFFFH 。

8. 在8253定时/计数器的⽅式3中,如果计数初值为奇数,则OUT端输出的⾼电平持续时间⽐低电平(多或者少⼏个)多⼀个CLK周期。

9. 在8251A的异步串⾏⽅式输出过程中,字符的(最⾼位或最低位)最低位⾸先开始传送。

10. A/D转换器的转换过程需要经过采样、保持、量化、编码等1.构成微机的主要部件除CPU、内存、I/O接⼝外,还有____D____。

(A) 显⽰器(B) 键盘(C) 磁盘(D)系统总线2.在汇编过程中,不产⽣指令码,只⽤来指⽰汇编程序如何汇编的指令称为___B_____。

(A) 汇编指令(B)伪指令(C)机器指令(D)宏指令3.在8259A中,⽤来屏蔽中断源的寄存器是___C____。

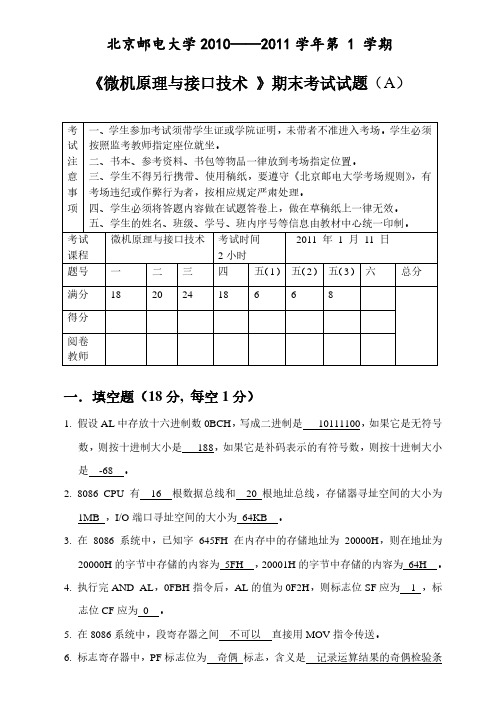

北京邮电大学2010-2011学年《微机原理与接口技术》期末考试试题及答案(A)

北京邮电大学2010——2011学年第 1 学期《微机原理与接口技术》期末考试试题(A)一.填空题(18分, 每空1分)1. 假设AL中存放十六进制数0BCH,写成二进制是10111100,如果它是无符号数,则按十进制大小是188,如果它是补码表示的有符号数,则按十进制大小是-68 。

2. 8086 CPU有16 根数据总线和20 根地址总线,存储器寻址空间的大小为1MB ,I/O端口寻址空间的大小为64KB 。

3. 在8086系统中,已知字645FH在内存中的存储地址为20000H,则在地址为20000H的字节中存储的内容为5FH ,20001H的字节中存储的内容为64H 。

4. 执行完AND AL,0FBH指令后,AL的值为0F2H,则标志位SF应为 1 ,标志位CF应为0 。

5. 在8086系统中,段寄存器之间不可以直接用MOV指令传送。

6.标志寄存器中,PF标志位为奇偶标志,含义是记录运算结果的奇偶检验条件。

7.DRAM存储器中由于电容中存储电荷会逐渐泄漏,所以必须定时对DRAM进行刷新。

8. 在8251A的异步串行方式输出过程中,数据的并-串转换是通过发送移位寄存器实现的。

9. 如果用某个字节密码与小写字符“m”(ASCII码为十进制109)进行异或XOR操作,结果字节内容为5BH,则可推断该字节密码为36H (十六进制)。

10. D/A转换器的分辨率是指其所能分辨的最小电压。

二.选择题(20分,每空2分)1.构成微机系统的主要部件除CPU、系统总线、I/O接口外,还有____D____。

(A) 显示器(B) 键盘(C) 磁盘(D)内存(ROM和RAM)2.对于以下各种中断,只有___D_____需要硬件提供中断类型码:(A) INTO (B) INT n (C) NMI (D) INTR3.8259中,用来保存正在服务的中断的寄存器是___B____。

(A) IRR (B) ISR (C) IMR (D) DAC4.已知8086 CPU中寄存器有如下内容:DS=2000H;ES=3000H;SS=4000H;CS=5000H;BP=4100H。

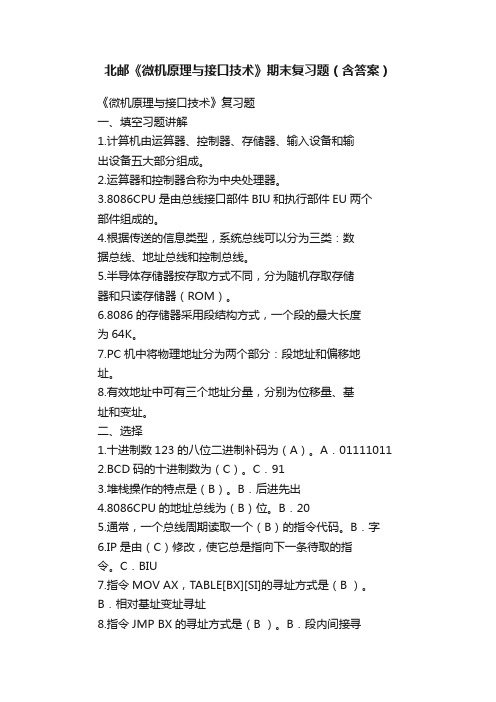

北邮《微机原理与接口技术》期末复习题(含答案)

北邮《微机原理与接口技术》期末复习题(含答案)《微机原理与接口技术》复习题一、填空习题讲解1.计算机由运算器、控制器、存储器、输入设备和输出设备五大部分组成。

2.运算器和控制器合称为中央处理器。

3.8086CPU是由总线接口部件BIU和执行部件EU两个部件组成的。

4.根据传送的信息类型,系统总线可以分为三类:数据总线、地址总线和控制总线。

5.半导体存储器按存取方式不同,分为随机存取存储器和只读存储器(ROM)。

6.8086的存储器采用段结构方式,一个段的最大长度为64K。

7.PC机中将物理地址分为两个部分:段地址和偏移地址。

8.有效地址中可有三个地址分量,分别为位移量、基址和变址。

二、选择1.十进制数123的八位二进制补码为(A)。

A.011110112.BCD码的十进制数为(C)。

C.913.堆栈操作的特点是(B)。

B.后进先出4.8086CPU的地址总线为(B)位。

B.205.通常,一个总线周期读取一个(B)的指令代码。

B.字6.IP是由(C)修改,使它总是指向下一条待取的指令。

C.BIU7.指令MOV AX,TABLE[BX][SI]的寻址方式是(B )。

B.相对基址变址寻址8.指令JMP BX的寻址方式是(B )。

B.段内间接寻址9.CPU中运算器的主要功能是(D)。

D.算术运算和逻辑运算10.8086是(B)。

B.微处理器11.8086处理器有20条地址线,可寻址访问的最大存储器空间为(D)。

D.1M12.8086处理器中通常用作数据寄存器,且隐含用法为计数寄存器的是(B)。

B.CX13.微型机的存储器地址为2000H~5FFFH,存储容量为(D)KB。

D.1614.微处理器用13条地址线寻址,其寻址范围为(C)。

C.4KB15.哪些存储器在断电(或关机)后,仍保留原有信息(C)。

C.ROM,,EPROM16.8086CPU寻址I/O端口最多使用地址线(B)条。

B.10三、请写出下列指令中源操作数的寻址方式,并计算物理地址。

(完整word版)微机原理与接口技术期末考试复习试题

微机原理与接口技术》试题(第一套) 、选择题(每题 3 分,共 30 分)8288 在 8086/8088 组成的计算机中的作用是 ( ② )。

提供系统时钟 CLK式为 ( ② )。

④ 变址寻址该存储单元的物理地址为 (④ 3AAA8H38060+2A48=3AAA8H片的存储容量为 ( ③ )。

④ 32KX 85.某存储器芯片容量为2KX 1 bit 、若用它组成 16KX 8bit存储器组, 所用芯片数以及用于组内寻址的地址线为 ( ② )。

① 32 片、 11 根 ② 64 片、14 根 ③ 8 片、 14 根 ④ 16 片、 8 根1. 数据缓冲器② 总线控制器 ③ 地址锁存器2. 指令 MOV 0283H[BX][SI] , AX中目标操作数的寻址方① 寄存器寻址② 基址变址相对寻址 ③ 基址寻址3.某存储单元的段基址为3806H ,段内偏移地址为 2A48H ,① 4100H3AA08H ③ 3B008H4.某存储器芯片有地址线13 根,数据线 8 根、该存储器芯① 15K X 832K X 256 ③ 8K X 8程序段④ 三个独立通道预置方式。

2、具有三种基本的传输方式:单字节传送、数 据块传送、 请求传送。

3、具有存储器到存储器的传送功能并行输入输出端口。

并行输入输出端口。

并行输入输出端口。

端口。

6. ADD AX ,[BX+8] ”的源操作数在当前(② )。

堆栈段② 数据段③ 代码段7. DMAC 8237 具有 ( ② ) 。

八个独立通道四个独立通道③ 二个独立通DMAC8237A 的主要性能:1、有 4 个独立的 DMA 通道,每 个通道都充许开放或禁止DMA 请求,都可以独立控制自动4、 具有正常时序和压缩时序两种基本时序。

5、 8257A 级联可扩充任意个 DMA 通道。

6、有两种优先管理方式: 固定优先级和循环优先级。

7、有较高的数据传输速率。

8.可编程并行接口 8255A 具有 ( ①)① 两个 8 位 (A 口、 口)和两个 4 位 (C 口的高、 低各 ② 两个 8 位 (A 口、 口) 和两个 4 位 (B 口的高、 低各③ 两个 8 位 (B 口、 口) 和两个 4 位 (A 口的高、 低各④ 两个 4 位 (A 口、 B口)和一个8位(C 口)并行输入输出9.8259分别有( ③ )个 ICW 和 OCW 。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《微机原理与接口技术》复习题一、填空习题讲解1.计算机由运算器、控制器、存储器、输入设备和输出设备五大部分组成。

2.运算器和控制器合称为中央处理器。

3.8086CPU是由总线接口部件BIU和执行部件EU两个部件组成的。

4.根据传送的信息类型,系统总线可以分为三类:数据总线、地址总线和控制总线。

5.半导体存储器按存取方式不同,分为随机存取存储器和只读存储器(ROM)。

6.8086的存储器采用段结构方式,一个段的最大长度为64K。

7.PC机中将物理地址分为两个部分:段地址和偏移地址。

8.有效地址中可有三个地址分量,分别为位移量、基址和变址。

二、选择1.十进制数123的八位二进制补码为(A)。

A.011110112.BCD码的十进制数为(C)。

C.913.堆栈操作的特点是(B)。

B.后进先出4.8086CPU的地址总线为(B)位。

B.205.通常,一个总线周期读取一个(B)的指令代码。

B.字6.IP是由(C)修改,使它总是指向下一条待取的指令。

C.BIU7.指令MOV AX,TABLE[BX][SI]的寻址方式是(B )。

B.相对基址变址寻址8.指令JMP BX的寻址方式是(B )。

B.段内间接寻址9.CPU中运算器的主要功能是(D)。

D.算术运算和逻辑运算10.8086是(B)。

B.微处理器11.8086处理器有20条地址线,可寻址访问的最大存储器空间为(D)。

D.1M12.8086处理器中通常用作数据寄存器,且隐含用法为计数寄存器的是(B)。

B.CX13.微型机的存储器地址为2000H~5FFFH,存储容量为(D)KB。

D.1614.微处理器用13条地址线寻址,其寻址范围为(C)。

C.4KB15.哪些存储器在断电(或关机)后,仍保留原有信息(C)。

C.ROM,,EPROM16.8086CPU寻址I/O端口最多使用地址线(B)条。

B.10三、请写出下列指令中源操作数的寻址方式,并计算物理地址。

已知:(DS)=2000H,(ES)=2100H,(SI)=00A0H,(SS)=1500H,(BX)=0100H,(BP)=0100H,数据变量VAL的偏移地址为0050H。

ADD AX,[100H]直接寻址 PA=20100HADD AX,[BX]间接寻址 PA=20100HADD AX,ES:[BX]间接寻址 PA=21100HADD AX,[BP]间接寻址 PA=15100HADD AX,[BX+10H]直接变址寻址 PA=20110HADD AX,VAL[BX]直接变址寻址 PA=20150HADD AX,[BX][SI]基址变址寻址 PA=201A0HADD AX,VAL[BX][SI]相对基址变址寻址 PA=201F0HADD AX,[SI]ADD AX,VAL[BP]习题讲解四、微型计算机系统结构五、分支结构的两种程序流程图六、循环次数的循环程序结构图七、已知:在DATA单元开始连续存放着10个带符号的字节数据,要求计算其中0的个数,结果放入R单元。

要求编写完整的8086汇编语言源程序(含全部的伪指令)TITLE FGREATERDATA S EGMENTDATA D B 3,28,-4,22,0,-65,24,7,-3,-36R DBDATA E NDSSTACK SEGMENT PARA STACK‘STACK’DW 100 DUP()STACK ENDSCOSEG SEGMENTASSUME CS:COSEG,DS:DATA,SS:STACKSTART PROC FARBEGIN: PUSH DS MOV AX,0PUSH AXMOV AX,DATAMOV DS,AXMOV AX,0习题讲解-8255A八、接口设计1、设8255A工作在方式0,A口为输入口,B口、C口为输出口。

设片选信号CS由A9~A2=确定。

请编程对8255A进行初始化。

2、设8255A工作在方式1,A口输出,B口输入,PC4~PC5为输入,禁止B口中断。

设片选信号CS由A9~A2=确定。

请编程对8255A进行初始化。

一个8255A芯片的A口和B口分别与8个LED灯和8个开关连接,通过开关控制LED灯的开和闭。

8255的端口地址为40, 42, 44和46H。

试编写初始化程序。

初始化程序如下:MOV AL, BOUT 46H, AL3、1)设置波特率的控制字格式(DLAB=1):1 0 0 0 0 0 0 0 B设波特率为1200波特,则除数=1843200÷(1200×16) =96 =0060H初始化程序:MOV AL,BMOV DX,3FBHOUT DX,ALMOV AL,60HMOV DX,3F8HOUT DX,ALMOV AL,00HMOV DX,3F9HOUT DX,AL2)设:数据位7位,停止位1位,采用偶校验;数据格式控制字为: 0 0 0 1 1 0 1 0程序:MOV AL,00011010BMOV DX,3FBHOUT DX,AL3)查询通信WAIT:MOV DX,3FDH ;读通信线路状态寄存器 IN AL,DXTEST AL,1EH ;测试D1~D4位有无出错JNZ ERROR ;有错,转错误处理TEST AL,01H ;测试D0位有无数据发送JNZ RECE ;有数据,转接收数据处理TEST AL,20H ;测试D5位发送器保持寄存器空否JZ WAIT ;不空,循环等待┆TRNAS:MOV DX 3F8H ;发送数据OUT DX,AL┆RECE:MOV DX,3F8H ;接收数据IN AL,DX┆工作方式字4、选择2号计数器,工作在方式2,计数初值为533H (2个字节),采用二进制计数,其程序段为:TIMER EQU 40H ;0号计数器端口地址MOV AL,B ;2号计数器的方式控制字 OUT TOMER+3,AL ;写入控制寄存器MOV AX,533H ;计数初值OUT TIMER+2,AL ;先送低字节到2号计数器MOV AL,AH ;取高字节OUT TIMER+2,AL ;后送高字节到2号计数器5、8254的计数器2工作于方式2,其计数时钟CLK2,为100KHz,输出信号OUT2作定时中断申请,定时间隔为8ms,试计算其计数初值N .N=8ms×100KHz=8006、有个1s的脉冲信号源送82534的计数器1利用软件方式扩大定时1秒,每秒钟从8255A的PA口读入一组开关数并送PB口的LED管显示,设8254,8255A的端口地址分别为40H~43H和60H~63H,且只用10条地址线(A0~A9)用于端口译码。

请编写对8254计数器1的初始化程序段(仅50ms.)编写对8255A的初始化程序段。

① 8253的初始化程序:MOV AL, 01110110B ; 计数器1方式3,二进制OUT 43H, ALMOV AX, 50000OUT 41H, ALMOV AL, AHOUT 41H, AL② 8255初始化MOV AL, B ;A口方式0输入,B口方式0输出OUT 63H, AL复习测试60题的数据线有(B)位。

2.运算器的核心部分是(B ) B.算术逻辑单元指令队列的长度为(B )字节。

4.存储器12345H单元中存放有数据5FH,用记号(A)表示。

A.(12345H)=5FH机存储管理中,偏移地址的最大寻址范围是(C )。

6.二进制数转换为压缩BCD码为(C)。

7.在机器数的(A)中,零的表示形式是唯一的。

A.补码8.在段定义时,如果定位类型用户未选择,就表示是隐含类型,其隐含类型是( D)。

9.定点8位字长的字,采用2的补码形式时,一个字所能表示的整数范围为(A)。

A.-128~+12710.构成微机的主要的部件有CPU、系统总线、I/O接口和(D)。

D.内存在进行无符号数比较时,应根据(C)标志位来判断比较结果。

,ZF12.汇编语言源程序中,每个语句由四项组成,其中不可省略的项是(B)。

B.操作码项13.在分支程序进行条件判断前,可用指令构成条件,其中不能形成条件的指令是(D)。

14.在汇编过程中不产生指令码,只用来指示汇编程序如何汇编的指令是(C)。

C.伪指令15.下列寄存器组中在段内寻址时可以提供偏移地址的寄存器组是(B)。

,BP,SI,DI16.堆栈操作的特点是(B)。

B.后进先出17.指令MOV AX,[1000H]中源操作数的寻址方式是(B)。

B.直接寻址的地址总线为(B)位。

19.通常,一个总线周期读取一个(B)的指令代码。

B.字是由(C)修改,使它总是指向下一条待取的指令。

对中断请求相应优先级最高的请求(C)。

C.内部硬件中断22.已知[x]原=和[Y]原=,则[X-Y]补=(D)。

23.汇编语句 DATA SEGMENT STACKDW 100 DUP(0)DATA ENDS的含义是(C)。

C.定义200个字节的堆栈段24.若程序将某16位带符号数直接加到8086CPU的IP 上,会(A)。

A.是程序发生转移,其范围为32K25.溢出是两带符号数(B),结果超出规定的数值范围。

B.两同号数相加XT机对I/O端口的最大寻址范围为(B)。

27.已知AL=6AH,BL=78H,执行指令ADD AL,BL后,CF、OF和AF的值为(D)。

,1,128.已知X=-0110110B,Y=-0111010B,将两数以补码形式送入AL和BL,执行指令SUB AL,BL后,CF、ZF、SF和OF分别为(D)。

,0,0,029.若8259采用全嵌套方式工作,现有IR4正在被服务,又有IR2,IR3,IR4,IR6中断源发生,若允许嵌套,则CPU转去服务(C)。

30.如果一个堆栈从20000H开始,它的长度为0200H,则执行指令PUSH AXPUSH CXPUSH DXPOP AX 后,栈顶、栈底的地址为(B)。

,20000H的16位通用寄存器有(B)。

个32.下列转移指令中,转移地址采用段间直接寻址的是(B)。

FAR PTR ADD133.一台微机具有4KB的连续存储器。

其存储空间首址为4000H,则末址为(A)。

.由于8086有单独的I/O指令,所以其I/O端口(A)。

A.只能安排在I/O空间内35.在查询I/O控制方式时,外设准备好的状态信息是通过(A)供给CPU进行查询的,当CPU已查询到外设准备好时,CPU就通过()与外设交换信息。

A.数据总线36.响应NMI请求的必要条件是(B)。

B.一条指令结束37.8086的中断是向量中断,其中断服务程序的入口地址是由(D)提供。

D.由中断类型号指向的中断向量表中读出38.在DMA传送方式中,以(B)方式的传输效率为最高。