On the Connection Between 2d Topological Gravity and the Reduced Hermitian Matrix Model

数学专业英语词汇(T)_数学物理英语词汇

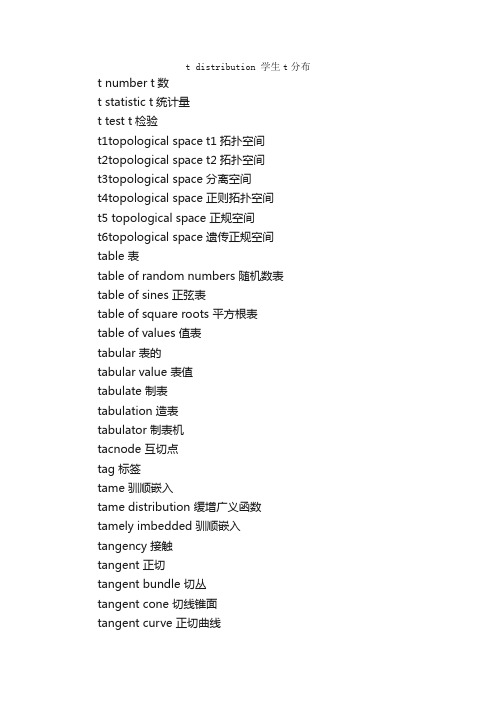

t distribution 学生t分布t number t数t statistic t统计量t test t检验t1topological space t1拓扑空间t2topological space t2拓扑空间t3topological space 分离空间t4topological space 正则拓扑空间t5 topological space 正规空间t6topological space 遗传正规空间table 表table of random numbers 随机数表table of sines 正弦表table of square roots 平方根表table of values 值表tabular 表的tabular value 表值tabulate 制表tabulation 造表tabulator 制表机tacnode 互切点tag 标签tame 驯顺嵌入tame distribution 缓增广义函数tamely imbedded 驯顺嵌入tangency 接触tangent 正切tangent bundle 切丛tangent cone 切线锥面tangent curve 正切曲线tangent function 正切tangent line 切线tangent of an angle 角的正切tangent plane 切平面tangent plane method 切面法tangent surface 切曲面tangent vector 切向量tangent vector field 切向量场tangent vector space 切向量空间tangential approximation 切线逼近tangential component 切线分量tangential curve 正切曲线tangential equation 切线方程tangential stress 切向应力tangents method 切线法tape 纸带tape inscription 纸带记录tariff 税tautology 重言taylor circle 泰勒圆taylor expansion 泰勒展开taylor formula 泰勒公式taylor series 泰勒级数technics 技术technique 技术telegraph equation 电报方程teleparallelism 绝对平行性temperature 温度tempered distribution 缓增广义函数tend 倾向tendency 瞧tension 张力tensor 张量tensor algebra 张量代数tensor analysis 张量分析tensor bundle 张量丛tensor calculus 张量演算法tensor density 张量密度tensor differential equation 张量微分方程tensor field 张量场tensor form 张量形式tensor form of the first kind 第一张量形式tensor function 张量函数tensor of torsion 挠率张量tensor product 张量乘积tensor product functor 张量乘积函子tensor representation 张量表示tensor space 张量空间tensor subspace 张量子空间tensor surface 张量曲面tensorial multiplication 张量乘法term 项term of higher degree 高次项term of higher order 高次项term of series 级数的项terminability 有限性terminable 有限的terminal decision 最后判决terminal edge 终结边terminal point 终点terminal unit 级端设备terminal vertex 悬挂点terminate 终止terminating chain 可终止的链terminating continued fraction 有尽连分数terminating decimal 有尽小数termination 终止terminology 专门名词termwise 逐项的termwise addition 逐项加法termwise differentiation 逐项微分termwise integration 逐项积分ternary 三元的ternary connective 三元联结ternary form 三元形式ternary notation 三进制记数法ternary number system 三进制数系ternary operation 三项运算ternary relation 三项关系ternary representation og numbers 三进制记数法tertiary obstruction 第三障碍tesseral harmonic 田形函数tesseral legendre function 田形函数test 检验test for additivity 加性检验test for uniform convergence 一致收敛检验test function 测试函数test of dispersion 色散检验test of goodness of fit 拟合优度检验test of hypothesis 假设检验test of independence 独立性检验test of linearity 线性检验test of normality 正规性检验test point 测试点test routine 检验程序test statistic 检验统计量tetracyclic coordinates 四圆坐标tetrad 四元组tetragon 四角形tetragonal 正方的tetrahedral 四面角tetrahedral angle 四面角tetrahedral co ordinates 四面坐标tetrahedral group 四面体群tetrahedral surface 四面曲面tetrahedroid 四面体tetrahedron 四面形tetrahedron equation 四面体方程theorem 定理theorem for damping 阻尼定理theorem of alternative 择一定理theorem of identity for power series 幂级数的一致定理theorem of implicit functions 隐函数定理theorem of mean value 平均值定理theorem of principal axes 轴定理theorem of residues 残数定理theorem of riemann roch type 黎曼洛赫型定理theorem on embedding 嵌入定理theorems for limits 极限定理theoretical curve 理论曲线theoretical model 理论模型theory of automata 自动机理论theory of cardinals 基数论theory of complex multiplication 复数乘法论theory of complexity of computations 计算的复杂性理论theory of correlation 相关论theory of differential equations 微分方程论theory of dimensions 维数论theory of elementary divisors 初等因子理论theory of elementary particles 基本粒子论theory of equations 方程论theory of errors 误差论theory of estimation 估计论theory of functions 函数论theory of games 对策论theory of hyperbolic functions 双曲函数论theory of judgment 判断论theory of numbers 数论theory of ordinals 序数论theory of perturbations 摄动理论theory of probability 概率论theory of proportions 比例论theory of relativity 相对论theory of reliability 可靠性理论theory of representations 表示论theory of sets 集论theory of sheaves 层理论theory of singularities 奇点理论theory of testing 检验论theory of time series 时间序列论theory of transversals 横断线论theory of types 类型论thermal 热的thermodynamic 热力学的thermodynamics 热力学theta function 函数theta series 级数thick 厚的thickness 厚度thin 薄的thin set 薄集third boundary condition 第三边界条件third boundary value problem 第三边界值问题third fundamental form 第三基本形式third isomorphism theorem 第三同构定理third proportional 比例第三项third root 立方根thom class 汤姆类thom complex 汤姆复形three body problem 三体问题three dimensional 三维的three dimensional space 三维空间three dimensional torus 三维环面three eighths rule 八分之三法three faced 三面的three figur 三位的three place 三位的three point problem 三点问题three series theorem 三级数定理three sheeted 三叶的three sided 三面的three sigma rule 三规则three termed 三项的three valued 三值的three valued logic 三值逻辑three valued logic calculus 三值逻辑学threshold logic 阈逻辑time interval 时程time lag 时滞time series analysis 时序分析timesharing 分时toeplitz matrix 托普利兹矩阵tolerance 容许tolerance distribution 容许分布tolerance estimation 容许估计tolerance factor 容许因子tolerance level 耐受水平tolerance limit 容许界限tolerance region 容许区域top digit 最高位数字topological 拓扑的topological abelian group 拓扑阿贝耳群topological algebra 拓扑代数topological cell 拓扑胞腔topological circle 拓扑圆topological completeness 拓扑完备性topological complex 拓扑复形topological convergence 拓扑收敛topological dimension 拓扑维topological direct sum 拓扑直和topological dynamics 拓扑动力学topological embedding 拓扑嵌入topological field 拓扑域topological group 拓扑群topological homeomorphism 拓扑同胚topological index 拓扑指数topological invariant 拓扑不变量topological limit 拓扑极限topological linear space 拓扑线性空间topological manifold 拓扑廖topological mapping 拓扑同胚topological pair 拓扑偶topological polyhedron 曲多面体topological product 拓扑积topological residue class ring 拓扑剩余类环topological ring 拓扑环topological simplex 拓扑单形topological skew field 拓扑非交换域topological space 拓扑空间topological sphere 拓扑球面topological structure 拓扑结构topological sum 拓扑和topological type 拓扑型topologically complete set 拓扑完备集topologically complete space 拓扑完备空间topologically equivalent space 拓扑等价空间topologically nilpotent element 拓扑幂零元topologically ringed space 拓扑环式空间topologically solvable group 拓扑可解群topologico differential invariant 拓扑微分不变式topologize 拓扑化topology 拓扑topology of bounded convergence 有界收敛拓扑topology of compact convergence 紧收敛拓扑topology of uniform convergence 一致收敛拓扑toroid 超环面toroidal coordinates 圆环坐标toroidal function 圆环函数torque 转矩torsion 挠率torsion coefficient 挠系数torsion form 挠率形式torsion free group 非挠群torsion group 挠群torsion module 挠模torsion of a curve 曲线的挠率torsion product 挠积torsion subgroup 挠子群torsion tensor 挠率张量torsion vector 挠向量torsionfree connection 非挠联络torsionfree module 无挠模torsionfree ring 无挠环torus 环面torus function 圆环函数torus group 环面群torusknot 环面纽结total 总和total correlation 全相关total curvature 全曲率total degree 全次数total differential 全微分total differential equation 全微分方程total error 全误差total graph 全图total image 全象total inspection 全检查total instability 全不稳定性total inverse image 全逆象total matrix algebra 全阵环total matrix ring 全阵环total order 全序total predicate 全谓词total probability 总概率total probability formula 总概率公式total regression 总回归total relation 通用关系total space 全空间total stability 全稳定性total step iteration 整步迭代法total step method 整步迭代法total stiefel whitney class 全斯蒂费尔惠特尼类total subset 全子集total sum 总和total variation 全变差totally bounded set 准紧集totally bounded space 准紧空间totally differentiable 完全可微分的totally differentiable function 完全可微函数totally disconnected 完全不连通的totally disconnected graph 完全不连通图totally disconnected groupoid 完全不连通广群totally disconnected set 完全不连通集totally disconnected space 完全不连通空间totally geodesic 全测地的totally nonnegative matrix 全非负矩阵totally ordered group 全有序群totally ordered set 线性有序集totally positive 全正的totally positive matrix 全正矩阵totally quasi ordered set 完全拟有序集totally real field 全实域totally reflexive relation 完全自反关系totally regular matrix method 完全正则矩阵法totally singular subspace 全奇异子空间totally symmetric loop 完全对称圈totally symmetric quasigroup 完全对称拟群touch 相切tournament 竞赛图trace 迹trace form 迹型trace function 迹函数trace of dyadic 并向量的迹trace of matrix 矩阵的迹trace of tensor 张量的迹tracing point 追迹点track 轨迹tractrix 曳物线trajectory 轨道transcendence 超越性transcendence basis 超越基transcendence degree 超越次数transcendency 超越性transcendental element 超越元素transcendental equation 超越方程transcendental function 超越函数transcendental integral function 超越整函数transcendental number 超越数transcendental singularity 超越奇点transcendental surface 超越曲面transfer 转移transfer function 转移函数transfinite 超限的transfinite diameter 超限直径transfinite induction 超限归纳法transfinite number 超限序数transfinite ordinal 超限序数transform 变换transformation 变换transformation equation 变换方程transformation factor 变换因子transformation formulas of the coordinates 坐标的变换公式transformation function 变换函数transformation group 变换群transformation of air mass 气团变性transformation of coordinates 坐标的变换transformation of parameter 参数变换transformation of state 状态变换transformation of the variable 变量的更换transformation rules 变换规则transformation theory 变换论transformation to principal axes 轴变换transgression 超渡transient response 瞬态响应transient stability 瞬态稳定性transient state 瞬态transient time 过渡时间transition function 转移函数transition graph 转换图transition matrix 转移矩阵transition probability 转移函数transitive closure 传递闭包transitive graph 传递图transitive group of motions 可迁运动群transitive law 可迁律transitive permutation group 可迁置换群transitive relation 传递关系transitive set 可递集transitivity 可递性transitivity laws 可迁律translatable design 可旋转试验设计translate 转移translation 平移translation curve 平移曲线translation group 平移群translation invariant 平移不变的translation invariant metric 平移不变度量translation number 殆周期translation of axes 坐标轴的平移translation operator 平移算子translation surface 平移曲面translation symmetry 平移对称translation theorem 平移定理transmission channel 传输通道transmission ratio 传输比transport problem 运输问题transportation algorithm 运输算法transportation matrix 运输矩阵transportation network 运输网络transportation problem 运输问题transpose 转置transposed inverse matrix 转置逆矩阵transposed kernel 转置核transposed map 转置映射transposed matrix 转置阵transposition 对换transversal 横截矩阵胚transversal curve 横截曲线transversal field 模截场transversal lines 截线transversality 横截性transversality condition 横截条件transverse axis 横截轴transverse surface 横截曲面trapezium 不规则四边形trapezoid 不规则四边形trapezoid formula 梯形公式trapezoid method 梯形公式traveling salesman problem 转播塞尔斯曼问题tree 树trefoil 三叶形trefoil knot 三叶形纽结trend 瞧trend line 瞧直线triad 三元组trial 试验triangle 三角形triangle axiom 三角形公理triangle condition 三角形公理triangle inequality 三角形公理triangulable 可三角剖分的triangular decomposition 三角分解triangular form 三角型triangular matrix 三角形矩阵triangular number 三角数triangular prism 三棱柱triangular pyramid 四面形triangular surface 三角曲面triangulate 分成三角形triangulation 三角剖分triaxial 三轴的triaxial ellipsoid 三维椭面trichotomy 三分法trident of newton 牛顿三叉线tridiagonal matrix 三对角线矩阵tridimensional 三维的trigammafunction 三函数trigonometric 三角的trigonometric approximation polynomial 三角近似多项式trigonometric equation 三角方程trigonometric function 三角函数trigonometric moment problem 三角矩问题trigonometric polynomial 三角多项式trigonometric series 三角级数trigonometrical interpolation 三角内插法trigonometry 三角学trihedral 三面形的trihedral angle 三面角trihedron 三面体trilateral 三边的trilinear 三线的trilinear coordinates 三线坐标trilinear form 三线性形式trinomial 三项式;三项式的trinomial equation 三项方程triplanar point 三切面重点 ?triple 三元组triple curve 三重曲线triple integral 三重积分triple point 三重点triple product 纯量三重积triple product of vectors 向量三重积triple root 三重根triple series 三重级数triple tangent 三重切线triply orthogonal system 三重正交系triply tangent 三重切线的trirectangular spherical triangle 三直角球面三角形trisecant 三度割线trisect 把...三等分trisection 三等分trisection of an angle 角的三等分trisectrix 三等分角线trivalent map 三价地图trivector 三向量trivial 平凡的trivial character 单位特贞trivial cohomology functor 平凡上同弹子trivial extension 平凡扩张trivial fibre bundle 平凡纤维丛trivial graph 平凡图trivial homogeneous ideal 平凡齐次理想trivial knot 平凡纽结trivial solution 平凡解trivial subset 平凡子集trivial topology 密着拓扑trivial valuation 平凡赋值triviality 平凡性trivialization 平凡化trochoid 摆线trochoidal 余摆线的trochoidal curve 摆线true error 真误差true formula 真公式true proposition 真命题true sign 直符号true value 真值truncated cone 截锥truncated cylinder 截柱truncated distribution 截尾分布truncated pyramid 截棱锥truncated sample 截样本truncated sequence 截序列truncation 舍位truncation error 舍位误差truncation point 舍位点truth 真值truth function 真值函项truth matrix 真值表truth set 真值集合truth symbol 真符号truth table 真值表truthvalue 真值tube 管tubular knot 管状纽结tubular neighborhood 管状邻域tubular surface 管状曲面turbulence 湍流turbulent 湍聊turing computability 图灵机可计算性turing computable 图灵机可计算的turing machine 图录机turn 转向turning point 转向点twice 再次twice differentiable function 二次可微函数twin primes 素数对twisted curve 空间曲线twisted torus 挠环面two address 二地址的two address code 二地址代码two address instruction 二地址指令two body problem 二体问题two decision problem 二判定问题two digit 二位的two dimensional 二维的two dimensional laplace transformation 二重拉普拉斯变换two dimensional normal distribution 二元正态分布two dimensional quadric 二维二次曲面two dimensional vector space 二维向量空间two fold transitive group 双重可迁群two person game 两人对策two person zero sum game 二人零和对策two phase sampling 二相抽样法two place 二位的two point distribution 二点分布two point form 两点式two sample method 二样本法two sample problem 二样本问题two sample test 双样本检验two sheet 双叶的two sided condition 双边条件two sided decomposition 双边分解two sided divisor 双边因子two sided ideal 双边理想two sided inverse 双边逆元two sided module 双边模two sided neighborhood 双侧邻域two sided surface 双侧曲面two sided test 双侧检定two stage sampling 两阶段抽样法two termed expression 二项式two valued logic 二值逻辑two valued measure 二值测度two variable matrix 双变量矩阵two way array 二向分类two way classification 二向分类twopoint boundary value problem 两点边值问题type 型type problem 类型问题typenumber 型数typical mean 典型平均。

Affine Algebras, Langlands Duality and Bethe Ansatz

EDWARD FRENKEL

arXiv:q-alg/9506003v3 Sep 1999

In memory of Claude Itzykson

1. Introduction. By Langlands duality one usually understands a correspondence between automorphic representations of a reductive group G over the ring of adels of a field F , and homomorphisms from the Galois group Gal(F /F ) to the Langlands dual group GL . It was originally introduced in the case when F is a number field or the field of rational functions on a curve over a finite field [1]. Recently A. Beilinson and V. Drinfeld [2] proposed a version of Langlands correspondence in the case when F is the field of rational functions on a curve X over C. This geometric Langlands correspondence relates certain D–modules on the moduli stack MG (X ) of principal G–bundles on X , and GL –local systems on X (i.e. homomorphisms π1 (X ) → GL ). A. Beilinson and V. Drinfeld construct this correspondence by applying a localization functor to representations of the affine Kac-Moody algebra g of critical level k = −h∨ , where h∨ is the dual Coxeter number. The localization functor assigns a twisted D–module on MG (X ) to an arbitrary g– module from a category O0 . The fibers of this D–module are analogous to spaces of conformal blocks from conformal field theory. In fact, the D–module, which corresponds to the vacuum irreducible g–module of level k ∈ Z+ , is the sheaf of sections of a vector bundle (with projectively flat connection), whose fiber is dual to the space of conformal blocks of the Wess-Zumino-Witten model. The analogy between conformal field theory and the theory of automorphic representations was underscored by E. Witten in [3]. It is at the critical level where this analogy can be made even more precise due to the richness of representation theory of g. The peculiarity of the critical level is that a completion of the universal enveloping algebra of g at this level, U−h∨ (g) = U (g)/(K + h∨ ), contains a large center Z (g). This center is isomorphic to the classical W–algebra W(gL ) associated to the Lie algebra gL , which is Langlands dual to g [4]. Recall that W(gL ) consists of functionals on a certain Poisson manifold, which is obtained by the Drinfeld-Sokolov reduction from a hyperplane in the dual space to gL [5]. Elements of this Poisson manifold can be considered as connections of special kind on a GL –bundle over a punctured disc called gL –opers in [6]. For example, sl2 –opers are the same as projective connections. Thus,

2002. ‘Connectives in quantum and other cumulative logics

Why do Birkhoff and von Neumann expect that the negation of an observable be observable?

2 C-logics

2.1 Definition

The framework is the one presented in [7]. Let L be any non-empty set. The elements of L should be viewed as propositions or formulas and L is therefore a language. At present no structure is assumed on L and its elements are therefore to be taken as atomic propositions. Let C : 2L −→ 2L. Definition 1 The operation C is said to be a C-logics iff it satisfies the two following properties.

May 2002

Abstract

The nonmonotonic logics definable by definability-preserving choice functions that satisfy Coherence have been studied in [7]. Larger families correspond to weakenings of this property. The cumulative and loop-cumulative relations of [6] are characterized by such models and, as a consequence, one may study the natural connectives for those logics. The representation results obtained are surprisingly smooth: in the completeness part the choice function may be defined on any set of models, not only definable sets and no definability-preservation property is required in the soundness part. For those logics, proper conjunction and negation may be defined, but no proper disjunction, contrary to the situation studied in [7]. Quantum Logics, as defined by [3] are such Logics but the orthogonal complement does not provide a proper negation.

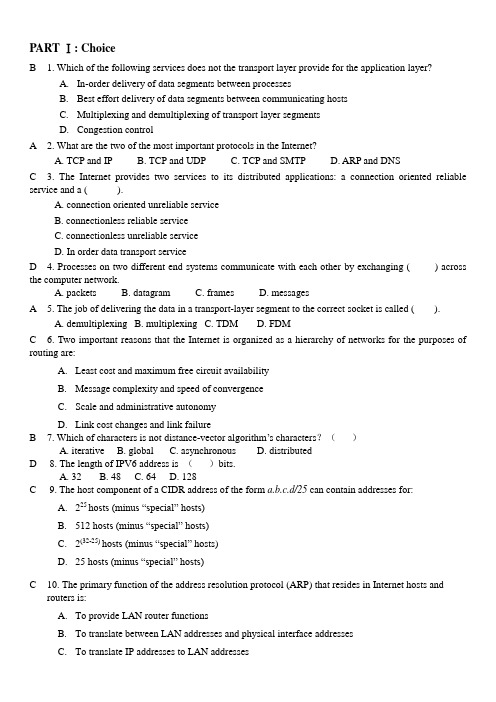

天津理工大学 计算机网络题库

PART Ⅰ: ChoiceB 1. Which of the following services does not the transport layer provide for the application layer?A.In-order delivery of data segments between processesB.Best effort delivery of data segments between communicating hostsC.Multiplexing and demultiplexing of transport layer segmentsD.Congestion controlA 2. What are the two of the most important protocols in the Internet?A. TCP and IPB. TCP and UDPC. TCP and SMTPD. ARP and DNSC 3. The Internet provides two services to its distributed applications: a connection oriented reliable service and a ( ).A. connection oriented unreliable serviceB. connectionless reliable serviceC. connectionless unreliable serviceD. In order data transport serviceD 4. Processes on two different end systems communicate with each other by exchanging ( ) across the computer network.A. packetsB. datagramC. framesD. messagesA 5. The job of delivering the data in a transport-layer segment to the correct socket is called ( ).A. demultiplexingB. multiplexingC. TDMD. FDMC 6. Two important reasons that the Internet is organized as a hierarchy of networks for the purposes of routing are:A.Least cost and maximum free circuit availabilityB.Message complexity and speed of convergenceC.Scale and administrative autonomyD.Link cost changes and link failureB 7. Which of characters is not distance-vector algorithm’s characters?()A. iterativeB. globalC. asynchronousD. distributedD 8. The length of IPV6 address is ()bits.A. 32B. 48C. 64D. 128C 9. The host component of a CIDR address of the form a.b.c.d/25 can contain addresses for:A.225 hosts (minus “special” hosts)B.512 hosts (minus “special” hosts)C.2(32-25) hosts (minus “special” hosts)D.25 hosts (minus “special” hosts)C 10. The primary function of the address resolution protocol (ARP) that resides in Internet hosts androuters is:A.To provide LAN router functionsB.To translate between LAN addresses and physical interface addressesC.To translate IP addresses to LAN addressesD.To calculate the shortest path between two nodes on a LANA 11. The POP3 protocol runs over ____ and uses port ____.A. TCP 110B. UDP 110C. UDP 25D. TCP 25D 12.When a destination host transport layer receives data from the network layer, it unambiguouslyidentifies the appropriate process to pass the data to by using a triplet consisting of:A. Source port #, destination IP address, and source IP addressB. Destination port #, source port #, process ID#C. Destination port #, source port #, destination IP addressD. Destination port #, source port #, source IP addressD 13. From the list below, select the items found in the TCP segment structure that are not found in theUDP segment structure:A. Application Generated DataB. Destination Port #C. Source Port #D. Sequence #A 14. The RIP routing protocol is based on an algorithm that is:A. Based on information received only from link “neighbors”B. A link state algorithmC. An OSPF algorithmD. A centralized routing algorithmB 15. With an exterior routing protocol, which of the following issues generally dominates the routing decisions?A. Geographical distance between AS’sB. PolicyC. Number of AS’s traversedD. Current congestion levels in the AS’sA 1. End system are connected together by ____.A. communication linksB. application layerC. transport layerD. the network layerC 2. Which application’s NOT using TCP?A. SMTPB. HTTPC. DNSD. All of themB 3. In the polling protocols, the master node polls each of the nodes in a/an ____ fashion.A. randomB. appointedC. round-robinD. uncirculatedC 4. The DNS protocol runs over ____ and uses port ____.A. UDP 36B. TCP 36C. UDP 53D. TCP 53A 5. TCP provides a ____ service to its applications to eliminate the possibility of the sender over-flowingthe receiver’s buffer.A. flow-controlB. congestion controlC. reliability controlD. data connectionD 6. We can classify just about any multiple access protocol as belonging to one of three categories: channel partitioning protocols, random access protocols, and ____.A. address resolution protocolsB. Dynamic host configuration protocolsC. link-control protocolsD. taking-turns protocolsB 8. The maximum transfer unit(MTU) in Ethernet frame structure is ()byte .A. 1000B. 1500C. 800D. 2000B 9. The socket of UDP is identified by _____ and _______.A. source IP address and source port numberB. destination IP address and destination port number.C. source IP address and destination port number.D. destination IP address and source IP address.C 10. Which is not plug and play in the following four items?A. DHCPB. HubsC. RoutersD. SwitchesD 11.Which of routers is not default routers ?A. first-hop routerB. source routerC. destination routerD. second-hop routerB 13. ICMP is_____.A. the protocol of Application layerB. the protocol of network layerC. the protocol of transport layerD. not a part of TCP/IP protocolsB 14. As general, we has following channel partitioning protocols except ____.A. TDMB. CSMAC. FDMD.CDMAD 15. ____ is most used for error reporting.A. UDPB. SMTPC. FTPD. ICMPB 16. The header of IPV6 is ____byte.A. 20B. 40C. 60D. 80B 17. In the network layer these service are host-to-host service provided by ____. (B)A. the transport layer to the network layerB. the network layer to the transport layerC. the network layer to the network layerD. the transport layer to the transport layerA 18. If there is not enough memory to buffer an incoming packet , a policy that drop the arriving packet called ____.A. drop-tailB. packet lossC. protocolD. encapsulationC 19. In either case, a ____ receives routing protocol messages, which are used to configure its forwarding table.A. serverB. hostC. routerD. ModemD 20. Which of the following functions does not belong to PPP___.A. framingB. link-control protocolsC. network-control protocolsD. error correctionB 1. Which of the following services does the Internet network layer provide for the Internet transport layer?A.In-order delivery of data segments between processesB.Best effort delivery of data segments between communicating hostsC.Multiplexing and demultiplexing of transport layer segmentsD.Congestion controlD 2. The main task of the Internet’s Domain Name System (DNS) is to:A.Translate port numbers to IP addressesB.Specify the standards for Internet domain namesC.Provide an authority for registering domain namesD.Translate mnemonic(记忆的)names to IP addressesA 10. The FTP protocol runs over ____ and uses port ____.A. TCP 21B. TCP 80C. UDP 20D. TCP 110C 3.RDT3.0’s receiver FSM is same to:a) RDT1.0 b) RDT2.1 c) RDT2.2 d) RDT2.0B 4.The Transmission Control Protocol (TCP) provides which of the following services?a)End-to-end station addressingb)Application multiplexingc)Inter network routingd)Medium access control (MAC)D 6.Given that the requested information is not available at any intermediate databases, a non-iterated DNS query from a requesting host would follow the path:a)Root name server, local name server, authoritative name serverb)Authoritative name server, root name server, host name serverc)Local name server, root name server, local name server, authoritative name servere)Local name server, root name server, authoritative name serverA 8.lect the four essential steps, briefly described, for terminating a TCP connection between a client and a server, assuming that the initiating host is the client:(1)Client sends TCP segment with ACK0 and final sequence number(2)Client sends TCP segment with FIN =1 and goes into FIN_WAIT state(3)Server sends TCP segment to ACK the client’s FIN request and enters CLOSE_WAIT state(4)Server sends TCP segment with FIN=0(5)Server sends TCP segment with FIN=1(6)Client sends TCP segment with to ACK server’s FIN and enters second FIN_WAIT state(7)Client sends TCP segment with FIN=0a) 2,3,5,6 b) 5,1,2,3 c) 1,3,5,7 d) 2,3,4,6B 10.When compensating for link cost changes in the distance vector algorithm, it can generally be said that:a)Increased costs are propagated quickly, i.e., “bad news” travels fastb)Decreased costs are propagated rapidly, i.e., “good news” travels fastc)Decreased costs do not converged)None of the aboveB 14.As an IP datagram travels from its source to its destination:a)the source IP address is changed at each router to identify the sending routerb)the router uses the destination IP address to consult its routing tablec)the router does not use the IP addresses in the datagramd)the destination IP address is changed at each router to reflect the next hopC 15.From the list below, choose the bit pattern which could be a valid generator value for the CRC code (R) 11010:a)1110b)011010c)100101d)10011A 16.Consider sending a 1300 byte IPv4 datagram into a link that has an MTU of 500 bytes:a)Three fragments are created.b)Four fragments are created.c)Three fragments are created with offsets 0, 500 1000d)The last fragment consists of exactly 300 bytes of data from the original datagramC 17.Suppose one IPv6 router wants to send a datagram to another IPv6 router, but the two are connected together via an intervening IPv4 router. If the two routers use tunneling, then:a)The sending IPv6 router creates an IPv4 datagram and puts it in the data field of an IPv6datagram.b)The sending IPv6 router creates one or more IPv6 fragments, none of which is larger than themaximum size of an IPv4 datagram.c)The sending IPv6 router creates an IPv6 datagram and puts it in the data field of an IPv4datagram.d)The sending IPv6 router creates an IPv6 datagram and intervening IPv4 router will reject theIPv6 datagramD 18.Which of the following was an important consideration in the design of IPv6a)fixed length 40-byte header and specified options to decrease processing time at IPv6 nodesb)128-bit addresses to extend the address spacec)different types of service (flows) definedd)all of the aboveD 19.A network bridge table is used to perform the following:a)Mapping MAC addresses to bridge port numbersb)Forwarding frames directly to outbound ports for MAC addresses it handlesc)Filtering (discarding) frames that are not destined for MAC addresses it handlesd)All of the abovePART Ⅱ: True / False (1 points per question – total:20 points)1. The DNS server can update the records. (T)2. The TCP connection is a direct virtual pipe between the client’s socket and the server’s connection socket. (T)3. SMTP protocol connect the sender’s mail server and receiver’s mail server (T)4. Whereas a transport-layer protocol provides logical communication between processes running on different hosts, a network-layer protocol provides logical communication between hosts. (T)5. UDP and TCP also provide integrity checking by including right-detection fields in their headers. (F)6. If the application developer chooses UDP instead of TCP, then the application is not directly talking with IP. ( F )7. When we develop a new application, we must assign the application a port number. ( T )8. Real-tine applications, like Internet phone and video conferencing, react very poorly to TCP’s congestion control. ( T )9. The sender knows that a received ACK or NAK packet was generated in response to its most recently transmitted data packet. (T)10. To simplify terminology, when in an Internet context, we refer to the 4-PDU as a unit. (F)11. DV algorithm is essentially the only routing algorithm used in practice today in the Internet。

PU(2) MONOPOLES. III EXISTENCE OF GLUING AND OBSTRUCTION MAPS

2

PAUL M. N. FEEHAN AND THOMAS G. LENESS

moduli space of PU(2) monopoles and thus enable calculations of their contributions to Donaldson invariants using the PU(2)-monopole cobordism 27]. 1.1. Statement of results. The main purpose of the present article and its companion 26] is to prove a general gluing theorem for PU(2) monopoles, adequate for the topological calculations mentioned in 28] and carried out in detail in 21], 27]. Throughout our work we let (X; g ) be a closed, connected, oriented, C 1 Riemannian four-manifold with b+ (X ) > 0 and spinc structure s0 = ( ; W + ; W ? ). We require that the perturbation parameters de ning the PU(2) monopole equations (2.1) be generic, so the transversality results of 12], 17], and 33] ensure that the moduli spaces of PU(2) monopoles, Seiberg-Witten U(1) monopoles, and anti-self-dual SO(3) connections possess the usual smoothness properties and have the expected dimension. While we shall direct the reader to x2, x3, and x9 for detailed de nitions and notation, we note that M sw (s0 ) is the moduli space of Seiberg-Witten monopoles on X , that M (t) is the moduli space of PU(2) monopoles on X for a spinu structure t = ( ; W + ; W ? ; E ), where E is a Hermitian, rank-two bundle over X , and that M (t; ) is a nite-dimensional thickened or virtual moduli space of PU(2) monopoles which contains M (t), as a submanifold away from singularities, with > 0 a small-eigenvalue bound arising in the extended PU(2) monopole equations which de ne M (t; ). We let w 2 H 2(X ; Z be a class such that no ) SO(3) bundle over X with second Stiefel-Whitney class equal to w (mod 2) admits a at connection. The open subset M ;0(t) M (t) is represented by pairs such that the SO(3) connection is not reducible and the spinor is not identically zero. Theorem 1.1. Let E be a rank-two, Hermitian vector bundle over X with c1(E ) = w 1 1. Let 0 < ` < b c be an integer, let E` be the rankand c2(E ) ? 4 c1 (E )2 = two, Hermitian vector bundle over X with det E` = det E and c2 (E`) = c2 (E ) ? `. Let t = ( ; W +; W ?; E ) and t` = ( ; W +; W ?; E`). Let Sym` (X ) be a smooth stratum and let U`; b M (t` ; ) be a nite-dimensional, precompact, open, S 1-invariant subset. The space U`; is a tubular neighborhood of U`; \ M ;0 (t` ), of size "` > 0 via the tubular distance function (9.39). Then, for a small enough positive constants "` and 0, there are A compact Lie group G( ), an S 1 -equivariant C 1 principle G( )-bundle Fr(U`; ; ) ! U`; , a universal topological G( )-space Z( ), and an S 1-equivariant ber bundle Gl(U`; ; ; 0) = Fr(U`; ; ) G( ) Z( ) ! U`; : Here, 0 is a su ciently small positive constant, depending at most on (g; ; U`; ). An S 1-equivariant C 1 map ; : Gl(U`; ; ; 0) ! M ;0(t; ), where Gl+ (U`; ; ; 0) Gl(U`; ; ; 0) is the open subset (3.26). An S 1-equivariant C 1 section ; of an S 1-equivariant C 1 vector bundle over Gl+(U`; ; ; 0). The bundle has real rank equal to 2` plus the real codimension of M ;0(t) M ;0(t; ). Together, the map ; and section ; have the property that ;0 ?1 ; ( ; (0)) M (t): We call Gl(U`; ; ; 0) the bundle of local gluing data, ; the local gluing map , the local obstruction bundle , and ; the local obstruction section . The gluing maps

Optimization processing manner null of multi-stage

专利名称:Optimization processing manner null of multi-stage发明人:松永 裕介,藤田 昌宏申请号:JP特願平2-57421申请日:19900308公开号:JP特公平7-120365B2公开日:19951220专利内容由知识产权出版社提供摘要:PURPOSE:To speed up the optimization processing of a multistage logic circuit by executing arithmetic processing by using data structure called a sequenced dichotomic decision graph, for instance, executing the arithmetic processing between two dichotomic decision graphs expressing logical functions. CONSTITUTION:The sequence of variable of plural pieces of the input variables of the multistage logic circuit is determined, and the input variable V1 of first precedence is allotted to a root, and all the other input variable V2, V3 are allotted to nodes, and every logic (1, 0) the allotted input variable takes is branched to each gate and net of the multistage logic circuit from the root, and a branch is connected by turns to the node to which the next input variable conforming to the determined precedence is allotted. Then, the tree-structured dichotomic decision graph to express a permissive function in which the branch is connected to a leaf to give the logic (1,0, don't care) of every gate and net is generated finally. Thus, the optimization processing of the multi-stage logic circuit can be speeded up.申请人:富士通株式会社地址:神奈川県川崎市中原区上小田中1015番地国籍:JP代理人:大菅 義之 (外1名)更多信息请下载全文后查看。

MIC2199资料

Micrel, Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel + 1 (408) 944-0800 • fax + 1 (408) 474-1000 • MLF and MicroLeadFrame are trademarks of Amkor Technology, Inc.Typical ApplicationV INF4.5V–24V to 3.3V/7A ConverterE F F I C I E N C Y (%)I LOAD(A)Efficiency forV IN = 5V and V OUT = 3.3VPin ConfigurationCOMPEN/UVLOFB CSH HSD VSW BST GND VOUT VIN LSD VDD4×4 MLF-12L (ML)Ordering InformationPart Number Voltage Temperature Range Package MIC2199BMLAdj–40°C to +125°C12-lead 4×4 MLF™Pin DescriptionPin NumberPin Name Pin Function1COMP Compensation (Output):Internal error amplifier output. Connect to capacitor or series RC network to compensate the regulator control loop.2EN/UVLOEnable/Undervoltage Lockout (Input):Low-level signal powers down the controller. Input below the 2.5V threshold disables switching and functions as an accurate undervoltage lockout (UVLO). Input below the threshold forces complete micropower (<0.1µA) shutdown.3FB Feedback (Input):Regulates FB pin to 0.8V. See “Applications Information”for resistor divider calculations.4CSHCurrent-Sense High (Input):Current limit comparator non-inverting input. A built-in offset of 100mV between CSH and V OUT pins in conjunction with the current-sense resistor set the current limit threshold level. This is also the non-inverting input to the current sense amplifier.5VOUT Current-Sense Low (Input):Output voltage feedback input and inverting input for the current limit comparator and the current sense amplifier.6VIN Unregulated Input (Input):+4.5V to +32V supply input.7VDD5V Internal Linear-Regulator (Output):V DD is the external MOSFET gate drive supply voltage and internal supply bus for the IC. Bypass to GND with 4.7µF.8LSD Low-Side Drive (Output):High-current driver output for low-side N-Channel MOSFET. Voltage swing is between ground and V DD .9GND Ground (Return).10BST Boost (Input):Provides drive voltage for the high-side MOSFET driver. The drive voltage is higher than the input voltage by V DD minus a diode drop.11VSW Switch (Return):High-side MOSFET driver return.12HSDHigh-Side Drive (Output):High-current driver output for high-side MOSFET.This node voltage swing is between ground and V IN +5V minus a diode drop.Electrical Characteristics (Note 4)V IN = V EN = 12V; T J = 25°C, unless noted, bold values indicate –40°C ≤ T J ≤ +125°C ParameterCondition Min Typ Max Units Feedback Voltage Reference (±1%)0.7920.80.808V Feedback Voltage Reference (±2%)0.7840.816V Feedback Voltage Reference 4.5V < V IN < 32V, 0 < (V CSH – V OUT ) < 60mV (±3%)0.7760.824V Feedback Bias Current 10nA Output Voltage Range0.86V Output Voltage Line Regulation V IN = 4.5V to 32V, V CSH – V OUT = 60mV 0.03%/V Output Voltage Load Regulation 25mV < (V CSH – V OUT ) < 60mV0.5%Input and V DD Supply Quiescent Currentexcluding external MOSFET gate drive current 1.6 2.5mA Shutdown Quiescent Current V EN/UVLO = 0V 0.15µA Digital Supply Voltage (V DD )I L = 0mA to 5mA4.75.0 5.3V Undervoltage LockoutV IN upper threshold (turn-on threshold) 4.25 4.4V V IN lower threshold (turn-off threshold)3.954.1VEnable/UVLOEnable Input Threshold 0.6 1.1 1.6V UVLO Threshold 2.22.5 2.8V Enable Input Current V EN/UVLO = 5V0.15µACurrent LimitCurrent Limit Threshold Voltage (V CSH – V OUT )557595mVError AmplifierTransconductance Error Amplifier GM 0.2mSOscillator Section Oscillator Frequency 270300330kHz Maximum Duty Cycle 8085%Minimum On-Time170200nsAbsolute Maximum Ratings (Note 1)Analog Supply Voltage (V IN ).......................................+34VDigital Supply Voltage (V DD ).........................................+7V Driver Supply Voltage (B ST )..................................V IN + 7V Sense Voltage (V OUT , C SH ).............................7V to –0.3V Enable Pin Voltage (V EN/UVLO )......................................V IN Power Dissipation (P D )4×4 MLF™.................................665mW @ T A = 85°C Ambient Storage Temperature (T S ).........–65°C to +150°C ESD, Note 3Operating Ratings (Note 2)Analog Supply Voltage (V IN )........................+4.5V to +32V Output Voltage Range (V OUT )........................+0.8V to +6V Junction Temperature (T J ).......................–40°C to +125°C Package Thermal Resistance4×4 MLF-12L (θJA )..............................................60°C/WParameter Condition Min Typ Max Units Frequency Foldback Threshold measured at V OUT pin0.250.400.55V Foldback Frequency75kHz Gate DriversRise/Fall Time C L = 3000pF60ns Output Driver Impedance source58.5Ωsink 3.56ΩDriver Non-Overlap Time80nsNote 1.Exceeding the absolute maximum rating may damage the device.Note 2.The device is not guaranteed to function outside its operating rating.Note 3.Devices are ESD protected; however, handling precautions are recommended. Human body model, 1.5k in series with 100pF.Note 4.Specification for packaged product only.C U R R E N T (m A )TEMPERATURE (°C)Quiescent Currentvs. TemperatureQ U I E S C E N T C U R R E N T (m A )SUPPLY VOLTAGE (V)Quiescent Current vs. Supply VoltageR E F E R E N C E V O L T A G E (V )SUPPLY VOLTAGE (V)V FBLine RegulationF B V O L T AG E (V )TEMPERATURE (°C)V FBV D D R E G U L A T O R V O L T A G E (V )LOAD CURRENT (mA)V DDLoad RegulationV D D R E G U L A T O R V O L T A G E (V )TEMPERATURE (°C)V DDF R E Q U E N C Y V A R I A T I O N (%)TEMPERATURE (°C)Oscillator Frequency vs. TemperatureF R E Q U E N C Y V A R I A T I O N (%)SUPPLY VOLTAGE (V)Oscillator Frequency vs. Supply VoltageTypical CharacteristicsO V E R C U R R E N T T H R E S H O L D (V )TEMPERATURE (°C)Overcurrent Thresholdvs. Temperature00.511.522.533.5O U T P U T V O L T A G E (V )OUTPUT CURRENT (A)Current Limit FoldbackV D D R E G U L A T O R V O L T A G E (V )SUPPLY VOLTAGE (V)V DDLine RegulationBlock DiagramV C COMP R Figure 1.Internal Block DiagramFunctional DescriptionThe MIC2199 is a BiCMOS, switched-mode, synchronous step-down (buck) converter controller. Current-mode control is used to achieve superior transient line and load regulation.An internal corrective ramp provides slope compensation for stable operation above a 50% duty cycle. The controller is optimized for high-efficiency, high-performance DC-DC con-verter applications.The MIC2199 block diagram is shown above.The MIC2199 controller is divided into 5 functions.•Control loop •Current limit•Reference, enable and UVLO •MOSFET gate drive •OscillatorControl LoopThe MIC2199 operates in PWM (pulse-width-modulation)mode. In PWM mode, the synchronous buck converter forces continuous current to flow in the inductor which also improves cross regulation of transformer coupled, multiple output con-figurations.PWM Control LoopThe MIC2199 uses current-mode control to regulate the output voltage. This method senses the output voltage (outer loop) and the inductor current (inner loop). It uses inductor current and output voltage to determine the duty cycle of the buck converter. Sampling the inductor current removes the inductor from the control loop, which simplifies compensa-tion.A block diagram of the MIC2199 PWM current-mode control loop is shown in Figure 2 and the PWM mode voltage and current waveform is shown in Figure 3. The inductor current is sensed by measuring the voltage across the resistor, R CS .A ramp is added to the amplified current-sense signal toprovide slope compensation, which is required to prevent unstable operation at duty cycles greater than 50%.A transconductance amplifier is used for the error amplifier,which compares an attenuated sample of the output voltage with a reference voltage. The output of the error amplifier isthe COMP (compensation) pin, which is compared to the current-sense waveform in the PWM block. When the current signal becomes greater than the error signal, the comparator turns off the high-side drive. The COMP pin (pin 1) provides access to the output of the error amplifier and allows the use of external components to stabilize the voltage loop.C R Figure 2.PWM OperationV DD 0V0V 0AV DD V IN + V DDV INV SWReset PulseV HSDV LSDI LOADI L1Figure 3.PWM-Mode TimingCurrent LimitThe MIC2199 output current is detected by the voltage drop across the external current-sense resistor (R CS in Figure 2.). The current limit threshold is 75mV±20mV. The current-sense resistor must be sized using the minimum current limit threshold. The external components must be designed to withstand the maximum current limit. The current-sense resistor value is calculated by the equation below:R55mVICSOUT(max)=The maximum output current is:I 95mV ROUT(max)CS=The current-sense pins CSH (pin 4) and V OUT (pin 5) are noise sensitive due to the low signal level and high input impedance. The PCB traces should be short and routed close to each other. A small (1nF to 0.1µF) capacitor across the pins will attenuate high frequency switching noise.When the peak inductor current exceeds the current limit threshold, the current limit comparator, in Figure2, turns off the high-side MOSFET for the remainder of the cycle. The output voltage drops as additional load current is pulled from the converter. When the output voltage reaches approxi-mately 0.4V, the circuit enters frequency-foldback mode and the oscillator frequency will drop to 75kHz while maintaining the peak inductor current equal to the nominal 75mV across the external current-sense resistor. This limits the maximum output power delivered to the load under a short circuit condition.Reference, Enable and UVLO CircuitsThe output drivers are enabled when the following conditions are satisfied:•The V DD voltage (pin 7) is greater than its under-voltage threshold (typically 4.25V).•The voltage on the enable pin is greater than the enable UVLO threshold (typically 2.5V).The internal bias circuit generates a 0.8V bandgap reference voltage for the voltage error amplifier and a 5V V DD voltage for the gate drive circuit. The MIC2199 uses FB (pin 3) for output voltage sensing.The enable pin (pin 2) has two threshold levels, allowing the MIC2199 to shut down in a low current mode, or turn off output switching in UVLO mode. An enable pin voltage lower than the shutdown threshold turns off all the internal circuitry and reduces the input current to typically 0.1µA.If the enable pin voltage is between the shutdown and UVLO thresholds, the internal bias, V DD, and reference voltages are turned on. The output drivers are inhibited from switching and remain in a low state. Raising the enable voltage above the UVLO threshold of 2.5V enables the output drivers.Either of two UVLO conditions will disable the MIC2199 from switching.•When the V DD drops below 4.1V•When the enable pin drops below the 2.5V threshold MOSFET Gate DriveThe MIC2199 high-side drive circuit is designed to switch an N-Channel MOSFET. Referring to the block diagram in Figure 2, a bootstrap circuit, consisting of D2 and C BST, supplies energy to the high-side drive circuit. Capacitor C BST is charged while the low-side MOSFET is on and the voltage on the V SW pin (pin 11) is approximately 0V. When the high-side MOSFET driver is turned on, energy from C BST is used to turn the MOSFET on. As the MOSFET turns on, the voltage on the V SW pin increases to approximately V IN. Diode D2 is reversed biased and C BST floats high while continuing to keep the high-side MOSFET on. When the low-side switch is turned back on, C BST is recharged through D2.The drive voltage is derived from the internal 5V V DD bias supply. The nominal low-side gate drive voltage is 5V and the nominal high-side gate drive voltage is approximately 4.5V due the voltage drop across D2. A fixed 80ns delay between the high- and low-side driver transitions is used to prevent current from simultaneously flowing unimpeded through both MOSFETs.OscillatorThe internal oscillator is free running and requires no external components. The nominal oscillator frequency is 500kHz. If the output voltage is below approximately 0.4V, the oscillator operates in a frequency-foldback mode and the switching frequency is reduced to 75kHz.TIMEFigure 4.Startup WaveformAbove 0.4V, the switching frequency increases to 500kHz causing the output voltage to rise a greater rate. The rise time of the output is dependent on the output capacitance, output voltage, and load current. The oscilloscope photo in Figure 4 show the output voltage at startup.Minimum PulsewidthThe MIC2199 has a specified minimum pulsewidth. This minimum pulsewidth places a lower limit on the minimum duty cycle of the buck converter.Figure 5 shows the minimum output voltage versus input supply voltage for the MIC2199. For example, for V IN = 15V,V OUT = 1V would be the lowest achievable voltage thatconforms to the minimum-on-time.O U T P U T V O L T A G E (V )INPUT VOLTAGE (V)Figure 5.Minimum Output Voltagevs. Input Supply VoltageApplications InformationFollowing applications information includes component se-lection and design guidelines.Inductor SelectionValues for inductance, peak, and RMS currents are required to select the output inductor. The input and output voltages and the inductance value determine the peak-to-peak induc-tor ripple current. Generally, higher inductance values are used with higher input voltages. Larger peak-to-peak ripple currents will increase the power dissipation in the inductor and MOSFETs. Larger output ripple currents will also require more output capacitance to smooth out the larger ripple current. Smaller peak-to-peak ripple currents require a larger inductance value and therefore a larger and more expensive inductor. A good compromise between size, loss and cost is to set the inductor ripple current to be equal to 20% of the maximum output current.The inductance value is calculated by the equation below.L V (V V )V f 0.2I OUT IN(max)OUT IN(max)S OUT(max)=×−×××where:f S = switching frequency0.2 = ratio of AC ripple current to DC output current V IN(max) = maximum input voltageThe peak-to-peak inductor current (AC ripple current) is:I V (V V )V f LPP OUT IN(max)OUT IN(max)S =×−××The peak inductor current is equal to the average output current plus one half of the peak-to-peak inductor ripple current.I I 0.5I PK OUT(max)PP=+×The RMS inductor current is used to calculate the I 2×R losses in the inductor.I I 113I I INDUCTOR(rms)OUT(max)P OUT(max)2=×+⎛⎝⎜⎞⎠⎟Maximizing efficiency requires the proper selection of core material and minimizing the winding resistance. The high frequency operation of the MIC2199 requires the use of ferrite materials for all but the most cost sensitive applications.Lower cost iron powder cores may be used but the increase in core loss will reduce the efficiency of the power supply. This is especially noticeable at low output power. The winding resistance decreases efficiency at the higher output current levels. The winding resistance must be minimized although this usually comes at the expense of a larger inductor.The power dissipated in the inductor is equal to the sum of the core and copper losses. At higher output loads, the core losses are usually insignificant and can be ignored. At lower output currents, the core losses can be a significant contribu-tor. Core loss information is usually available from the mag-netics vendor.Copper loss in the inductor is calculated by the equation below:P I R INDUCTORCu INDUCTOR(rms)WINDING2=×The resistance of the copper wire, R WINDING , increases with temperature. The value of the winding resistance used should be at the operating temperature.R R 10.0042(T T )WINDING(hot)WINDING(20C)HOT 20C =×+×−()°°where:T HOT = temperature of the wire under operating load T 20°C = ambient temperatureR WINDING(20°C) is room temperature winding resistance (usually specified by the manufacturer)Current-Sense Resistor SelectionLow inductance power resistors, such as metal film resistors should be used. Most resistor manufacturers make low inductance resistors with low temperature coefficients, de-signed specifically for current-sense applications. Both resis-tance and power dissipation must be calculated before the resistor is selected. The value of R SENSE is chosen based on the maximum output current and the maximum threshold level. The power dissipated is based on the maximum peak output current at the minimum overcurrent threshold limit.R 55mV I SENSE OUT(max)=The maximum overcurrent threshold is:I 95mV R OVERCURRENT(max)CS=The maximum power dissipated in the sense resistor is:P I R D(R)OVERCURRENT(max)2CSSENSE =×MOSFET SelectionExternal N-Channel logic-level power MOSFETs must be used for the high- and low-side switches. The MOSFET gate-to-source drive voltage of the MIC2199 is regulated by an internal 5V V DD regulator. Logic-level MOSFETs, whose operation is specified at V GS = 4.5V must be used.It is important to note the on-resistance of a MOSFET increases with increasing temperature. A 75°C rise in junc-tion temperature will increase the channel resistance of the MOSFET by 50% to 75% of the resistance specified at 25°C.This change in resistance must be accounted for when calculating MOSFET power dissipation.Total gate charge is the charge required to turn the MOSFET on and off under specified operating conditions (V DS and V GS ). The gate charge is supplied by the MIC2199 gate drive circuit. At 500kHz switching frequency, the gate charge can be a significant source of power dissipation in the MIC2199.At low output load this power dissipation is noticeable as areduction in efficiency. The average current required to drivethe high-side MOSFET is:I Q f G[high-side](avg)G S=×where:I G[high-side](avg) =average high-side MOSFET gate currentQ G = total gate charge for the high-side MOSFET taken from manufacturer’s data sheet with V GS = 5V.f s = 300kHzThe low-side MOSFET is turned on and off at V DS = 0because the freewheeling diode is conducting during this time. The switching losses for the low-side MOSFET is usually negligible. Also, the gate drive current for the low-side MOSFET is more accurately calculated using C ISS at V DS =0 instead of gate charge.For the low-side MOSFET:I C V f G[low-side](avg)ISS GS S=××Since the current from the gate drive comes from the inputvoltage, the power dissipated in the MIC2199 due to gate drive is:P V I I GATEDRIVE IN G[high-side](avg)G[low-side](avg)=+()A convenient figure of merit for switching MOSFETs is the on-resistance times the total gate charge (R DS(on) × Q G ). Lower numbers translate into higher efficiency. Low gate-charge logic-level MOSFETs are a good choice for use with the MIC2199. Power dissipation in the MIC2199 package limits the maximum gate drive current.Parameters that are important to MOSFET switch selection are:•Voltage rating •On-resistance •Total gate chargeThe voltage rating of the MOSFETs are essentially equal to the input voltage. A safety factor of 20% should be added to the V DS(max) of the MOSFETs to account for voltage spikes due to circuit parasitics.The power dissipated in the switching transistor is the sum of the conduction losses during the on-time (P CONDUCTION ) and the switching losses that occur during the period of time when the MOSFETs turn on and off (P AC ).P P P SW CONDUCTION AC=+where:P I R CONDUCTION SW(rms)SW 2=×P P P AC AC(off)AC(on)=+R SW = on-resistance of the MOSFET switch.Making the assumption the turn-on and turnoff transition times are equal, the transition time can be approximated by:t C V C V I T ISS GS OSS ING=×+×where:C ISS and C OSS are measured at V DS = 0.I G = gate drive current (1A for the MIC2199)The total high-side MOSFET switching loss is:P (V V )I t f AC IN D PK T S=+×××where:t T = switching transition time (typically 20ns to 50ns)V D = freewheeling diode drop, typically 0.5V.f S it the switching frequency, nominally 300kHzThe low-side MOSFET switching losses are negligible and can be ignored for these calculations.RMS Current and MOSFET Power Dissipation CalculationUnder normal operation, the high-side MOSFETs RMS cur-rent is greatest when V IN is low (maximum duty cycle). The low-side MOSFETs RMS current is greatest when V IN is high (minimum duty cycle). However, the maximum stress the MOSFETs see occurs during short circuit conditions, where the output current is equal to I OVERCURRENT(max). (See the “Sense Resistor” section). The calculations below are for normal operation. To calculate the stress under short circuit conditions, substitute I OVERCURRENT(max) for I OUT(max). Use the formula below to calculate D under short circuit condi-tions.D 0.063 1.810V SHORTCIRCUIT 3IN=−××−The RMS value of the high-side switch current is:I D I I 12SW(high side)(rms)OUT(max)2PP2−=×+⎛⎝⎜⎞⎠⎟I 1D I I 12SW(low side)(rms)OUT(max)2PP2−=−()+⎛⎝⎜⎞⎠⎟where:D = duty cycle of the converterD V V OUT IN=×ηη = efficiency of the converter.Converter efficiency depends on component parameters,which have not yet been selected. For design purposes, an efficiency of 90% can be used for V IN less than 10V and 85%can be used for V IN greater than 10V. The efficiency can be more accurately calculated once the design is complete. If the assumed efficiency is grossly inaccurate, a second iteration through the design procedure can be made.For the high-side switch, the maximum DC power dissipation is:P R ISWITCH1(dc)DS(on)1SW1(rms)2=×For the low-side switch (N-Channel MOSFET), the DC power dissipation is:P R ISWITCH2(dc)DS(on)2SW2(rms)2=×Since the AC switching losses for the low side MOSFET is near zero, the total power dissipation is:P Plow-side MOSFET(max)SWITCH2(dc)=The total power dissipation for the high side MOSFET is:P P Phigh sideMOSFET(max)SWITCH1(dc)AC−=+External Schottky DiodeAn external freewheeling diode is used to keep the inductor current flow continuous while both MOSFETs are turned off. This dead time prevents current from flowing unimpeded through both MOSFETs and is typically 80ns The diode conducts twice during each switching cycle. Although the average current through this diode is small, the diode must be able to handle the peak current.I I280ns fD(avg)OUT S=×××The reverse voltage requirement of the diode is:V VDIODE(rrm) IN=The power dissipated by the Schottky diode is:P I VDIODE D(avg)F=×where:V F = forward voltage at the peak diode currentThe external Schottky diode, D2, is not necessary for circuit operation since the low-side MOSFET contains a parasitic body diode. The external diode will improve efficiency and decrease high frequency noise. If the MOSFET body diode is used, it must be rated to handle the peak and average current. The body diode has a relatively slow reverse recovery time and a relatively high forward voltage drop. The power lost in the diode is proportional to the forward voltage drop of the diode. As the high-side MOSFET starts to turn on, the body diode becomes a short circuit for the reverse recovery period, dissipating additional power. The diode recovery and the circuit inductance will cause ringing during the high-side MOSFET turn-on.An external Schottky diode conducts at a lower forward voltage preventing the body diode in the MOSFET from turning on. The lower forward voltage drop dissipates less power than the body diode. The lack of a reverse recovery mechanism in a Schottky diode causes less ringing and less power loss. Depending on the circuit components and oper-ating conditions, an external Schottky diode will give a 1/2% to 1% improvement in efficiency.Output Capacitor SelectionThe output capacitor values are usually determined by the capacitors ESR (equivalent series resistance). Voltage rating and RMS current capability are two other important factors in selecting the output capacitor. Recommended capacitors are tantalum, low-ESR aluminum electrolytics, and OS-CON. The output capacitor’s ESR is usually the main cause of output ripple. The maximum value of ESR is calculated by: RVIESROUTPP≤∆where:V OUT = peak-to-peak output voltage rippleI PP = peak-to-peak inductor ripple currentThe total output ripple is a combination of the ESR and the output capacitance. The total ripple is calculated below:∆VI(1D)C fI ROUTPPOUT S2PP ESR2=×−×⎛⎝⎜⎞⎠⎟+×()where:D = duty cycleC OUT = output capacitance valuef S = switching frequencyThe voltage rating of capacitor should be twice the output voltage for a tantalum and 20% greater for an aluminum electrolytic or OS-CON.The output capacitor RMS current is calculated below: II12CPPOUT(rms)=The power dissipated in the output capacitor is:P I RDISS(C C ESR(C)OUT OUT(rms)2OUT)=×Input Capacitor SelectionThe input capacitor should be selected for ripple current rating and voltage rating. Tantalum input capacitors may fail when subjected to high inrush currents, caused by turning the input supply on. Tantalum input capacitor voltage rating should be at least 2 times the maximum input voltage to maximize reliability. Aluminum electrolytic, OS-CON, and multilayer polymer film capacitors can handle the higher inrush currents without voltage derating.The input voltage ripple will primarily depend on the input capacitors ESR. The peak input current is equal to the peak inductor current, so:∆V I RIN INDUCTOR(peak)ESR(C)IN=×The input capacitor must be rated for the input current ripple.The RMS value of input capacitor current is determined at the maximum output current. Assuming the peak-to-peak induc-tor ripple current is low:I I D (1D)C (rms)OUT(max)IN≈××−The power dissipated in the input capacitor is:P I R DISS(C)C(rms)ESR(C)IN IN 2IN =×Voltage Setting ComponentsThe MIC2199 requires two resistors to set the output voltage as shown in Figure 6.Figure 6.Voltage-Divider ConfigurationThe output voltage is determined by the equation:V V 1R1R2O REF =×+⎛⎝⎜⎞⎠⎟Where: V REF for the MIC2199 is typically 0.8V.A typical value of R1 can be between 3k and 10k. If R1 is too large it may allow noise to be introduced into the voltage feedback loop. If R1 is too small in value it will decrease the efficiency of the power supply, especially at low output loads.Once R1 is selected, R2 can be calculated using:R2V R1V V REF O REF=×−Voltage Divider Power DissipationThe reference voltage and R2 set the current through the voltage divider.I V R2DIVIDER REF =The power dissipated by the divider resistors is:P (R1R2)I DIVIDER DIVIDER2=+×Efficiency Calculation and ConsiderationsEfficiency is the ratio of output power to input power. The difference is dissipated as heat in the buck converter. Under light output load, the significant contributors are:•Supply current to the MIC2199•MOSFET gate-charge power (included in the IC supply current)•Core losses in the output inductor To maximize efficiency at light loads:•Use a low gate-charge MOSFET or use the small-est MOSFET, which is still adequate for maximum output current.•Use a ferrite material for the inductor core, which has less core loss than an MPP or iron power core.Under heavy output loads the significant contributors to power loss are (in approximate order of magnitude):•Resistive on-time losses in the MOSFETs •Switching transition losses in the MOSFETs •Inductor resistive losses•Current-sense resistor losses•Input capacitor resistive losses (due to the capaci-tors ESR)To minimize power loss under heavy loads:•Use logic-level, low on-resistance MOSFETs. Mul-tiplying the gate charge by the on-resistance gives a figure of merit, providing a good balance be-tween low and high load efficiency.•Slow transition times and oscillations on the volt-age and current waveforms dissipate more power during turn-on and turnoff of the MOSFETs. A clean layout will minimize parasitic inductance and capacitance in the gate drive and high current paths. This will allow the fastest transition times and waveforms without oscillations. Low gate-charge MOSFETs will transition faster than those with higher gate-charge requirements.•For the same size inductor, a lower value will have fewer turns and therefore, lower winding resis-tance. However, using too small of a value will require more output capacitors to filter the output ripple, which will force a smaller bandwidth, slower transient response and possible instability under certain conditions.•Lowering the current-sense resistor value will de-crease the power dissipated in the resistor. How-ever, it will also increase the overcurrent limit and will require larger MOSFETs and inductor compo-nents.•Use low-ESR input capacitors to minimize the power dissipated in the capacitors ESR.。

Python程序设计(英语)智慧树知到课后章节答案2023年下中央财经大学

Python程序设计(英语)智慧树知到课后章节答案2023年下中央财经大学中央财经大学第一章测试1.What is the fundamental question of computer science? ()A:How much money can a programmer make? B:What can be computed?C:What is the most effective programming language? D:How fast can acomputer compute?答案:What can be computed?2. A statement is ()A:a precise description of a problem B:a complete computer command C:a section of an algorithm D:a translation of machine language答案:a complete computer command3.The items listed in the parentheses of a function definition are called ()A:parentheticals B:both B and C are correct C:parameters D:arguments答案:both B and C are correct4.All information that a computer is currently working on is stored in mainmemory. ()A:对 B:错答案:对5. A loop is used to skip over a section of a program. ()A:错 B:对答案:错第二章测试1.Which of the following is not a legal identifier?()A:spAm B:2spam C:spam D:spam4U答案:spam2.In Python, getting user input is done with a special expression called ()A:simultaneous assignment B:input C:for D:read答案:input3.The process of describing exactly what a computer program will do to solve aproblem is called ()A:specification B:programming C:Design D:implementation答案:specification4.In Python, x = x + 1 is a legal statement. ()A:错 B:对答案:对5.The best way to write a program is to immediately type in some code andthen debug it until it works. ()A:对 B:错答案:错第三章测试1.Which of the following is not a built-in Python data type? ()A:int B:rational C:string D:float答案:rational2.The most appropriate data type for storing the value of pi is ()A:string B:int C:float D:irrational答案:float3.The pattern used to compute factorials is ()A:input, process, output B:accumulator C:counted loop D:plaid答案:accumulator4.In Python, 4+5 produces the same result type as 4.0+5.0. ()A:对 B:错答案:错5.Definite loops are loops that execute a known number of times. ()答案:对第四章测试1. A method that changes the state of an object is called a(n) ()A:function B:constructor C:mutator D:accessor答案:mutator2.Which of the following computes the horizontal distance between points p1and p2? ()A:abs(p1.getX( ) - p2.getX( )) B:abs (p1-p2) C:p2.getX( ) - p1.getX( )D:abs(p1.getY( ) - p2.getY( ))答案:abs(p1.getX( ) - p2.getX( ))3.What color is color_rgb (0,255,255)? ()A:Cyan B:Yellow C:Magenta D:Orange答案:Cyan4.The situation where two variables refer to the same object is called aliasing.()A:错 B:对答案:对5. A single point on a graphics screen is called a pixel. ()答案:对第五章测试1.Which of the following is the same as s [0:-1]? ()A:s[:] B:s[:len(s)-1] C:s[-1] D:s[0:len(s)]答案:s[:len(s)-1]2.Which of the following cannot be used to convert a string of digits into anumber? ()A:int B:eval C:str D:float答案:str3.Which string method converts all the characters of a string to upper case? ()A:capwords B:upper C:capitalize D:uppercase答案:upper4.In Python “4”+“5”is “45”. ()A:错 B:对答案:对5.The last character of a strings is at position len(s)-1. ()答案:对第六章测试1. A Python function definition begins with ()A:def B:define C:defun D:function答案:def2.Which of the following is not a reason to use functions? ()A:to demonstrate intellectual superiority B:to reduce code duplication C:tomake a program more self-documenting D:to make a program more modular 答案:to demonstrate intellectual superiority3. A function with no return statement returns ()A:its parameters B:nothing C:its variables D:None答案:None4.The scope of a variable is the area of the program where it may be referenced.()A:对 B:错答案:对5.In Python, a function can return only one value. ()答案:错第七章测试1.In Python, the body of a decision is indicated by ()A:indentation B:curly braces C:parentheses D:a colon答案:indentation2.Placing a decision inside of another decision is an example of ()A:procrastination B:spooning C:cloning D:nesting答案:nesting3.Find a correct algorithm to solve a problem and then strive for ()A:clarity B:efficiency C:scalability D:simplicity答案:clarity;efficiency;scalability;simplicity4.Some modules, which are made to be imported and used by other programs,are referred to as stand-alone programs. ()A:对 B:错答案:错5.If there was no bare except at the end of a try statement and none of theexcept clauses match, the program would still crash. ()答案:对第八章测试1. A loop pattern that asks the user whether to continue on each iteration iscalled a(n) ()A:end-of-file loop B:sentinel loop C:interactive loop D:infinite loop答案:interactive loop2. A loop that never terminates is called ()A:indefinite B:busy C:infinite D:tight答案:infinite3.Which of the following is not a valid rule of Boolean algebra? ()A:a and (b or c) == (a and b) or (a and c) B:(True or False) == True C:not(a and b)== not(a) and not(b) D:(True or x) == True答案:not(a and b)== not(a) and not(b)4.The counted loop pattern uses a definite loop. ()A:错 B:对答案:对5. A sentinel loop should not actually process the sentinel value. ()答案:对第九章测试1.()A:random() >= 66 B:random() < 0.66 C:random() < 66 D:random() >= 0.66答案:random() < 0.662.The arrows in a module hierarchy chart depict ()A:control flow B:one-way streets C:logistic flow D:information flow答案:information flow3.In the racquetball simulation, what data type is returned by the gameOverfunction? ()A:bool B:string C:float D:int答案:bool4. A pseudorandom number generator works by starting with a seed value. ()A:错 B:对答案:对5.Spiral development is an alternative to top-down design. ()A:错 B:对答案:错第十章测试1. A method definition is similar to a(n) ()A:module B:import statement C:function definition D:loop答案:function definition2.Which of the following methods is NOT part of the Button class in thischapter? ()A:activate B:clicked C:setLabel D:deactivate答案:setLabel3.Which of the following methods is part of the DieView class in this chapter?()A:setColor B:clicked C:setValue D:activate答案:setValue4.New objects are created by invoking a constructor. ()A:对 B:错答案:对5.A:错 B:对答案:错第十一章测试1.The method that adds a single item to the end of a list is ()A:plus B:add C:append D:extend答案:append2.Which of the following expressions correctly tests if x is even? ()A:not odd (x) B:x % 2 == 0 C:x % 2 == x D:even (x)答案:x % 2 == 03.Items can be removed from a list with the del operator. ()A:错 B:对答案:对4.Unlike strings, Python lists are not mutable. ()A:对 B:错答案:错5.()A:对 B:错答案:错第十二章测试1.Which of the following was NOT a class in the racquetball simulation? ()A:SimStats B:Player C:RBallGame D:Score答案:Score2.What is the data type of server in an RBallGame? ()A:SimStats B:bool C:int D:Player答案:Player3.The setValue method redefined in ColorDieView class is an example of ()A:polymorphism B:generality C:encapsulation D:inheritance答案:polymorphism;inheritance4.Hiding the details of an object in a class definition is called instantiation. ()A:对 B:错答案:错5.Typically, the design process involves considerable trial and error. ()A:错 B:对答案:对。

failed to establish a new connection -2

failed to establish a new connection -2"Failed to establish a new connection -2" is a commonly encountered error message in network communication. This error typically occurs when a client, such as a web browser, tries to establish a connection with a server and is unable to do so. There can be several reasons for this error, including network connectivity issues, incorrect server configurations, firewall blocking, or a problem with the client-side software.One possible reason for this error is a network connectivity problem. It could be due to a temporary network outage, a misconfiguration of network settings, or a physical problem with the network infrastructure. In such cases, it is recommended to check network cables, routers, and switches to ensure proper connectivity. Additionally, running network diagnostics tools or contacting the network administrator can help identify and resolve any network-related issues.Another possibility is incorrect server configurations. The server may not be properly configured to accept incoming connections or may be using incorrect port or protocol settings. It is essential to review the server configuration files and ensure that they match the expected settings. Common configuration files include the hosts file, which maps network names to IP addresses, and the server's firewall rules. Verifying these configurations, restarting the server, or seeking assistance from server administrators can help in resolving the issue.Firewall blocking is another frequent cause for "Failed to establish a new connection -2" error. Firewalls, either built-in on the clientor server-side, are security measures designed to protect networks by restricting incoming and outgoing connections. Sometimes, a firewall may block the connection attempts from the client. In such cases, checking the firewall settings, adding exceptions for the necessary ports or applications, or disabling the firewall temporarily can help establish a successful connection.Lastly, the error can be attributed to a problem with the client-side software, such as a web browser or an application making the connection. Outdated or incompatible software versions, conflicting extensions or plugins, or misconfigured proxy settings can all lead to connection failures. Updating the software, disabling conflicting extensions, verifying proxy settings, or even trying a different client tool can help resolve the issue.To summarize, encountering a "Failed to establish a new connection -2" error message indicates a problem in establishing a connection between the client and server. It can be caused by network connectivity issues, incorrect server configurations, firewall blocking, or client-side software problems. By troubleshooting these potential causes and addressing them accordingly, it is possible to resolve the issue and establish a successful connection.。

ch6-1_eng combinational logic

Static CMOS Logic Gate CMOS NAND Gate CMOS NOR Gate Complex CMOS Logic Gates Design

EE141 Integrated © Digital

Circuits2nd

9

Combinational Circuits

Pullup Network Inputs Pulldown Network Gnd Out

The function of the PDN is to connect the output to VSS when the output of the logic gate is meant to be 0.

Static CMOS Logic Gate Structure

The static CMOS style is really an extension of the static CMOS inverter to multiple inputs. A logic function in static CMOS must be implemented in both NMOS and PMOS transistors. It is the combination of the pull-up network(PUN) and the pull-down network(PDN). Each input always connects to PUN and PDN simultaneously.

Circuits2nd

Combinational Circuits

Static CMOS Logic Gate Structure (cont.)

VDD

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1 2

E-mail: ambjorn@nbi.dk E-mail: Martin.Harris@nbi.dk 3 E-mail: weis@nbi.dk

1

1

Introduction

Despite substantial progress in our understanding of two-dimensional quantum gravity we are still left with two separate theories: two-dimensional topological gravity and Liouville theory. Topological gravity is a theory where concepts such as geodesic distance make no sense. It can be viewed as a theory on the moduli space of punctured Riemann surfaces, and it is defined in such a way that it allows us to calculate intersection indices related to the moduli spaces. In Liouville theory geodesic distance plays a key rˆ ole: Hartle-Hawking wave functions are defined in terms of the geodesic length of the boundaries [1, 2] and it is possible to consider the quantum theory of universwell as correlation functions depending on the geodesic distance between two punctures [3] (see also references [4, 5] for a discussion of more general correlation functions). Nevertheless, the two theories seem to be identical. The various proofs of the equivalence have so far been rather indirect [6, 7]. Typically, generalized Schwinger-Dyson equations have been derived for the two theories and have been shown to be identical by suitable identifications of variables. By such identifications the concepts of length and area enter into topological gravity without any obvious interpretation. As an example let us mention the following situation: in topological gravity we can calculate the expectation values σn of certain generalized puncture operators and we can define the generating function for this set of observables by ℓn W (ℓ) = σn . (1) n n! In topological gravity ℓ has no interpretation, beyond that of an indeterminate which defines the generating function. However, W (ℓ) agrees with the corresponding HartleHawking wave functional calculated by the use of dynamical triangulations. In Liouville theory ℓ has from first principles an interpretation as the length of a macroscopic boundary of the two-dimensional universe. The same arguments apply to the total space-time volume A, which is defined from first principles if one uses Liouville theory, while it has no natural definition within the framework of topological gravity. The rest of this paper is organized as follows: in section 2 we discuss how concepts such as the volume of space-time and the length of boundaries can be introduced in topological gravity. Since these concepts are natural in topological quantum gravity it should be possible to make a detailed mapping to Liouville theory. This is most conveniently done if we use the dynamically triangulated version of Liouville theory. In order to define the mapping we introduce in section 3 a contour integral representation of the partition function of topological gravity. A related integral representation for the Hermitian matrix model allows us in section 4 to perform a simple and detailed identification between the correlation functions in topological gravity and those in quantum gravity defined via dynamical triangulations. As a side result of this identification we use topological gravity 2

The Niels Bohr Institute, Blegdamsvej 17, DK-2100 Copenhagen Ø, Denmark.

Abstract

We discuss how concepts such as geodesic length and the volume of space-time can appear in 2d topological gravity. We then construct a detailed mapping between the reduced Hermitian matrix model and 2d topological gravity at genus zero. This leads to a complete solution of the counting problem for planar graphs with vertices of even coordination number. The connection between multi-critical matrix models and multi-critical topological gravity at genus zero is studied in some detail. PACS: 04.60.-m Keywords: topological gravity; 2d quantum gravity; matrix model

results to solve completely the counting problem for planar graphs, whose vertices all have even coordination numbers. In section 5 we apply the mapping between topological gravity and matrix models to the case of multi-critical models. Section 6 contains our conclusions.

M φ2 2

+

iφ3 6

dφ exp −Tr

M φ2 2

,

(2)

where the integration is over N × N Hermitian matrices φ. The matrix M is assumed to be symmetric and positive definite, and one can show that ZN (M ) only depends on (2k − 1)!! Tr M −(2k+1) , k ≥ 0, (3) k! where by convention (−1)!! = 1. For N → ∞ the u-function of the KdV-equation is then tk = − u({ti }) = One can write (for N → ∞): log Z ({ti }) = exp