第9章 存储器及其应用

第九章 多媒体数据的存储

2.硬盘

根据磁头的工作方式,可将硬盘存储器分为: (1)移动头磁盘 (2)固定头磁盘

磁盘主要有盘片组、磁头、主轴驱动机构、磁头驱 动定位机构、读/写电路、接口及控制电路等组成。

硬盘的主要技术指标: 道密度与位密度 存储容量 转速 平均存取时间 缓存容量 平均故障间隔时间 硬盘控制器的数据传输率

3.制作VCD光盘

(1)将一张空白光盘放入刻录机,并启动Nero Burning Rom。

(2)在打开的“新编辑”对话框介质类型下拉列表框内选择 “CD”选项;在左侧的列表框中选择“Video CD”图标。

(3)配置选项卡。 (4)添加视频。 (5)配置“刻录编译”对话框。 (6)刻录。 (7)刻录完成,关闭Nero Burning Rom程序。

光盘一般由透明塑料聚碳酸脂材料和多层涂敷 层构成,由基板、存储介质层、反射层及密封保护 层和最上面的印刷层组成。

光 盘 的 直 径 是 12Omm , 厚 度 为 1.2mm , 重 量 为 14~18g,光盘的中心孔直径为15mm。

9.2.2 光盘数据的写入与读出

写入过程:将激光束聚焦成直径为小于1μm 的微小光点,用其热作用,融化光盘表面上的光存 储介质薄膜,在薄膜上形成凹坑。有洞的位置表示 记录了“1”,没有洞的位置表示“0”。这样,在 光盘存储介质层就形成了连续的数据。

谢谢

9.2 数字光盘

所谓数字光盘,就是利用光存储技术存储数据 的圆盘形存储器。

光存储技术是通过光学方法读/写数据的一种 专门技术。

光存储技术的原理是通过改变一个存储单元的 某种光学性质,光电检测器检测识别存储单元相应 光学性质的变化,就可以读出其中存储的二进制数 据“0”和“1”。

9.2.1 激光盘的盘片结构

微型计算机原理及应用第9章输入输出和接口技术

CLK & IOW PS

gf e dcba

COM

35

3.2 数据输入三态缓冲器

外设输入的数据和状态信号,通过数据输入三态缓冲 器经数据总线传送给微处理器。 74LS244三态总线驱动器

74LS244可以用作无条 件传送的输入接口电路。

36

3.2 数据输入三态缓冲器

8

1.2 接口控制原理

(2)串行数据传送

串行数据传送是将构成字符的每个二进制数据位, 按一定的顺序逐位进行传送的方式。 串行数据传送主要用于远程终端或经过公共电话 网的计算机之间的通信。 远距离数据传送采用串行方式比较经济,但串行 数据传送比并行数据传送控制复杂。

9

1.2 接口控制原理

异步串行通信协议规定字符数据的传送格式:

微型计算机原理及应用

1

输入输出和接口技术

1 2 3

接口的基本概念 I/O指令和I/O地址译码 简单的I/O接口

2

输入输出(I/O)是指微型计算机与外界的信息交换, 即通信(communication)。微型计算机与外界的通信, 是通过输入输出设备进行的,通常一种I/O设备与微 型机连接,就需要一个连接电路,我们称之为I/O接 口。 接口是用于控制微机系统与外设或外设与系统设 备之间的数据交换和通信的硬件电路。接口设计涉及 到两个基本问题,一是中央处理器如何寻址外部设备, 实现多个设备的识别;二是中央处理器如何与外设连 接,进行数据、状态和控制信号的交换。 3

状态设臵和存储电路主要由一组数据寄存器构成, 中央处理器和外设就是根据状态寄存器的内容进行 协调动作的。 数据存储和缓冲电路也是一组寄存器,用于暂存 中央处理器和外设之间传送的数据,以完成速度匹配 工作。 7

第9章 单片机的指令系统说明

计算机总是把操作数当作有符号数(补码形式)看待 并影响PSW的相关标志位。影响情况如下: 进位/借位标志CY: 两数和的D7位有进位时,(CY)=1,否则,(CY)=0。 半进位/借位标志AC: 两数和的D3位有进位时,(AC)=1,否则,(AC)=0。 溢出标志OV: 两数和的D7,D6位只有一位有进位时,(OV)=1;否则, (OV)=0,即OV=C6⊕C7。 奇偶标志P: 当累加器A中“1”的个数为奇数时,(P)=1;为偶数 时(P)=0。

例2 把片外RAM的36H单元中的数据送到片外RAM的 1200H单元。 〈分析〉(36H)→(1200H) 程序如下: MOV R1,#36H MOVX A ,@R1 MOV DPTR,#1200H MOVX @DPTR, A <想一想>下面的程序可以实现吗? MOV DPTR, #1200H MOV R1,#36H MOV @DPTR,@R1 注意:片外RAM之间不能直接传送数据,必须经过累加器 A

例5 试分析8051单片机执行下述指令后,累加器A和PSW各标 志位的变化。 MOV A,#0A5H ADD A,#0CFH 解: (A)=10100101B + Data=11001111B CY 01110100B C7 C6 AC (CY)=C7=1;(AC)=1;溢出标志(OV)=C7⊕C6=1⊕0=1,有 溢出;(P)=0。执行结果:(A)=74H。 若为无符号数运算, (CY)=1,表示结果超出(0~255) 范围。若为带符号数运算,因(-49)+(-91)=-140,超出了 (-128~+127)的范围,所以OV=1溢出。

半字节交换 XCHD A,@Ri SWAP A

;(A3~0)((Ri)3~0) ;(A3~0)(A7~4)

自考《计算机系统结构》第9章精讲

第九章并⾏处理技术 本章讲述的重点内容就是阵列处理机和多处理机,对阵列机的基本结构、主要特点、以及阵列机的互连络和并⾏存储器的⽆冲突访问等内容要加强理解。

本章应掌握的概念有:阵列处理机、络拓扑结构、单级⽴⽅体络、多级⽴⽅体等。

⼀、并⾏处理技术(识记): 并⾏性主要是指同时性或并发性,并⾏处理是指对⼀种相对于串⾏处理的处理⽅式,它着重开发计算过程中存在的并发事件。

并⾏性通常划分为作业级、任务级、例⾏程序或⼦程序级、循环和迭代级以及语句和指令级。

作业级的层次⾼,并⾏处理粒度粗。

粗粒度开并⾏性开发主要采⽤MIMD⽅式,⽽细粒度并⾏性开发则主要采⽤SIMD⽅式。

开发计算机并⾏性的⽅法主要有:资源重复、时间重叠和资源共享三种⽅法。

⼆、SIMD并⾏计算机(阵列处理机) 阵列机也称并⾏处理机。

它将⼤量重复设置的处理单元按⼀定⽅式互连成阵列,在单⼀控制部件CU(Contrul Unit)控制下对各⾃所分配的不同数据并⾏执⾏同⼀指令规定的操作,是操作并⾏的SIMD计算机。

它采⽤资源重复的措施开发并⾏性。

是以SIMD(单指令流多数据流)⽅式⼯作的。

1、阵列机的基本结构(识记) 阵列机通常由⼀个控制器CU、N个处理器单元PE(Processing Element)、M个存储模块以及⼀个互连络部件(IN)组成。

根据其中存储器模块的分布⽅式,阵列机可分为两种基本结构:分布式存储器的阵列机和共享存储器的阵列机(理解⼆者不同之处)。

阵列机的主要特点: 它采⽤资源重复的⽅法引⼊空间因素,这与利⽤时间重叠的流⽔线处理机是不⼀样的。

它是利⽤并⾏性中的同时性⽽不是并发性,所有的处理单元必须同时进⾏相同操作(资源重复同时性)(我们想象⼀下亚运会的开幕式⼤型团体操表演,每个⼈就是⼀个PE,他们听从⼀个总指挥的指令,同时进⾏⾃⼰的操作,很快地就能"计算"出⼀个结果(队形)来。

) 它是以某类算法为背景的专⽤计算机,基本上是专⽤于向量处理的计算机(某类算法专⽤机)。

存储器概述

EEPROM芯片2864A

N13根地址线A12~A0 8 根 数 据 线 I/O7 ~

I/O0 片选CE*

读写OE*、WE*

A12 2 A7 3 A6 4 A5 5 A4 6 A3 7 A2 8 A1 9 A0 10 I/O0 11 I/O1 12 I/O2 13 GND 14

动态RAM DRAM 4116 DRAM 2164

1 静态RAM

SRAM的基本存储单元是触发器电路 每个基本存储单元存储二进制数一位 许多个基本存储单元形成行列存储矩阵

SRAM芯片6264 NC 1 A12 2

A7 3

存储容量为8K×8

A6 4 A5 5

28个引脚:

A4 6

13根地址线A12~A0 8根数据线D7~D0

Infineon(英飞菱)的内存条结构剖析

1、PCB板 下图是Infineon原装256MB DDR266,采用单面8颗粒TSOP封装。

2、金手指 这一根根黄色的接触点是内存与主板内存槽接触的部分,数据就是靠它们来传输的,通

常称为金手指。

3、内存芯片(颗粒)内存的芯片就是内存的灵魂所在,内存的性能、速度、容量都是由内 存芯片决定的。

只读存储器ROM

掩膜ROM:信息制作在芯片中,不可更改 PROM:允许一次编程,此后不可更改 EPROM:用紫外光擦除,擦除后可编程;

并允许用户多次擦除和编程 EEPROM(E2PROM):采用加电方法在

线进行擦除和编程,也可多次擦写 Flash Memory(闪存):能够快速擦写的

EEPROM,但只能按块(Block)擦除

28 Vcc 27 A14 26 A13 25 A8

24 A9 23 A11 22 OE 21 A10 20 CE 19 D7 18 D6 17 D5 16 D4 15 D3

操作系统原理-第九章 设备管理习题(有答案)

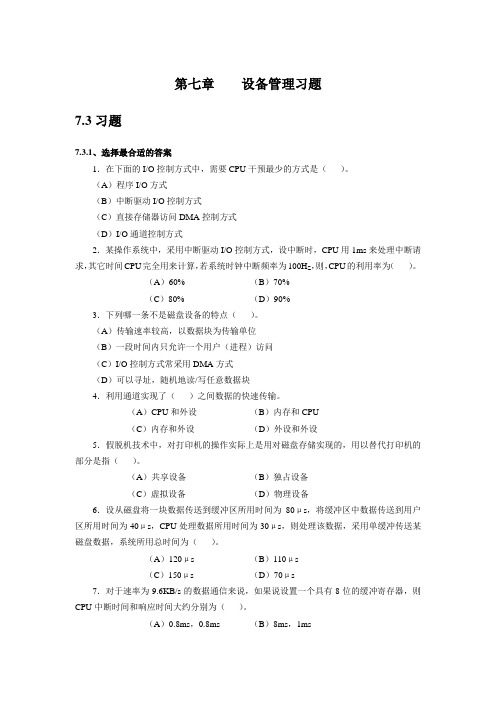

第七章设备管理习题7.3习题7.3.1、选择最合适的答案1.在下面的I/O控制方式中,需要CPU干预最少的方式是()。

(A)程序I/O方式(B)中断驱动I/O控制方式(C)直接存储器访问DMA控制方式(D)I/O通道控制方式2.某操作系统中,采用中断驱动I/O控制方式,设中断时,CPU用1ms来处理中断请求,其它时间CPU完全用来计算,若系统时钟中断频率为100H Z,则,CPU的利用率为()。

(A)60% (B)70%(C)80% (D)90%3.下列哪一条不是磁盘设备的特点()。

(A)传输速率较高,以数据块为传输单位(B)一段时间内只允许一个用户(进程)访问(C)I/O控制方式常采用DMA方式(D)可以寻址,随机地读/写任意数据块4.利用通道实现了()之间数据的快速传输。

(A)CPU和外设(B)内存和CPU(C)内存和外设(D)外设和外设5.假脱机技术中,对打印机的操作实际上是用对磁盘存储实现的,用以替代打印机的部分是指()。

(A)共享设备(B)独占设备(C)虚拟设备(D)物理设备6.设从磁盘将一块数据传送到缓冲区所用时间为80μs,将缓冲区中数据传送到用户区所用时间为40μs,CPU处理数据所用时间为30μs,则处理该数据,采用单缓冲传送某磁盘数据,系统所用总时间为()。

(A)120μs (B)110μs(C)150μs (D)70μs7.对于速率为9.6KB/s的数据通信来说,如果说设置一个具有8位的缓冲寄存器,则CPU中断时间和响应时间大约分别为()。

(A)0.8ms,0.8ms (B)8ms,1ms(C)0.8ms,0.1ms (D)0.1ms,0.1ms8.在调试程序时,可以先把所有输出送屏幕显示而不必正式输出到打印设备,其运用了()。

(A)SPOOLing技术(B)I/O重定向(C)共享技术(D)缓冲技术9.设备驱动程序是系统提供的一种通道程序,它专门用于在请求I/O的进程与设备控制器之间传输信息。

计算机组成原理第九章课件(白中英编科学出版社)

⊙第九章并行组织

计算机组成原理

任课教师:赵孟德 上海电机学院

计算机组成原理

☼ 第一章 计算机系统概论 ☼ 第二章 运算方法和运算器 ☼ 第三章 存储系统 ☼ 第四章 指令系统 ☼ 第五章 中央处理器 ☼ 第六章 总线系统 ☼ 第七章 外围设备 ☼ 第八章 输入输出系统 ☼ 第九章 并行组织

机群具有低费用、可扩展且故障分离的优 势;有许多大型机的应用更适合在松散连 接的机器上运行,例如网络服务公司的文 件服务器、Web服务器,还有数据库领域、 科学计算市场

计算机组成原理

多线程技术

⊙第九章并行组织

进程(process)是可以独立运行的一段代码

多个处理器可以执行同一个程序并共享程序代码 和地址空间。当多个进程用这种方式共享程序代 码和地址空间时,常被称之为线程(thread)

寄存器-寄存器向量结构

– 所有向量操作是在向量寄存器之间进行(除向 量读取和存储)

– 对应标量的寄存器-寄存器(load-store)结构 – 图9.12

计算机组成原理

向量机的特点

⊙第九章并行组织

一条指令执行大量运算(相当于标量处理的一个 循环)

– 减少了大量取指操作

每个结果都与前一个结果不相关

退出逻辑跟踪两个逻辑处理器 交替以程序顺序退出微操作

计算机组成原理

⊙第九章并行组织

第9章教学要求

了解互连网络的作用

区别标量处理和向量处理,了解向量处理机和阵 列处理机的概念

了解多处理机系统和机群系统的概念

END

计算机组成原理

第九章 小结

⊙第九章并行组织

计算机组成原理

⊙第九章并行组织

本章小结

⊙第九章并行组织

计算机组成原理 第9章

9.1 I/O接口的类型及其功能

• I/O接口(Interface)是计算机主机(CPU)与外围设备 的连接部件,它是CPU与外围设备进行信息交换时所必需 的电路,主要用于解决不同设备与CPU之间的速度差异、 数据变换与缓冲等问题。 • 9.1.1 I/O接口的类型 按照数据传送的方式分:并行接口和串行接口 按数据传送的控制方式分:程序控制方式接口(包括无条 件传送方式、程序查询方式、程序中断方式)、直接存 储器存取(DMA)接口、通道方式接口和I/O处理机等 按通用性分类:通用接口和专用接口。 按输入/输出的信号分类:I/O接口可分为数字接口和模拟 接口两种。

9.3 程序中断方式

9.3.1 中断的基本概念 中断指CPU在正常运行程序时,由于内部/外部事件 或由程序的预先安排使CPU中断正在运行的程序,而 转到为内部/外部事件或为预先安排的事件服务的程 序中去。服务完毕,再返回去继续执行被暂时中断的 程序。内部/外部事件或为预先安排的事件往往比 CPU当前正在运行的程序更加紧迫。这种暂时停止当 前运行的程序而去执行其它紧迫任务的过程叫做中断。

9.1.2 I/O接口的功能

1.寻址 I/O 接口为每一个外围设备都分配一个地址码。以便 CPU 访问某个外围设备时能够根据给定的设备地址找到此 设备。 2.数据缓冲 3.预处理 4.控制功能

9.2 CPU与I/O接口之间的信息传送方式

外围设备的定时方式:CPU 与外围设备的定时,有三种 情况: • 速度极慢或简单的外围设备,如机械开关、显示二极 管等,CPU总是能足够快地作出响应。 • 慢速或中速的外围设备:这类设备的速度和CPU的速 度并不在一个数量级,或者由于设备(如键盘)本身 是在不规则时间间隔下操作的,因此,CPU与这类设 备之间的数据交换通常采用异步方式。 • 高速的外部设备:这类设备以相等的时间间隔操作, 而CPU也是以等间隔的速率执行输入/输出指令,因此, 这种方式叫做同步定时方式。一旦CPU和外设发生同 步,它们之间的数据交换便靠时钟脉冲控制来进行。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

9.2 随机存取存储器RAM

9.2.2 SRAM的结构 4.SRAM常用器件

9.2 随机存取存储器RAM

9.2.3 DRAM工作原理

9.2 随机存取存储器RAM

9.2.4 SRAM存储容量的扩展方法 1.位扩展

9.2 随机存取存储器RAM

9.2.4 SRAM存储容量的扩展方法 2. 字扩展

9.3 只读存储器ROM

9.5 存储器应用电路设计

9.5.2 简易逻辑分析仪设计 2. 调入LPM_RAM模块

9.5 存储器应用电路设计

9.5.2 简易逻辑分析仪设计 2. 调入LPM_RAM模块

9.5 存储器应用电路设计

9.5.2 简易逻辑分析仪设计 3. 调入计数器模块LPM_COUNTER

4. 系统功能分析

9.5 存储器应用电路设计

9.3.1 ROM的分类与结构 1.ROM的分类

9.3 只读存储器ROM

9.3.1 ROM的分类与结构 2.ROM的结构

9.3 只读存储器ROM

9.3.2 掩膜 ROM

9.3 只读存储器ROM

9.3.3 可编程ROM结构原理 1.可编程ROM(Programmable ROM,简称PROM)

9.3 只读存储器ROM

9.3.3 可编程ROM结构原理 2.可擦除可编程ROM

9.3 只读存储器ROM

9.3.3 可编程ROM结构原理 2.可擦除可编程ROM

9.3 只读存储器ROM

9.3.3 可编程ROM结构原理 2.可擦除可编程ROM

9.3 只读存储器ROM

9.3.3 可编程ROM结构原理 3.电可擦型可编程ROM

9.5 存储器应用电路设计

9.5.3 乐曲硬件演奏电路设计

③ 模块CNT138T是一个8位二进制计数器,内部设置计数最大值为138, 即一个模为139的计数器,用作为音符数据ROM MUSIC的地址发生器。

9.3 只读存储器ROM

9.3.3 可编程ROM结构原理

9.3 只读存储器ROM

通过分析可得到其它 2764的地址为: U1(2000H~3FFFH)、 U2(4000H~5FFFH)、 U3(6000H~7FFFH)、 U4(8000H~9FFFH)、 U5(A000H~BFFFH)、 U6(C000H~DFFFH)、 U7(E000H~FFFFH)。

9.3 只读存储器ROM

9.3.4 其它类型的存储器 1. 快闪存储器Flash Memory 2. 非易失性静态读写存储器NVSRAM 3. 串行存储器 4. 多端口存储器MPRAM

9.4 FPGA中的嵌入式存储器

9.5 存储器应用电路设计

9.5.1 利用LPM_ROM设计查表式乘法器

9.5 存储器应用电路设计

第9章 存储器及其应用

9.1 概述

9.1.1 存储器的分类 1. 按存储介质分类 2. 按存取功能分类 3.按制造工艺分类

4.根据数据的输入/输出方式分类

9.1 概述

9.1.2 存储器的技术指标 1.存储容量

2.存取速度

9.2 随机存取存储器RAM

9.2.1 RAM的分类与结构特点 1.RAM分类

9.5 存储器应用电路设计

9.5.3 乐曲硬件演奏电路设计

③ 模块CNT138T是一个8位二进制计数器,内部设置计数最大值为138, 即一个模为139的计数器,用作为音符数据ROM MUSIC的地址发生器。

9.5 存储器应用电路设计

9.5.3 乐曲硬件演奏电路设计

③ 模块CNT138T是一个8位二进制计数器,内部设置计数最大值为138, 即一个模为139的计数器,用作为音符数据ROM MUSIC的地址发生器。

9.5.2 简易逻辑分析仪设计 5. 系统时序仿真

9.5 存储器应用电路设计

9.5.3 乐曲硬件演奏电路设计

9.5 存储器应用电路设计

9.5.3 乐曲硬件演奏电路设计 ① 音符的频率可以由图9-30中的SPKER获得

9.5 存储器应用电路设计

9.5.3 乐曲硬件演奏电路设计 ② 音符的持续时间需根据乐曲的速度及每个音符的节拍数来确定

9.2 随机存取存储器RAM

9.2.1 RAM的分类与结构特点 2.RAM的基本结构

9.2 随机存取存储器RAM

9.2.2 SRAM的结构 1.SRAM的基本存储单元

9.2 随机存取存储器RAM

9.2.2 SRAM的结构 2.用D触发器构成SRAM结构

9.2 随机存取存储器RAM

9.2.2 SRAM的结构 3.SRAM存储矩阵结构

9.5.1 利用LPM_ROM设计查表式乘法器

9.5 存储器应用电路设计

9.5.1 利用LPM_ROM设计查表式乘法器

9.5 存储器应用电路设计

9.5.1 利用LPM_ROM设计查表式乘法器

9.5 存储器应用电路设计

9.5.1 利用LPM_ROM设计查表式乘法器

9.5 存储器应用电路设计

9.5.2 简易逻辑分析仪设计 1. 基本电路结构